# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823sh005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

### **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

#### 17

# **Register Map**

Table 8 lists the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0823 Series devices. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, or all GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page No   |

|----------------|-----------------------------------|---------------|-------------|-----------|

| General-Purpos | <u> </u>                          |               |             | 1 490 110 |

| Z8F0823/Z8F08  |                                   |               |             |           |

|                |                                   |               | ~~~         |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | _             | XX          |           |

| Z8F0423/Z8F04  |                                   |               |             |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | —             | XX          |           |

| Z8F0223/Z8F02  | 13 Devices                        |               |             |           |

| 000–1FF        | General-Purpose Register File RAM | —             | XX          |           |

| 200–EFF        | Reserved                          | —             | XX          |           |

| Z8F0123/Z8F01  | 13 Devices                        |               |             |           |

| 000–0FF        | General-Purpose Register File RAM | _             | XX          |           |

| 100–EFF        | Reserved                          | _             | XX          |           |

| Timer 0        |                                   |               |             |           |

| F00            | Timer 0 High Byte                 | ТОН           | 00          | 80        |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | 80        |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | 81        |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | 81        |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | 81        |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | 82        |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | 82        |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | 83        |

| Timer 1        |                                   |               |             |           |

| F08            | Timer 1 High Byte                 | T1H           | 00          | 80        |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | 80        |

| F0A            | Timer 1 Reload High Byte          | T1RH          | FF          | 81        |

| F0B            | Timer 1 Reload Low Byte           | T1RL          | FF          | 81        |

| Address (Hex)   | Register Description                  | Mnemonic | Reset (Hex) | Page No                   |

|-----------------|---------------------------------------|----------|-------------|---------------------------|

| FF2             | Watchdog Timer Reload High Byte       | WDTH     | FF          | 91                        |

| FF3             | Watchdog Timer Reload Low Byte        | WDTL     | FF          | 91                        |

| FF4–FF5         | Reserved                              |          | XX          |                           |

| Trim Bit Contro | I                                     |          |             |                           |

| FF6             | Trim Bit Address                      | TRMADR   | 00          | 143                       |

| FF7             | Trim Data                             | TRMDR    | XX          | 144                       |

| Flash Memory    | Controller                            |          |             |                           |

| FF8             | Flash Control                         | FCTL     | 00          | 137                       |

| FF8             | Flash Status                          | FSTAT    | 00          | 137                       |

| FF9             | Flash Page Select                     | FPS      | 00          | 138                       |

|                 | Flash Sector Protect                  | FPROT    | 00          | 139                       |

| FFA             | Flash Programming Frequency High Byte | FFREQH   | 00          | 140                       |

| FFB             | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 140                       |

| eZ8 CPU         |                                       |          |             |                           |

| FFC             | Flags                                 |          | XX          | Refer to eZ8              |

| FFD             | Register Pointer                      | RP       | XX          | CPU Core                  |

| FFE             | Stack Pointer High Byte               | SPH      | XX          | —User Manual<br>_(UM0128) |

| FFF             | Stack Pointer Low Byte                | SPL      | XX          | _(0///0/20)               |

| XX=Undefined    |                                       |          |             |                           |

#### Table 8. Register File Address Map (Continued)

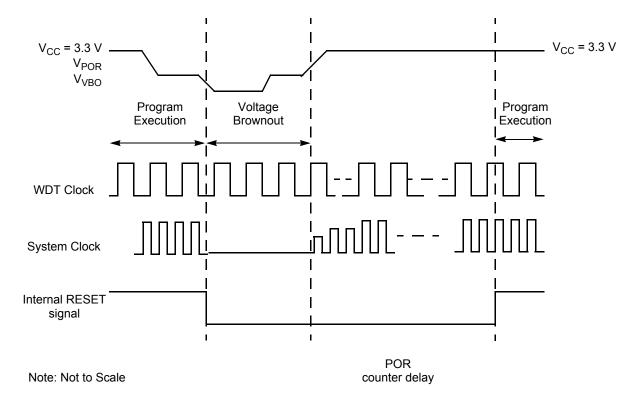

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or STOP mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. For more details, see Timers on page 67.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

## **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA, and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see Electrical Characteristics on page 193.

## **Shared Reset Pin**

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, take care that no external stimulus drives the pin Low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

## **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$ONE-SHOT Mode Time-Out Period (s) = \frac{(Reload Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below to configure a timer for CONTINUOUS mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

## **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |  |

|-------|---|-----|---|----|----|---|---|---|--|--|--|--|--|

| FIELD |   | TXD |   |    |    |   |   |   |  |  |  |  |  |

| RESET | Х | Х   | Х | Х  | Х  | Х | Х | Х |  |  |  |  |  |

| R/W   | W | W   | W | W  | W  | W | W | W |  |  |  |  |  |

| ADDR  |   |     |   | F4 | 0H |   |   |   |  |  |  |  |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

## Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS      | 7                                         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |  |

|-----------|-------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

| FIELD     | Reserved                                  |     |     |     |     |     |     |     |  |  |  |  |  |

| RESET     | U                                         | U   | U   | U   | U   | U   | U   | U   |  |  |  |  |  |

| R/W       | R/W                                       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| ADDR      | Information Page Memory 0020H             |     |     |     |     |     |     |     |  |  |  |  |  |

| Note: U = | U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

### Trim Bit Address 0001H—Reserved

#### Table 90. Trim Option Bits at 0001H

| BITS      | 7                             | 6            | 5            | 4          | 3   | 2   | 1   | 0   |  |  |  |  |  |

|-----------|-------------------------------|--------------|--------------|------------|-----|-----|-----|-----|--|--|--|--|--|

| FIELD     |                               | Reserved     |              |            |     |     |     |     |  |  |  |  |  |

| RESET     | U                             | U            | U            | U          | U   | U   | U   | U   |  |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W        | R/W | R/W | R/W | R/W |  |  |  |  |  |

| ADDR      | Information Page Memory 0021H |              |              |            |     |     |     |     |  |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write | <b>)</b> . |     |     |     |     |  |  |  |  |  |

Software Compensation Procedure on page 122. The location of each calibration byte is provided in Table 93 on page 148.

| Info Page | Memory  |                       | Reference               |                |

|-----------|---------|-----------------------|-------------------------|----------------|

| Address   | Address | Compensation<br>Usage | ADC Mode                | Туре           |

| 60        | FE60    | Offset                | Single-Ended Unbuffered | Internal 2.0 V |

| 08        | FE08    | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0 V |

| 09        | FE09    | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0 V |

| 63        | FE63    | Offset                | Single-Ended Unbuffered | Internal 1.0 V |

| 0A        | FE0A    | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0 V |

| 0B        | FE0B    | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0 V |

| 66        | FE66    | Offset                | Single-Ended Unbuffered | External 2.0 V |

| 0C        | FE0C    | Gain High Byte        | Single-Ended Unbuffered | External 2.0 V |

| 0D        | FE0D    | Gain Low Byte         | Single-Ended Unbuffered | External 2.0 V |

#### Table 93. ADC Calibration Data Location

### **Serialization Data**

#### Table 94. Serial Number at 001C-001F (S\_NUM)

| BITS      | 7                                 | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-----------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD     | S_NUM                             |              |              |     |     |     |     |     |  |  |  |  |

| RESET     | U                                 | U            | U            | U   | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                               | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Information Page Memory 001C-001F |              |              |     |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                       | y Reset. R/W | = Read/Write |     |     |     |     |     |  |  |  |  |

S NUM— Serial Number Byte

The serial number is a unique four-byte binary value.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# eZ8 CPU Instruction Set

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands, and comments.

Labels are assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

182

| Assembly        |                                                                                                                       | Addre       | ss Mode    | - Opcode(s) | Fla | ıgs |               |   |   |   | - Fetch | Instr  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----|-----|---------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                                                    | dst         | src        | (Hex)       | С   | z   | S             | v | D | Н |         | Cycles |

| HALT            | HALT Mode                                                                                                             |             |            | 7F          | -   | _   | -             | _ | - | - | 1       | 2      |

| INC dst         | $dst \leftarrow dst + 1$                                                                                              | R           |            | 20          | -   | *   | *             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | IR          |            | 21          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | r           |            | 0E-FE       | _   |     |               |   |   |   | 1       | 2      |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                              | RR          |            | A0          | -   | *   | *             | * | - | - | 2       | 5      |

|                 |                                                                                                                       | IRR         |            | A1          | -   |     |               |   |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1$ |             |            | BF          | *   | *   | *             | * | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                        | DA          |            | 8D          | _   | _   | _             | _ | _ | _ | 3       | 2      |

|                 |                                                                                                                       | IRR         |            | C4          | -   |     |               |   |   |   | 2       | 3      |

| JP cc, dst      | if cc is true<br>PC $\leftarrow$ dst                                                                                  | DA          |            | 0D-FD       | -   | _   | -             | _ | _ | - | 3       | 2      |

| JR dst          | $PC \leftarrow PC + X$                                                                                                | DA          |            | 8B          | -   | _   | _             | _ | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                               | DA          |            | 0B-FB       | -   | _   | _             | _ | _ | - | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                       | r           | IM         | 0C-FC       | -   | _   | -             | - | - | - | 2       | 2      |

|                 |                                                                                                                       | r           | X(r)       | C7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | X(r)        | r          | D7          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | r           | lr         | E3          | _   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | R           | R          | E4          | _   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | R           | IR         | E5          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | R           | IM         | E6          | -   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | IR          | IM         | E7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | lr          | r          | F3          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | IR          | R          | F5          | -   |     |               |   |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                          | f the resul | t of the o | peration.   |     |     | eset<br>et to |   | 0 |   |         |        |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

| Abbreviation | Description                           | Abbreviation                                   | Description            |

|--------------|---------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |

| СС           | Condition code                        | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                   | R                                              | 8-bit register         |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register             | RA                                             | Relative               |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |

## Table 116. Opcode Map Abbreviations

#### Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

## **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

#### Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |  |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |  |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |  |

|                     |                                                    | T <sub>A</sub> = | = 3.0 V to<br>0 °C to +<br>otherwise | 70 °C      |                           |                                                                                              |  |

|---------------------|----------------------------------------------------|------------------|--------------------------------------|------------|---------------------------|----------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                          | Minimum Typical  |                                      | Maximum    | Units                     | Conditions                                                                                   |  |

|                     | Resolution                                         | 10               |                                      | _          | bits                      |                                                                                              |  |

|                     | Differential Nonlinearity<br>(DNL)                 | -1.0             | _                                    | 1.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Integral Nonlinearity (INL)                        | -3.0             | _                                    | 3.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Offset Error with Calibration                      |                  | <u>+</u> 1                           |            | LSB <sup>3</sup>          |                                                                                              |  |

|                     | Absolute Accuracy with Calibration                 |                  | <u>+</u> 3                           |            | LSB <sup>3</sup>          |                                                                                              |  |

| V <sub>REF</sub>    | Internal Reference Voltage                         | 1.0<br>2.0       | 1.1<br>2.2                           | 1.2<br>2.4 | V                         | REFSEL=01<br>REFSEL=10                                                                       |  |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature   |                  | <u>+</u> 1.0                         |            | %                         | Temperature variation<br>with V <sub>DD</sub> = 3.0                                          |  |

| V <sub>REF</sub>    | Internal Reference Voltage Variation with $V_{DD}$ |                  | <u>+</u> 0.5                         |            | %                         | Supply voltage variation<br>with T <sub>A</sub> = 30 °C                                      |  |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance               |                  | 850                                  |            | Ω                         | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                     | Single-Shot Conversion<br>Time                     | _                | 5129                                 | -          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                  | 10258                                |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Continuous Conversion<br>Time                      | -                | 256                                  | -          |                           | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                  | 512                                  |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Signal Input Bandwidth                             | -                | 10                                   |            | kHz                       | As defined by -3 dB point                                                                    |  |

| R <sub>S</sub>      | Analog Source Impedance <sup>4</sup>               | -                | -                                    | 10         | kΩ                        | In unbuffered mode                                                                           |  |

### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing

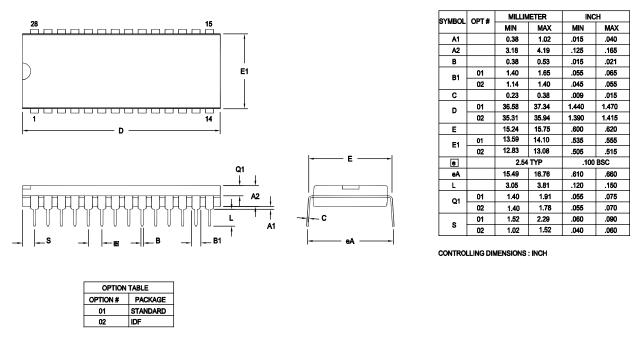

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

| Part Number                              | F           |           | ines      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|------------------------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part                                     | Flash       | RAM       | I/O Lines | Inter      | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 8                     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0813PB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °( | 0         |            |                        |                     |                |                     |

| Z8F0813PB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |           |           |            |                        |                     |                |                     |

218