Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823sj005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |

|-----------------|---------------------------|----------|-------------|---------|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |

| F10–F3F         | Reserved                  | —        | XX          |         |

| UART            |                           |          |             |         |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |

| F48–F6F         | Reserved                  | _        | XX          |         |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |

| F74–F7F         | Reserved                  | _        | XX          |         |

| Low Power Cor   | ntrol                     |          |             |         |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |

| F81             | Reserved                  |          | XX          |         |

| LED Controller  |                           |          |             |         |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |

| F85             | Reserved                  | _        | XX          |         |

| Oscillator Cont | rol                       |          |             |         |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |

| F87–F8F         | Reserved                  | _        | XX          |         |

| Comparator 0    |                           |          |             |         |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |

|                 |                           |          |             |         |

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 58      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 60      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 61      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 59      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 62      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 62      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 60      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 63      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 63      |

| FC9–FCC         | Reserved                |          | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 64      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 64      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 65      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 43      |

| FD1             | Port A Control          | PACTL    | 00          | 45      |

| FD2             | Port A Input Data       | PAIN     | XX          | 45      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 45      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 43      |

| FD5             | Port B Control          | PBCTL    | 00          | 45      |

| FD6             | Port B Input Data       | PBIN     | XX          | 45      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 45      |

| GPIO Port C     | ·                       |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 43      |

| FD9             | Port C Control          | PCCTL    | 00          | 45      |

| FDA             | Port C Input Data       | PCIN     | XX          | 45      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 45      |

| FDC-FEF         | Reserved                | _        | XX          |         |

| Watchdog Time   |                         |          |             |         |

| FF0             | Reset Status            | RSTSTAT  | XX          | 90      |

| -               | Watchdog Timer Control  | WDTCTL   | XX          | 90      |

|                 | 0                       | WDTU     |             |         |

## Table 8. Register File Address Map (Continued)

## Table 19. Port A–C Control Registers (PxCTL)

| BITS  | 7   | 6    | 5   | 4        | 3        | 2   | 1   | 0   |  |

|-------|-----|------|-----|----------|----------|-----|-----|-----|--|

| FIELD |     | PCTL |     |          |          |     |     |     |  |

| RESET |     | 00H  |     |          |          |     |     |     |  |

| R/W   | R/W | R/W  | R/W | R/W      | R/W      | R/W | R/W | R/W |  |

| ADDR  |     |      |     | FD1H, FD | 5H, FD9H |     |     |     |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

# Port A-C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address register (Table 20).

| BITS  | 7        | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| FIELD | DD7      | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |

| RESET | 1        | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W   | R/W      | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  | lf 01H i | If 01H in Port A–C Address Register, accessible through the Port A–C Control Register |     |     |     |     |     |     |  |

## Table 20. Port A–C Data Direction Sub-Registers (PxDD)

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–C Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tristated.

# Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 21) is accessed through the Port A–C Control register by writing 02H to the Port A–C Address register. The Port A–C Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–C Alternate Function Set 1 Sub-Registers on page 48 and Port A–C Alternate Function Set 2 Sub-Registers on

## Table 32. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |     | LEDLVLL[7:0] |     |     |     |     |     |     |  |

| RESET | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |     | F84H         |     |     |     |     |     |     |  |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA 01 = 7 mA10 = 13 mA

10 = 13 mA11 = 20 mA

|          | •                                   | •                                                                          |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 87)                             |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          |                                     |                                                                            |

## Table 33. Trap and Interrupt Vectors in Order of Priority

Reserved—Must be 0

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### Table 39. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |

| ADDR  |          | FC2H  |              |               |               |          |          |        |  |

Reserved—0 when read

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

## **IRQ1 Enable High and Low Bit Registers**

Table 40 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 41 and Table 42) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register.

|            |            | -        |             |

|------------|------------|----------|-------------|

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 40. IRQ1 Enable and Priority Encoding

where x indicates the register bits from 0–7.

63

#### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |  |

|------------|----------|-------------|-------------|--|

| 1          | 1        | Level 3     | High        |  |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-------|----------|-----|-----|-----|-------|-------|-------|-------|

| FIELD | Reserved |     |     |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |          |     |     | FC  | 7H    |       |       |       |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     |       |  |  |  |

|-------|-----|------|-------|-----|-------|-------|-------|-------|--|--|--|

| FIELD |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |  |  |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |  |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |  |

| ADDR  |     | FC8H |       |     |       |       |       |       |  |  |  |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the hold-ing register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

## **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

#### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2 received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

0 = No overrun error occurred

1 = An overrun error occurred

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred

1 = A framing error occurred

#### BRKD-Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit.

0 = No break occurred

1 = A break occurred

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting

1 = Transmission is complete

#### $CTS \longrightarrow \overline{CTS}$ signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

#### Table 65. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6    | 5      | 4    | 3   | 2   | 1 | 0 |  |  |  |

|-------|---|------|--------|------|-----|-----|---|---|--|--|--|

| FIELD |   |      | NEWFRM | MPRX |     |     |   |   |  |  |  |

| RESET | 0 | 0    | 0      | 0    | 0   | 0   | 0 | 0 |  |  |  |

| R/W   | R | R    | R      | R    | R/W | R/W | R | R |  |  |  |

| ADDR  |   | F44H |        |      |     |     |   |   |  |  |  |

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7   | 6    | 5    | 4   | 3    | 2    | 1    | 0    |  |  |  |  |

|-------|-----|------|------|-----|------|------|------|------|--|--|--|--|

| FIELD | TEN | REN  | CTSE | PEN | PSEL | SBRK | STOP | LBEN |  |  |  |  |

| RESET | 0   | 0    | 0    | 0   | 0    | 0    | 0    | 0    |  |  |  |  |

| R/W   | R/W | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |  |  |  |  |

| ADDR  |     | F42H |      |     |      |      |      |      |  |  |  |  |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled

1 = Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a run function can be implemented by writing 40H to this register.

Table 99. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3   | 2 | 1 | 0   |

|-------|---------|-------|--------|---|-----|---|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | RST |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0   | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R   | R | R | R/W |

#### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = Z8 Encore! XP F0823 Series device is operating in NORMAL mode

1 = Z8 Encore! XP F0823 Series device is in DEBUG mode

#### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

- 0 = Breakpoints are disabled

- 1 = Breakpoints are enabled

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled

1 = Debug Acknowledge is enabled

#### Reserved—0 when read

#### RST—Reset

Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 at the end of reset.

0 = No effect

1 = Reset the Flash Read Protect Option Bit device

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values as described in Trim Bit Address Space on page 146.

Select one of the two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 165.

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

|          | •        |                                               |

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

|          |          |                                               |

#### **Table 107. Arithmetic Instructions**

178

Table 112. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

## Table 113. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

## Table 114. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| Assembly        |                                                                  | Address Mode<br>Opcode |             |           | Flags |   |              |   |   |   | - Fetch | Instr. |

|-----------------|------------------------------------------------------------------|------------------------|-------------|-----------|-------|---|--------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                               | dst                    | src         | (Hex)     | С     | Ζ | S            | v | D | Н |         | Cycles |

| RR dst          |                                                                  | R                      |             | E0        | *     | * | *            | * | _ | - | 2       | 2      |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                    | IR                     |             | E1        | _     |   |              |   |   |   | 2       | 3      |

| RRC dst         |                                                                  | R                      |             | C0        | *     | * | *            | * | _ | - | 2       | 2      |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR                     |             | C1        | _     |   |              |   |   |   | 2       | 3      |

| SBC dst, src    | $dst \gets dst - src - C$                                        | r                      | r           | 32        | *     | * | *            | * | 1 | * | 2       | 3      |

|                 |                                                                  | r                      | lr          | 33        | _     |   |              |   |   |   | 2       | 4      |

|                 |                                                                  | R                      | R           | 34        | _     |   |              |   |   |   | 3       | 3      |

|                 |                                                                  | R                      | IR          | 35        | _     |   |              |   |   |   | 3       | 4      |

|                 |                                                                  | R                      | IM          | 36        | _     |   |              |   |   |   | 3       | 3      |

|                 |                                                                  | IR                     | IM          | 37        | _     |   |              |   |   |   | 3       | 4      |

| SBCX dst, src   | $dst \gets dst - src - C$                                        | ER                     | ER          | 38        | *     | * | *            | * | 1 | * | 4       | 3      |

|                 |                                                                  | ER                     | IM          | 39        | _     |   |              |   |   |   | 4       | 3      |

| SCF             | C ← 1                                                            |                        |             | DF        | 1     | - | _            | _ | _ | - | 1       | 2      |

| SRA dst         | <b>*</b> *                                                       | R                      |             | D0        | *     | * | *            | 0 | _ | - | 2       | 2      |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR                     |             | D1        |       |   |              |   |   |   | 2       | 3      |

| SRL dst         | 0 - D7 D6 D5 D4 D3 D2 D1 D0 - C                                  | R                      |             | 1F C0     | *     | * | 0            | * | _ | - | 3       | 2      |

|                 | dst                                                              | IR                     |             | 1F C1     |       |   |              |   |   |   | 3       | 3      |

| SRP src         | $RP \leftarrow src$                                              |                        | IM          | 01        | -     | _ | _            | _ | _ | - | 2       | 2      |

| STOP            | STOP Mode                                                        |                        |             | 6F        | _     | _ | _            | _ | _ | _ | 1       | 2      |

| SUB dst, src    | $dst \gets dst - src$                                            | r                      | r           | 22        | *     | * | *            | * | 1 | * | 2       | 3      |

|                 |                                                                  | r                      | lr          | 23        | -     |   |              |   |   |   | 2       | 4      |

|                 |                                                                  | R                      | R           | 24        | -     |   |              |   |   |   | 3       | 3      |

|                 |                                                                  | R                      | IR          | 25        | _     |   |              |   |   |   | 3       | 4      |

|                 |                                                                  | R                      | IM          | 26        | -     |   |              |   |   |   | 3       | 3      |

|                 |                                                                  | IR                     | IM          | 27        | -     |   |              |   |   |   | 3       | 4      |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu                | It of the o | peration. |       |   | ese<br>et to |   | 0 |   |         |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

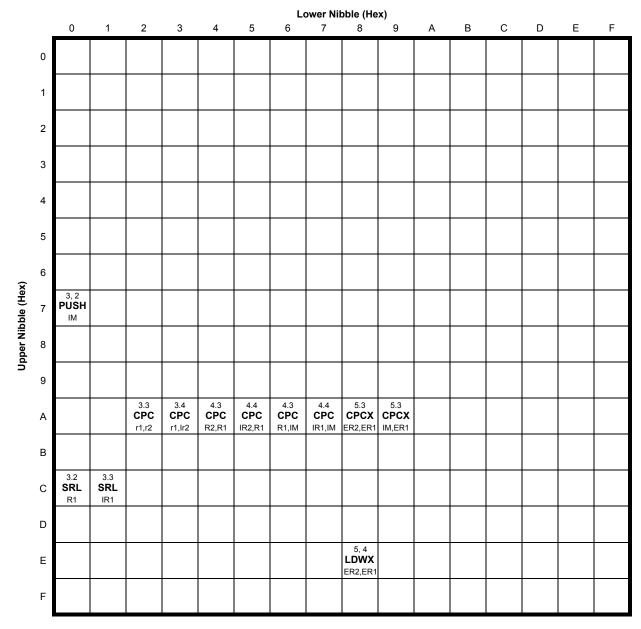

Figure 28. Second Opcode Map after 1FH

211

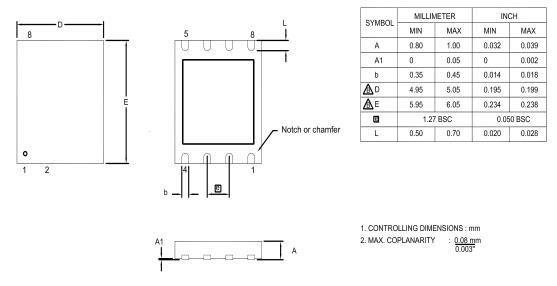

Figure 36 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F0823 Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 36. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

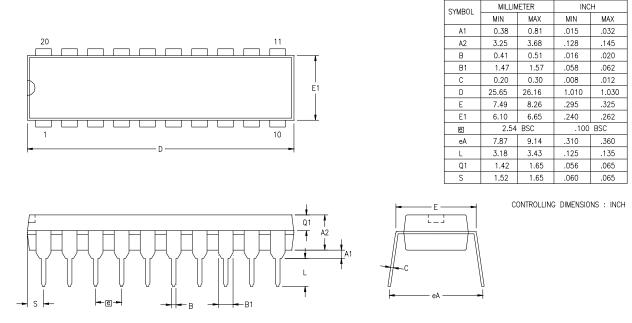

Figure 37 displays the 20-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Figure 37. 20-Pin Plastic Dual Inline Package (PDIP)

| nber                                |                                          |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |  |  |  |

|-------------------------------------|------------------------------------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|

| Part Number                         | Flash                                    | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |  |  |  |

| Z8 Encore! XP with 2                | KB Flash                                 | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |  |  |  |

| Standard Temperature: 0 °C to 70 °C |                                          |            |           |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005SC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005SC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005SC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005SC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005SC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005SC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005SC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005SC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005SC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Extended Temperatur                 | e: -40 °C                                | to 105 °C  | ;         |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005EC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005EC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005EC                      | 2 KB                                     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005EC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005EC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005EC                      | 2 KB                                     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005EC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005EC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005EC                      | 2 KB                                     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Replace C with G for Leas           | Replace C with G for Lead-Free Packaging |            |           |            |                        |                     |                |                     |  |  |  |

Index

**COMPARE 84** compare - extended addressing 175 COMPARE mode 84 compare with carry 175 compare with carry - extended addressing 175 complement 177 complement carry flag 176 condition code 173 continuous conversion (ADC) 120 CONTINUOUS mode 84 control register definition, UART 104 Control Registers 13, 17 **COUNTER modes 84** CP 175 **CPC 175 CPCX 175** CPU and peripheral overview 4 CPU control instructions 176 **CPX 175** Customer Support 237

# D

DA 173, 175 data memory 15 DC characteristics 194 debugger, on-chip 151 **DEC 175** decimal adjust 175 decrement 175 decrement and jump non-zero 178 decrement word 175 **DECW 175** destination operand 174 device, port availability 35 DI 176 direct address 173 disable interrupts 176 **DJNZ 178** dst 174

## Ε

EI 176

electrical characteristics 193 ADC 201 flash memory and timing 200 GPIO input data sample timing 202 Watchdog Timer 200, 202 enable interrupt 176 ER 173 extended addressing register 173 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 174 eZ8 CPU instruction notation 172 eZ8 CPU instruction set 171 eZ8 CPU instruction set 171

# F

FCTL register 137, 143, 144 features, Z8 Encore! 1 first opcode map 190 FLAGS 174 flags register 174 flash controller 4 option bit address space 144 option bit configuration - reset 141 program memory address 0000H 144 program memory address 0001H 145 flash memory 129 arrangement 130 byte programming 135 code protection 133 configurations 129 control register definitions 137, 143 controller bypass 136 electrical characteristics and timing 200 flash control register 137, 143, 144 flash option bits 134 flash status register 137 flow chart 132 frequency high and low byte registers 139 mass erase 135 operation 131 operation timing 133