Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823sj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Warning:** DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Table of Contents**

| Overview                                    | . 1 |

|---------------------------------------------|-----|

| Features                                    | . 1 |

| Part Selection Guide                        | . 2 |

| Block Diagram                               | . 3 |

| CPU and Peripheral Overview                 | . 4 |

| eZ8 CPU Features                            |     |

| General-Purpose I/O                         |     |

| Flash Controller                            |     |

| Internal Precision Oscillator               |     |

| Analog Comparator                           |     |

| Universal Asynchronous Receiver/Transmitter |     |

| Timers                                      |     |

| Interrupt Controller                        | . 5 |

| Reset Controller                            | . 6 |

| On-Chip Debugger                            |     |

| Pin Description                             | . 7 |

| Available Packages                          | . 7 |

| Pin Configurations                          |     |

| Signal Descriptions                         | . 9 |

| Pin Characteristics                         | 10  |

| Address Space                               | 13  |

| Register File                               | 13  |

| Program Memory                              | 13  |

| Data Memory                                 | 15  |

| Flash Information Area                      | 15  |

| Register Map                                | 17  |

| Reset and Stop Mode Recovery                | 21  |

| Reset Types                                 | 21  |

| Reset Sources                               | 22  |

| Power-On Reset                              |     |

| Voltage Brownout Reset                      |     |

| Watchdog Timer Reset                        |     |

| External Reset Input                        |     |

|                                             | 20  |

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA5 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         |                                         |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

0 PIN0 X R

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    |  |

|-------|------|------|------|------|------|------|------|--|

| FIELD | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 |  |

| RESET | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W   | R    | R    | R    | R    | R    | R    | R    |  |

# Table 28. Port A–C Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low)

1 = Input data is logical 1 (High)

# Port A–C Output Data Register

The Port A–C Output Data register (Table 29) controls the output data to the pins.

FD2H, FD6H, FDAH

### Table 29. Port A–C Output Data Register (PxOUT)

| BITS  | 7                | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|------------------|-------|-------|-------|-------|-------|-------|-------|

| FIELD | POUT7            | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET | 0                | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  | FD3H, FD7H, FDBH |       |       |       |       |       |       |       |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 30) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

ADDR

Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Timer Oscillator Fail Trap

### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all interrupts are enabled with identical interrupt priority (for example, all as Level 2 interrupts), the interrupt priority is assigned from highest to lowest as specified in Table 33 on page 54. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 33. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Timer Oscillator Fail Trap, and Illegal Instruction Trap always have highest (Level 3) priority.

#### Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests: LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

| BITS  | 7        | 6    | 5   | 4   | 3    | 2    | 1    | 0    |

|-------|----------|------|-----|-----|------|------|------|------|

| FIELD | Reserved |      |     |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0        | 0    | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W      | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |          | FC6H |     |     |      |      |      |      |

#### Table 36. Interrupt Request 2 Register (IRQ2)

Reserved—Must be 0

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x

1 = An interrupt request from GPIO Port C pin x is awaiting service

where x indicates the specific GPIO Port C pin number (0-3)

## **IRQ0 Enable High and Low Bit Registers**

Table 37 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 38 and Table 39) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register.

| -          |            |          |             |

|------------|------------|----------|-------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

#### Table 38. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2        | 1        | 0      |

|-------|----------|-------|-------|--------|--------|----------|----------|--------|

| FIELD | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |

| RESET | 0        | 0     | 0     | 0      | 0      | 0        | 0        | 0      |

| R/W   | R/W      | R/W   | R/W   | R/W    | R/W    | R/W      | R/W      | R/W    |

| ADDR  |          | FC1H  |       |        |        |          |          |        |

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 =Count occurs on the rising edge of the Timer Input signal

- 1 = Count occurs on the falling edge of the Timer Input signal

#### **PWM SINGLE OUTPUT Mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARE Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### GATED Mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

## Operation

#### **Data Format**

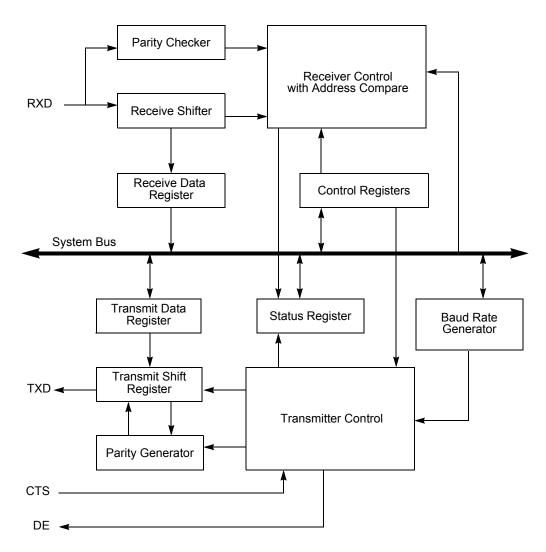

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7    | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|------|-----|------|-----|------|------|------|------|

| FIELD | TEN  | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0    | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  | F42H |     |      |     |      |      |      |      |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled

1 = Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 71 provides information about data rate errors for 5.5296 MHz System Clock.

| 5.5296 MHz System Clock  |                          |                      |           |  |  |  |  |

|--------------------------|--------------------------|----------------------|-----------|--|--|--|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |  |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |  |  |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |  |  |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |  |  |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |  |  |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |  |  |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |  |  |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |  |  |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |  |  |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |  |  |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |  |  |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |  |  |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |  |  |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |  |  |  |

#### Table 71. UART Baud Rates

| Table 78. Flash Code Pr | rotection Using  | the Flash O | ntion Bits |

|-------------------------|------------------|-------------|------------|

|                         | olection bailing | the mash o  |            |

| FWP | Flash Code Protection Description                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code programming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                           |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total size of the Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect Register controls the protection state of each Flash sector. This register is shared with the Page Select Register. It is accessed by writing 73H followed by 5EH to the Flash controller. The next write to the Flash Control Register targets the Sector Protect Register.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

# Operation

# **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

# **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

# **On-Chip Debugger**

Z8 Encore! XP<sup>®</sup> F0823 Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features that include:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize the pins available

# Architecture

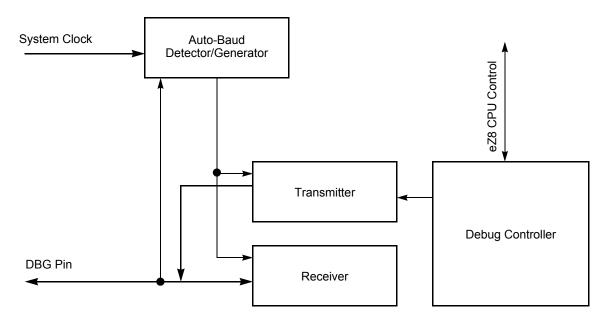

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 22 displays the architecture of the OCD.

Figure 22. On-Chip Debugger Block Diagram

## Table 110. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |  |  |  |  |  |  |  |

|----------|----------|------------------------|--|--|--|--|--|--|--|

| SCF      | —        | Set Carry Flag         |  |  |  |  |  |  |  |

| SRP      | SrC      | Set Register Pointer   |  |  |  |  |  |  |  |

| STOP     | _        | STOP Mode              |  |  |  |  |  |  |  |

| WDT      | _        | Watchdog Timer Refresh |  |  |  |  |  |  |  |

## Table 111. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                    |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | SrC         | Push using Extended Addressing                                         |

## Table 112. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| СОМ      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

| Table 114. Rotate and Shift Instructions | (Continued) |

|------------------------------------------|-------------|

|------------------------------------------|-------------|

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

# eZ8 CPU Instruction Summary

Table 115 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly        |                                                              | Addre      | ss Mode     | - Opcode(s) | Flags |              |   |   |   |   | - Fetch | Instr. |

|-----------------|--------------------------------------------------------------|------------|-------------|-------------|-------|--------------|---|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                           | dst        | src         | (Hex)       | С     | Ζ            | S | v | D | Н |         | Cycles |

| ADC dst, src    | $dst \gets dst + src + C$                                    | r          | r           | 12          | *     | *            | * | * | 0 | * | 2       | 3      |

|                 |                                                              | r          | lr          | 13          | _     |              |   |   |   |   | 2       | 4      |

|                 |                                                              | R          | R           | 14          | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                              | R          | IR          | 15          | _     |              |   |   |   |   | 3       | 4      |

|                 |                                                              | R          | IM          | 16          | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                              | IR         | IM          | 17          | _     |              |   |   |   |   | 3       | 4      |

| ADCX dst, src   | $dst \gets dst + src + C$                                    | ER         | ER          | 18          | *     | *            | * | * | 0 | * | 4       | 3      |

|                 |                                                              | ER         | IM          | 19          | _     |              |   |   |   |   | 4       | 3      |

| ADD dst, src    | $dst \gets dst + src$                                        | r          | r           | 02          | *     | *            | * | * | 0 | * | 2       | 3      |

|                 |                                                              | r          | lr          | 03          | _     |              |   |   |   |   | 2       | 4      |

|                 |                                                              | R          | R           | 04          | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                              | R          | IR          | 05          | _     |              |   |   |   |   | 3       | 4      |

|                 |                                                              | R          | IM          | 06          | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                              | IR         | IM          | 07          | _     |              |   |   |   |   | 3       | 4      |

| ADDX dst, src   | $dst \gets dst + src$                                        | ER         | ER          | 08          | *     | *            | * | * | 0 | * | 4       | 3      |

|                 |                                                              | ER         | IM          | 09          | _     |              |   |   |   |   | 4       | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o | peration.   |       | = Re<br>= Se |   |   | 0 |   |         |        |

#### Table 115. eZ8 CPU Instruction Summary

| Assembly        |                                                                       | Addre       | ss Mode     | Opcode(s) | Flags |              |   |   |   |   | - Fetch | Instr. |

|-----------------|-----------------------------------------------------------------------|-------------|-------------|-----------|-------|--------------|---|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                    | dst         | src         | (Hex)     | С     | Ζ            | S | v | D | Н | Cycles  |        |

| COM dst         | dst ← ~dst                                                            | R           |             | 60        | -     | *            | * | 0 | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 61        | _     |              |   |   |   |   | 2       | 3      |

| CP dst, src     | dst - src                                                             | r           | r           | A2        | *     | *            | * | * | _ | _ | 2       | 3      |

|                 |                                                                       | r           | lr          | A3        | _     |              |   |   |   |   | 2       | 4      |

|                 |                                                                       | R           | R           | A4        | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                                       | R           | IR          | A5        | _     |              |   |   |   |   | 3       | 4      |

|                 |                                                                       | R           | IM          | A6        | _     |              |   |   |   |   | 3       | 3      |

|                 |                                                                       | IR          | IM          | A7        | _     |              |   |   |   |   | 3       | 4      |

| CPC dst, src    | dst - src - C                                                         | r           | r           | 1F A2     | *     | *            | * | * | - | _ | 3       | 3      |

|                 |                                                                       | r           | lr          | 1F A3     | _     |              |   |   |   |   | 3       | 4      |

|                 |                                                                       | R           | R           | 1F A4     | _     |              |   |   |   |   | 4       | 3      |

|                 |                                                                       | R           | IR          | 1F A5     | _     |              |   |   |   |   | 4       | 4      |

|                 |                                                                       | R           | IM          | 1F A6     |       |              |   |   |   |   | 4       | 3      |

|                 |                                                                       | IR          | IM          | 1F A7     |       |              |   |   |   |   | 4       | 4      |

| CPCX dst, src   | dst - src - C                                                         | ER          | ER          | 1F A8     | *     | *            | * | * | - | _ | 5       | 3      |

|                 |                                                                       | ER          | IM          | 1F A9     | _     |              |   |   |   |   | 5       | 3      |

| CPX dst, src    | dst - src                                                             | ER          | ER          | A8        | *     | *            | * | * | _ | _ | 4       | 3      |

|                 |                                                                       | ER          | IM          | A9        | _     |              |   |   |   |   | 4       | 3      |

| DA dst          | $dst \gets DA(dst)$                                                   | R           |             | 40        | *     | *            | * | Х | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 41        | _     |              |   |   |   |   | 2       | 3      |

| DEC dst         | dst ← dst - 1                                                         | R           |             | 30        | -     | *            | * | * | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 31        | _     |              |   |   |   |   | 2       | 3      |

| DECW dst        | dst ← dst - 1                                                         | RR          |             | 80        | -     | *            | * | * | - | _ | 2       | 5      |

|                 |                                                                       | IRR         |             | 81        | _     |              |   |   |   |   | 2       | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                              |             |             | 8F        | -     | -            | - | _ | _ | _ | 1       | 2      |

| DJNZ dst, RA    | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X | r           |             | 0A-FA     | -     | _            | _ | _ | - | _ | 2       | 3      |

| El              | IRQCTL[7] ← 1                                                         |             |             | 9F        | _     | _            | _ | _ | _ | _ | 1       | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined            | of the resu | It of the o | peration. |       | = Re<br>= Se |   |   | 0 |   |         |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

|                   |                               |                                  | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                 |  |

|-------------------|-------------------------------|----------------------------------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|--|

| Symbol            | Parameter                     | arameter Minimum Typical Maximum |                        | Maximum              | Units | Conditions                                                                      |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4                              | _                      | -                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |  |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -                                | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$ $V_{DD} = 3.3 \text{ V};$                                     |  |

| IIL               | Input Leakage<br>Current      | -                                | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -                                | -                      | <u>+</u> 5           | μA    |                                                                                 |  |

| I <sub>LED</sub>  | Controlled Current            | 1.8                              | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |  |

|                   | Drive                         | 2.8                              | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |  |

|                   |                               | 7.8                              | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |  |

|                   |                               | 12                               | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -                                | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -                                | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -                                | 9.5 <sup>2</sup>       | -                    | pF    |                                                                                 |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30                               | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |  |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD                              |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |  |

### Table 118. DC Characteristics (Continued)

Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        |                                                                                                                                                                   |  |  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                             |  |  |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |  |  |

| Flash Byte Program Time                       | 20        | -                                    | 40      | μs     |                                                                                                                                                                   |  |  |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |  |  |

| Flash Mass Erase Time                         | 200       | -                                    | _       | ms     |                                                                                                                                                                   |  |  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                   |  |  |

| Flash Row Program Time                        | _         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |  |

| Data Retention                                | 100       | _                                    | -       | years  | 25 °C                                                                                                                                                             |  |  |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |  |  |

## Table 123. Flash Memory Electrical Characteristics and Timing

#### Table 124. Watchdog Timer Electrical Characteristics and Timing

|                     |                          | $T_A = -4$ | = 2.7 V to<br>40 °C to +<br>otherwise | 105 °C      |       |                                                                        |

|---------------------|--------------------------|------------|---------------------------------------|-------------|-------|------------------------------------------------------------------------|

| Symbol              | Parameter                | Minimum    | Typical                               | Maximum     | Units | Conditions                                                             |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |            | 10                                    |             | kHz   |                                                                        |

| F <sub>WDT</sub>    | WDT Oscillator Error     |            |                                       | <u>+</u> 50 | %     |                                                                        |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98       | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C                     |

|                     |                          | 0.70       | 1                                     | 1.30        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50       | 1                                     | 1.50        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

| mber                                |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |  |  |  |

|-------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|--|

| Part Number                         | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |  |  |  |

| Z8 Encore! XP with 2                | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |  |  |  |

| Standard Temperature: 0 °C to 70 °C |            |            |           |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Extended Temperatur                 | e: -40 °C  | to 105 °C  | )         |            |                        |                     |                |                     |  |  |  |

| Z8F0223PB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0223QB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0223SB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0223SH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0223HH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0223PH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0223SJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0223HJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0223PJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Replace C with G for Leas           | d-Free Pac | kaging     |           |            |                        |                     |                |                     |  |  |  |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Index

# Symbols

# 174 % 174 @ 174

# **Numerics**

10-bit ADC 4 40-lead plastic dual-inline package 214, 215

# Α

absolute maximum ratings 193 AC characteristics 197 ADC 175 architecture 117 automatic power-down 118 block diagram 118 continuous conversion 120 control register 122, 124 control register definitions 122 data high byte register 124 data low bits register 125 electrical characteristics and timing 201 operation 118 single-shot conversion 119 ADCCTL register 122, 124 ADCDH register 124 ADCDL register 125 ADCX 175 ADD 175 add - extended addressing 175 add with carry 175 add with carry - extended addressing 175 additional symbols 174 address space 13 ADDX 175 analog signals 10 analog-to-digital converter (ADC) 117 AND 177

ANDX 177 arithmetic instructions 175 assembly language programming 171 assembly language syntax 172

# В

B 174 b 173 baud rate generator, UART 103 **BCLR 176** binary number suffix 174 **BIT 176** bit 173 clear 176 manipulation instructions 176 set 176 set or clear 176 swap 176 test and jump 178 test and jump if non-zero 178 test and jump if zero 178 bit jump and test if non-zero 178 bit swap 178 block diagram 3 block transfer instructions 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178**

# С

CALL procedure 178 CAPTURE mode 84, 85 CAPTURE/COMPARE mode 85 cc 173 CCF 176 characteristics, electrical 193 clear 177 CLR 177 COM 177 227