Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | e200z7                                                                 |

| Core Size                  | 32-Bit Tri-Core                                                        |

| Speed                      | 264MHz                                                                 |

| Connectivity               | EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                        |

| Peripherals                | DMA, LVD, POR, Zipwire                                                 |

| Number of I/O              | -                                                                      |

| Program Memory Size        | 8MB (8M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 416-BGA                                                                |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777ck2mme3 |

#### Introduction

- Enhanced Modular Input/Output System (eMIOS) supporting 32 unified channels with each channel capable of single action, double action, pulse width modulation (PWM) and modulus counter operation

- Two Enhanced Queued Analog-to-Digital Converter (eQADC) modules with:

- Two separate analog converters per eQADC module

- Support for a total of 70 analog input pins, expandable to 182 inputs with offchip multiplexers

- Interface to twelve hardware Decimation Filters

- Enhanced "Tap" command to route any conversion to two separate Decimation Filters

- Four independent 16-bit Sigma-Delta ADCs (SDADCs)

- 10-channel Reaction Module

- Ethernet (FEC)

- Two PSI5 modules

- Two SENT Receiver (SRX) modules supporting 12 channels

- Zipwire: SIPI and LFAST modules

- Five Deserial Serial Peripheral Interface (DSPI) modules

- Five Enhanced Serial Communication Interface (eSCI) modules

- Four Controller Area Network (FlexCAN) modules

- Two M\_CAN modules that support FD

- Fault Collection and Control Unit (FCCU)

- Clock Monitor Units (CMUs)

- Tamper Detection Module (TDM)

- Cryptographic Services Engine (CSE)

- Complies with Secure Hardware Extension (SHE) Functional Specification Version 1.1 security functions

- Includes software selectable enhancement to key usage flag for MAC verification and increase in number of memory slots for security keys

- PASS module to support security features

- Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Device and board test support per Joint Test Action Group (JTAG) IEEE 1149.1 and 1149.7

- On-chip voltage regulator controller (VRC) that derives the core logic supply voltage from the high-voltage supply

- On-chip voltage regulator for flash memory

- Self Test capability

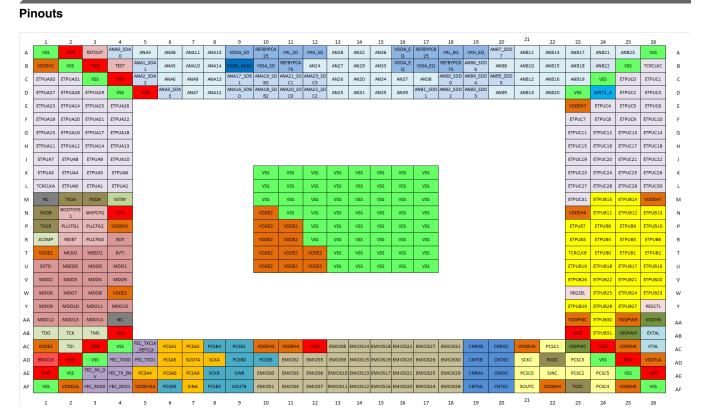

Figure 2. MPC5777C 416-ball MAPBGA (full diagram)

# 2.2 516-ball MAPBGA pin assignments

Figure 3 shows the 516-ball MAPBGA pin assignments.

# 3.4 Operating conditions

The following table describes the operating conditions for the device, and for which all specifications in the data sheet are valid, except where explicitly noted.

If the device operating conditions are exceeded, the functionality of the device is not guaranteed.

Table 3. Device operating conditions

| 0 1 1                            |                                                                                | 0 - 100                                |        | Value |                      |      |

|----------------------------------|--------------------------------------------------------------------------------|----------------------------------------|--------|-------|----------------------|------|

| Symbol                           | Parameter                                                                      | Conditions                             | Min    | Тур   | Max                  | Unit |

|                                  |                                                                                | Frequency                              | •      |       | •                    | •    |

| f <sub>SYS</sub>                 | Device operating frequency <sup>1</sup>                                        | _                                      | _      | _     | 264 <sup>2</sup>     | MHz  |

| f <sub>PLATF</sub>               | Platform operating frequency                                                   | _                                      |        | _     | 132                  | MHz  |

| f <sub>ETPU</sub>                | eTPU operating frequency                                                       | _                                      | _      | _     | 200                  | MHz  |

| f <sub>EBI</sub>                 | EBI operating frequency                                                        | _                                      | _      | _     | 66                   | MHz  |

| f <sub>PER</sub>                 | Peripheral block operating frequency                                           | _                                      | _      | _     | 132                  | MHz  |

| f <sub>FM_PER</sub>              | Frequency-modulated peripheral block operating frequency                       | _                                      | _      | _     | 132                  | MHz  |

| t <sub>CYC</sub>                 | Platform clock period                                                          | _                                      | 1 –    | _     | 1/f <sub>PLATF</sub> | ns   |

| t <sub>CYC_ETPU</sub>            | eTPU clock period                                                              | _                                      | 1 –    | _     | 1/f <sub>ETPU</sub>  | ns   |

| t <sub>CYC_PER</sub>             | Peripheral clock period                                                        | _                                      | T —    | _     | 1/f <sub>PER</sub>   | ns   |

|                                  |                                                                                | Temperature                            |        |       | 1                    | 1    |

| TJ                               | Junction operating temperature range                                           | Packaged devices                       | -40.0  | _     | 150.0                | °C   |

| $T_A$ ( $T_L$ to $T_H$ )         | Ambient operating temperature range                                            | Packaged devices                       | -40.0  | _     | 125.0 <sup>3</sup>   | °C   |

|                                  | -                                                                              | Voltage                                |        |       |                      | _I   |

| $V_{DD}$                         | External core supply voltage <sup>4, 5</sup>                                   | LVD/HVD enabled                        | 1.2    | _     | 1.32                 | V    |

|                                  |                                                                                | LVD/HVD disabled <sup>6, 7, 8, 9</sup> | 1.2    | _     | 1.38                 |      |

| V <sub>DDA_MISC</sub>            | TRNG and IRC supply voltage                                                    | _                                      | 3.5    | _     | 5.5                  | V    |

| $V_{DDEx}$                       | I/O supply voltage (fast I/O pads)                                             | 5 V range                              | 4.5    | _     | 5.5                  | V    |

|                                  |                                                                                | 3.3 V range                            | 3.0    | _     | 3.6                  |      |

| V <sub>DDEHx</sub> 9             | I/O supply voltage (medium I/O                                                 | 5 V range                              | 4.5    | _     | 5.5                  | V    |

|                                  | pads)                                                                          | 3.3 V range                            | 3.0    | _     | 3.6                  |      |

| V <sub>DDEH1</sub>               | eTPU_A, eSCI_A, eSCI_B, and configuration I/O supply voltage (medium I/O pads) | 5 V range                              | 4.5    | _     | 5.5                  | V    |

| V <sub>DDPMC</sub> <sup>10</sup> | Power Management Controller (PMC) supply voltage                               | Full functionality                     | 3.15   | _     | 5.5                  | V    |

| $V_{DDPWR}$                      | SMPS driver supply voltage                                                     | Reference to V <sub>SSPWR</sub>        | 3.0    | _     | 5.5                  | V    |

| $V_{DDFLA}$                      | Flash core voltage                                                             | _                                      | 3.15   | _     | 3.6                  | V    |

| V <sub>STBY</sub>                | RAM standby supply voltage                                                     | _                                      | 0.9511 | _     | 5.5                  | V    |

Table continues on the next page...

Table 3. Device operating conditions (continued)

| Combal                                         | Parameter                                            | Conditions                   |          | Value               |                   | Unit |

|------------------------------------------------|------------------------------------------------------|------------------------------|----------|---------------------|-------------------|------|

| Symbol                                         | Parameter                                            | Conditions                   | Min      | Тур                 | Max               | Unit |

| V <sub>STBY_BO</sub>                           | Standby RAM brownout flag trip point voltage         | _                            | _        | _                   | 0.9 <sup>12</sup> | V    |

| V <sub>RL_SD</sub>                             | SDADC ground reference voltage                       | _                            |          | V <sub>SSA_SD</sub> |                   | V    |

| V <sub>DDA_SD</sub>                            | SDADC supply voltage <sup>13</sup>                   | _                            | 4.5      | _                   | 5.5               | V    |

| V <sub>DDA_EQA/B</sub>                         | eQADC supply voltage                                 | _                            | 4.75     | _                   | 5.25              | V    |

| $V_{RH\_SD}$                                   | SDADC reference                                      | _                            | 4.5      | V <sub>DDA_SD</sub> | 5.5               | V    |

| V <sub>DDA_SD</sub> – V <sub>RH_SD</sub>       | SDADC reference differential voltage                 | _                            | _        | _                   | 25                | mV   |

| V <sub>SSA_SD</sub> – V <sub>RL_SD</sub>       | V <sub>RL_SD</sub> differential voltage              | _                            | -25      | _                   | 25                | mV   |

| $V_{RH\_EQ}$                                   | eQADC reference                                      | _                            | 4.75     | _                   | 5.25              | V    |

| V <sub>DDA_EQA/B</sub> –<br>V <sub>RH_EQ</sub> | eQADC reference differential voltage                 | _                            | _        | _                   | 25                | mV   |

| V <sub>SSA_EQ</sub> – V <sub>RL_EQ</sub>       | V <sub>RL_EQ</sub> differential voltage              | _                            | -25      | _                   | 25                | mV   |

| V <sub>SSA_EQ</sub> – V <sub>SS</sub>          | V <sub>SSA_EQ</sub> differential voltage             | _                            | -25      | _                   | 25                | mV   |

| V <sub>SSA_SD</sub> – V <sub>SS</sub>          | V <sub>SSA_SD</sub> differential voltage             | _                            | -25      | _                   | 25                | mV   |

| $V_{RAMP}$                                     | Slew rate on power supply pins                       | _                            | <u> </u> | _                   | 100               | V/ms |

|                                                |                                                      | Current                      |          | •                   |                   | '    |

| I <sub>IC</sub>                                | DC injection current (per pin) <sup>14,</sup> 15, 16 | Digital pins and analog pins | -3.0     | _                   | 3.0               | mA   |

| I <sub>MAXSEG</sub>                            | Maximum current per power segment <sup>17, 18</sup>  | _                            | -80      | _                   | 80                | mA   |

- Maximum operating frequency is applicable to the computational cores and platform for the device. See the Clocking chapter in the MPC5777C Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 2. If frequency modulation (FM) is enabled, the maximum frequency still cannot exceed this value.

- The maximum specification for operating junction temperature T<sub>J</sub> must be respected. Thermal characteristics provides details.

- 4. Core voltage as measured on device pin to guarantee published silicon performance

- 5. During power ramp, voltage measured on silicon might be lower. Maximum performance is not guaranteed, but correct silicon operation is guaranteed. See power management and reset management for description.

- 6. Maximum core voltage is not permitted for entire product life. See absolute maximum rating.

- 7. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device.

- 8. This LVD/HVD disabled supply voltage condition only applies after LVD/HVD are disabled by the application during the reset sequence, and the LVD/HVD are active until that point.

- 9. This spec does not apply to  $V_{\mbox{\scriptsize DDEH1}}.$

- 10. When internal flash memory regulator is used:

- Flash memory read operation is supported for a minimum  $V_{DDPMC}$  value of 3.15 V.

- Flash memory read, program, and erase operations are supported for a minimum V<sub>DDPMC</sub> value of 3.5 V.

When flash memory power is supplied externally (V<sub>DDPMC</sub> shorted to V<sub>DDFLA</sub>): The V<sub>DDPMC</sub> range must be within the limits specified for LVD\_FLASH and HVD\_FLASH monitoring. Table 29 provides the monitored LVD\_FLASH and HVD\_FLASH limits

- 11. If the standby RAM regulator is not used, the V<sub>STBY</sub> supply input pin must be tied to ground.

- 12. V<sub>STBY\_BO</sub> is the maximum voltage that sets the standby RAM brownout flag in the device logic. The minimum voltage for RAM data retention is guaranteed always to be less than the V<sub>STBY\_BO</sub> maximum value.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 9, 06/2016.

# 3.8.1 Enhanced Queued Analog-to-Digital Converter (eQADC)

Table 17. eQADC conversion specifications (operating)

| Cumbal             | Devemeter                                                   | Va         | lue             | 11                   |

|--------------------|-------------------------------------------------------------|------------|-----------------|----------------------|

| Symbol             | Parameter                                                   | Min        | Max             | Unit                 |

| f <sub>ADCLK</sub> | ADC Clock (ADCLK) Frequency                                 | 2          | 33              | MHz                  |

| CC                 | Conversion Cycles                                           | 2 + 13     | 128 + 15        | ADCLK cycles         |

| T <sub>SR</sub>    | Stop Mode Recovery Time <sup>1</sup>                        | 10         | _               | μs                   |

| _                  | Resolution <sup>2</sup>                                     | 1.25       | _               | mV                   |

| INL                | INL: 16.5 MHz eQADC clock <sup>3</sup>                      | -4         | 4               | LSB <sup>4</sup>     |

|                    | INL: 33 MHz eQADC clock <sup>3</sup>                        | -6         | 6               | LSB                  |

| DNL                | DNL: 16.5 MHz eQADC clock <sup>3</sup>                      | -3         | 3               | LSB                  |

|                    | DNL: 33 MHz eQADC clock <sup>3</sup>                        | -3         | 3               | LSB                  |

| OFFNC              | Offset Error without Calibration                            | 0          | 140             | LSB                  |

| OFFWC              | Offset Error with Calibration                               | -8         | 8               | LSB                  |

| GAINNC             | Full Scale Gain Error without Calibration                   | -150       | 0               | LSB                  |

| GAINWC             | Full Scale Gain Error with Calibration                      | -8         | 8               | LSB                  |

| I <sub>INJ</sub>   | Disruptive Input Injection Current <sup>5, 6, 7, 8</sup>    | -3         | 3               | mA                   |

| E <sub>INJ</sub>   | Incremental Error due to injection current <sup>9, 10</sup> | _          | +4              | Counts               |

| TUE                | TUE value <sup>11, 12</sup> (with calibration)              | _          | ±8              | Counts               |

| GAINVGA1           | Variable gain amplifier accuracy (gain = 1) <sup>13</sup>   | -          | -               | Counts <sup>15</sup> |

|                    | INL, 16.5 MHz ADC                                           | -4         | 4               |                      |

|                    | INL, 33 MHz ADC                                             | -8         | 8               |                      |

|                    | DNL, 16.5 MHz ADC                                           | -314       | 3 <sup>14</sup> |                      |

|                    | DNL, 33 MHz ADC                                             | -314       | 3 <sup>14</sup> |                      |

| GAINVGA2           | Variable gain amplifier accuracy (gain = 2) <sup>13</sup>   | -          | -               | Counts               |

|                    | INL, 16.5 MHz ADC                                           | <b>-</b> 5 | 5               |                      |

|                    | INL, 33 MHz ADC                                             | -8         | 8               |                      |

|                    | DNL, 16.5 MHz ADC                                           | -3         | 3               |                      |

|                    | DNL, 33 MHz ADC                                             | -3         | 3               |                      |

| GAINVGA4           | Variable gain amplifier accuracy (gain = 4) <sup>13</sup>   | -          | -               | Counts               |

|                    | INL, 16.5 MHz ADC                                           | <b>-7</b>  | 7               |                      |

|                    | INL, 33 MHz ADC                                             | -8         | 8               |                      |

|                    | DNL, 16.5 MHz ADC                                           | _4         | 4               |                      |

|                    |                                                             |            |                 |                      |

| 1                  | DNL, 33 MHz ADC                                             | -4         | 4               | mΛ                   |

| I <sub>ADC</sub>   | Current consumption per ADC (two ADCs per EQADC)            | _          | 10              | mA<br>A              |

| $I_{ADR}$          | Reference voltage current consumption per EQADC             | _          | 200             | μΑ                   |

<sup>1.</sup> Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

<sup>2.</sup> At V<sub>RH\_EQ</sub> – V<sub>RL\_EQ</sub> = 5.12 V, one count = 1.25 mV without using pregain. Based on 12-bit conversion result; does not account for AC and DC errors

<sup>3.</sup> INL and DNL are tested from  $V_{RL}$  + 50 LSB to  $V_{RH}$  – 50 LSB.

<sup>4.</sup> At  $V_{RH} = Q - V_{RL} = Q = 5.12 \text{ V}$ , one LSB = 1.25 mV.

| Table 18. | SDADC electrical | specifications | (continued) |

|-----------|------------------|----------------|-------------|

|-----------|------------------|----------------|-------------|

| Cumbal                  | Parameter                                       | Conditions                                     |     | Valu | е                                               | Unit     |

|-------------------------|-------------------------------------------------|------------------------------------------------|-----|------|-------------------------------------------------|----------|

| Symbol                  | Parameter                                       | Conditions                                     | Min | Тур  | Max                                             | fF fF mA |

| t <sub>SETTLING</sub>   | Settling time after mux change                  | Analog inputs are muxed HPF = ON               | _   | _    | 2*δ <sub>GROUP</sub> +<br>3*f <sub>ADCD_S</sub> | _        |

|                         |                                                 | HPF = OFF                                      | _   | _    | 2*δ <sub>GROUP</sub> +<br>2*f <sub>ADCD_S</sub> |          |

| t <sub>ODRECOVERY</sub> | Overdrive recovery time                         | After input comes within range from saturation | _   | _    | 2*δ <sub>GROUP</sub> + f <sub>ADCD_S</sub>      | _        |

|                         |                                                 | HPF = ON                                       |     |      |                                                 |          |

|                         |                                                 | HPF = OFF                                      | _   | _    | 2*δ <sub>GROUP</sub>                            |          |

| C <sub>S_D</sub>        | SDADC sampling                                  | GAIN = 1, 2, 4, 8                              | _   | _    | 75*GAIN                                         | fF       |

|                         | capacitance after sampling switch <sup>16</sup> | GAIN = 16                                      | _   | _    | 600                                             | fF       |

| I <sub>BIAS</sub>       | Bias consumption                                | At least one SDADC enabled                     | _   | _    | 3.5                                             | mA       |

| I <sub>ADV_D</sub>      | SDADC supply consumption                        | Per SDADC enabled                              | _   | _    | 4.325                                           | mA       |

| I <sub>ADR_D</sub>      | SDADC reference current consumption             | Per SDADC enabled                              | _   | _    | 20                                              | μА       |

- 1. For input voltage above the maximum and below the clamp voltage of the input pad, there is no latch-up concern, and the signal will only be "clipped."

- 2. VINP is the input voltage applied to the positive terminal of the SDADC

- 3. VINM is the input voltage applied to the negative terminal of the SDADC

- 4. Sampling is generated internally f<sub>SAMPLING</sub> = f<sub>ADCD M</sub>/2

- 5. For Gain = 16, SDADC resolution is 15 bit.

- 6. Calibration of gain is possible when gain = 1. Offset Calibration should be done with respect to  $0.5^*V_{RH\_SD}$  for differential mode and single ended mode with negative input =  $0.5^*V_{RH\_SD}$ . Offset Calibration should be done with respect to 0 for single ended mode with negative input = 0. Both Offset and Gain Calibration is guaranteed for +/-5% variation of  $V_{RH\_SD}$ , +/-10% variation of  $V_{DDA\_SD}$ , +/-50 C temperature variation.

- 7. Offset and gain error due to temperature drift can occur in either direction (+/-) for each of the SDADCs on the device.

- 8. SDADC is functional in the range 3.6 V < V<sub>DDA\_SD</sub> < 4.0 V: SNR parameter degrades by 3 dB. SDADC is functional in the range 3.0 V < V<sub>RH\_SD</sub> < 4.0 V: SNR parameter degrades by 9 dB.

- 9. SNR values guaranteed only if external noise on the ADC input pin is attenuated by the required SNR value in the frequency range of f<sub>ADCD\_M</sub> f<sub>ADCD\_S</sub> to f<sub>ADCD\_M</sub> + f<sub>ADCD\_S</sub>, where f<sub>ADCD\_M</sub> is the input sampling frequency and f<sub>ADCD\_S</sub> is the output sample frequency. A proper external input filter should be used to remove any interfering signals in this frequency range.

- 10. Input impedance in differential mode  $Z_{IN} = Z_{DIFF}$

- 11. Input impedance given at  $f_{ADCD\_M} = 16$  MHz. Impedance is inversely proportional to SDADC clock frequency.  $Z_{DIFF} = (f_{ADCD\_M}) * Z_{DIFF} = (16 \text{ MHz} / f_{ADCD\_M}) * Z_{CM}$ .

- 12. Input impedance in single-ended mode  $Z_{IN} = (2 * Z_{DIFF} * Z_{CM}) / (Z_{DIFF} + Z_{CM})$

- 13. V<sub>INTCM</sub> is the Common Mode input reference voltage for the SDADC. It has a nominal value of (V<sub>RH SD</sub> V<sub>RL SD</sub>) / 2.

- 14. The  $\pm 1\%$  passband ripple specification is equivalent to 20 \*  $\log_{10}$  (0.99) = 0.087 dB.

- 15. Propagation of the information from the pin to the register CDR[CDATA] and the flags SFR[DFEF] and SFR[DFFF] is given by the different modules that must be crossed: delta/sigma filters, high pass filter, FIFO module, and clock domain synchronizers. The time elapsed between data availability at the pin and internal SDADC module registers is given by the following formula, where f<sub>ADCD\_S</sub> is the frequency of the sampling clock, f<sub>ADCD\_M</sub> is the frequency of the modulator, and f<sub>FM\_PER\_CLK</sub> is the frequency of the peripheral bridge clock feeds to the SDADC module:

REGISTER LATENCY =  $t_{LATENCY} + 0.5/f_{ADCD\_S} + 2 (\sim +1)/f_{ADCD\_M} + 2(\sim +1)f_{FM\_PER\_CLK}$

The (~+1) symbol refers to the number of clock cycles uncertainty (from 0 to 1 clock cycle) to be added due to resynchronization of the signal during clock domain crossing.

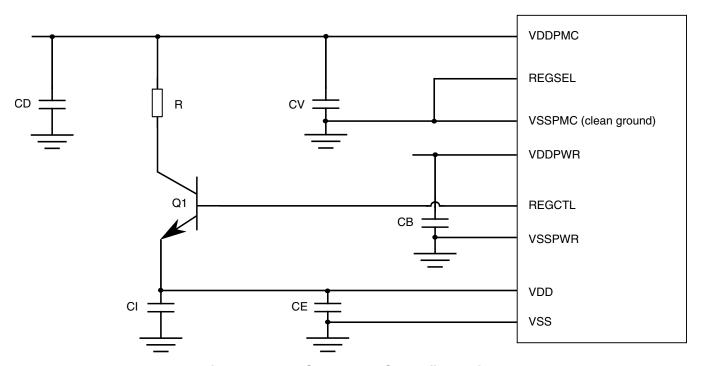

The following table shows the recommended components to be used in LDO regulation mode.

| Part name | Part type | Nominal               | Description                                                                                      |

|-----------|-----------|-----------------------|--------------------------------------------------------------------------------------------------|

| Q1        | NPN BJT   | h <sub>FE</sub> = 400 | NJD2873: ON Semiconductor LDO voltage regulator controller (VRC)                                 |

| CI        | Capacitor | 4.7 μF - 20 V         | Ceramic capacitor, total ESR < 70 mΩ                                                             |

| CE        | Capacitor | 0.047–0.049 μF - 7 V  | Ceramic—one capacitor for each V <sub>DD</sub> pin                                               |

| CV        | Capacitor | 22 μF - 20 V          | Ceramic V <sub>DDPMC</sub> (optional 0.1 μF)                                                     |

| CD        | Capacitor | 22 μF - 20 V          | Ceramic supply decoupling capacitor, ESR < 50 m $\Omega$ (as close as possible to NPN collector) |

| СВ        | Capacitor | 0.1 μF - 7 V          | Ceramic V <sub>DDPWR</sub>                                                                       |

| R         | Resistor  | Application specific  | Optional; reduces thermal loading on the NPN with high V <sub>DDPMC</sub> levels                 |

Table 25. Recommended operating characteristics

The following diagram shows the LDO configuration connection.

Figure 12. VRC 1.2 V LDO configuration

# 3.11.1.2 SMPS mode recommended external components and characteristics

The following table shows the recommended components to be used in SMPS regulation mode.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 9, 06/2016.

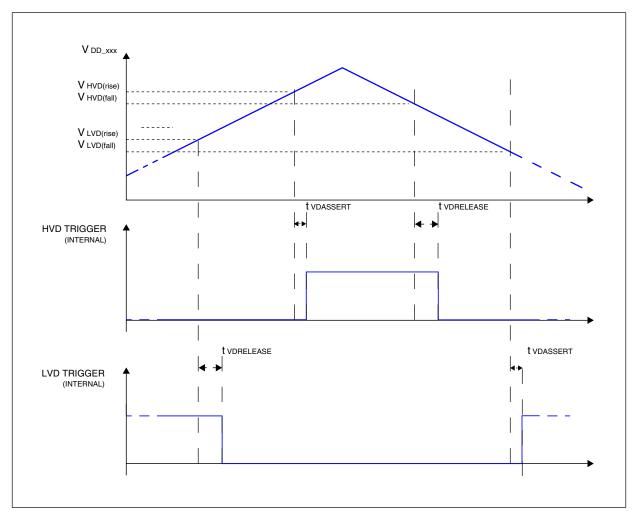

Figure 15. Voltage monitor threshold definition

Table 29. Voltage monitor electrical characteristics 1, 2

|                       |                                     |                              | Co           | nfigura      | tion       |      | Value |      |      |

|-----------------------|-------------------------------------|------------------------------|--------------|--------------|------------|------|-------|------|------|

| Symbol                | Parameter                           | Conditions                   | Trim<br>bits | Mask<br>Opt. | Pow.<br>Up | Min  | Тур   | Max  | Unit |

| POR098_c <sup>3</sup> | LV internal supply power            | Rising voltage (powerup)     | N/A          | No           | Enab.      | 960  | 1010  | 1060 | mV   |

|                       | on reset                            | Falling voltage (power down) |              |              |            | 940  | 990   | 1040 |      |

| LVD_core_hot          | LV internal <sup>4</sup> supply low | Rising voltage (untrimmed)   | 4bit         | No           | Enab.      | 1100 | 1140  | 1183 | mV   |

|                       | voltage monitoring                  | Falling voltage (untrimmed)  |              |              |            | 1080 | 1120  | 1163 |      |

|                       |                                     | Rising voltage (trimmed)     |              |              |            | 1142 | 1165  | 1183 |      |

|                       |                                     | Falling voltage (trimmed)    |              |              |            | 1122 | 1145  | 1163 |      |

| LVD_core_cold         | '''                                 | Rising voltage               | 4bit         | Yes          | Disab.     | 1165 | 1180  | 1198 | mV   |

|                       | voltage monitoring                  | Falling voltage              |              |              |            | 1136 | 1160  | 1178 |      |

| HVD_core              | LV internal cold supply             | Rising voltage               | 4bit         | Yes          | Disab.     | 1338 | 1365  | 1385 | mV   |

|                       | high voltage monitoring             | Falling voltage              |              |              |            | 1318 | 1345  | 1365 |      |

Table continues on the next page...

Table 29. Voltage monitor electrical characteristics<sup>1, 2</sup> (continued)

|                        |                                                  |                              | Co           | nfigura      | tion       |      | Value |      |      |

|------------------------|--------------------------------------------------|------------------------------|--------------|--------------|------------|------|-------|------|------|

| Symbol                 | Parameter                                        | Conditions                   | Trim<br>bits | Mask<br>Opt. | Pow.<br>Up | Min  | Тур   | Max  | Unit |

| POR_HV                 | HV V <sub>DDPMC</sub> supply power               | Rising voltage (powerup)     | N/A          | No           | Enab.      | 2444 | 2600  | 2756 | mV   |

|                        | on reset threshold                               | Falling voltage (power down) |              |              |            | 2424 | 2580  | 2736 |      |

| LVD_HV                 | HV internal V <sub>DDPMC</sub> supply            | Rising voltage (untrimmed)   | 4bit         | No           | Enab.      | 2935 | 3023  | 3112 | mV   |

|                        | low voltage monitoring                           | Falling voltage (untrimmed)  |              |              |            | 2922 | 3010  | 3099 |      |

|                        |                                                  | Rising voltage (trimmed)     |              |              |            | 2946 | 3010  | 3066 |      |

|                        |                                                  | Falling voltage (trimmed)    |              |              |            | 2934 | 2998  | 3044 |      |

| HVD_HV                 | HV internal V <sub>DDPMC</sub> supply            | Rising voltage               | 4bit         | Yes          | Disab.     | 5696 | 5860  | 5968 | mV   |

|                        | high voltage monitoring                          | Falling voltage              |              |              |            | 5666 | 5830  | 5938 |      |

| LVD_FLASH              | FLASH supply low voltage                         | Rising voltage (untrimmed)   | 4bit         | No           | Enab.      | 2935 | 3023  | 3112 | mV   |

|                        | monitoring <sup>6</sup>                          | Falling voltage (untrimmed)  |              |              |            | 2922 | 3010  | 3099 |      |

|                        |                                                  | Rising voltage (trimmed)     |              |              |            | 2956 | 3010  | 3053 |      |

|                        |                                                  | Falling voltage (trimmed)    |              |              |            | 2944 | 2998  | 3041 |      |

| HVD_FLASH              | FLASH supply high                                | Rising voltage               | 4bit         | Yes          | Disab.     | 3456 | 3530  | 3584 | mV   |

|                        | voltage monitoring <sup>6</sup>                  | Falling voltage              |              |              |            | 3426 | 3500  | 3554 |      |

| LVD_IO                 | Main I/O V <sub>DDEH1</sub> supply               | Rising voltage (untrimmed)   | 4bit         | No           | Enab.      | 3250 | 3350  | 3488 | mV   |

|                        | low voltage monitoring                           | Falling voltage (untrimmed)  |              |              |            | 3220 | 3320  | 3458 |      |

|                        |                                                  | Rising voltage (trimmed)     |              |              |            | 3347 | 3420  | 3468 |      |

|                        |                                                  | Falling voltage (trimmed)    |              |              |            | 3317 | 3390  | 3438 |      |

| t <sub>VDASSERT</sub>  | Voltage detector threshold crossing assertion    | _                            | _            | _            | _          | 0.1  | _     | 2.0  | μs   |

| t <sub>VDRELEASE</sub> | Voltage detector threshold crossing de-assertion | _                            | _            | _            | _          | 5    | _     | 20   | μs   |

- LVD is released after t<sub>VDRSLEASE</sub> temporization when upper threshold is crossed; LVD is asserted t<sub>VDASSERT</sub> after detection when lower threshold is crossed.

- HVD is released after t<sub>VDRELEASE</sub> temporization when lower threshold is crossed; HVD is asserted t<sub>VDASSERT</sub> after detection when upper threshold is crossed.

- 3. POR098\_c threshold is an untrimmed value, before the completion of the power-up sequence. All other LVD/HVD thresholds are provided after trimming.

- 4. LV internal supply levels are measured on device internal supply grid after internal voltage drop.

- 5. LV external supply levels are measured on the die side of the package bond wire after package voltage drop.

- 6. V<sub>DDFLA</sub> range is guaranteed when internal flash memory regulator is used.

## 3.11.4 Power sequencing requirements

Requirements for power sequencing include the following.

#### NOTE

In these descriptions, *star route layout* means a track split as close as possible to the power supply source. Each of the split tracks is routed individually to the intended end connection.

- 1. For both LDO mode and SMPS mode, V<sub>DDPMC</sub> and V<sub>DDPWR</sub> must be connected together (shorted) to ensure aligned voltage ramping up/down. In addition:

- For SMPS mode, a star route layout of the power track is required to minimize mutual noise. If SMPS mode is not used, the star route layout is not required.

V<sub>DDPWR</sub> is the supply pin for the SMPS circuitry.

- For 3.3 V operation,  $V_{DDFLA}$  must also be star routed and shorted to  $V_{DDPWR}$  and  $V_{DDPMC}$ . This triple connection is required because 3.3 V does not guarantee correct functionality of the internal  $V_{DDFLA}$  regulator. Consequently,  $V_{DDFLA}$  is supplied externally.

- 2. V<sub>DDA MISC</sub>: IRC operation is required to provide the clock for chip startup.

- The V<sub>DDPMC</sub>, V<sub>DD</sub>, and V<sub>DDEH1</sub> (reset pin pad segment) supplies are monitored.

They hold IRC until all of them reach operational voltage. In other words,

V<sub>DDA\_MISC</sub> must reach its specified minimum operating voltage before or at the same time that all of these monitored voltages reach their respective specified minimum voltages.

- An alternative is to connect the same supply voltage to both  $V_{DDEH1}$  and  $V_{DDA\_MISC}$ . This alternative approach requires a star route layout to minimize mutual noise.

- 3. Multiple  $V_{DDEx}$  supplies can be powered up in any order.

- During any time when  $V_{DD}$  is powered up but  $V_{DDEx}$  is not yet powered up: pad outputs are unpowered.

- During any time when V<sub>DDEx</sub> is powered up before all other supplies: all pad output buffers are tristated.

- 4. Ramp up V<sub>DDA EO</sub> before V<sub>DD</sub>. Otherwise, a reset might occur.

- 5. When the device is powering down while using the internal SMPS regulator, V<sub>DDPMC</sub> and V<sub>DDPWR</sub> supplies must ramp down through the voltage range from 2.5 V to 1.5 V in less than 1 second. Slower ramp-down times might result in reduced lifetime reliability of the device.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 9, 06/2016.

#### 3.12 Flash memory specifications

# 3.12.1 Flash memory program and erase specifications NOTE

All timing, voltage, and current numbers specified in this section are defined for a single embedded flash memory within an SoC, and represent average currents for given supplies and operations.

Table 30 shows the estimated Program/Erase times.

Table 30. Flash memory program and erase specifications

| Symbol               | Characteristic <sup>1</sup>        | Typ <sup>2</sup> |                               | ctory<br>nming <sup>3, 4</sup>  | Field Update                           |                   |                     | Unit |

|----------------------|------------------------------------|------------------|-------------------------------|---------------------------------|----------------------------------------|-------------------|---------------------|------|

|                      |                                    |                  | Initial<br>Max                | Initial<br>Max, Full<br>Temp    | Typical<br>End of<br>Life <sup>5</sup> | Lifeti            | me Max <sup>6</sup> |      |

|                      |                                    |                  | 20°C ≤T <sub>A</sub><br>≤30°C | -40°C ≤T <sub>J</sub><br>≤150°C | -40°C ≤T <sub>J</sub><br>≤150°C        | ≤ 1,000<br>cycles | ≤ 250,000 cycles    |      |

| t <sub>dwpgm</sub>   | Doubleword (64 bits) program time  | 43               | 100                           | 150                             | 55                                     | 500               |                     | μs   |

| t <sub>ppgm</sub>    | Page (256 bits) program time       | 73               | 200                           | 300                             | 108                                    | 500               |                     | μs   |

| t <sub>qppgn</sub>   | Quad-page (1024 bits) program time | 268              | 800                           | 1,200                           | 396                                    | 2,000             |                     | μs   |

| t <sub>16kers</sub>  | 16 KB Block erase time             | 168              | 290                           | 320                             | 250                                    | 1,000             |                     | ms   |

| t <sub>16kpgn</sub>  | 16 KB Block program time           | 34               | 45                            | 50                              | 40                                     | 1,000             |                     | ms   |

| t <sub>32kers</sub>  | 32 KB Block erase time             | 217              | 360                           | 390                             | 310                                    | 1,200             |                     | ms   |

| t <sub>32kpgm</sub>  | 32 KB Block program time           | 69               | 100                           | 110                             | 90                                     | 1,200             |                     | ms   |

| t <sub>64kers</sub>  | 64 KB Block erase time             | 315              | 490                           | 590                             | 420                                    | 1,600             |                     | ms   |

| t <sub>64kpgm</sub>  | 64 KB Block program time           | 138              | 180                           | 210                             | 170                                    | 1,600             |                     | ms   |

| t <sub>256kers</sub> | 256 KB Block erase time            | 884              | 1,520                         | 2,030                           | 1,080                                  | 4,000             | _                   | ms   |

| t <sub>256kpgm</sub> | 256 KB Block program time          | 552              | 720                           | 880                             | 650                                    | 4,000             | _                   | ms   |

- 1. Program times are actual hardware programming times and do not include software overhead. Block program times assume quad-page programming.

- 2. Typical program and erase times represent the median performance and assume nominal supply values and operation at 25 °C. Typical program and erase times may be used for throughput calculations.

- 3. Conditions: ≤ 150 cycles, nominal voltage.

- 4. Plant Programing times provide guidance for timeout limits used in the factory.

- 5. Typical End of Life program and erase times represent the median performance and assume nominal supply values. Typical End of Life program and erase values may be used for throughput calculations.

- 6. Conditions:  $-40^{\circ}\text{C} \le T_{\text{J}} \le 150^{\circ}\text{C}$ , full spec voltage.

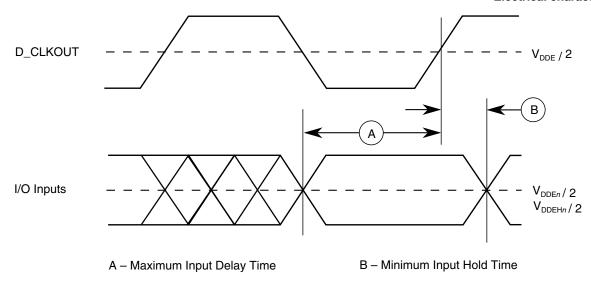

Figure 17. Generic input setup/hold timing

## 3.13.2 Reset and configuration pin timing

Table 35. Reset and configuration pin timing<sup>1</sup>

| Spec | Characteristic                                     | Symbol            | Min | Max | Unit                          |

|------|----------------------------------------------------|-------------------|-----|-----|-------------------------------|

| 1    | RESET Pulse Width                                  | t <sub>RPW</sub>  | 10  | _   | t <sub>cyc</sub> <sup>2</sup> |

| 2    | RESET Glitch Detect Pulse Width                    | t <sub>GPW</sub>  | 2   | _   | t <sub>cyc</sub> <sup>2</sup> |

| 3    | PLLCFG, BOOTCFG, WKPCFG Setup Time to RSTOUT Valid | t <sub>RCSU</sub> | 10  | _   | t <sub>cyc</sub> <sup>2</sup> |

| 4    | PLLCFG, BOOTCFG, WKPCFG Hold Time to RSTOUT Valid  | t <sub>RCH</sub>  | 0   | _   | t <sub>cyc</sub> <sup>2</sup> |

- 1. Reset timing specified at:  $V_{DDEH}$  = 3.0 V to 5.25 V,  $V_{DD}$  = 1.08 V to 1.32 V, TA = TL to TH.

- 2. For further information on  $t_{cvc}$ , see Table 3.

# RESET 1 RESTOUT

Figure 18. Reset and configuration pin timing

#### 3.13.3 IEEE 1149.1 interface timing

PLLCFG BOOTCFG WKPCFG

Table 36. JTAG pin AC electrical characteristics<sup>1</sup>

| #  | Symbol                                | Chavastaviatia                                         | Va  | lue              | Unit |

|----|---------------------------------------|--------------------------------------------------------|-----|------------------|------|

| #  | Symbol                                | Characteristic                                         | Min | Max              | Unit |

| 1  | t <sub>JCYC</sub>                     | TCK cycle time                                         | 100 | _                | ns   |

| 2  | t <sub>JDC</sub>                      | TCK clock pulse width                                  | 40  | 60               | %    |

| 3  | t <sub>TCKRISE</sub>                  | TCK rise and fall times (40%–70%)                      | _   | 3                | ns   |

| 4  | t <sub>TMSS</sub> , t <sub>TDIS</sub> | TMS, TDI data setup time                               | 5   | _                | ns   |

| 5  | t <sub>TMSH</sub> , t <sub>TDIH</sub> | TMS, TDI data hold time                                | 5   | _                | ns   |

| 6  | t <sub>TDOV</sub>                     | TCK low to TDO data valid                              | _   | 16 <sup>2</sup>  | ns   |

| 7  | t <sub>TDOI</sub>                     | TCK low to TDO data invalid                            | 0   | _                | ns   |

| 8  | t <sub>TDOHZ</sub>                    | TCK low to TDO high impedance                          | _   | 15               | ns   |

| 9  | t <sub>JCMPPW</sub>                   | JCOMP assertion time                                   | 100 | _                | ns   |

| 10 | t <sub>JCMPS</sub>                    | JCOMP setup time to TCK low                            | 40  | _                | ns   |

| 11 | t <sub>BSDV</sub>                     | TCK falling edge to output valid                       | _   | 600 <sup>3</sup> | ns   |

| 12 | t <sub>BSDVZ</sub>                    | TCK falling edge to output valid out of high impedance | _   | 600              | ns   |

| 13 | t <sub>BSDHZ</sub>                    | TCK falling edge to output high impedance              | _   | 600              | ns   |

| 14 | t <sub>BSDST</sub>                    | Boundary scan input valid to TCK rising edge           | 15  | _                | ns   |

| 15 | t <sub>BSDHT</sub>                    | TCK rising edge to boundary scan input invalid         | 15  | _                | ns   |

- 1. These specifications apply to JTAG boundary scan only. See Table 37 for functional specifications.

- 2. Timing includes TCK pad delay, clock tree delay, logic delay and TDO output pad delay.

- 3. Applies to all pins, limited by pad slew rate. Refer to I/O delay and transition specification and add 20 ns for JTAG delay.

#### **Electrical characteristics**

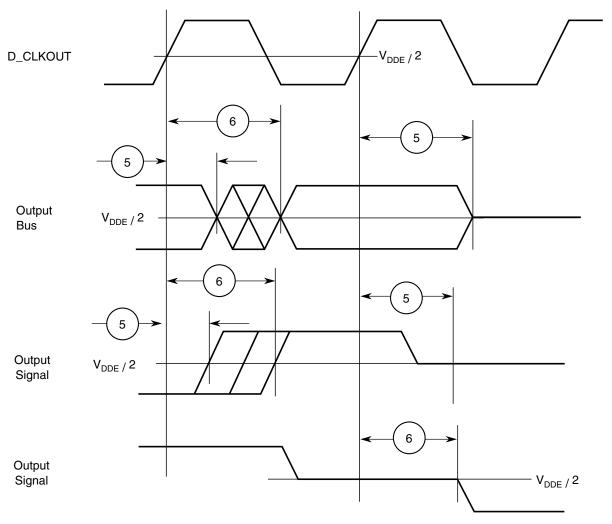

Figure 26. Synchronous output timing

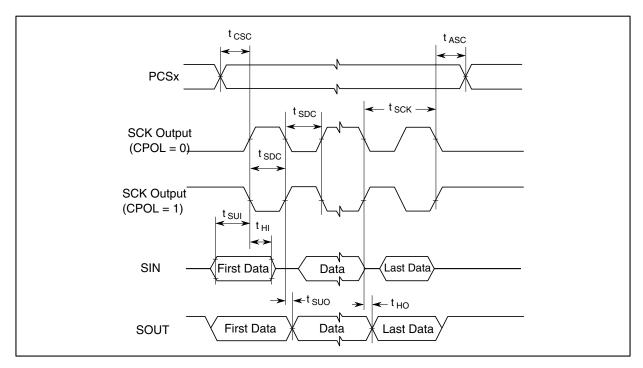

Table 43. DSPI CMOS master classic timing (full duplex and output only) – MTFE = 0, CPHA =  $0 \text{ or } 1^1$  (continued)

| <u>"</u> [ | Symbol            | Characteristic                              | Condition <sup>2</sup> |                        | Value <sup>3</sup>              |                         | Unit |

|------------|-------------------|---------------------------------------------|------------------------|------------------------|---------------------------------|-------------------------|------|

| #          |                   |                                             | Pad drive <sup>4</sup> | Load (C <sub>L</sub> ) | Min                             | Max                     | Unit |

| 3          | t <sub>ASC</sub>  | After SCK delay                             | PCR[SRC]=11b           | PCS: 0 pF              | $(M^7 \times t_{SYS}, ^6) - 35$ | _                       | ns   |

|            |                   |                                             |                        | SCK: 50 pF             |                                 |                         |      |

|            |                   |                                             | PCR[SRC]=10b           | PCS: 0 pF              | $(M^7 \times t_{SYS}, ^6) - 35$ | _                       | 1    |

|            |                   |                                             |                        | SCK: 50 pF             |                                 |                         |      |

|            |                   |                                             | PCR[SRC]=01b           | PCS: 0 pF              | $(M^7 \times t_{SYS}, ^6) - 35$ | _                       | 1    |

|            |                   |                                             |                        | SCK: 50 pF             |                                 |                         |      |

|            |                   |                                             | PCS: PCR[SRC]=01b      | PCS: 0 pF              | $(M^7 \times t_{SYS}, ^6) - 35$ | _                       | 1    |

|            |                   |                                             | SCK: PCR[SRC]=10b      | SCK: 50 pF             |                                 |                         |      |

| 4          | t <sub>SDC</sub>  | SCK duty cycle <sup>8</sup>                 | PCR[SRC]=11b           | 0 pF                   | 1/2t <sub>SCK</sub> – 2         | 1/2t <sub>SCK</sub> + 2 | ns   |

|            |                   |                                             | PCR[SRC]=10b           | 0 pF                   | 1/2t <sub>SCK</sub> – 2         | 1/2t <sub>SCK</sub> + 2 | 1    |

|            |                   |                                             | PCR[SRC]=01b           | 0 pF                   | 1/2t <sub>SCK</sub> – 5         | 1/2t <sub>SCK</sub> + 5 |      |

|            |                   | •                                           | PCS strob              | e timing               |                                 |                         |      |

| 5          | t <sub>PCSC</sub> | PCSx to PCSS time <sup>9</sup>              | PCR[SRC]=10b           | 25 pF                  | 13.0                            | _                       | ns   |

| 6          | t <sub>PASC</sub> | PCSS to PCSx time <sup>9</sup>              | PCR[SRC]=10b           | 25 pF                  | 13.0                            | _                       | ns   |

|            |                   | 1                                           | SIN setu               | p time                 |                                 |                         |      |

| 7          | t <sub>SUI</sub>  | SIN setup time to SCK <sup>10</sup>         | PCR[SRC]=11b           | 25 pF                  | 29.0                            | <u>—</u>                | ns   |

|            |                   |                                             | PCR[SRC]=10b           | 50 pF                  | 31.0                            | _                       |      |

|            |                   |                                             | PCR[SRC]=01b           | 50 pF                  | 62.0                            | _                       |      |

|            |                   | 1                                           | SIN hole               | d time                 |                                 |                         |      |

| 8          | t <sub>HI</sub>   | SIN hold time from SCK <sup>10</sup>        | PCR[SRC]=11b           | 0 pF                   | -1.0                            | _                       | ns   |

|            |                   |                                             | PCR[SRC]=10b           | 0 pF                   | -1.0                            | _                       |      |

|            |                   |                                             | PCR[SRC]=01b           | 0 pF                   | -1.0                            | _                       |      |

|            |                   | •                                           | SOUT data valid tim    | e (after SCK ed        | dge)                            |                         |      |

| 9          | t <sub>SUO</sub>  | SOUT data valid time from SCK <sup>11</sup> | PCR[SRC]=11b           | 25 pF                  | _                               | 7.0                     | ns   |

|            |                   |                                             | PCR[SRC]=10b           | 50 pF                  | _                               | 8.0                     |      |

|            |                   |                                             | PCR[SRC]=01b           | 50 pF                  | _                               | 18.0                    |      |

|            |                   |                                             | SOUT data hold time    | e (after SCK ed        | lge)                            |                         |      |

| 10         | t <sub>HO</sub>   | SOUT data hold time after SCK <sup>11</sup> | PCR[SRC]=11b           | 25 pF                  | -9.0                            | _                       | ns   |

|            |                   |                                             | PCR[SRC]=10b           | 50 pF                  | -10.0                           | _                       |      |

|            |                   |                                             | PCR[SRC]=01b           | 50 pF                  | -21.0                           | _                       | 7    |

- 1. All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

- 2. When a characteristic involves two signals, the pad drive and load conditions apply to each signal's pad, unless specified otherwise

- 3. All timing values for output signals in this table are measured to 50% of the output voltage.

- 4. Pad drive is defined as the PCR[SRC] field setting in the SIU. Timing is guaranteed to same drive capabilities for all signals; mixing of pad drives may reduce operating speeds and may cause incorrect operation.

- 5. N is the number of clock cycles added to time between PCS assertion and SCK assertion and is software programmable using DSPI\_CTARx[PSSCK] and DSPI\_CTARx[CSSCK]. The minimum value is 2 cycles unless TSB mode or Continuous

#### **Electrical characteristics**

- SCK clock mode is selected, in which case, N is automatically set to 0 clock cycles (PCS and SCK are driven by the same edge of DSPI\_CLKn).

- t<sub>SYS</sub> is the period of DSPI\_CLKn clock, the input clock to the DSPI module. Maximum frequency is 100 MHz (min t<sub>SYS</sub> = 10 ns).

- 7. M is the number of clock cycles added to time between SCK negation and PCS negation and is software programmable using DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC]. The minimum value is 2 cycles unless TSB mode or Continuous SCK clock mode is selected, in which case, M is automatically set to 0 clock cycles (PCS and SCK are driven by the same edge of DSPI\_CLKn).

- 8. t<sub>SDC</sub> is only valid for even divide ratios. For odd divide ratios the fundamental duty cycle is not 50:50. For these odd divide ratios cases, the absolute spec number is applied as jitter/uncertainty to the nominal high time and low time.

- 9. PCSx and PCSS using same pad configuration.

- 10. Input timing assumes an input slew rate of 1 ns (10% 90%) and uses TTL / Automotive voltage thresholds.

- 11. SOUT Data Valid and Data hold are independent of load capacitance if SCK and SOUT load capacitances are the same value.

Figure 32. DSPI CMOS master mode – classic timing, CPHA = 0

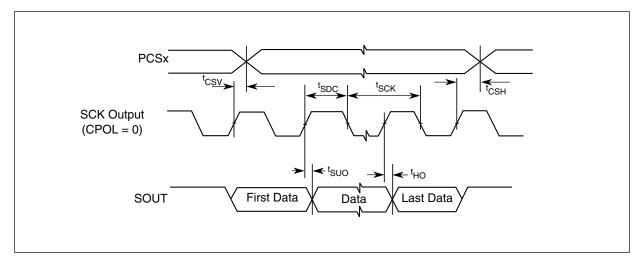

Table 47. DSPI CMOS master timing – output only – timed serial bus mode TSB = 1 or ITSB = 1, CPOL = 0 or 1, continuous SCK clock  $^{1,2}$  (continued)

| #  | Symbol           | Characteristic                                          | Condition <sup>3</sup>   |                        | Value <sup>4</sup>      |                         | Unit |

|----|------------------|---------------------------------------------------------|--------------------------|------------------------|-------------------------|-------------------------|------|

| "  |                  |                                                         | Pad drive <sup>5</sup>   | Load (C <sub>L</sub> ) | Min                     | Max                     |      |

| 3  | t <sub>CSH</sub> | PCS hold after SCK <sup>6</sup>                         | PCR[SRC]=11b             | PCS: 0 pF              | -14                     | _                       | ns   |

|    |                  |                                                         |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                                         | PCR[SRC]=10b             | PCS: 0 pF              | -14                     | _                       | ns   |

|    |                  |                                                         |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                                         | PCR[SRC]=01b             | PCS: 0 pF              | -33                     | _                       | ns   |

|    |                  |                                                         |                          | SCK: 50 pF             |                         |                         |      |

|    |                  |                                                         | PCS: PCR[SRC]=01b        | PCS: 0 pF              | -35                     | _                       | ns   |

|    |                  |                                                         | SCK: PCR[SRC]=10b        | SCK: 50 pF             |                         |                         |      |

| 4  | t <sub>SDC</sub> | SCK duty cycle <sup>7</sup>                             | PCR[SRC]=11b             | 0 pF                   | 1/2t <sub>SCK</sub> - 2 | 1/2t <sub>SCK</sub> + 2 | ns   |

|    |                  |                                                         | PCR[SRC]=10b             | 0 pF                   | 1/2t <sub>SCK</sub> – 2 | 1/2t <sub>SCK</sub> + 2 | ns   |

|    |                  |                                                         | PCR[SRC]=01b             | 0 pF                   | 1/2t <sub>SCK</sub> - 5 | 1/2t <sub>SCK</sub> + 5 | ns   |

|    |                  |                                                         | SOUT data valid time (af | ter SCK edge)          |                         |                         |      |

| 9  | t <sub>suo</sub> | from SCK                                                | PCR[SRC]=11b             | 25 pF                  | _                       | 7.0                     | ns   |

|    |                  |                                                         | PCR[SRC]=10b             | 50 pF                  | _                       | 8.0                     | ns   |

|    |                  | CPHA = 1 <sup>8</sup>                                   | PCR[SRC]=01b             | 50 pF                  | _                       | 18.0                    | ns   |

|    |                  |                                                         | SOUT data hold time (aft | er SCK edge)           |                         |                         |      |

| 10 | t <sub>HO</sub>  | t <sub>HO</sub> SOUT data hold time after SCK CPHA = 18 | PCR[SRC]=11b             | 25 pF                  | -9.0                    | _                       | ns   |

|    |                  |                                                         | PCR[SRC]=10b             | 50 pF                  | -10.0                   | _                       | ns   |

|    |                  |                                                         | PCR[SRC]=01b             | 50 pF                  | -21.0                   | _                       | ns   |

- 1. TSB = 1 or ITSB = 1 automatically selects MTFE = 1 and CPHA = 1.

- 2. All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

- 3. When a characteristic involves two signals, the pad drive and load conditions apply to each signal's pad, unless specified otherwise.

- 4. All timing values for output signals in this table are measured to 50% of the output voltage.

- 5. Pad drive is defined as the PCR[SRC] field setting in the SIU. Timing is guaranteed to same drive capabilities for all signals; mixing of pad drives may reduce operating speeds and may cause incorrect operation.

- 6. With TSB mode or Continuous SCK clock mode selected, PCS and SCK are driven by the same edge of DSPI\_CLKn. This timing value is due to pad delays and signal propagation delays.

- 7. t<sub>SDC</sub> is only valid for even divide ratios. For odd divide ratios the fundamental duty cycle is not 50:50. For these odd divide ratios cases, the absolute spec number is applied as jitter/uncertainty to the nominal high time and low time.

- 8. SOUT Data Valid and Data hold are independent of load capacitance if SCK and SOUT load capacitances are the same value.

#### **Electrical characteristics**

Figure 40. DSPI LVDS and CMOS master timing – output only – modified transfer format MTFE = 1, CHPA = 1

#### 3.13.10 **FEC** timing

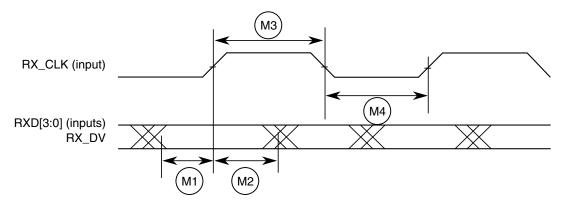

#### 3.13.10.1 MII receive signal timing (RXD[3:0], RX\_DV, and RX\_CLK)

The receiver functions correctly up to a RX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. The system clock frequency must be at least equal to or greater than the RX\_CLK frequency.

Table 48. MII receive signal timing<sup>1</sup>

| Symbol | Characteristic                  | Value |     | Unit          |  |

|--------|---------------------------------|-------|-----|---------------|--|

| Symbol | Characteristic                  | Min   | Max | onit          |  |

| M1     | RXD[3:0], RX_DV to RX_CLK setup | 5     | _   | ns            |  |

| M2     | RX_CLK to RXD[3:0], RX_DV hold  | 5     | _   | ns            |  |

| M3     | RX_CLK pulse width high         | 35%   | 65% | RX_CLK period |  |

| M4     | RX_CLK pulse width low          | 35%   | 65% | RX_CLK period |  |

1. All timing specifications valid to the pad input levels defined in I/O pad current specifications.

79

Figure 41. MII receive signal timing diagram

#### 3.13.10.2 MII transmit signal timing (TXD[3:0], TX\_EN, and TX\_CLK)

The transmitter functions correctly up to a TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. The system clock frequency must be at least equal to or greater than the TX\_CLK frequency.

The transmit outputs (TXD[3:0], TX\_EN) can be programmed to transition from either the rising or falling edge of TX\_CLK, and the timing is the same in either case. This options allows the use of noncompliant MII PHYs.

Refer to the *MPC5777C Microcontroller Reference Manual's* Fast Ethernet Controller (FEC) chapter for details of this option and how to enable it.

| Table 49. | MII transmit signal timing <sup>1</sup> |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Symbol | Characteristic                    | Value <sup>2</sup> |     | Unit          |  |

|--------|-----------------------------------|--------------------|-----|---------------|--|

| Symbol | Characteristic                    | Min                | Max | Offic         |  |

| M5     | TX_CLK to TXD[3:0], TX_EN invalid | 4.5                | _   | ns            |  |

| M6     | TX_CLK to TXD[3:0], TX_EN valid   | _                  | 25  | ns            |  |

| M7     | TX_CLK pulse width high           | 35%                | 65% | TX_CLK period |  |

| M8     | TX_CLK pulse width low            | 35%                | 65% | TX_CLK period |  |

- 1. All timing specifications valid to the pad input levels defined in I/O pad specifications.

- 2. Output parameters are valid for  $C_L = 25$  pF, where  $C_L$  is the external load to the device. The internal package capacitance is accounted for, and does not need to be subtracted from the 25 pF value.

Package information

$$R_{\theta \text{JA}} = R_{\theta \text{JC}} + R_{\theta \text{CA}}$$

where:

$R_{\Theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\Theta JC}$  is device related and is not affected by other factors. The thermal environment can be controlled to change the case-to-ambient thermal resistance,  $R_{\Theta CA}$ . For example, change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This description is most useful for packages with heat sinks where 90% of the heat flow is through the case to heat sink to ambient. For most packages, a better model is required.

A more accurate two-resistor thermal model can be constructed from the junction-to-board thermal resistance and the junction-to-case thermal resistance. The junction-to-case thermal resistance describes when using a heat sink or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. This model can be used to generate simple estimations and for computational fluid dynamics (CFD) thermal models. More accurate compact Flotherm models can be generated upon request.

To determine the junction temperature of the device in the application on a prototype board, use the thermal characterization parameter ( $\Psi_{JT}$ ) to determine the junction temperature by measuring the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} x P_D)$$

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately