# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z7                                                                 |

| Core Size                  | 32-Bit Tri-Core                                                        |

| Speed                      | 264MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, FlexCANbus, LINbus, SCI, SPI                |

| Peripherals                | DMA, LVD, POR, Zipwire                                                 |

| Number of I/O              | -                                                                      |

| Program Memory Size        | 8MB (8M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 16b Sigma-Delta, eQADC                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 416-BGA                                                                |

| Supplier Device Package    | 416-MAPBGA (27x27)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5777ck3mme3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1** Introduction

## **1.1 Features summary**

On-chip modules available within the family include the following features:

- Three dual issue, 32-bit CPU core complexes (e200z7), two of which run in lockstep

- Power Architecture embedded specification compliance

- Instruction set enhancement allowing variable length encoding (VLE), optional encoding of mixed 16-bit and 32-bit instructions, for code size footprint reduction

- On the two computational cores: Signal processing extension (SPE1.1) instruction support for digital signal processing (DSP)

- Single-precision floating point operations

- On the two computational cores: 16 KB I-Cache and 16 KB D-Cache

- Hardware cache coherency between cores

- 16 hardware semaphores

- 3-channel CRC module

- 8 MB on-chip flash memory

- Supports read during program and erase operations, and multiple blocks allowing EEPROM emulation

- 512 KB on-chip general-purpose SRAM including 64 KB standby RAM

- Two multichannel direct memory access controllers (eDMA)

- 64 channels per eDMA

- Dual core Interrupt Controller (INTC)

- Dual phase-locked loops (PLLs) with stable clock domain for peripherals and frequency modulation (FM) domain for computational shell

- Crossbar Switch architecture for concurrent access to peripherals, flash memory, or RAM from multiple bus masters with End-To-End ECC

- External Bus Interface (EBI) for calibration and application use

- System Integration Unit (SIU)

- Error Injection Module (EIM) and Error Reporting Module (ERM)

- Four protected port output (PPO) pins

- Boot Assist Module (BAM) supports serial bootload via CAN or SCI

- Three second-generation Enhanced Time Processor Units (eTPUs)

- 32 channels per eTPU

- Total of 36 KB code RAM

- Total of 9 KB parameter RAM

| Symbol                              | Parameter                                                   | Conditions <sup>1</sup>                                 | Va   | lue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Unit  |  |

|-------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Symbol                              | Parameter                                                   | Conditions                                              | Min  | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Unit  |  |

| Cycle                               | Lifetime power cycles                                       | —                                                       | —    | 1000k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —     |  |

| V <sub>DD</sub>                     | 1.2 V core supply voltage <sup>2, 3, 4</sup>                | —                                                       | -0.3 | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDEHx</sub>                  | I/O supply voltage (medium I/O pads) <sup>5</sup>           | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDEx</sub>                   | I/O supply voltage (fast I/O pads) <sup>5</sup>             | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDPMC</sub>                  | Power Management Controller supply voltage <sup>5</sup>     | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDFLA</sub>                  | Decoupling pin for flash regulator <sup>6</sup>             | —                                                       | -0.3 | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>STBY</sub>                   | RAM standby supply voltage <sup>5</sup>                     | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>SSA_SD</sub>                 | SDADC ground voltage                                        | Reference to V <sub>SS</sub>                            | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{SSA_EQ}$                        | eQADC ground voltage                                        | Reference to V <sub>SS</sub>                            | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDA_EQA/B</sub>              | eQADC supply voltage                                        | Reference to V <sub>SSA_EQ</sub>                        | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDA_SD</sub>                 | SDADC supply voltage                                        | Reference to V <sub>SSA_SD</sub>                        | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>RL_SD</sub>                  | SDADC ground reference                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{RL}_{EQ}$                       | eQADC ground reference                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{RH}_{EQ}$                       | eQADC alternate reference                                   | Reference to V <sub>RL_EQ</sub>                         | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>RH_SD</sub>                  | SDADC alternate reference                                   | Reference to V <sub>RL_SD</sub>                         | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>REFBYPC</sub>                | eQADC reference decoupling capacitor pins                   | REFBYPCA25, REFBYPCA75,<br>REFBYPCB25, REFBYPC75        | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDA_MISC</sub>               | TRNG and IRC supply voltage                                 | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>DDPWR</sub>                  | SMPS driver supply pin                                      | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>SSPWR</sub>                  | SMPS driver supply pin                                      | Reference to V <sub>SS</sub>                            | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{SS} - V_{SSA_EQ}$               | V <sub>SSA_EQ</sub> differential voltage                    | —                                                       | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{SS} - V_{SSA\_SD}$              | V <sub>SSA_SD</sub> differential voltage                    | —                                                       | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{SS} - V_{RL_{EQ}}$              | V <sub>RL_EQ</sub> differential voltage                     | —                                                       | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| $V_{SS} - V_{RL_{SD}}$              | V <sub>RL_SD</sub> differential voltage                     | —                                                       | -0.3 | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

| V <sub>IN</sub>                     | I/O input voltage range <sup>7</sup>                        | —                                                       | -0.3 | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V     |  |

|                                     |                                                             | Relative to V <sub>DDEx</sub> /V <sub>DDEHx</sub>       | —    | 1000k         1.5         6.0         6.0         6.0         4.5         6.0         0.3         0.3         6.0         0.3         6.0         0.3         6.0         0.3         6.0         0.3         6.0         0.3         6.0         6.0         0.3         6.0         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3         0.3 <td< td=""><td>V</td></td<> | V     |  |

|                                     |                                                             | Relative to V <sub>SS</sub>                             | -0.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V     |  |

| I <sub>INJD</sub>                   | Maximum DC injection current for digital pad                | Per pin, applies to all digital pins                    | -5   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mA    |  |

| I <sub>INJA</sub>                   | Maximum DC injection current for analog pad                 | Per pin, applies to all analog pins                     | -5   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mA    |  |

| I <sub>MAXSEG</sub> <sup>8, 9</sup> | Maximum current per I/O power segment                       | _                                                       | -120 | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mA    |  |

| T <sub>STG</sub>                    | Storage temperature range and non-<br>operating times       | _                                                       | -55  | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | °C    |  |

| STORAGE                             | Maximum storage time, assembled part programmed in ECU      | No supply; storage temperature in range –40 °C to 60 °C | -    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | years |  |

| T <sub>SDR</sub>                    | Maximum solder temperature <sup>10</sup><br>Pb-free package |                                                         | -    | 260                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | °C    |  |

## Table 1. Absolute maximum ratings

Table continues on the next page ...

- 13. For supply voltages between 3.0 V and 4.0 V there will be no guaranteed precision of ADC (accuracy/linearity). ADC will recover to a fully functional state when the voltage rises above 4.0 V.

- 14. Full device lifetime without performance degradation

- 15. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. See the absolute maximum ratings table for maximum input current for reliability requirements.

- 16. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pin is above the supply rail, current will be injected through the clamp diode to the supply rail. For external RC network calculation, assume a typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 17. The sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DDEx</sub>/V<sub>DDEHx</sub> power segment is defined as one or more GPIO pins located between two V<sub>DDEx</sub>/V<sub>DDEHx</sub> supply pins.

- 18. The average current values given in I/O pad current specifications should be used to calculate total I/O segment current.

## 3.5 DC electrical specifications

### NOTE

$I_{DDA\_MISC}$  is the sum of current consumption of IRC,  $I_{TRNG}$ , and  $I_{STBY}$  in the 5 V domain. IRC current is provided in the IRC specifications.

### NOTE

I/O, XOSC, EQADC, SDADC, and Temperature Sensor current specifications are in those components' dedicated sections.

| Symbol              | Parameter                                                                      | Conditions                                           |     | Value |      | Unit |

|---------------------|--------------------------------------------------------------------------------|------------------------------------------------------|-----|-------|------|------|

| Symbol              | Farameter                                                                      | Conditions                                           | Min | Тур   | Max  | Unit |

| I <sub>DD</sub>     | Operating current on the V <sub>DD</sub> core logic supply <sup>1</sup>        | LVD/HVD enabled, $V_{DD}$ = 1.2 V to 1.32 V          | _   | 0.65  | 1.35 | A    |

|                     |                                                                                | LVD/HVD disabled, $V_{DD} = 1.2 \text{ V}$ to 1.38 V | _   | 0.65  | 1.4  |      |

| I <sub>DD_PE</sub>  | Operating current on the V <sub>DD</sub> supply for flash memory program/erase | -                                                    | _   |       | 85   | mA   |

| IDDPMC              | Operating current on the V <sub>DDPMC</sub> supply <sup>2</sup>                | Flash memory read                                    | _   | _     | 40   | mA   |

|                     |                                                                                | Flash memory program/erase                           | _   | _     | 70   |      |

|                     |                                                                                | PMC only                                             |     | _     | 35   |      |

|                     | Operating current on the V <sub>DDPMC</sub> supply                             | Flash memory read                                    |     |       | 10   | mA   |

|                     | (internal core regulator bypassed)                                             | Flash memory program/erase                           | _   | _     | 40   |      |

|                     |                                                                                | PMC only                                             |     | _     | 5    |      |

| IREGCTL             | Core regulator DC current output on V <sub>REGCTL</sub> pin                    | -                                                    | _   | _     | 25   | mA   |

| I <sub>STBY</sub>   | Standby RAM supply current (T <sub>J</sub> = 150°C)                            | 1.08 V                                               | _   | _     | 1140 | μA   |

|                     |                                                                                | 1.25 V to 5.5 V                                      | _   | _     | 1170 |      |

| I <sub>DD_PWR</sub> | Operating current on the V <sub>DDPWR</sub> supply                             | -                                                    | —   | —     | 50   | mA   |

| I <sub>BG_REF</sub> | Bandgap reference current consumption <sup>3</sup>                             |                                                      | _   | —     | 600  | μA   |

| I <sub>TRNG</sub>   | True Random Number Generator current                                           | -                                                    |     | —     | 2.1  | mA   |

#### Table 4. DC electrical specifications

## Table 14. External oscillator (XOSC) electrical specifications (continued)

| Symbol             | Parameter                                                         | Conditions | Va  | Unit |    |

|--------------------|-------------------------------------------------------------------|------------|-----|------|----|

| Symbol             | Falanielei                                                        | Conditions | Min | Max  |    |

| V <sub>EXTAL</sub> | Oscillation amplitude on the EXTAL pin after startup <sup>6</sup> | _          | 0.5 | 1.6  | V  |

| V <sub>HYS</sub>   | Comparator hysteresis                                             | —          | 0.1 | 1.0  | V  |

| I <sub>XTAL</sub>  | XTAL current <sup>6, 7</sup>                                      | —          |     | 14   | mA |

1. This value is determined by the crystal manufacturer and board design.

- 2. Proper PC board layout procedures must be followed to achieve specifications.

- 3. Crystal recovery time is the time for the oscillator to settle to the correct frequency after adjustment of the integrated load capacitor value.

- 4. See crystal manufacturer's specification for recommended load capacitor (C<sub>L</sub>) values. The external oscillator requires external load capacitors when operating in a "low" transconductance range. Account for on-chip stray capacitance (C<sub>S\_EXTAL</sub>/C<sub>S\_XTAL</sub>) and PCB capacitance when selecting a load capacitor value. When operating in a "medium" or "high" transconductance range, the integrated load capacitor value is selected via software to match the crystal manufacturer's specification, while accounting for on-chip and PCB capacitance.

- 5. Select a "low," "medium," or "high" setting using the UTEST Miscellaneous DCF client's XOSC\_LF\_EN and XOSC\_EN\_HIGH fields. "Low" is the setting commonly used for crystals at 8 MHz, "medium" is commonly used for crystals greater than 8 MHz to 20 MHz, and "high" is commonly used for crystals greater than 20 MHz to 40 MHz. However, the user must characterize carefully to determine the best g<sub>m</sub> setting for the intended application because crystal load capacitance, board layout, and other factors affect the g<sub>m</sub> value that is needed. The user may need an additional Rshunt to optimize g<sub>m</sub> depending on the system environment. Use of overtone crystals is not recommended.

- 6. Amplitude on the EXTAL pin after startup is determined by the ALC block (that is, the Automatic Level Control Circuit). The function of the ALC is to provide high drive current during oscillator startup, while reducing current after oscillation to reduce power, distortion, and RFI, and to avoid over-driving the crystal. The operating point of the ALC is dependent on the crystal value and loading conditions.

- I<sub>XTAL</sub> is the oscillator bias current out of the XTAL pin with both EXTAL and XTAL pins grounded. This is the maximum current during startup of the oscillator. The current after oscillation is typically in the 2–3 mA range and is dependent on the load and series resistance of the crystal. Test circuit is shown in Figure 7.

| load_cap_sel[4:0] from DCF record | Load capacitance <sup>1, 2</sup> (pF) |

|-----------------------------------|---------------------------------------|

| 00000                             | 1.8                                   |

| 00001                             | 2.8                                   |

| 00010                             | 3.7                                   |

| 00011                             | 4.6                                   |

| 00100                             | 5.6                                   |

| 00101                             | 6.5                                   |

| 00110                             | 7.4                                   |

| 00111                             | 8.4                                   |

| 01000                             | 9.3                                   |

| 01001                             | 10.2                                  |

| 01010                             | 11.2                                  |

| 01011                             | 12.1                                  |

| 01100                             | 13.0                                  |

| 01101                             | 13.9                                  |

#### Table 15. Selectable load capacitance

Table continues on the next page...

## 3.8.1 Enhanced Queued Analog-to-Digital Converter (eQADC) Table 17. eQADC conversion specifications (operating)

| Cumb al            | Devenueter                                                   | Va               | Value           |                      |  |

|--------------------|--------------------------------------------------------------|------------------|-----------------|----------------------|--|

| Symbol             | Parameter                                                    | Min              | Max             | - Unit               |  |

| f <sub>ADCLK</sub> | ADC Clock (ADCLK) Frequency                                  | 2                | 33              | MHz                  |  |

| CC                 | Conversion Cycles                                            | 2 + 13           | 128 + 15        | ADCLK cycles         |  |

| T <sub>SR</sub>    | Stop Mode Recovery Time <sup>1</sup>                         | 10               | _               | μs                   |  |

| _                  | Resolution <sup>2</sup>                                      | 1.25             | _               | mV                   |  |

| INL                | INL: 16.5 MHz eQADC clock <sup>3</sup>                       | -4               | 4               | LSB <sup>4</sup>     |  |

|                    | INL: 33 MHz eQADC clock <sup>3</sup>                         | -6               | 6               | LSB                  |  |

| DNL                | DNL: 16.5 MHz eQADC clock <sup>3</sup>                       | -3               | 3               | LSB                  |  |

|                    | DNL: 33 MHz eQADC clock <sup>3</sup>                         | -3               | 3               | LSB                  |  |

| OFFNC              | Offset Error without Calibration 0 140                       |                  | 140             | LSB                  |  |

| OFFWC              | Offset Error with Calibration                                | -8               | 8               | LSB                  |  |

| GAINNC             | Full Scale Gain Error without Calibration                    | -150             | 0               | LSB                  |  |

| GAINWC             | Full Scale Gain Error with Calibration                       | -8               | 8               | LSB                  |  |

| I <sub>INJ</sub>   | Disruptive Input Injection Current <sup>5, 6, 7, 8</sup>     | -3               | 3               | mA                   |  |

| E <sub>INJ</sub>   | Incremental Error due to injection current <sup>9, 10</sup>  | —                | +4              | Counts               |  |

| TUE                | TUE value <sup>11, 12</sup> (with calibration)               | _                | ±8              | Counts               |  |

| GAINVGA1           | Variable gain amplifier accuracy (gain = 1) <sup>13</sup>    | -                | -               | Counts <sup>15</sup> |  |

|                    | INL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3 <sup>14</sup> | 3 <sup>14</sup> |                      |  |

| GAINVGA2           | Variable gain amplifier accuracy (gain = 2) <sup>13</sup>    | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -5               | 5               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -3               | 3               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -3               | 3               |                      |  |

| GAINVGA4           | Variable gain amplifier accuracy (gain = $4$ ) <sup>13</sup> | -                | -               | Counts               |  |

|                    | INL, 16.5 MHz ADC                                            | -7               | 7               |                      |  |

|                    | INL, 33 MHz ADC                                              | -8               | 8               |                      |  |

|                    | DNL, 16.5 MHz ADC                                            | -4               | 4               |                      |  |

|                    | DNL, 33 MHz ADC                                              | -4               | 4               |                      |  |

|                    | Current consumption per ADC (two ADCs per EQADC)             |                  | 10              | mA                   |  |

|                    | Reference voltage current consumption per EQADC              |                  | 200             |                      |  |

| I <sub>ADR</sub>   |                                                              |                  | 200             | μΑ                   |  |

1. Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions. Delay from power up to full accuracy = 8 ms.

At V<sub>RH\_EQ</sub> - V<sub>RL\_EQ</sub> = 5.12 V, one count = 1.25 mV without using pregain. Based on 12-bit conversion result; does not account for AC and DC errors

- 3. INL and DNL are tested from V<sub>RL</sub> + 50 LSB to V<sub>RH</sub> 50 LSB.

- 4. At  $V_{RH_{EQ}} V_{RL_{EQ}} = 5.12 \text{ V}$ , one LSB = 1.25 mV.

| Symbol                                          | Deremeter                                  | Conditions                                                       |     | Value |     | llm |

|-------------------------------------------------|--------------------------------------------|------------------------------------------------------------------|-----|-------|-----|-----|

| Symbol                                          | Parameter                                  | Conditions                                                       | Min | Тур   | Мах | Uni |

| SNR <sub>DIFF150</sub> Signal to noise ratio in |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 80  | _     |     | dB  |

|                                                 | differential mode, 150<br>Ksps output rate | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 1                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 77  | _     | —   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 2                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 74  | _     | —   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 4                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 71  | _     | —   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 8                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 68  | _     | _   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 16                                                        |     |       |     |     |

| SNR <sub>DIFF333</sub>                          |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 71  | _     | _   | dE  |

|                                                 | differential mode, 333<br>Ksps output rate | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 1                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 70  | _     | _   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 2                                                         |     |       |     |     |

|                                                 |                                            | $4.5 \text{ V} < \text{V}_{\text{DDA}SD} < 5.5 \text{ V}^{8, 9}$ | 68  | -     | _   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 4                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 65  | _     | —   |     |

|                                                 |                                            | $V_{RH_{SD}} = V_{DDA_{SD}}$                                     |     |       |     |     |

|                                                 |                                            | GAIN = 8                                                         |     |       |     |     |

|                                                 |                                            | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V <sup>8, 9</sup>              | 62  | _     | _   |     |

|                                                 |                                            | $V_{RH\_SD} = V_{DDA\_SD}$                                       |     |       |     |     |

|                                                 |                                            | GAIN = 16                                                        |     |       |     |     |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Cumhal                                       | Devenueter                                    | Canditiana                          |     | Value |     | 11   |

|----------------------------------------------|-----------------------------------------------|-------------------------------------|-----|-------|-----|------|

| Symbol                                       | Parameter                                     | Conditions                          | Min | Тур   | Max | Unit |

| SINAD <sub>DIFF333</sub> Signal to noise and |                                               | Gain = 1                            | 66  | _     |     | dBFS |

|                                              | distortion ratio in<br>differential mode, 333 | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              | Ksps output rate                              | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 2                            | 66  | _     | —   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 4                            | 63  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 8                            | 62  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              | $V_{RH_{SD}} = V_{DDA_{SD}}$                  |                                     |     |       |     |      |

|                                              |                                               | Gain = 16                           | 59  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

| SINAD <sub>SE150</sub>                       | Signal to noise and                           | Gain = 1                            | 66  | _     |     | dBFS |

|                                              | distortion ratio in single-ended mode,        | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              | 150 Ksps output rate                          | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 2                            | 66  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 4                            | 63  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 8                            | 62  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                                              |                                               | Gain = 16                           | 54  | _     | _   |      |

|                                              |                                               | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                                              |                                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

## Table 18. SDADC electrical specifications (continued)

Table continues on the next page ...

| Cumbal                 | Paramatar                                 | Conditions                          |     | Value |     | Unit |

|------------------------|-------------------------------------------|-------------------------------------|-----|-------|-----|------|

| Symbol                 | Parameter                                 | Conditions                          | Min | Тур   | Мах | Unit |

| THD <sub>DIFF150</sub> | Total harmonic                            | Gain = 1                            | 65  | _     | _   | dBFS |

|                        | distortion in differential mode, 150 Ksps | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        | output rate                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 2                            | 68  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 4                            | 74  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 8                            | 80  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 16                           | 80  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

| THD <sub>DIFF333</sub> | Total harmonic                            | Gain = 1                            | 65  | _     | _   | dBFS |

|                        | distortion in differential mode, 333 Ksps | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        | output rate                               | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 2                            | 68  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_SD} = V_{DDA_SD}$            |     |       |     |      |

|                        |                                           | Gain = 4                            | 74  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 8                            | 80  | _     | —   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

|                        |                                           | Gain = 16                           | 80  | _     | _   |      |

|                        |                                           | 4.5 V < V <sub>DDA_SD</sub> < 5.5 V |     |       |     |      |

|                        |                                           | $V_{RH_{SD}} = V_{DDA_{SD}}$        |     |       |     |      |

| Table 18  | SDADC electrical s | necifications ( | (continued) |

|-----------|--------------------|-----------------|-------------|

| Table To. | SDADC electrical S | pecifications   | (continuea) |

Table continues on the next page...

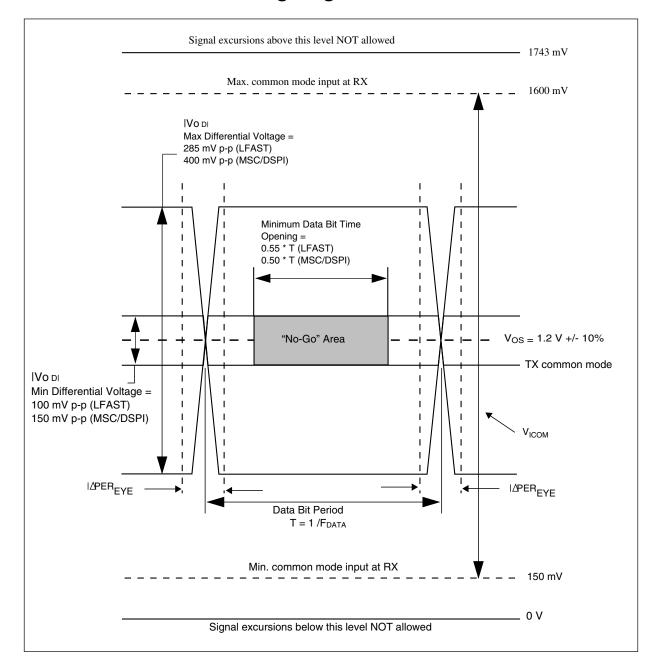

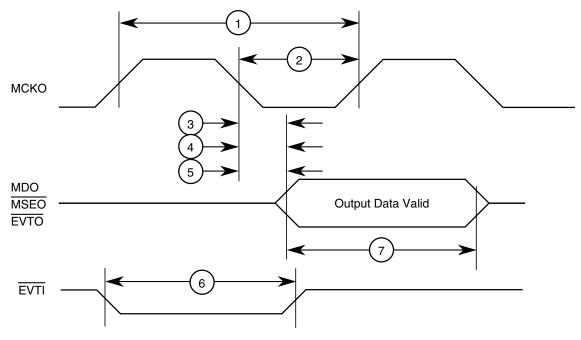

## 3.10.1 LFAST interface timing diagrams

Figure 8. LFAST and MSC/DSPI LVDS timing definition

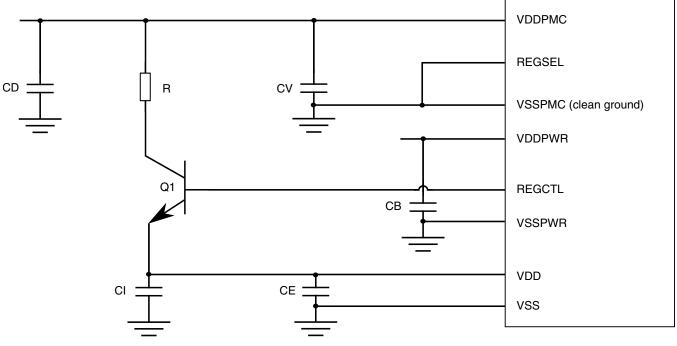

The following table shows the recommended components to be used in LDO regulation mode.

| Part type | Nominal                                                                  | Description                                                                                                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NPN BJT   | h <sub>FE</sub> = 400                                                    | NJD2873: ON Semiconductor LDO voltage regulator controller (VRC)                                                                                                                                                                                            |

| Capacitor | 4.7 μF - 20 V                                                            | Ceramic capacitor, total ESR < 70 m $\Omega$                                                                                                                                                                                                                |

| Capacitor | 0.047–0.049 µF - 7 V                                                     | Ceramic—one capacitor for each V <sub>DD</sub> pin                                                                                                                                                                                                          |

| Capacitor | 22 μF - 20 V                                                             | Ceramic V <sub>DDPMC</sub> (optional 0.1 µF)                                                                                                                                                                                                                |

| Capacitor | 22 µF - 20 V                                                             | Ceramic supply decoupling capacitor, ESR < 50 m $\Omega$ (as close as possible to NPN collector)                                                                                                                                                            |

| Capacitor | 0.1 µF - 7 V                                                             | Ceramic V <sub>DDPWR</sub>                                                                                                                                                                                                                                  |

| Resistor  | Application specific                                                     | Optional; reduces thermal loading on the NPN with high V <sub>DDPMC</sub> levels                                                                                                                                                                            |

|           | NPN BJT<br>Capacitor<br>Capacitor<br>Capacitor<br>Capacitor<br>Capacitor | NPN BJT $h_{FE} = 400$ Capacitor         4.7 $\mu$ F - 20 V           Capacitor         0.047-0.049 $\mu$ F - 7 V           Capacitor         22 $\mu$ F - 20 V           Capacitor         22 $\mu$ F - 20 V           Capacitor         0.1 $\mu$ F - 7 V |

Table 25. Recommended operating characteristics

The following diagram shows the LDO configuration connection.

Figure 12. VRC 1.2 V LDO configuration

# 3.11.1.2 SMPS mode recommended external components and characteristics

The following table shows the recommended components to be used in SMPS regulation mode.

The following table describes the supply stability capacitances required on the device for proper operation.

| Symbol                    | Parameter                                                                       | Conditions | Value <sup>1</sup> |                  |              | Unit |

|---------------------------|---------------------------------------------------------------------------------|------------|--------------------|------------------|--------------|------|

| Symbol                    | Farameter                                                                       | Conditions | Min                | Тур              | 1<br>Max<br> | Unit |

| C <sub>LV</sub>           | Minimum V <sub>DD</sub> external bulk capacitance <sup>2, 3</sup>               | LDO mode   | 4.7                | _                | —            | μF   |

|                           |                                                                                 | SMPS mode  | 22                 | _                | _            | μF   |

| C <sub>SMPSPWR</sub>      | Minimum SMPS driver supply capacitance                                          | —          | 22                 | _                | _            | μF   |

| C <sub>HV_PMC</sub>       | Minimum V <sub>DDPMC</sub> external bulk capacitance <sup>4, 5</sup>            | LDO mode   | 22                 | _                | —            | μF   |

|                           |                                                                                 | SMPS mode  | 22                 | _                | —            | μF   |

| C <sub>HV_IO</sub>        | Minimum V <sub>DDEx</sub> /V <sub>DDEHx</sub> external capacitance <sup>2</sup> | —          | —                  | 4.7 <sup>6</sup> | _            | μF   |

| C <sub>HV_FLA</sub>       | Minimum V <sub>DD_FLA</sub> external capacitance <sup>7</sup>                   | —          | 1.0                | 2.0              | _            | μF   |

| C <sub>HV_ADC_EQA/B</sub> | Minimum V <sub>DDA_EQA/B</sub> external capacitance <sup>8</sup>                | —          | 0.01               | _                | _            | μF   |

| C <sub>REFEQ</sub>        | Minimum REF <sub>BYPCA/B</sub> external capacitance <sup>9</sup>                | —          | 0.01               | _                |              | μF   |

| C <sub>HV_ADC_SD</sub>    | Minimum V <sub>DDA_SD</sub> external capacitance <sup>10</sup>                  | —          | 1.0                | 2.2              |              | μF   |

Table 28.

Device power supply integration

1. See Figure 14 for capacitor integration.

- 2. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 3. Each V<sub>DD</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 4. Recommended X7R or X5R ceramic low ESR capacitors, ±15% variation over process, voltage, temperature, and aging.

- 5. Each V<sub>DDPMC</sub> pin requires both a 47 nF and a 0.01 µF capacitor for high-frequency bypass and EMC requirements.

- 6. The actual capacitance should be selected based on the I/O usage in order to keep the supply voltage within its operating range.

- 7. The recommended flash regulator composition capacitor is 2.0  $\mu$ F typical X7R or X5R, with -50% and +35% as min and max. This puts the min cap at 0.75  $\mu$ F.

- For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_EQA/B</sub> and V<sub>SSA\_EQ</sub>.

- 9. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 µF between REF<sub>BYPCA/B</sub> and V<sub>SS</sub>.

- 10. For noise filtering it is recommended to add a high frequency bypass capacitance of 0.1 μF between V<sub>DDA\_SD</sub> and V<sub>SSA\_SD</sub>.

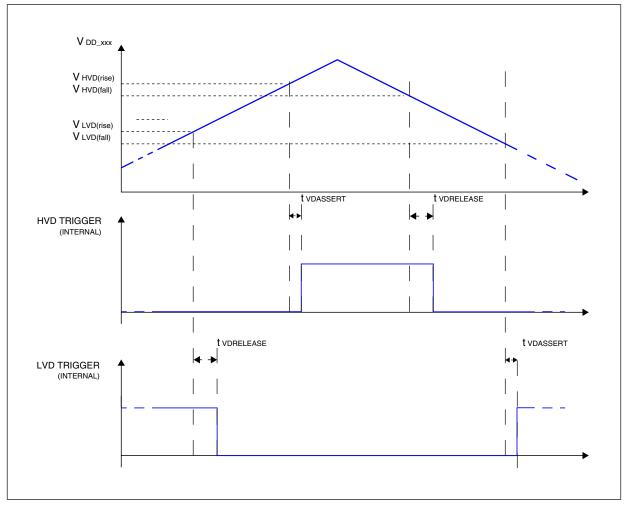

## 3.11.3 Device voltage monitoring

The LVD/HVDs for the device and their levels are given in the following table. Voltage monitoring threshold definition is provided in the following figure.

Figure 15. Voltage monitor threshold definition

| Table 29. | Voltage monitor electrical characteristics <sup>1, 2</sup> |

|-----------|------------------------------------------------------------|

|-----------|------------------------------------------------------------|

|                       |                                     |                              | Co           | nfigura      | tion       |      | Value |      |      |

|-----------------------|-------------------------------------|------------------------------|--------------|--------------|------------|------|-------|------|------|

| Symbol                | Parameter                           | Conditions                   | Trim<br>bits | Mask<br>Opt. | Pow.<br>Up | Min  | Тур   | Max  | Unit |

| POR098_c <sup>3</sup> | LV internal supply power            | Rising voltage (powerup)     | N/A          | No           | Enab.      | 960  | 1010  | 1060 | mV   |

|                       | on reset                            | Falling voltage (power down) |              |              |            | 940  | 990   | 1040 |      |

| LVD_core_hot          | LV internal <sup>4</sup> supply low | Rising voltage (untrimmed)   | 4bit         | No           | Enab.      | 1100 | 1140  | 1183 | mV   |

|                       | voltage monitoring                  | Falling voltage (untrimmed)  |              |              |            | 1080 | 1120  | 1163 |      |

|                       |                                     | Rising voltage (trimmed)     | 1            |              |            | 1142 | 1165  | 1183 |      |

|                       |                                     | Falling voltage (trimmed)    |              |              |            | 1122 | 1145  | 1163 |      |

| LVD_core_cold         | LV external <sup>5</sup> supply low | Rising voltage               | 4bit         | Yes          | Disab.     | 1165 | 1180  | 1198 | mV   |

|                       | voltage monitoring                  | Falling voltage              |              |              |            | 1136 | 1160  | 1178 |      |

| HVD_core              | LV internal cold supply             | Rising voltage               | 4bit         | Yes          | Disab.     | 1338 | 1365  | 1385 | mV   |

|                       | high voltage monitoring             | Falling voltage              |              |              |            | 1318 | 1345  | 1365 |      |

Table continues on the next page...

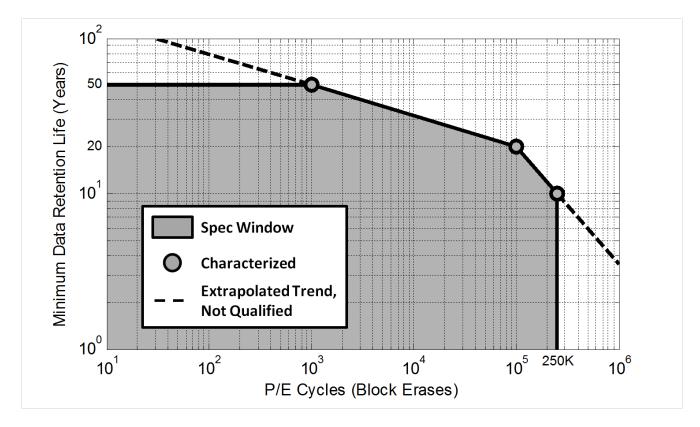

## 3.12.4 Data retention vs program/erase cycles

Graphically, Data Retention versus Program/Erase Cycles can be represented by the following figure. The spec window represents qualified limits. The extrapolated dotted line demonstrates technology capability, however is beyond the qualification limits.

## 3.12.5 Flash memory AC timing specifications Table 33. Flash memory AC timing specifications

| Symbol            | Characteristic                                                                | Min | Typical                                       | Max                                             | Units |

|-------------------|-------------------------------------------------------------------------------|-----|-----------------------------------------------|-------------------------------------------------|-------|

| t <sub>psus</sub> | Time from setting the MCR-PSUS bit until MCR-DONE bit is set to a 1.          |     | 7<br>plus four<br>system<br>clock<br>periods  | 9.1<br>plus four<br>system<br>clock<br>periods  | μs    |

| t <sub>esus</sub> | Time from setting the MCR-ESUS bit until MCR-DONE bit is set to a 1.          |     | 16<br>plus four<br>system<br>clock<br>periods | 20.8<br>plus four<br>system<br>clock<br>periods | μs    |