### Atmel - ATTINY2313V-10SI Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | AVR                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 10MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                       |

| Number of I/O              | 18                                                          |

| Program Memory Size        | 2KB (1K x 16)                                               |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 128 x 8                                                     |

| RAM Size                   | 128 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                              |

| Supplier Device Package    | 20-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/attiny2313v-10si |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

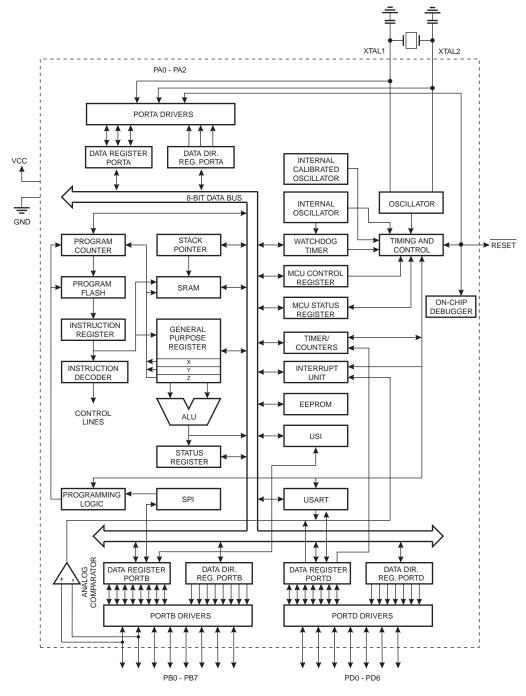

### **Block Diagram**

# Resources

A comprehensive set of development tools, application notes and datasheets are available for downloadon http://www.atmel.com/avr.

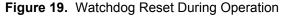

### Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period t<sub>TOUT</sub>. Refer to page 46 for details on operation of the Watchdog Timer.

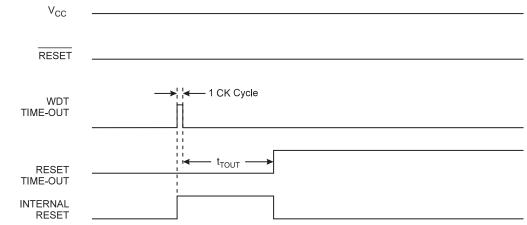

MCU Status Register – The MCU Status Register provides information on which reset source caused an MCU reset. MCUSR

#### Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

Bit 1 – EXTRF: External Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

### • Bit 0 – PORF: Power-on Reset Flag

This bit is set if a Power-on Reset occurs. The bit is reset only by writing a logic zero to the flag.

To make use of the Reset flags to identify a reset condition, the user should read and then reset the MCUSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the reset flags.

### Internal Voltage Reference

Voltage Reference Enable Signals and Start-up Time ATtiny2313 features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator.

The voltage reference has a start-up time that may influence the way it should be used. The start-up time is given in Table 18. To save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODLEVEL [2..0] Fuse).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the ACBG bit in ACSR).

Thus, when the BOD is not enabled, after setting the ACBG bit, the user must always allow the reference to start up before the output from the Analog Comparator is used. To reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

| Symbol          | Parameter                             | Condition                                        | Min | Тур | Мах | Units |

|-----------------|---------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| V <sub>BG</sub> | Bandgap reference voltage             | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C | 1.0 | 1.1 | 1.2 | V     |

| t <sub>BG</sub> | Bandgap reference start-up time       | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C |     | 40  | 70  | μs    |

| I <sub>BG</sub> | Bandgap reference current consumption | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C |     | 15  |     | μA    |

Table 18. Internal Voltage Reference Characteristics<sup>(1)</sup>

Note: 1. Values are guidelines only. Actual values are TBD.

| The most typical and general program setup for the Reset and Interrupt Vector Addresses in |

|--------------------------------------------------------------------------------------------|

| ATtiny2313 is:                                                                             |

| 1 uny201013.   |                                                             |                    |                                 |

|----------------|-------------------------------------------------------------|--------------------|---------------------------------|

| Address Labels | s Code                                                      |                    | Comments                        |

| 0x0000         | rjmp                                                        | RESET              | ; Reset Handler                 |

| 0x0001         | rjmp                                                        | INTO               | ; External Interrupt0 Handler   |

| 0x0002         | rjmp                                                        | INT1               | ; External Interrupt1 Handler   |

| 0x0003         | rjmp                                                        | TIM1_CAPT          | ; Timer1 Capture Handler        |

| 0x0004         | rjmp                                                        | TIM1_COMPA         | ; Timer1 CompareA Handler       |

| 0x0005         | rjmp                                                        | TIM1_OVF           | ; Timer1 Overflow Handler       |

| 0x0006         | rjmp                                                        | TIM0_OVF           | ; Timer0 Overflow Handler       |

| 0x0007         | rjmp                                                        | USART0_RXC         | ; USARTO RX Complete Handler    |

| 0x0008         | rjmp                                                        | USART0_DRE         | ; USART0,UDR Empty Handler      |

| 0x0009         | rjmp                                                        | USART0_TXC         | ; USART0 TX Complete Handler    |

| 0x000A         | rjmp                                                        | ANA_COMP           | ; Analog Comparator Handler     |

| 0x000B         | rjmp                                                        | PCINT              | ; Pin Change Interrupt          |

| 0x000C         | rjmp                                                        | TIMER1_COMPB       | ; Timer1 Compare B Handler      |

| 0x000D         | rjmp                                                        | TIMER0_COMPA       | ; Timer0 Compare A Handler      |

| 0x000E         | rjmp                                                        | TIMER0_COMPB       | ; Timer0 Compare B Handler      |

| 0x000F         | rjmp                                                        | USI_START          | ; USI Start Handler             |

| 0x0010         | rjmp                                                        | USI_OVERFLOW       | ; USI Overflow Handler          |

| 0x0011         | rjmp                                                        | EE_READY           | ; EEPROM Ready Handler          |

| 0x0012         | rjmp                                                        | WDT_OVERFLOW       | ; Watchdog Overflow Handler     |

|                |                                                             |                    |                                 |

| ;              |                                                             |                    |                                 |

| 0x0013 RESET   | : ldi                                                       | r16, low(RAMEN     | D); Main program start          |

| 0x0014         | out                                                         | SPL,r16            | Set Stack Pointer to top of RAM |

| 0x0015         | sei                                                         |                    | ; Enable interrupts             |

| 0x0016         | <instr< td=""><td><pre>xxx&lt;</pre></td><td></td></instr<> | <pre>xxx&lt;</pre> |                                 |

|                |                                                             |                    |                                 |

|                |                                                             |                    |                                 |

Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed between  $\frac{1}{2}$  and  $\frac{1}{2}$  system clock period depending upon the time of assertion.

When reading back a software assigned pin value, a nop instruction must be inserted as indicated in Figure 24. The out instruction sets the "SYNC LATCH" signal at the positive edge of the clock. In this case, the delay tpd through the synchronizer is 1 system clock period.

Figure 24. Synchronization when Reading a Software Assigned Pin Value

# External Interrupts

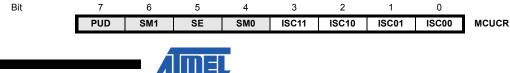

The External Interrupts are triggered by the INT0 pin, INT1 pin or any of the PCINT7..0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0, INT1 or PCINT7..0 pins are configured as outputs. This feature provides a way of generating a software interrupt. The pin change interrupt PCIF will trigger if any enabled PCINT7..0 pin toggles. The PCMSK Register control which pins contribute to the pin change interrupts. Pin change interrupts on PCINT7..0 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode.

The INT0 and INT1 interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the "MCU Control Register – MCUCR" on page 32. When the INT0 or INT1 interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low. Note that recognition of falling or rising edge interrupts on INT0 and INT1 requires the presence of an I/O clock, described in "Clock Systems and their Distribution" on page 24. Low level interrupt on INT0 and INT1 is detected asynchronously. This implies that this interrupt can be used for waking the part from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

Note that if a level triggered interrupt is used for wake-up from Power-down, the required level must be held long enough for the MCU to complete the wake-up to trigger the level interrupt. If the level disappears before the end of the Start-up Time, the MCU will still wake up, but no interrupt will be generated. The start-up time is defined by the SUT and CKSEL Fuses as described in "System Clock and Clock Options" on page 24.

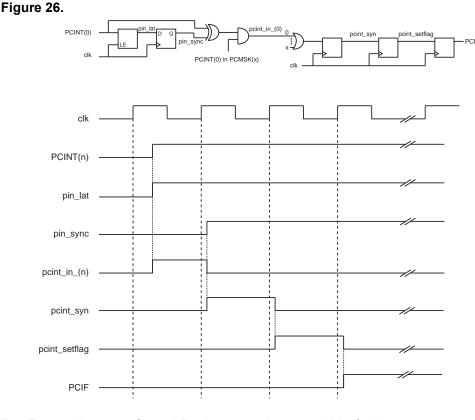

An example of timing of a pin change interrupt is shown in Figure 26.

# Pin Change Interrupt Timing

**MCU Control Register** The External Interrupt Control Register contains control bits for interrupt sense control. – **MCUCR**

# 8-bit Timer/Counter0 with PWM

Timer/Counter0 is a general purpose 8-bit Timer/Counter module, with two independent Output Compare Units, and with PWM support. It allows accurate program execution timing (event management) and wave generation. The main features are:

- Two Independent Output Compare Units

- Double Buffered Output Compare Registers

- Clear Timer on Compare Match (Auto Reload)

- Glitch Free, Phase Correct Pulse Width Modulator (PWM)

- Variable PWM Period

- Frequency Generator

- Three Independent Interrupt Sources (TOV0, OCF0A, and OCF0B)

### Overview

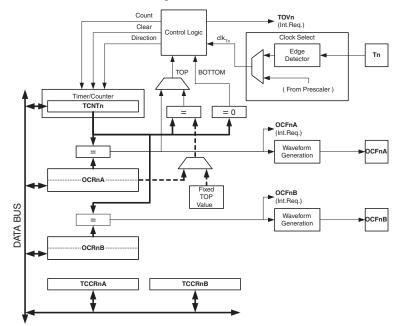

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 27. For the actual placement of I/O pins, refer to "Pinout ATtiny2313" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "8-bit Timer/Counter Register Description" on page 75.

### Figure 27. 8-bit Timer/Counter Block Diagram

### Registers

The Timer/Counter (TCNT0) and Output Compare Registers (OCR0A and OCR0B) are 8-bit registers. Interrupt request (abbreviated to Int.Req. in the figure) signals are all visible in the Timer Interrupt Flag Register (TIFR). All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK). TIFR and TIMSK are not shown in the figure.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the T0 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock ( $clk_{T0}$ ).

The double buffered Output Compare Registers (OCR0A and OCR0B) is compared with the Timer/Counter value at all times. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pins (OC0A and OC0B). See "Output Compare Unit" on page 66. for details. The Compare Match event will also set the Compare Flag (OCF0A or OCF0B) which can be used to generate an Output Compare interrupt request.

|                                             | The OCR0x Registers are double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR0x Compare Registers to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free. The OCR0x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0x Buffer Register, and if double buffering is disabled the CPU will access the OCR0x directly.      |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Force Output<br>Compare                     | In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0x) bit. Forcing Compare Match will not set the OCF0x Flag or reload/clear the timer, but the OC0x pin will be updated as if a real Compare Match had occurred (the COM0x1:0 bits settings define whether the OC0x pin is set, cleared or toggled).                                                                                                                                                                                                                                                                                                                   |

| Compare Match<br>Blocking by TCNT0<br>Write | All CPU write operations to the TCNT0 Register will block any Compare Match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0x to be initial-<br>ized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Using the Output<br>Compare Unit            | Since writing TCNT0 in any mode of operation will block all Compare Matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the Output Compare Unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0x value, the Compare Match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is down-counting.                                                                                                                                                                                                                          |

|                                             | The setup of the OC0x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0x value is to use the Force Output Compare (FOC0x) strobe bits in Normal mode. The OC0x Registers keep their values even when changing between Waveform Generation modes.                                                                                                                                                                                                                                                                                                                                                                                  |

|                                             | Be aware that the COM0x1:0 bits are not double buffered together with the compare value.<br>Changing the COM0x1:0 bits will take effect immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Compare Match<br>Output Unit                | The Compare Output mode (COM0x1:0) bits have two functions. The Waveform Generator uses the COM0x1:0 bits for defining the Output Compare (OC0x) state at the next Compare Match. Also, the COM0x1:0 bits control the OC0x pin output source. Figure 30 shows a simplified schematic of the logic affected by the COM0x1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COM0x1:0 bits are shown. When referring to the OC0x state, the reference is for the internal OC0x Register, not the OC0x pin. If a system reset occur, the OC0x Register is reset to "0". |

|                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | COMnx1 Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   | COMnx0 Waveform D Q<br>FOCn Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   | The general I/O port function is overridden by the Output Compare (OC0x) from the Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                   | Generator if either of the COM0x1:0 bits are set. However, the OC0x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   | Register bit for the OC0x pin (DDR_OC0x) must be set as output before the OC0x value is visible on the pin. The port override function is independent of the Waveform Generation mode.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                   | The design of the Output Compare pin logic allows initialization of the OC0x state before the out-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                   | put is enabled. Note that some COM0x1:0 bit settings are reserved for certain modes of operation. See "8-bit Timer/Counter Register Description" on page 75.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Compare Output Mode<br>and Waveform<br>Generation | The Waveform Generator uses the COM0x1:0 bits differently in Normal, CTC, and PWM modes.<br>For all modes, setting the COM0x1:0 = 0 tells the Waveform Generator that no action on the<br>OC0x Register is to be performed on the next Compare Match. For compare output actions in<br>the non-PWM modes refer to Figure 29 on page 66. For fast PWM mode, refer to Table 26 on<br>page 57, and for phase correct PWM refer to Table 27 on page 57.                                                                                                                                                                 |

|                                                   | A change of the COM0x1:0 bits state will have effect at the first Compare Match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC0x strobe bits.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Modes of<br>Operation                             | The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the Waveform Generation mode (WGM02:0) and Compare Output mode (COM0x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM0x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM0x1:0 bits control whether the output should be set, cleared, or toggled at a Compare Match (See "Compare Match Output Unit" on page 67.). |

|                                                   | For detailed timing information refer to Figure 34, Figure 35, Figure 36 and Figure 37 in "Timer/Counter Timing Diagrams" on page 73.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Normal Mode                                       | The simplest mode of operation is the Normal mode (WGM02:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP = $0xFF$ ) and then restarts from the bottom ( $0x00$ ). In normal operation the Timer/Counter Overflow Flag (TOV0) will be set in the same                                                                                                                                                                                                                            |

# Figure 30. Compare Match Output Unit, Schematic

| Pog | ietore |

|-----|--------|

| Reg | isters |

The *Timer/Counter* (TCNT1), *Output Compare Registers* (OCR1A/B), and *Input Capture Register* (ICR1) are all 16-bit registers. Special procedures must be followed when accessing the 16-bit registers. These procedures are described in the section "Accessing 16-bit Registers" on page 86. The *Timer/Counter Control Registers* (TCCR1A/B) are 8-bit registers and have no CPU access restrictions. Interrupt requests (abbreviated to Int.Req. in the figure) signals are all visible in the *Timer Interrupt Flag Register* (TIFR). All interrupts are individually masked with the *Timer Interrupt Mask Register* (TIMSK). TIFR and TIMSK are not shown in the figure.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the T1 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock ( $clk_{T1}$ ).

The double buffered Output Compare Registers (OCR1A/B) are compared with the Timer/Counter value at all time. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pin (OC1A/B). See "Output Compare Units" on page 92.. The compare match event will also set the Compare Match Flag (OCF1A/B) which can be used to generate an Output Compare interrupt request.

The Input Capture Register can capture the Timer/Counter value at a given external (edge triggered) event on either the Input Capture pin (ICP1) or on the Analog Comparator pins (See "Analog Comparator" on page 151.) The Input Capture unit includes a digital filtering unit (Noise Canceler) for reducing the chance of capturing noise spikes.

The TOP value, or maximum Timer/Counter value, can in some modes of operation be defined by either the OCR1A Register, the ICR1 Register, or by a set of fixed values. When using OCR1A as TOP value in a PWM mode, the OCR1A Register can not be used for generating a PWM output. However, the TOP value will in this case be double buffered allowing the TOP value to be changed in run time. If a fixed TOP value is required, the ICR1 Register can be used as an alternative, freeing the OCR1A to be used as PWM output.

Definitions

The following definitions are used extensively throughout the section:

| Table 42. De | efinitions |

|--------------|------------|

|--------------|------------|

| BOTTOM | The counter reaches the <i>BOTTOM</i> when it becomes 0x0000.                                                                                                                                                                                                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFFFF (decimal 65535).                                                                                                                                                                                                                                  |

| ТОР    | The counter reaches the <i>TOP</i> when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be one of the fixed values: 0x00FF, 0x01FF, or 0x03FF, or to the value stored in the OCR1A or ICR1 Register. The assignment is dependent of the mode of operation. |

### Compatibility

The 16-bit Timer/Counter has been updated and improved from previous versions of the 16-bit AVR Timer/Counter. This 16-bit Timer/Counter is fully compatible with the earlier version regarding:

- All 16-bit Timer/Counter related I/O Register address locations, including Timer Interrupt Registers.

- Bit locations inside all 16-bit Timer/Counter Registers, including Timer Interrupt Registers.

- Interrupt Vectors.

The following control bits have changed name, but have same functionality and register location:

- PWM10 is changed to WGM10.

- PWM11 is changed to WGM11.

- CTC1 is changed to WGM12.

The following bits are added to the 16-bit Timer/Counter Control Registers:

- FOC1A and FOC1B are added to TCCR1A.

- WGM13 is added to TCCR1B.

The 16-bit Timer/Counter has improvements that will affect the compatibility in some special cases.

Accessing 16-bit Registers The TCNT1, OCR1A/B, and ICR1 are 16-bit registers that can be accessed by the AVR CPU via the 8-bit data bus. The 16-bit register must be byte accessed using two read or write operations. Each 16-bit timer has a single 8-bit register for temporary storing of the high byte of the 16-bit access. The same temporary register is shared between all 16-bit registers within each 16-bit timer. Accessing the low byte triggers the 16-bit read or write operation. When the low byte of a 16-bit register is written by the CPU, the high byte stored in the temporary register, and the low byte written are both copied into the 16-bit register in the same clock cycle. When the low byte of a 16-bit register is read by the CPU, the high byte of the 16-bit register is copied into the temporary register in the same clock cycle as the low byte is read.

> Not all 16-bit accesses uses the temporary register for the high byte. Reading the OCR1A/B 16bit registers does not involve using the temporary register.

> To do a 16-bit write, the high byte must be written before the low byte. For a 16-bit read, the low byte must be read before the high byte.

The following code examples show how to access the 16-bit timer registers assuming that no interrupts updates the temporary register. The same principle can be used directly for accessing the OCR1A/B and ICR1 Registers. Note that when using "C", the compiler handles the 16-bit access.

Data Reception -<br/>The USART<br/>ReceiverThe USART Receiver is enabled by writing the Receive Enable (RXEN) bit in the UCSRB Regis-<br/>ter to one. When the Receiver is enabled, the normal pin operation of the RxD pin is overridden<br/>by the USART and given the function as the Receiver's serial input. The baud rate, mode of<br/>operation and frame format must be set up once before any serial reception can be done. If syn-<br/>chronous operation is used, the clock on the XCK pin will be used as transfer clock.

**Receiving Frames with 5 to 8 Data Bits** The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCK clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received. A second stop bit will be ignored by the Receiver. When the first stop bit is received, i.e., a complete serial frame is present in the Receive Shift Register, the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDR I/O location.

The following code example shows a simple USART receive function based on polling of the Receive Complete (RXC) flag. When using frames with less than eight bits the most significant bits of the data read from the UDR will be masked to zero. The USART has to be initialized before the function can be used.

```

Assembly Code Example<sup>(1)</sup>

USART Receive:

; Wait for data to be received

sbis UCSRA, RXC

rjmp USART Receive

; Get and return received data from buffer

in

r16, UDR

ret

C Code Example<sup>(1)</sup>

unsigned char USART Receive ( void )

/* Wait for data to be received */

while ( ! (UCSRA & (1<<RXC)) )

;

/* Get and return received data from buffer */

return UDR;

}

```

The example code assumes that the part specific header file is included. For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The function simply waits for data to be present in the receive buffer by checking the RXC flag, before reading the buffer and returning the value.

Note:

| Parity Checker | The Parity Checker is active when the high USART Parity mode (UPM1) bit is set. Type of Parity Check to be performed (odd or even) is selected by the UPM0 bit. When enabled, the Parity Checker calculates the parity of the data bits in incoming frames and compares the result with the parity bit from the serial frame. The result of the check is stored in the receive buffer together with the received data and stop bits. The Parity Error (UPE) flag can then be read by software to check if the frame had a Parity Error. |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | The LIDE bit is not if the point character that can be read from the reasing huffer had a Darity                                                                                                                                                                                                                                                                                                                                                                                                                                        |

The UPE bit is set if the next character that can be read from the receive buffer had a Parity Error when received and the Parity Checking was enabled at that point (UPM1 = 1). This bit is valid until the receive buffer (UDR) is read.

- **Disabling the Receiver** In contrast to the Transmitter, disabling of the Receiver will be immediate. Data from ongoing receptions will therefore be lost. When disabled (i.e., the RXEN is set to zero) the Receiver will no longer override the normal function of the RxD port pin. The Receiver buffer FIFO will be flushed when the Receiver is disabled. Remaining data in the buffer will be lost

- Flushing the ReceiveThe receiver buffer FIFO will be flushed when the Receiver is disabled, i.e., the buffer will be<br/>emptied of its contents. Unread data will be lost. If the buffer has to be flushed during normal<br/>operation, due to for instance an error condition, read the UDR I/O location until the RXC flag is<br/>cleared. The following code example shows how to flush the receive buffer.

| Assembly Code Example <sup>(1)</sup>                                         |

|------------------------------------------------------------------------------|

| USART_Flush:                                                                 |

| sbis UCSRA, RXC                                                              |

| ret                                                                          |

| in r16, UDR                                                                  |

| rjmp USART_Flush                                                             |

| C Code Example <sup>(1)</sup>                                                |

| <pre>void USART_Flush( void )</pre>                                          |

| {                                                                            |

| unsigned char dummy;                                                         |

| <pre>while ( UCSRA &amp; (1&lt;<rxc) )="" dummy="UDR;&lt;/pre"></rxc)></pre> |

| }                                                                            |

- Note: 1. The example code assumes that the part specific header file is included.

- For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

Asynchronous Data Reception The USART includes a clock recovery and a data recovery unit for handling asynchronous data reception. The clock recovery logic is used for synchronizing the internally generated baud rate clock to the incoming asynchronous serial frames at the RxD pin. The data recovery logic samples and low pass filters each incoming bit, thereby improving the noise immunity of the Receiver. The asynchronous reception operational range depends on the accuracy of the internal baud rate clock, the rate of the incoming frames, and the frame size in number of bits.

| Start Condition<br>Detector                  | The start condition detector is shown in Figure 65. The SDA line is delayed (in the range of 50 to 300 ns) to ensure valid sampling of the SCL line.<br>The start condition detector is working asynchronously and can therefore wake up the processor from the Power-down sleep mode. However, the protocol used might have restrictions on the SCL hold time. Therefore, when using this feature in this case the Oscillator start-up time set by the CKSEL Fuses (see "Clock Systems and their Distribution" on page 24) must also be taken into the consideration. |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alternative USI<br>Usage                     | When the USI unit is not used for serial communication, it can be set up to do alternative tasks due to its flexible design.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Half-duplex<br>Asynchronous Data<br>Transfer | By utilizing the Shift Register in Three-wire mode, it is possible to implement a more compact and higher performance UART than by software only.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4-bit Counter                                | The 4-bit counter can be used as a stand-alone counter with overflow interrupt. Note that if the counter is clocked externally, both clock edges will generate an increment.                                                                                                                                                                                                                                                                                                                                                                                           |

| 12-bit Timer/Counter                         | Combining the USI 4-bit counter and Timer/Counter0 allows them to be used as a 12-bit counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Edge Triggered<br>External Interrupt         | By setting the counter to maximum value (F) it can function as an additional external interrupt. The overflow flag and interrupt enable bit are then used for the external interrupt. This feature is selected by the USICS1 bit.                                                                                                                                                                                                                                                                                                                                      |

| Software Interrupt                           | The counter overflow interrupt can be used as a software interrupt triggered by a clock strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| USI Register<br>Descriptions                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| USI Data Register –<br>USIDR                 | Bit 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

MSB

R/W

0

R/W

0

R/W

0

Read/Write

Initial Value

The USI uses no buffering of the serial register, i.e., when accessing the Data Register (USIDR) the serial register is accessed directly. If a serial clock occurs at the same cycle the register is written, the register will contain the value written and no shift is performed. A (left) shift operation is performed depending of the USICS1..0 bits setting. The shift operation can be controlled by an external clock edge, by a Timer/Counter0 overflow, or directly by software using the USICLK strobe bit. Note that even when no wire mode is selected (USIWM1..0 = 0) both the external data input (DI/SDA) and the external clock input (USCK/SCL) can still be used by the Shift Register.

R/W

0

R/W

0

R/W

0

R/W

0

The output pin in use, DO or SDA depending on the wire mode, is connected via the output latch to the most significant bit (bit 7) of the Data Register. The output latch is open (transparent) during the first half of a serial clock cycle when an external clock source is selected (USICS1 = 1), and constantly open when an internal clock source is used (USICS1 = 0). The output will be changed immediately when a new MSB written as long as the latch is open. The latch ensures that data input is sampled and data output is changed on opposite clock edges.

Note that the corresponding Data Direction Register to the pin must be set to one for enabling data output from the Shift Register.

USIDR

LSB

R/W

0

### • Bit 7 – USISIE: Start Condition Interrupt Enable

Setting this bit to one enables the Start Condition detector interrupt. If there is a pending interrupt when the USISIE and the Global Interrupt Enable Flag is set to one, this will immediately be executed.

### • Bit 6 – USIOIE: Counter Overflow Interrupt Enable

Setting this bit to one enables the Counter Overflow interrupt. If there is a pending interrupt when the USIOIE and the Global Interrupt Enable Flag is set to one, this will immediately be executed.

### • Bit 5..4 – USIWM1..0: Wire Mode

These bits set the type of wire mode to be used. Basically only the function of the outputs are affected by these bits. Data and clock inputs are not affected by the mode selected and will always have the same function. The counter and Shift Register can therefore be clocked externally, and data input sampled, even when outputs are disabled. The relations between USIWM1..0 and the USI operation is summarized in Table 60 on page 149.

# Self-Programming the Flash

The device provides a Self-Programming mechanism for downloading and uploading program code by the MCU itself. The Self-Programming can use any available data interface and associated protocol to read code and write (program) that code into the Program memory. The SPM instruction is disabled by default but it can be enabled by programming the SELFPRGEN fuse (to "0").

The Program memory is updated in a page by page fashion. Before programming a page with the data stored in the temporary page buffer, the page must be erased. The temporary page buffer is filled one word at a time using SPM and the buffer can be filled either before the Page Erase command or between a Page Erase and a Page Write operation:

Alternative 1, fill the buffer before a Page Erase

- Fill temporary page buffer

- Perform a Page Erase

- Perform a Page Write

Alternative 2, fill the buffer after Page Erase

- Perform a Page Erase

- Fill temporary page buffer

- Perform a Page Write

If only a part of the page needs to be changed, the rest of the page must be stored (for example in the temporary page buffer) before the erase, and then be re-written. When using alternative 1, the Boot Loader provides an effective Read-Modify-Write feature which allows the user software to first read the page, do the necessary changes, and then write back the modified data. If alternative 2 is used, it is not possible to read the old data while loading since the page is already erased. The temporary page buffer can be accessed in a random sequence. It is essential that the page address used in both the Page Erase and Page Write operation is addressing the same page.

- Performing Page<br/>Erase by SPMTo execute Page Erase, set up the address in the Z-pointer, write "00000011" to SPMCSR and<br/>execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored.<br/>The page address must be written to PCPAGE in the Z-register. Other bits in the Z-pointer will<br/>be ignored during this operation.

- The CPU is halted during the Page Erase operation.

**Filling the Temporary Buffer (Page Loading)** To write an instruction word, set up the address in the Z-pointer and data in R1:R0, write "00000001" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The content of PCWORD in the Z-register is used to address the data in the temporary buffer. The temporary buffer will auto-erase after a Page Write operation or by writing the CTPB bit in SPMCSR. It is also erased after a system reset. Note that it is not possible to write more than one time to each address without erasing the temporary buffer.

If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded will be lost.

- Performing a PageTo execute Page Write, set up the address in the Z-pointer, write "00000101" to SPMCSR and<br/>execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored.<br/>The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to<br/>zero during this operation.

- The CPU is halted during the Page Write operation.

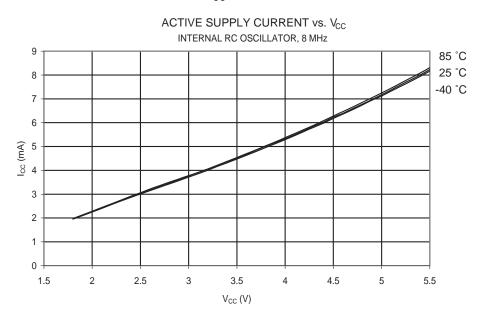

Figure 86. Active Supply Current vs. V<sub>CC</sub> (Internal RC Oscillator, 8 MHz)

# ATtiny2313

# Instruction Set Summary

| Mnemonics        | Operands          | Description                               | Operation                                                                                | Flags              | #Clocks |

|------------------|-------------------|-------------------------------------------|------------------------------------------------------------------------------------------|--------------------|---------|

| ARITHMETIC AND L | OGIC INSTRUCTIONS | 6                                         |                                                                                          |                    |         |

| ADD              | Rd, Rr            | Add two Registers                         | $Rd \leftarrow Rd + Rr$                                                                  | Z,C,N,V,H          | 1       |

| ADC              | Rd, Rr            | Add with Carry two Registers              | $Rd \leftarrow Rd + Rr + C$                                                              | Z,C,N,V,H          | 1       |

| ADIW             | Rdl,K             | Add Immediate to Word                     | Rdh:Rdl ← Rdh:Rdl + K                                                                    | Z,C,N,V,S          | 2       |

| SUB              | Rd, Rr            | Subtract two Registers                    | $Rd \leftarrow Rd - Rr$                                                                  | Z,C,N,V,H          | 1       |

| SUBI             | Rd, K             | Subtract Constant from Register           | $Rd \gets Rd - K$                                                                        | Z,C,N,V,H          | 1       |

| SBC              | Rd, Rr            | Subtract with Carry two Registers         | $Rd \leftarrow Rd - Rr - C$                                                              | Z,C,N,V,H          | 1       |

| SBCI             | Rd, K             | Subtract with Carry Constant from Reg.    | $Rd \leftarrow Rd - K - C$                                                               | Z,C,N,V,H          | 1       |

| SBIW             | Rdl,K             | Subtract Immediate from Word              | Rdh:Rdl ← Rdh:Rdl - K                                                                    | Z,C,N,V,S          | 2       |

| AND              | Rd, Rr            | Logical AND Registers                     | $Rd \leftarrow Rd \bullet Rr$                                                            | Z,N,V              | 1       |

| ANDI             | Rd, K             | Logical AND Register and Constant         | $Rd \leftarrow Rd \bullet K$                                                             | Z,N,V              | 1       |

| OR               | Rd, Rr            | Logical OR Registers                      | $Rd \leftarrow Rd v Rr$                                                                  | Z,N,V              | 1       |

| ORI              | Rd, K             | Logical OR Register and Constant          | Rd ← Rd v K                                                                              | Z,N,V              | 1       |

| EOR              | Rd, Rr            | Exclusive OR Registers                    | $Rd \leftarrow Rd \oplus Rr$                                                             | Z,N,V              | 1       |

| COM              | Rd                | One's Complement                          | $Rd \leftarrow 0xFF - Rd$                                                                | Z,C,N,V            | 1       |

| NEG              | Rd                | Two's Complement                          | Rd ← 0x00 - Rd                                                                           | Z,C,N,V,H          | 1       |

| SBR              | Rd,K              | Set Bit(s) in Register                    | $Rd \leftarrow Rd \vee K$                                                                | Z,N,V              | 1       |

| CBR              | Rd,K              | Clear Bit(s) in Register                  | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                    | Z,N,V              | 1       |

| INC              | Rd                | Increment                                 | Rd ← Rd + 1                                                                              | Z,N,V              | 1       |

| DEC              | Rd                | Decrement                                 | Rd ← Rd – 1                                                                              | Z,N,V              | 1       |

| TST              | Rd                | Test for Zero or Minus                    | $Rd \leftarrow Rd \bullet Rd$                                                            | Z,N,V              | 1       |

| CLR              | Rd                | Clear Register                            | Rd ← Rd ⊕ Rd                                                                             | Z,N,V              | 1       |

| SER              | Rd                | Set Register                              | $Rd \leftarrow 0xFF$                                                                     | None               | 1       |

| BRANCH INSTRUCT  | 1                 | Deletion lower                            |                                                                                          | News               | 0       |

| RJMP             | k                 | Relative Jump                             | $PC \leftarrow PC + k + 1$                                                               | None               | 2       |

| IJMP             | k                 | Indirect Jump to (Z)                      | $PC \leftarrow Z$ $PC \leftarrow PC + k + 1$                                             | None               | 2       |

| RCALL            | к                 | Relative Subroutine Call                  |                                                                                          | None               | -       |

| ICALL<br>RET     |                   | Indirect Call to (Z)<br>Subroutine Return | $PC \leftarrow Z$<br>$PC \leftarrow STACK$                                               | None<br>None       | 3 4     |

| RETI             |                   | Interrupt Return                          | $PC \leftarrow STACK$<br>$PC \leftarrow STACK$                                           | None               | 4       |

| CPSE             | Rd,Rr             | Compare, Skip if Equal                    | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                 | Nono               | 4       |

| CP               | Rd,Rr             | Compare                                   | Rd - Rr                                                                                  | None<br>Z, N,V,C,H | 1/2/3   |

| CPC              | Rd,Rr             | Compare with Carry                        | Rd – Rr – C                                                                              | Z, N,V,C,H         | 1       |

| CPI              | Rd,K              | Compare Register with Immediate           | Rd – K                                                                                   | Z, N,V,C,H         | 1       |

| SBRC             | Rr, b             | Skip if Bit in Register Cleared           | if $(Rr(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                        | None               | 1/2/3   |

| SBRS             | Rr, b             | Skip if Bit in Register is Set            | if $(Rr(b)=0)$ PC $\leftarrow$ PC + 2 or 3<br>if $(Rr(b)=1)$ PC $\leftarrow$ PC + 2 or 3 | None               | 1/2/3   |

| SBIC             | P, b              | Skip if Bit in I/O Register Cleared       | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                         | None               | 1/2/3   |

| SBIS             | P, b              | Skip if Bit in I/O Register is Set        | if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                         | None               | 1/2/3   |

| BRBS             | s, k              | Branch if Status Flag Set                 | if (SREG(s) = 1) then $PC \leftarrow PC+k + 1$                                           | None               | 1/2     |

| BRBC             | s, k              | Branch if Status Flag Cleared             | if (SREG(s) = 0) then $PC \leftarrow PC+k + 1$                                           | None               | 1/2     |

| BREQ             | k                 | Branch if Equal                           | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRNE             | k                 | Branch if Not Equal                       | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRCS             | k                 | Branch if Carry Set                       | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRCC             | k                 | Branch if Carry Cleared                   | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRSH             | k                 | Branch if Same or Higher                  | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRLO             | k                 | Branch if Lower                           | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRMI             | k                 | Branch if Minus                           | if (N = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRPL             | k                 | Branch if Plus                            | if (N = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRGE             | k                 | Branch if Greater or Equal, Signed        | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                                    | None               | 1/2     |

| BRLT             | k                 | Branch if Less Than Zero, Signed          | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1                                     | None               | 1/2     |

| BRHS             | k                 | Branch if Half Carry Flag Set             | if (H = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRHC             | k                 | Branch if Half Carry Flag Cleared         | if (H = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRTS             | k                 | Branch if T Flag Set                      | if (T = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRTC             | k                 | Branch if T Flag Cleared                  | if (T = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRVS             | k                 | Branch if Overflow Flag is Set            | if (V = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRVC             | k                 | Branch if Overflow Flag is Cleared        | if (V = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRIE             | k                 | Branch if Interrupt Enabled               | if (I = 1) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BRID             | k                 | Branch if Interrupt Disabled              | if (I = 0) then PC $\leftarrow$ PC + k + 1                                               | None               | 1/2     |

| BIT AND BIT-TEST | INSTRUCTIONS      |                                           |                                                                                          |                    |         |

| SBI              | P,b               | Set Bit in I/O Register                   | I/O(P,b) ← 1                                                                             | None               | 2       |

| CBI              | P,b               | Clear Bit in I/O Register                 | I/O(P,b) ← 0                                                                             | None               | 2       |

|                  | Rd                | Logical Shift Left                        | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                           | Z,C,N,V            | 1       |

| LSL              | Ru                | Edgloar on the Edit                       |                                                                                          |                    | -       |

| LSL<br>LSR       | Rd                | Logical Shift Right                       | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                           | Z,C,N,V            | 1       |

| Changes from Rev.                   |     |                                                                      |

|-------------------------------------|-----|----------------------------------------------------------------------|

| 2514F-08/04 to                      | 1.  | Updated "Features" on page 1.                                        |

| Rev. 2514G-10/04                    | 2.  | Updated "Pinout ATtiny2313" on page 2.                               |

|                                     | 3.  | Updated "Ordering Information" on page 217.                          |

|                                     | 4.  | Updated "Packaging Information" on page 218.                         |

|                                     | 5.  | Updated "Errata" on page 221.                                        |

|                                     | 0.  |                                                                      |

| Changes from Rev.                   |     |                                                                      |

| 2514E-04/04 to                      | 1.  | Updated "Features" on page 1.                                        |

| Rev. 2514F-08/04                    | 2.  | Updated "Alternate Functions of Port B" on page 55.                  |

|                                     | 3.  | Updated "Calibration Byte" on page 162.                              |

|                                     | 4.  | Moved Table 69 on page 162 and Table 70 on page 162 to "Page Size"   |

|                                     | 4.  | on page 162.                                                         |

|                                     | 5.  | Updated "Enter Programming Mode" on page 165.                        |

|                                     | 6.  | Updated "Serial Programming Algorithm" on page 175.                  |

|                                     | 7.  | Updated Table 78 on page 176.                                        |

|                                     | 8.  | Updated "DC Characteristics" on page 179.                            |

|                                     | 9.  | Updated "ATtiny2313 Typical Characteristics" on page 183.            |

|                                     | 10. | Changed occurences of PCINT15 to PCINT7, EEMWE to EEMPE and          |

|                                     |     | EEWE to EEPE in the document.                                        |

|                                     |     |                                                                      |

| Changes from Rev.                   |     |                                                                      |

| 2514D-03/04 to                      | 1.  | Speed Grades changed                                                 |

| Rev. 2514E-04/04                    |     | - 12MHz to 10MHz                                                     |

|                                     | -   | - 24MHz to 20MHz                                                     |

|                                     | 2.  | Updated Figure 1 on page 2.                                          |

|                                     | 3.  | Updated "Ordering Information" on page 217.                          |

|                                     | 4.  | Updated "Maximum Speed vs. VCC" on page 182.                         |

|                                     | 5.  | Updated "ATtiny2313 Typical Characteristics" on page 183.            |

| Changes from Day                    |     |                                                                      |

| Changes from Rev.<br>2514C-12/03 to |     | Undeted Table 2 on your 25                                           |

| Rev. 2514D-03/04                    | 1.  | Updated Table 2 on page 25.                                          |

| Rev. 2514D-03/04                    | 2.  | Replaced "Watchdog Timer" on page 41.                                |

|                                     | 3.  | Added "Maximum Speed vs. VCC" on page 182.                           |

|                                     | 4.  | "Serial Programming Algorithm" on page 175 updated.                  |

|                                     | 5.  | Changed mA to $\mu$ A in preliminary Figure 136 on page 209.         |