Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 25                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 256 x 8                                                              |

| RAM Size                   | 512 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f340k2t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to See "ELECTRICAL CHARACTERISTICS" on page 152. Legend / Abbreviations for Table 1:

Type: I = input, O = output, S = supply

Type:I = input, O = output, S = supInput level:A = Dedicated analog input

$\ln \rho (0) + \ln \rho (1) = \rho (0) + \rho (1) +$

In/Output level:  $C_T = CMOS 0.3V_{DD}/0.7V_{DD}$  with input trigger

Output level: HS = 20mA high sink (on N-buffer only)

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1</sup>), ana = analog

- Output:  $OD = open drain^{2}$ , PP = push-pull

The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

On the chip, each I/O port may have up to 8 pads. Pads that are not bonded to external pins are set in input pull-up configuration after reset through the option byte Package selection. The configuration of these pads must be kept at reset state to avoid added current consumption.

| I      | Pin    | n°     |                           |      | Le             | evel   |       |     | Ρ   | ort |     |      | Main               |                                         |                        |

|--------|--------|--------|---------------------------|------|----------------|--------|-------|-----|-----|-----|-----|------|--------------------|-----------------------------------------|------------------------|

| P32    | P44    | P48    | Pin Name                  | Type | ut             | out    |       | Inp | out |     | Out | tput | function<br>(after | Alternate F                             | unction                |

| LQFP32 | LQFP44 | LQFP48 |                           |      | Input          | Output | float | ndw | int | ana | OD  | РР   | reset)             |                                         |                        |

| 1      | 13     | 14     | V <sub>DDA</sub>          | S    |                |        |       |     |     |     |     |      | Analog Sup         | ply Voltage                             |                        |

| 2      | 14     | 15     | V <sub>SSA</sub>          | S    |                |        |       |     |     |     |     |      | Analog Gro         | und Voltage                             |                        |

| 3      | 15     | 16     | PF0/MCO/<br>AIN8          | I/O  | CT             |        | x     | e   | 1   | х   | х   | х    | Port F0            | Main clock out<br>(f <sub>OSC</sub> /2) | ADC Analog<br>Input 8  |

| 4      | 16     | 17     | PF1 (HS)/<br>BEEP         | I/O  | CT             | HS     | х     | e   | i1  |     | х   | х    | Port F1            | Beep signal output                      |                        |

|        | 17     | 18     | PF2 (HS)                  | I/O  | $C_T$          | HS     | Х     |     | ei1 |     | Х   | Х    | Port F2            |                                         |                        |

| 5      | 18     | 19     | PF4/<br>OCMP1_A/<br>AIN10 | I/O  | C <sub>T</sub> |        | x     | x   |     | х   | х   | х    | Port F4            | Timer A Output<br>Compare 1             | ADC Analog<br>Input 10 |

| 6      | 19     | 20     | PF6 (HS)/<br>ICAP1_A      | I/O  | CT             | HS     | х     | х   |     |     | х   | х    | Port F6            | Timer A Input Ca                        | pture 1                |

| 7      | 20     | 21     | PF7 (HS)/<br>EXTCLK_A     | I/O  | CT             | HS     | x     | х   |     |     | х   | х    | Port F7            | Timer A External                        | Clock Source           |

| -      | 21     | 22     | V <sub>DD_0</sub>         | S    |                |        |       |     |     |     |     |      | Digital Main       | Supply Voltage                          |                        |

| -      | 22     | 23     | V <sub>SS_0</sub>         | S    |                |        |       |     |     |     |     |      | Digital Grou       | ind Voltage                             |                        |

| 8      | 23     | 24     | PC0/<br>OCMP2_B/<br>AIN12 | I/O  | С <sub>Т</sub> |        | x     | x   |     | х   | х   | x    | Port C0            | Timer B Output<br>Compare 2             | ADC Analog<br>Input 12 |

| 9      | 24     | 27     | PC1/<br>OCMP1_B/<br>AIN13 | I/O  | CT             |        | x     | x   |     | х   | х   | х    | Port C1            | Timer B Output<br>Compare 1             | ADC Analog<br>Input 13 |

| 10     | 25     | 28     | PC2 (HS)/<br>ICAP2_B      | I/O  | C <sub>T</sub> | HS     | x     | х   |     |     | Х   | Х    | Port C2            | Timer B Input Ca                        | pture 2                |

47/

#### Table 1. Device Pin Description

| Address                                                                                                                             | Block   | Register<br>Label                                                                                                                                                        | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reset Status                                                                                          | Remarks                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 002Ch<br>002Dh                                                                                                                      | MCC     | MCCSR<br>MCCBCR                                                                                                                                                          | Main Clock Control/Status Register<br>MCC Beep Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h<br>00h                                                                                            | R/W<br>R/W                                                                                                                                                                                  |

| 002Eh<br>002Fh                                                                                                                      | AWU     | AWUCSR<br>AWUPR                                                                                                                                                          | AWU Control/Status Register<br>AWU Prescaler Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h<br>FFh                                                                                            | R/W<br>R/W                                                                                                                                                                                  |

| 0030h                                                                                                                               | WWDG    | WDGWR                                                                                                                                                                    | Window Watchdog Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7Fh                                                                                                   | R/W                                                                                                                                                                                         |

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Dh<br>003Eh<br>003Fh | TIMER A | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2HR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register<br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register<br>Timer A Output Compare 2 High Register<br>Timer A Output Compare 2 Low Register | 00h<br>00h<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>RAW |

| 0040h                                                                                                                               |         |                                                                                                                                                                          | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |                                                                                                                                                                                             |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Ch | TIMER B | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCLR<br>TBCLR<br>TBACLR<br>TBACLR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBOC2LR                    | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Output Compare 2 High Register<br>Timer B Output Compare 2 Low Register                                 | 00h<br>00h<br>xxh<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                | SCI     | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                                       | SCI Status Register<br>SCI Data Register<br>SCI Baud Rate Register<br>SCI Control Register 1<br>SCI Control Register 2<br>Reserved area<br>SCI Extended Receive Prescaler Register<br>SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                                                                                               | C0h<br>xxh<br>00h<br>x000 0000b<br>00h<br><br>00h<br>00h                                              | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                |

57

# FLASH PROGRAM MEMORY (Cont'd)

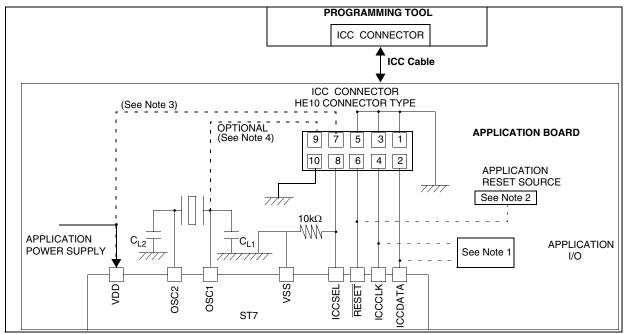

#### 4.4 ICC interface

ICP needs a minimum of 4 and up to 7 pins to be connected to the programming tool. These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input serial data pin

- ICCSEL: ICC selection

- OSC1: main clock input for external source (not required on devices without OSC1/OSC2 pins)

- $V_{DD}\!$ : application board power supply (optional, see Note 3)

#### Notes:

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values. 2. During the ICP session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

**3.** The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

**4.** Pin 9 has to be connected to the OSC1 pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

# Figure 6. Typical ICC Interface

# DATA EEPROM (Cont'd)

57

# Table 3. DATA EEPROM Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label    | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|-------------------|----------------------|---|---|---|---|---|---|------------|------------|

| 0020h             | EECSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | E2LAT<br>0 | E2PGM<br>0 |

# WINDOW WATCHDOG(Cont'd)

# Table 15. Watchdog Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 2A                | WDGCR             | WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 30                | WDGWR             | -    | W6 | W5 | W4 | W3 | W2 | W1 | W0 |

| 30                | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

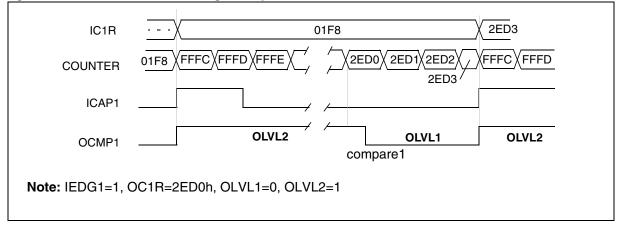

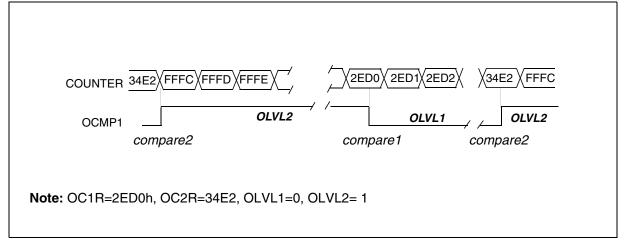

#### **16-BIT TIMER** (Cont'd)

#### 11.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OCIE bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the  $OC_iR$  value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

- OCFi bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR2 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} i \text{R} = \frac{\Delta t * f_{\text{CPU}}}{\text{PRESC}}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC} i \mathbb{R} = \Delta t \star f_{\text{EXT}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

# 16-BIT TIMER (Cont'd)

#### Figure 51. One Pulse Mode Timing Example

#### Figure 52. Pulse Width Modulation Mode Timing Example

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.4.5 Error Flags

#### 11.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's  $\overline{SS}$  pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

#### 11.4.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

- The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 11.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 0.1.3.2 Slave Select Management.

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

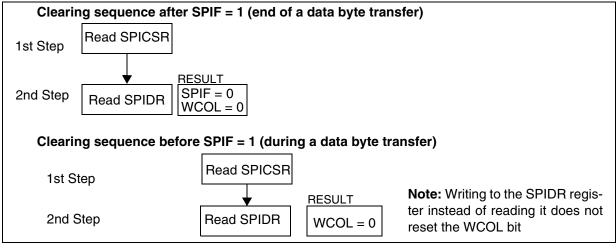

Clearing the WCOL bit is done through a software sequence (see Figure 6).

#### Figure 58. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

# SCI SERIAL COMMUNICATION INTERFACE (Cont'd)

# 11.5.7 Register Description

#### STATUS REGISTER (SCISR) Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

#### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note**: Data is not transferred to the shift register until the TDRE bit is cleared.

#### Bit 6 = TC Transmission complete.

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** *Received data ready flag.*

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when an Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new idle line occurs).

#### Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set, the RDR register content is not lost but the shift register is overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a desynchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate an interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it is transferred and only the OR bit is set.

#### Bit 0 = **PE** Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register. 0: No parity error

1: Parity error

# SCI SERIAL COMMUNICATION INTERFACE (Cont'd)

# DATA REGISTER (SCIDR)

#### Read/Write

#### Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 1).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 1).

# **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

#### Bits 7:6 = **SCP[1:0]** First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| 1                    | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | -    | 0    |

| 13                   |      | 1    |

Bits 5:3 = **SCT[2:0]** *SCI Transmitter rate divisor* These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |

|--------------------|------|------|------|

| 1                  |      | 0    | 0    |

| 2                  | _    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  |      | I    | 1    |

| 16                 |      | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 4    | 0    |

| 128                |      | I    | 1    |

**Note:** This TR factor is used only when the ETPR fine tuning factor is equal to 00h; otherwise, TR is replaced by the (TR\*ETPR) dividing factor.

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

| 1                  |      | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 4    | 0    |

| 8                  |      | 1    | 1    |

| 16                 |      | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 |      | -1   | 0    |

| 128                |      | I    | 1    |

**Note:** This RR factor is used only when the ERPR fine tuning factor is equal to 00h; otherwise, RR is replaced by the (RR\*ERPR) dividing factor.

# SCI SERIAL COMMUNICATION INTERFACE (Cont'd)

# EXTENDED RECEIVE PRESCALER DIVISION REGISTER (SCIERPR)

Read/Write

57

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ERPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

Bits 7:0 = **ERPR[7:0]** 8-bit Extended Receive Prescaler Register.

The extended Baud Rate Generator is activated when a value other than 00h is stored in this register. The clock frequency from the 16 divider (see Figure 3) is divided by the binary factor set in the SCIERPR register (in the range 1 to 255).

The extended baud rate generator is not active after a reset.

# EXTENDED TRANSMIT PRESCALER DIVISION REGISTER (SCIETPR)

Read/Write

Reset Value:0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ETPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

Bits 7:0 = **ETPR[7:0]** 8-bit Extended Transmit Prescaler Register.

The extended Baud Rate Generator is activated when a value other than 00h is stored in this register. The clock frequency from the 16 divider (see Figure 3) is divided by the binary factor set in the SCIETPR register (in the range 1 to 255).

The extended baud rate generator is not active after a reset.

# Table 22. Baud Rate Selection

|                                    |                            |                  | Co                       |                                                                                                                                                                                                                                               | Baud                                                           |                                                                        |      |

|------------------------------------|----------------------------|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|------|

| Symbol                             | Parameter                  | f <sub>CPU</sub> | Accuracy vs.<br>Standard | Prescaler                                                                                                                                                                                                                                     | Standard                                                       | Rate                                                                   | Unit |

| f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication<br>frequency | 8 MHz            | ~0.16%                   | Conventional Mode<br>TR (or RR) = 128, PR = 13<br>TR (or RR) = 32, PR = 13<br>TR (or RR) = 16, PR = 13<br>TR (or RR) = 8, PR = 13<br>TR (or RR) = 4, PR = 13<br>TR (or RR) = 16, PR = 3<br>TR (or RR) = 2, PR = 13<br>TR (or RR) = 1, PR = 13 | 300<br>1200<br>2400<br>4800<br>9600<br>10400<br>19200<br>38400 | ~1201.92<br>~2403.84<br>~4807.69<br>~9615.38<br>~10416.67<br>~19230.77 | Hz   |

|                                    |                            |                  | ~0.79%                   | Extended Mode<br>ETPR (or ERPR) = 35,<br>TR (or RR) = 1, PR = 1                                                                                                                                                                               | 14400                                                          | ~14285.71                                                              |      |

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### **11.6.4 Functional Description**

Refer to the CR, SR1 and SR2 registers in Section 11.6.7. for the bit definitions.

By default the I<sup>2</sup>C interface operates in Slave mode (M/SL bit is cleared) except when it initiates a transmit or receive sequence.

First the interface frequency must be configured using the FRi bits in the OAR2 register.

#### 11.6.4.1 Slave Mode

As soon as a start condition is detected, the address is received from the SDA line and sent to the shift register; then it is compared with the address of the interface or the General Call address (if selected by software).

**Note:** In 10-bit addressing mode, the comparision includes the header sequence (11110xx0) and the two most significant bits of the address.

**Header matched** (10-bit mode only): the interface generates an acknowledge pulse if the ACK bit is set.

Address not matched: the interface ignores it and waits for another Start condition.

Address matched: the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set.

- EVF and ADSL bits are set with an interrupt if the ITE bit is set.

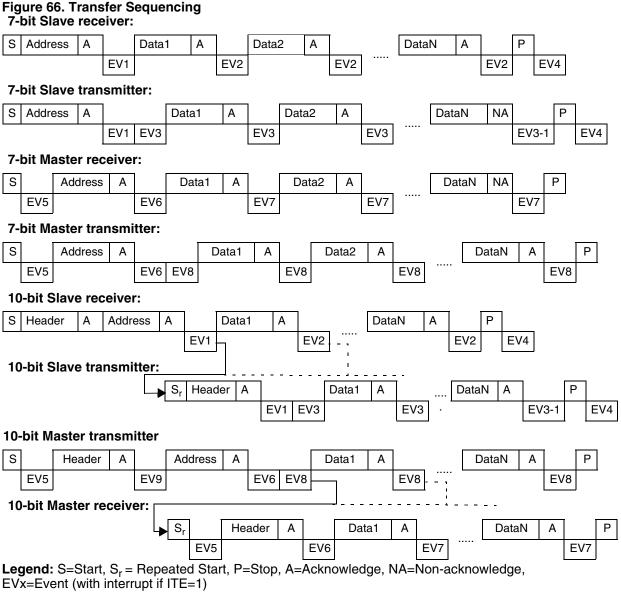

Then the interface waits for a read of the SR1 register, **holding the SCL line low** (see Figure 66 Transfer sequencing EV1).

Next, in 7-bit mode read the DR register to determine from the least significant bit (Data Direction Bit) if the slave must enter Receiver or Transmitter mode.

In 10-bit mode, after receiving the address sequence the slave is always in receive mode. It will enter transmit mode on receiving a repeated Start condition followed by the header sequence with matching address bits and the least significant bit set (11110xx1).

#### **Slave Receiver**

Following the address reception and after SR1 register has been read, the slave receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

EVF and BTF bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 66 Transfer sequencing EV2).

#### Slave Transmitter

Following the address reception and after SR1 register has been read, the slave sends bytes from the DR register to the SDA line via the internal shift register.

The slave waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 66 Transfer sequencing EV3).

When the acknowledge pulse is received:

The EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

#### **Closing slave communication**

After the last data byte is transferred a Stop Condition is generated by the master. The interface detects this condition and sets:

EVF and STOPF bits with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR2 register (see Figure 66 Transfer sequencing EV4).

#### **Error Cases**

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and the BERR bits are set with an interrupt if the ITE bit is set.

If it is a Stop then the interface discards the data, released the lines and waits for another Start condition.

If it is a Start then the interface discards the data and waits for the next slave address on the bus.

AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set with an interrupt if the ITE bit is set.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able

57

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

EV1: EVF=1, ADSL=1, cleared by reading SR1 register.

EV2: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

**EV3:** EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

**EV3-1:** EVF=1, AF=1, BTF=1; AF is cleared by reading SR1 register. BTF is cleared by releasing the lines (STOP=1, STOP=0) or by writing DR register (DR=FFh). **Note:** If lines are released by STOP=1, STOP=0, the subsequent EV4 is not seen.

**EV4:** EVF=1, STOPF=1, cleared by reading SR2 register.

EV5: EVF=1, SB=1, cleared by reading SR1 register followed by writing DR register.

EV6: EVF=1, cleared by reading SR1 register followed by writing CR register (for example PE=1).

EV7: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

EV8: EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

EV9: EVF=1, ADD10=1, cleared by reading SR1 register followed by writing DR register.

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Bit 1 = **M/SL** *Master/Slave*.

This bit is set by hardware as soon as the interface is in Master mode (writing START=1). It is cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration (ARLO=1). It is also cleared when the interface is disabled (PE=0).

0: Slave mode

1: Master mode

#### Bit 0 = SB Start bit (Master mode).

This bit is set by hardware as soon as the Start condition is generated (following a write START=1). An interrupt is generated if ITE=1. It is cleared by software reading SR1 register followed by writing the address byte in DR register. It is also cleared by hardware when the interface is disabled (PE=0).

0: No Start condition

1: Start condition generated

# I<sup>2</sup>C STATUS REGISTER 2 (SR2)

#### Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |    |       |      |      | 0    |

|---|---|---|----|-------|------|------|------|

| 0 | 0 | 0 | AF | STOPF | ARLO | BERR | GCAL |

Bit 7:5 = Reserved. Forced to 0 by hardware.

#### Bit 4 = **AF** Acknowledge failure.

This bit is set by hardware when no acknowledge is returned. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while AF=1 but by other flags (SB or BTF) that are set at the same time.

- 0: No acknowledge failure

- 1: Acknowledge failure

#### Bit 3 = **STOPF** Stop detection (Slave mode).

This bit is set by hardware when a Stop condition is detected on the bus after an acknowledge (if ACK=1). An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while STOPF=1.

- 0: No Stop condition detected

- 1: Stop condition detected

#### Bit 2 = **ARLO** Arbitration lost.

This bit is set by hardware when the interface loses the arbitration of the bus to another master. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

After an ARLO event the interface switches back automatically to Slave mode (M/SL=0).

The SCL line is not held low while ARLO=1.

0: No arbitration lost detected

1: Arbitration lost detected

Note:

- In a Multimaster environment, when the interface is configured in Master Receive mode it does not perform arbitration during the reception of the Acknowledge Bit. Mishandling of the ARLO bit from the I2CSR2 register may occur when a second master simultaneously requests the same data from the same slave and the I<sup>2</sup>C master does not acknowledge the data. The ARLO bit is then left at 0 instead of being set.

#### Bit 1 = **BERR** Bus error.

This bit is set by hardware when the interface detects a misplaced Start or Stop condition. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while BERR=1.

0: No misplaced Start or Stop condition

1: Misplaced Start or Stop condition

- Note:

- If a Bus Error occurs, a Stop or a repeated Start condition should be generated by the Master to re-synchronize communication, get the transmission acknowledged and the bus released for further communication

#### Bit 0 = GCAL General Call (Slave mode).

This bit is set by hardware when a general call address is detected on the bus while ENGC=1. It is cleared by hardware detecting a Stop condition (STOPF=1) or when the interface is disabled (PE=0).

0: No general call address detected on bus

1: general call address detected on bus

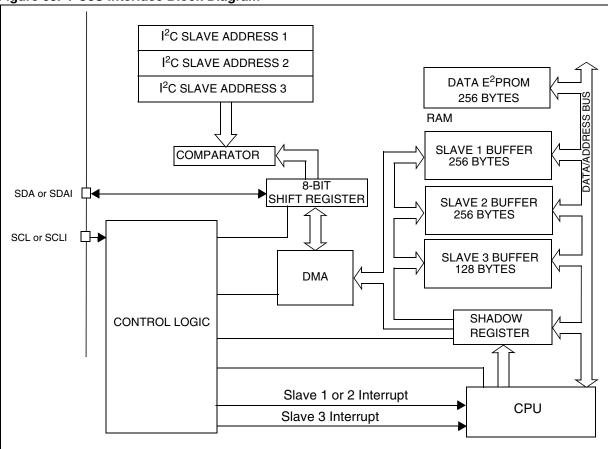

# 11.7 I2C TRIPLE SLAVE INTERFACE WITH DMA (I2C3S)

#### 11.7.1 Introduction

The l<sup>2</sup>C3S interface provides three l2C slave functions, supporting both standard (up to 100kHz) and fast l<sup>2</sup>C mode (100 to 400 kHz). Special features are provided for:

- Full-speed emulation of standard I<sup>2</sup>C E<sup>2</sup>PROMs

- Receiving commands to perform user-defined operations such as IAP

#### 11.7.2 Main Features

- Three user configurable independent slave addresses can be individually enabled

- 2x 256 bytes and 1x 128 bytes buffers with fixed addresses in RAM

- 7-bit Addressing

- DMA transfer to/from I<sup>2</sup>C bus and RAM

- Standard (transfers 256 bytes at up to 100 kHz)

# Figure 68. I<sup>2</sup>C3S Interface Block Diagram

- Fast Mode (transfers 256 bytes at up to 400 kHz)

- Transfer error detection and handling

- 3 interrupt flags per address for maximum flexibility

- Two interrupt request lines (one for Slaves 1 and 2, the other for Slave 3)

- Full emulation of standard I<sup>2</sup>C EEPROMs:

- Supports 5 read/write commands and combined format

- No I<sup>2</sup>C clock stretching

- Programmable page size (8/16 bytes) or full buffer

- Configurable write protection

- Data integrity and byte-pair coherency when reading 16-bit words from I<sup>2</sup>C bus

47/

# I<sup>2</sup>C3S INTERFACE (Cont'd)

#### 11.7.5.4 Rollover Handling

The RAM buffer of each slave is divided into pages whose length is defined according to PL1:0 bits in I2C3SCR1. Rollover takes place in these pages as described below.

In the case of Page Write, if the number of data bytes transmitted is more than the page length, the current address will roll over to the first byte of the current page and the previous data will be overwritten. This page size is configured using PL[1:0] bit in the I2C3SCR1 register.

In case of Sequential Read, if the current address register value reaches the memory address limit the address will roll over to the first address of the reserved area for the respective slave.

There is no status flag to indicate the roll over.

#### Note:

The reserved areas for slaves 1 and 2 have a limit of 256 bytes. The area for slave 3 is 128 bytes. The MSB of the address is hardwired, the addressing master therefore needs to send only an 8 bit address. The page boundaries are defined based on page size configuration using PL[1:0] bit in the I2C3SCR1 register. If an 8-byte page size is selected, the upper 5 bits of the RAM address are fixed and the lower 3 bits are incremented. For example, if the page write starts at register address 0x0C, the write will follow the sequence 0x0C, 0x0D, 0x0E, 0x0F, 0x08, 0x09, 0x0A, 0x0B. If a 16-byte page size is selected, the upper 4 bits of the RAM address are fixed and the lower 4 bits are incremented. For example if the page write starts at register address 0x0C, the write will follow the sequence 0x0C, 0x0D, 0x0E, 0x0F, 0x0B, 0x09, 0x0A, 0x0B.

#### 11.7.5.5 Error Conditions

- BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the BERR bit is set by hardware with an interrupt if ITER is set. During a stop condition, the interface discards the data, releases the lines and waits for another Start condition. However, a BERR on a Start condition will result in the interface discarding the data and waiting for the next slave address on the bus.

- NACK: Detection of a non-acknowledge bit not followed by a Stop condition. In this case, NACK bit is set by hardware with an interrupt if ITER is set.

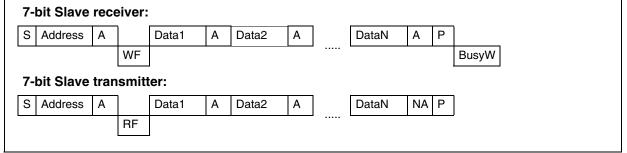

# Figure 72. Transfer Sequencing

Legend: S=Start, P=Stop, A=Acknowledge, NA=Non-acknowledge,

WF = WF event, WFx bit is set (with interrupt if ITWEx=1, after Stop or Restart conditions), cleared by reading the I2C3SSR register while no communication is ongoing.

RF = RF event, RFx is set (with interrupt if ITREx=1, after Stop or Restart conditions), cleared by reading the I2C3SSR register while no communication is ongoing.

BusyW = BusyW flag in the I2C3CR2 register set, cleared by software writing 0.

**Note:** The I2C3S supports a repeated start  $(S_r)$  in place of a stop condition (P).

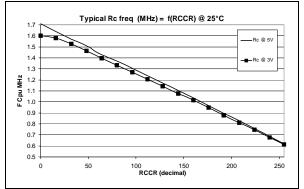

# Figure 85. Typical RC Frequency vs RCCR

# **13.6 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total de-

#### 13.6.1 Supply Current

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified

Symbol Parameter Conditions Max Unit Typ f<sub>CPU</sub>=8MHz<sup>1)</sup> 8.5 Supply current in RUN mode 13 f<sub>CPU</sub>=8MHz<sup>2)</sup> 3.7 Supply current in WAIT mode 6 mΑ f<sub>CPU</sub>=250kHz<sup>3)</sup> Supply current in SLOW mode 4.1 7 V<sub>DD</sub>=5.5V f<sub>CPU</sub>=250kHz<sup>4)</sup> Supply current in SLOW WAIT mode 2.2 3.5 IDD -40°C≤T<sub>A</sub>≤+85°C 10 Supply current in HALT mode<sup>5)</sup> 1 Supply current in AWUFH mode <sup>6)7)</sup> T<sub>4</sub>= +25°C 50 60 μΑ Supply current in Active Halt mode 6)7) T<sub>4</sub>= +25°C 500 700

#### Notes:

1. CPU running with memory access, all I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, LVD disabled.

2. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, LVD disabled.

3. SLOW mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, LVD disabled.

4. SLOW-WAIT mode selected with  $f_{CPU}$  based on  $f_{OSC}$  divided by 32. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load), all peripherals in reset state; clock input (OSC1) driven by external square wave, LVD disabled.

5. All I/O pins in output mode with a static value at  $V_{SS}$  (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max and  $f_{CPU}$  max.

6. All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load). Data tested in production at  $V_{DD}$  max. and  $f_{CPU}$  max.

7. This consumption refers to the Halt period only and not the associated run period which is software dependent.

vice consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

# **13.10 I/O PORT PIN CHARACTERISTICS**

#### **13.10.1 General Characteristics**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                | Parameter                                                                        | Conditions                         |                     | Min                   | Тур | Max                             | Unit             |

|-----------------------|----------------------------------------------------------------------------------|------------------------------------|---------------------|-----------------------|-----|---------------------------------|------------------|

| V <sub>IL</sub>       | Input low level voltage 1)                                                       |                                    |                     | V <sub>SS</sub> - 0.3 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V                |

| V <sub>IH</sub>       | Input high level voltage 1)                                                      |                                    |                     | 0.7xV <sub>DD</sub>   |     | V <sub>DD</sub> + 0.3           | v                |

| V <sub>hys</sub>      | Schmitt trigger voltage                                                          |                                    |                     |                       | 400 |                                 | mV               |

| ۱ <sub>L</sub>        | Input leakage current                                                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤ | ≤V <sub>DD</sub>    |                       |     | ±1                              |                  |

| ۱ <sub>S</sub>        | Static current consumption in-<br>duced by each floating input pin <sup>2)</sup> | Floating i                         | nput mode           |                       | 400 |                                 | μA               |

| D                     | Weak pull-up equivalent                                                          | V <sub>IN</sub> =V <sub>SS</sub>   | V <sub>DD</sub> =5V | 50                    | 120 | 250                             | kΩ               |

| R <sub>PU</sub>       | resistor <sup>3)</sup>                                                           | VIN=VSS                            | V <sub>DD</sub> =3V |                       | 160 |                                 | K22              |

| CIO                   | I/O pin capacitance                                                              |                                    |                     |                       | 5   |                                 | pF               |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>1)</sup>                                 | C <sub>L</sub> =50pF               |                     |                       | 25  |                                 | 20               |

| t <sub>r(IO)out</sub> | Output low to high level rise time <sup>1)</sup>                                 | Between 10% and 90%                |                     |                       | 25  |                                 | ns               |

| t <sub>w(IT)in</sub>  | External interrupt pulse time 4)                                                 |                                    |                     | 1                     |     |                                 | t <sub>CPU</sub> |

#### Notes:

1. Data based on validation/design results.

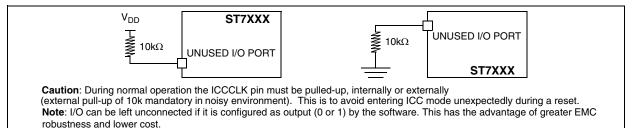

2. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see Figure 95). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

3. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor.

4. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

#### Figure 95. Two typical Applications with unused I/O Pin

166/191

# **15.2 DEVICE ORDERING INFORMATION**

# Table 33. Supported part numbers

| Part Number  | Peripherals                                                                                 | Program<br>Memory<br>(Bytes) | RAM<br>(Bytes) | Data<br>EEPROM<br>(Bytes) | Temp.<br>Range | Package |

|--------------|---------------------------------------------------------------------------------------------|------------------------------|----------------|---------------------------|----------------|---------|

| ST72F340K2T6 |                                                                                             | 8K FLASH                     | 512            |                           |                | LQFP32  |

| ST72F340S2T6 | Common peripherals<br>Common peripherals<br>+<br>10-bit ADC,                                | ON FLASH                     | 512            | 256                       | -40°C to 85°C  | LQFP44  |

| ST72F340K4T6 |                                                                                             | 16K FLASH                    | 1K             |                           |                | LQFP32  |

| ST72F340S4T6 |                                                                                             |                              |                |                           |                | LQFP44  |

| ST72F344K2T6 |                                                                                             | 8K FLASH<br>16K FLASH        | 512            |                           |                | LQFP32  |

| ST72F344S2T6 |                                                                                             |                              |                |                           |                | LQFP44  |

| ST72F344K4T6 |                                                                                             |                              | 1K             |                           |                | LQFP32  |

| ST72F344S4T6 | int high-accuracy 1MHz RC                                                                   |                              | IK             |                           |                | LQFP44  |

| ST72F345C4T6 | Common peripherals<br>+<br>I <sup>2</sup> C3SNS<br>10-bit ADC,<br>int high-accuracy 1MHz RC | 16K FLASH                    | 1K             | *                         |                | LQFP48  |

Contact ST sales office for product availability

#### 15.3 DEVELOPMENT TOOLS

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and thirdparty tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete, affordable hardware/software tool packages that include features and samples to help you quickly start developing your application.

#### 15.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16KBytes of code.

The range of hardware tools includes full-featured **ST7-EMU3 series emulators** and the low-cost

**RLink** in-circuit debugger/programmer. These tools are supported by the **ST7 Toolset** from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level language debugger, editor, project manager and integrated programming interface.

#### 15.3.3 Programming tools

During the development cycle, the **ST7-EMU3 se**ries emulators and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

### 15.3.4 Order codes for ST72F34x development tools

#### Table 34. Development tool order codes

|                                  |                                |               | Programming Tool                                     |                                                                |  |  |

|----------------------------------|--------------------------------|---------------|------------------------------------------------------|----------------------------------------------------------------|--|--|

| MCU                              | Starter kit                    | Emulator      | In-circuit debugger/<br>programmer                   | Dedicated programmer                                           |  |  |

| ST72F340<br>ST72F344<br>ST72F345 | ST72F34x-SK/RAIS <sup>1)</sup> | ST7MDT40-EMU3 | STX-RLINK <sup>2)</sup><br>ST7-STICK <sup>3)4)</sup> | ST7SB20J/xx <sup>3)5)</sup><br>ST7SB40-QP48/xx <sup>3)6)</sup> |  |  |

#### Notes:

1. USB connection to PC

2. RLink with ST7 tool set

3. Add suffix /EU, /UK or /US for the power supply for your region

4. Parallel port connection to PC

5. Only available for LQFP32 and LQFP44 packages

6. Only available for LQFP48 package

For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.