Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 4MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM, RF Mod                                        |

| Number of I/O              | 12                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 32-LQFP                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908rf2cfa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 6.6<br>6.6.1                                     | Configuration Register Option                                                                                                       |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 6.7<br>6.7.1<br>6.7.2<br>6.7.3<br>6.7.4<br>6.7.5 | I/O Registers86ICG Control Register88ICG Multiplier Register90ICG Trim Register90ICG DCO Divider Register90ICG DCO Stage Register90 |

|                                                  | Section 7. Keyboard/External Interrupt Module (KBI)                                                                                 |

| 7.1                                              | Introduction                                                                                                                        |

| 7.2                                              | Features                                                                                                                            |

| 7.3                                              | Functional Description                                                                                                              |

| 7.3.1                                            | External Interrupt                                                                                                                  |

| 7.3.2<br>7.3.3                                   | IRQ Pin       96         KBI Module During Break Interrupts       98                                                                |

| 7.3.4                                            | Keyboard Interrupt Pins                                                                                                             |

| 7.3.5                                            | Keyboard Initialization                                                                                                             |

| 7.4                                              | Low-Power Modes                                                                                                                     |

| 7.4.1<br>7.4.2                                   | Wait Mode                                                                                                                           |

| 7.5                                              | I/O Registers                                                                                                                       |

| 7.5.1                                            | IRQ and Keyboard Status and Control Register                                                                                        |

| 7.5.2                                            | Keyboard Interrupt Enable Register                                                                                                  |

|                                                  | Section 8. Low-Voltage Inhibit (LVI)                                                                                                |

| 8.1                                              | Introduction                                                                                                                        |

| 8.2                                              | Features                                                                                                                            |

| 8.3                                              | Functional Description                                                                                                              |

| 8.3.1                                            | False Trip Protection                                                                                                               |

| 8.3.2                                            | Short Stop Recovery Option                                                                                                          |

| 8.4                                              | LVI Status Register                                                                                                                 |

| 8.5                                              | LVI Interrupts                                                                                                                      |

| 8.6<br>8.6.1                                     | Wait Mode                                                                                                                           |

| 8.6.2                                            | Stop Mode                                                                                                                           |

|                                                  | Section 0. Input/Quantum (I/O) Porto                                                                                                |

| 0.4                                              | Section 9. Input/Output (I/O) Ports                                                                                                 |

| 9.1                                              | Introduction                                                                                                                        |

| 9.2<br>9.2.1                                     | Port A                                                                                                                              |

| 9.2.2                                            | Data Direction Register A                                                                                                           |

|                                                  |                                                                                                                                     |

|                                                  | MC68HC908RF2 — Rev. 4.                                                                                                              |

| 9.3 Port B                                                                                    |

|-----------------------------------------------------------------------------------------------|

| 9.3.1 Port B Data Register                                                                    |

| 9.3.2 Data Direction Register B                                                               |

| Section 10. System Integration Module (SIM)                                                   |

| 10.1 Introduction                                                                             |

| 10.2 SIM Bus Clock Control and Generation                                                     |

| 10.2.1 Bus Timing                                                                             |

| 10.2.2 Clock Startup from POR or LVI Reset                                                    |

| 10.2.3 Clocks in Stop Mode and Wait Mode                                                      |

| 10.3 Reset and System Initialization                                                          |

| 10.3.1 External Pin Reset                                                                     |

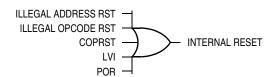

| 10.3.2 Active Resets from Internal Sources                                                    |

| 10.3.2.1 Power-On Reset                                                                       |

| 10.3.2.2 Computer Operating Properly (COP) Reset                                              |

| 10.3.2.4 Illegal Address Reset                                                                |

| 10.3.2.5 Low-Voltage Inhibit (LVI) Reset                                                      |

| 10.4 SIM Counter                                                                              |

| 10.4.1 SIM Counter During Power-On Reset                                                      |

| 10.4.2 SIM Counter During Stop Mode Recovery                                                  |

| 10.4.3 SIM Counter and Reset States                                                           |

| 10.5 Program Exception Control                                                                |

| 10.5.1 Interrupts                                                                             |

| 10.5.1.1       Hardware Interrupts       122         10.5.1.2       SWI Instruction       123 |

| 10.5.2 Reset                                                                                  |

| 10.5.3 Break Interrupts                                                                       |

| 10.5.4 Status Flag Protection in Break Mode                                                   |

| 10.6 Low-Power Modes                                                                          |

| 10.6.1 Wait Mode                                                                              |

| 10.6.2 Stop Mode                                                                              |

| 10.7 SIM Registers                                                                            |

| 10.7.1 SIM Break Status Register                                                              |

| 10.7.2 SIM Reset Status Register                                                              |

| 10.7.5 Silvi break riag Control Negister                                                      |

| Section 11. Timer Interface Module (TIM)                                                      |

| 11.1 Introduction                                                                             |

| 11.2 Features                                                                                 |

| 11.3 Pin Name Conventions 129                                                                 |

Memory Monitor ROM

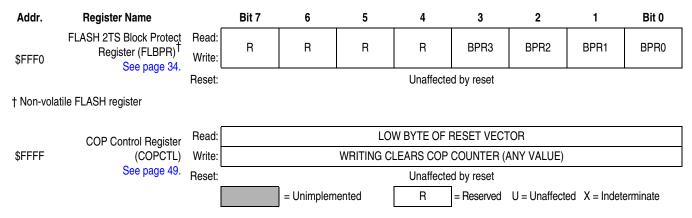

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

Table 2-1 is a list of vector locations.

**Address Vector** \$FFF2 ICG vector (high) ٥ \$FFF3 ICG vector (low) \$FFF4 TIM overflow vector (high) \$FFF5 TIM overflow vector (low) \$FFF6 TIM channel 1 vector (high) \$FFF7 TIM channel 1 vector (low) Priority TIM channel 0 vector (high) \$FFF8 \$FFF9 TIM channel 0 vector (low) \$FFFA IRQ/keyboard vector (high) \$FFFB IRQ/keyboard vector (low) \$FFFC SWI vector (high) \$FFFD SWI vector (low) \$FFFE Reset vector (high) High \$FFFF Reset vector (low)

**Table 2-1. Vector Locations**

#### 2.3 Monitor ROM

The 768 bytes at addresses \$F000–F2EF and \$FEF0–\$FEFF are utilized by the monitor ROM.

The address range \$F000–F2EF is reserved for the monitor code functions, FLASH memory programming, and erase algorithms.

The address range \$FEF0-\$FEFF holds reserved ROM addresses that contain the monitor code reset vectors.

34

#### 2.5.5 FLASH 2TS Block Protection

NOTE:

In performing a program or erase operation, the FLASH 2TS block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

Due to the ability of the on-board charge pump to erase and program the FLASH 2TS memory in the target application, provision is made for protecting blocks of memory from unintentional erase or program operations due to system malfunction. This protection is implemented by a reserved location in the memory for block protect information. This block protect register must be read before setting HVEN = 1. When the block protect register is read, its contents are latched by the FLASH 2TS control logic. If the address range for an erase or program operation includes a protected block, the PGM or ERASE bit is cleared which prevents the HVEN bit in the FLASH 2TS control register from being set such that no high-voltage operation is allowed in the array.

When the block protect register is erased (all 0s), the entire memory is accessible for program and erase. When bits within the register are programmed, they lock blocks of memory address ranges as shown in **2.5.6 FLASH 2TS Block Protect Register**. The block protect register itself can be erased or programmed only with an external voltage  $V_{TST}$  present on the  $\overline{IRQ}$  pin. The presence of  $V_{TST}$  on the  $\overline{IRQ}$  pin also allows entry into monitor mode out of reset. Therefore, the ability to change the block protect register is voltage-level dependent and can occur in either user or monitor modes.

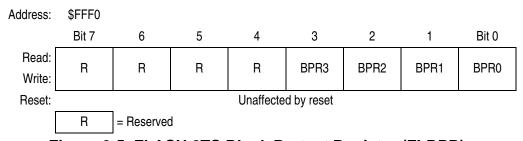

#### 2.5.6 FLASH 2TS Block Protect Register

The block protect register (FLBPR) is implemented as a byte within the FLASH 2TS memory. Each bit, when programmed, protects a range of addresses in the FLASH 2TS.

Figure 2-5. FLASH 2TS Block Protect Register (FLBPR)

BPR3 — Block Protect Register Bit 3

This bit protects the memory contents in the address ranges \$7A00–\$7FEF and \$FFF0–\$FFFF.

- 1 = Address range protected from erase or program

- 0 = Address range open to erase or program

The row whose cycling bit is different will be erased and the entire row will be programmed with the given data, including a toggled version of the cycling bit.

#### 2.5.8.5 Example Routine Calls

This code is for illustrative purposes only and does not represent valid syntax for any particular assembler.

```

RAM

EQU

$80

RDVRRNG

EQU

$F000

EQU

$F003

PRGRNGE

ERANRGE

EQU

$F006

REDPROG

EQU

$F009

RAM Definitions for Subroutines

ORG

RAM+8

CTRLBYT

RMB

CPUSPD

RMB

LADDR

RMB

BUMPS

RMB

RMB

DERASE

;Allocation of "DATA" space is dependent on the device and

;application

DATA

RMB

; CALLING EXAMPLE FOR READ/VERIFY A RANGE (RDVRRNG)

#$FF

;TARGET IS RAM

LDA

LDHX

#$7807

; END AFTER FIRST ROW

LADDR

STHX

LDHX

#$7800

;START AT FIRST ROW

RDVRRNG

; DATA WILL CONTAIN FLASH INFO

CALLING EXAMPLE FOR ERASE A RANGE (RNGEERA)

MOV

;Load Bus frequency in MHz * 4

#$08,CPUSPD

;Bits 5&6 hold the block size to erase

VOM

#$60,CTRLBYT

;00 Full Array

;20 One-Half Array

;40 Eight Rows

;60 Singe Row

; Remember a Row is 1 byte

;Set erase time in uS/24, number in

;decimal

LDHX

#100000/24

STHX

DERASE

```

MC68HC908RF2 — Rev. 4.0

Data Sheet

39

#### **Memory**

```

#$7800

LDHX

; Address in the range to erase

JSR

ERARNGE

; Call through jump table

; CALLING EXAMPLE FOR PROGRAM A RANGE (RNGEPROG)

#'P', DATA

MOV

#'R', DATA+1

VOM

VOM

#'0', DATA+2

#'G', DATA+3

MOV

#'T', DATA+4

MOV

#'E', DATA+5

MOV

#'S', DATA+6

VOM

VOM

#'T', DATA+7

VOM

#$08, CPUSPD

;Load Bus frequency in MHz * 4

;Load max number of programming steps

VOM

#$OA,BUMPS

; before a failure is returned

LDHX

#$7807

;Load the last address to program

STHX

LADDR

;into LADDR

#$7800

;Load the first address to program

LDHX

;into H:X

; This range may cross page boundaries

; and may be any length, so long as the

; data to program is loaded in RAM

; beginning at DATA.

JSR

PRGRNGE

; Call through jump table.

; CALLING EXAMPLE FOR REDUNDANT PROGRAM A ROW (REDPROG)

VOM

#$56, DATA

VOM

#'P', DATA+1

MOV

#'R', DATA+2

#'O', DATA+3

MOV

#'G', DATA+4

MOV

#'R', DATA+5

MOV

VOM

#'E', DATA+6

#'D', DATA+7

MOV

MOV

#$08, CPUSPD

;Load Bus frequency in MHz * 4

VOM

#$OA,BUMPS

;Load max number of programming steps

; before a failure is returned

;Set erase time in uS/24

#100000/24

LDHX

STHX

DERASE

LDHX

#$7808

;Load the last address of the multi-row

; range; (in this case, 2 rows)

STHX

LADDR

;into LADDR

LDHX

#$7800

;Load the first address of the

;multi-row range into H:X

; Call through jump table.

JSR

REDPROG

```

### **Central Processor Unit (CPU)**

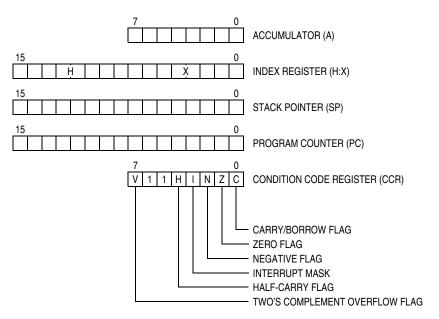

#### 5.3 CPU Registers

**Figure 5-1** shows the five CPU registers. CPU registers are not part of the memory map.

Figure 5-1. CPU Registers

#### 5.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 5-2. Accumulator (A)

### **Internal Clock Generator Module (ICG)**

### 6.6 Configuration Register Option

One configuration register option affects the functionality of the ICG: EXTSLOW (slow external clock).

All configuration register options will have a default setting. Refer to **Section 3. Configuration Register (CONFIG)** on how the configuration register is used.

#### 6.6.1 EXTSLOW

Slow external clock (EXTSLOW), when set, will decrease the drive strength of the oscillator amplifier, enabling low-frequency crystal operation (30 kHz–100 kHz). When clear, EXTSLOW enables high frequency crystal operation (1 MHz to 8 MHz).

EXTSLOW, when set, also configures the clock monitor to expect an external clock source that is slower than the low-frequency base clock (60 Hz–307.2 kHz). When EXTSLOW is clear, the clock monitor will expect an external clock faster than the low-frequency base clock (307.2 kHz–32 MHz).

The default state for this option is clear.

#### 6.7 I/O Registers

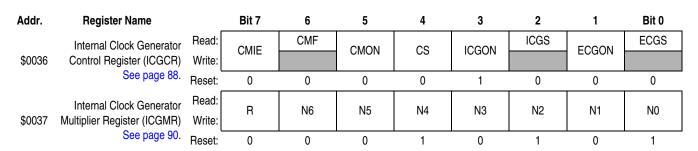

The ICG contains five registers, summarized in **Figure 6-10**. These registers are:

- ICG control register, ICGCR

- ICG multiplier register, ICGMR

- ICG trim register, ICGTR

- ICG DCO divider control register, ICGDVR

- ICG DCO stage control register, ICGDSR

Several of the bits in these registers have interaction where the state of one bit may force another bit to a particular state or prevent another bit from being set or cleared. A summary of this interaction is shown in **Table 6-5**.

Figure 6-10. ICG I/O Register Summary

### **Internal Clock Generator Module (ICG)**

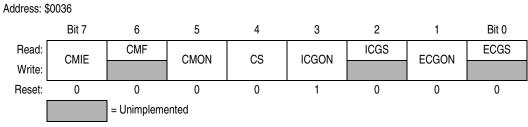

#### 6.7.1 ICG Control Register

The ICG control register (ICGCR) contains the control and status bits for the internal clock generator, external clock generator, and clock monitor as well as the clock select and interrupt enable bits.

Figure 6-11. ICG Control Register (ICGCR)

#### CMIE — Clock Monitor Interrupt Enable Bit

This read/write bit enables clock monitor interrupts. An interrupt will occur when both CMIE and CMF are set. CMIE can be set when the CMON bit has been set for at least one cycle. CMIE is forced clear when CMON is clear or during reset.

- 1 = Clock monitor interrupts enabled

- 0 = Clock monitor interrupts disabled

#### CMF — Clock Monitor Interrupt Flag

This read-only bit is set when the clock monitor determines that either ICLK or ECLK becomes inactive and the CMON bit is set. This bit is cleared by first reading the bit while it is set, followed by writing the bit low. This bit is forced clear when CMON is clear or during reset.

- 1 = Either ICLK or ECLK has become inactive.

- 0 = ICLK and ECLK have not become inactive since the last read of the ICGCR or the clock monitor is disabled.

#### CMON — Clock Monitor On Bit

This read/write bit enables the clock monitor. CMON can be set when both ICLK and ECLK have been on and stable for at least one bus cycle (ICGON, ECGON, ICGS, and ECGS are all set). CMON is forced set when CMF is set, to avoid inadvertent clearing of CMF. CMON is forced clear when either ICGON or ECGON is clear or during reset.

- 1 = Clock monitor output enabled

- 0 = Clock monitor output disabled

### Low-Voltage Inhibit (LVI)

In addition to forcing a reset condition, the LVI module has a second circuit dedicated to low-voltage detection. When  $V_{DD}$  falls below  $V_{LVS}$ , the output of the low-voltage comparator asserts the LOWV flag in the LVI status register (LVISR). In applications that require detecting low batteries, software can monitor by polling the LOWV bit.

#### 8.3.1 False Trip Protection

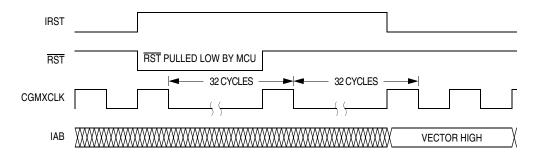

The  $V_{DD}$  pin level is digitally filtered to reduce false dead battery detection due to power supply noise. For the LVI module to reset due to a low-power supply,  $V_{DD}$  must remain at or below the  $V_{LVR}$  level for a minimum 32–40 CGMXCLK cycles. See **Table 8-1**.

LVI is guaranteed to generate

a reset

**Table 8-1. LOWV Bit Indication**

#### 8.3.2 Short Stop Recovery Option

$V_{DD} < V_{IVR}$

The LVI has an enable time of  $t_{\rm EN}$ . The system stabilization time for power-on reset and long stop recovery (both 4096 CGMXCLK cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 CGMXCLK delay must be greater than the LVI turn on time to avoid a period in startup where the LVI is not protecting the MCU.

NOTE:

The LVI is enabled automatically after reset or stop recovery, if the LVISTOP of the CONFIG register is set. (See **Section 3. Configuration Register (CONFIG)**.)

Data Sheet MC68HC908RF2 — Rev. 4.0

> 40 CGMXCLK cycles

Input/Output (I/O) Ports

Port B

#### TCH0 — Timer Channel I/O Bit

The PTB2/TCH0 pin is the TIM channel 0 input capture/output compare pin. The edge/level select bits, ELS0B:ELS0A, determine whether the PTB2/TCH0 pin is a timer channel I/O or a general-purpose I/O pin. See **Section 11. Timer Interface Module (TIM)**.

#### TCLK — Timer Clock Bit

The PTB3/TCLK pin is the external clock input for TIM. The prescaler select bits, PS[2:0], select PTB3/TCLK as the TIM clock input. (See 11.8.1 TIM Status and Control Register.) When not selected as the TIM clock, PTB3/TCLK is available for general-purpose I/O.

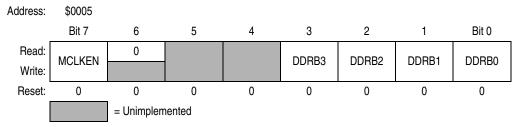

#### MCLK — Bus Clock Bit

The bus clock (MCLK) is driven out of pin PTB0/MCLK when enabled by the MCLKEN bit in port B data direction register bit 7.

#### 9.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 9-6. Data Direction Register B (DDRB)

#### MCLKEN — MCLK Enable Bit

This read/write bit enables MCLK to be an output signal on PTB0. If MCLK is enabled, PTB0 is under the control of MCLKEN. Reset clears this bit.

- 1 = MCLK output enabled

- 0 = MCLK output disabled

#### DDRB[3:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[3:0], configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

# **NOTE:** Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

Figure 9-7 shows the port B I/O logic.

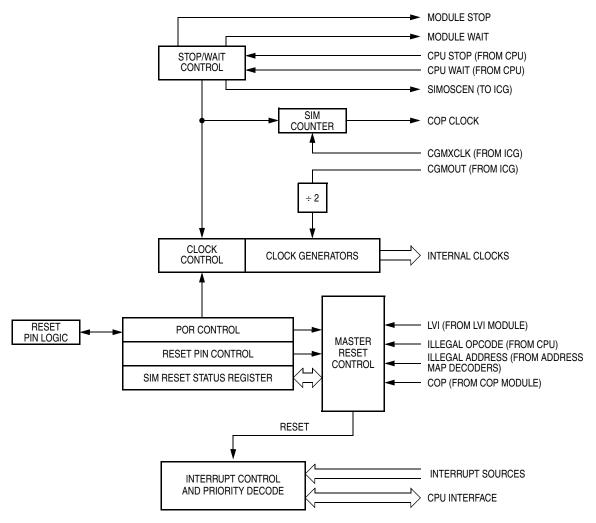

### **System Integration Module (SIM)**

Figure 10-2. SIM Block Diagram

Table 10-1 shows the internal signal names used in this section.

**Table 10-1. Signal Name Conventions**

| Signal Name | Description                                                      |

|-------------|------------------------------------------------------------------|

| CGMXCLK     | Selected clock source from internal clock generator module (ICG) |

| CGMOUT      | Clock output from ICG module (bus clock = CGMOUT divided by two) |

| ICLK        | Output from internal clock generator                             |

| ECLK        | External clock source                                            |

| IAB         | Internal address bus                                             |

| IDB         | internal data bus                                                |

| PORRST      | Signal from the power-on reset module to the SIM                 |

| IRST        | Internal reset signal                                            |

| R/W         | Read/write signal                                                |

System Integration Module (SIM) Reset and System Initialization

signal then follows the sequence from the falling edge of  $\overline{\text{RST}}$  shown in **Figure 10-5**.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

Figure 10-5. Internal Reset Timing

Figure 10-6. Sources of Internal Reset

#### 10.3.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin (RST) is held low while the SIM counter counts out 4096 CGMXCLK cycles. Another 64 CGMXCLK cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power-on, these events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables CGMOUT.

- Internal clocks to the CPU and modules are held inactive for 4096 CGMXCLK cycles to allow stabilization of the oscillator.

- The RST pin is driven low during the oscillator stabilization time.

- The POR bit of the SIM reset status register (SRSR) is set and all other bits in the register are cleared.

Timer Interface Module (TIM)

Functional Description

#### 11.4.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs or the TIM clock pin, TCLK. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

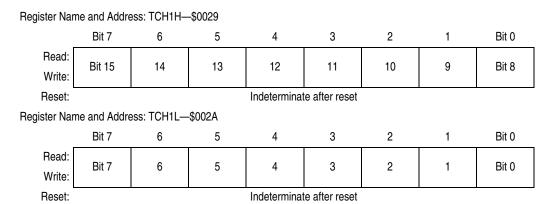

#### 11.4.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH and TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM CPU interrupt requests.

**NOTE:** TIM channel 1 should not be configured in this mode.

#### 11.4.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM channel 0 can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests for both TIM channel 0 and TIM channel 1.

**NOTE:** TIM channel 1 does not have an external pin associated with it.

#### 11.4.4 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in **11.4.3 Output Compare**. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use these methods to synchronize unbuffered changes in the output compare value on channel x:

When changing to a smaller value, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current output compare pulse. The interrupt routine has until the end of the counter overflow period to write the new value.

### Timer Interface Module (TIM)

TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

#### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

**NOTE:** Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode.

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000.

TRST is cleared automatically after the TIM counter is reset and always reads as 0. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

**NOTE:** Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

#### PS2-PS0 — Prescaler Select Bits

These read/write bits select either the TCLK pin or one of the seven prescaler outputs as the input to the TIM counter as **Table 11-2** shows. Reset clears the PS2–PS0 bits.

**Table 11-2. Prescaler Selection**

| PS2-PS0 | TIM Clock Source        |  |  |  |  |

|---------|-------------------------|--|--|--|--|

| 000     | Internal bus clock ÷1   |  |  |  |  |

| 001     | Internal bus clock ÷ 2  |  |  |  |  |

| 010     | Internal bus clock ÷ 4  |  |  |  |  |

| 011     | Internal bus clock ÷ 8  |  |  |  |  |

| 100     | Internal bus clock ÷ 16 |  |  |  |  |

| 101     | Internal bus clock ÷ 32 |  |  |  |  |

| 110     | Internal bus clock ÷ 64 |  |  |  |  |

| 111     | TCLK                    |  |  |  |  |

### **Timer Interface Module (TIM)**

| Register Name and Address: TCH0H—\$0026 |                                  |    |    |    |    |    |   |       |

|-----------------------------------------|----------------------------------|----|----|----|----|----|---|-------|

|                                         | Bit 7                            | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

| Read:<br>Write:                         | Bit 15                           | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset: Indeterminate after reset        |                                  |    |    |    |    |    |   |       |

| Register Name and Address: TCH0L—\$0027 |                                  |    |    |    |    |    |   |       |

|                                         | Bit 7                            | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

| Read:<br>Write:                         | Bit 7                            | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

| Reset:                                  | leset: Indeterminate after reset |    |    |    |    |    |   |       |

Figure 11-10. TIM Channel 0 Registers (TCH0H and TCH0L)

Figure 11-11. TIM Channel 1 Registers (TCH1H and TCH1L)

#### Data Sheet — MC68HC908RF2

### Section 12. PLL Tuned UHF Transmitter Module

#### 12.1 Introduction

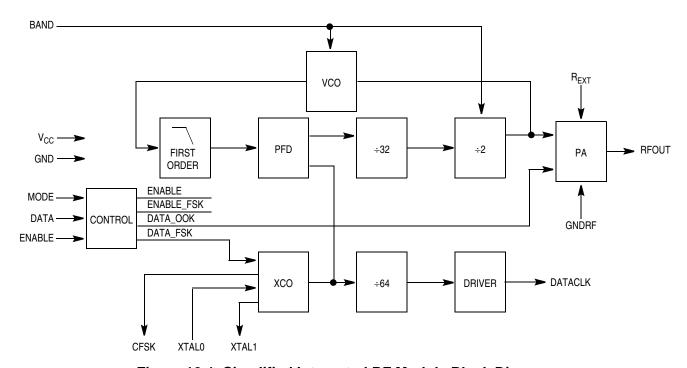

This section describes the integrated radio frequency (RF) module. This module integrates an ultra high frequency (UHF) transmitter offering these key features:

- Switchable frequency bands: 315, 434, and 868 MHz

- On/off keying (OOK) and frequency shift keying (FSK) modulation

- Adjustable output power range

- Fully integrated voltage-controlled oscillator (VCO)

- Supply voltage range: 1.9 to 3.7 V

- Very low standby current: 0.5 nA @ T<sub>A</sub> = 25°C

- Low supply voltage shutdown

- Data clock output for microcontroller

- Low external component count

Architecture of the module is described in Figure 12-1.

Figure 12-1. Simplified Integrated RF Module Block Diagram

**Electrical Specifications**

1.8-Volt to 3.3-Volt DC Electrical Characteristics Excluding UHF Module

#### 14.5 1.8-Volt to 3.3-Volt DC Electrical Characteristics Excluding UHF Module

| Characteristic <sup>(1)</sup>                                                                                                                       | Symbol                              | Min                                          | Typ <sup>(2)</sup>  | Max                     | Unit                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|---------------------|-------------------------|----------------------|

| Output high voltage (I <sub>Load</sub> = -1.2 mA) (I <sub>Load</sub> = -2.0 mA)                                                                     | V <sub>OH</sub>                     | V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -1.0 | _                   |                         | V                    |

| Output low voltage (I <sub>Load</sub> = 1.2 mA) (I <sub>Load</sub> = 3.0 mA) (I <sub>Load</sub> = 3.0 mA) PTA7–PTA0 only                            | V <sub>OL</sub>                     | _<br>_<br>_                                  | _<br>_<br>_         | 0.3<br>1.0<br>0.3       | V                    |

| Input high voltage, all ports, IRQ1, OSC1                                                                                                           | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>                        | _                   | V <sub>DD</sub> + 0.3   | V                    |

| Input low voltage, all ports, IRQ1, OSC1                                                                                                            | V <sub>IL</sub>                     | V <sub>SS</sub>                              | _                   | 0.3 x V <sub>DD</sub>   | V                    |

| $V_{DD}$ supply current<br>Run <sup>(3)</sup> (f <sub>op</sub> = 2.0 MHz)<br>Wait <sup>(4)</sup> (f <sub>op</sub> = 2.0 MHz)<br>Stop <sup>(5)</sup> | I <sub>DD</sub>                     | _<br>_<br>_                                  | _<br>_<br>10        | 4.3<br>1.2<br>—         | mA<br>mA<br>nA       |

| 25°C -40°C to 85°C -40°C to 125°C 25°C with LVI enabled -40°C to 85°C with LVI enabled                                                              |                                     | _<br>_<br>_<br>_                             | —<br>800<br>50<br>— | 100<br>1100<br>—<br>350 | nA<br>nA<br>μA<br>μA |

| I/O ports high-impedance leakage current <sup>(6)</sup>                                                                                             | I <sub>IL</sub>                     | _                                            | _                   | ± 1                     | μΑ                   |

| Input current                                                                                                                                       | I <sub>In</sub>                     | _                                            | _                   | ± 1                     | μΑ                   |

| Capacitance Ports (as input or output)                                                                                                              | C <sub>Out</sub><br>C <sub>In</sub> |                                              | _                   | 12<br>8                 | pF                   |

| POR re-arm voltage <sup>(7)</sup>                                                                                                                   | V <sub>POR</sub>                    | 0                                            | _                   | 200                     | mV                   |

| POR reset voltage <sup>(8)</sup>                                                                                                                    | V <sub>POR</sub>                    | 0                                            | 700                 | 800                     | mV                   |

| POR rise time ramp rate <sup>(9)</sup>                                                                                                              | R <sub>POR</sub>                    | 0.02                                         | _                   | _                       | V/ms                 |

| Monitor mode entry voltage                                                                                                                          | V <sub>HI</sub>                     | V <sub>DD</sub> + 2.5                        | _                   | 8                       | V                    |

| Pullup resistor, PTA6–PTA1, IRQ                                                                                                                     | R <sub>PU</sub>                     | 50                                           | 80                  | 120                     | kΩ                   |

- 1. Parameters are design targets at V<sub>DD</sub> = 1.8 V to 3.3 V, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, unless otherwise noted

- 2. Typical values reflect average measurements at midpoint of voltage range, 25°C only.

- 3. Run (operating)  $I_{DD}$  measured using internal clock generator module ( $f_{op}$ = 2.0 MHz).  $V_{DD}$  = 3.3 Vdc. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs.  $C_L$  = 20 pF. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 4. Wait I<sub>DD</sub> measured using internal clock generator module, f<sub>op</sub> = 2.0 MHz. All inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs. C<sub>L</sub> = 20 pF. OSC2 capacitance linearly affects wait I<sub>DD</sub>. All ports configured as inputs.

5. Stop I<sub>DD</sub> measured with no port pins sourcing current, all modules disabled except as noted.

- 6. Pullups and pulldowns are disabled.

- 7. Maximum is highest voltage that POR is guaranteed.

- 8. Maximum is highest voltage that POR is possible.

- 9. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

MC68HC908RF2 — Rev. 4.0

**Data Sheet**

Electrical Specifications UHF Transmitter Module

| Parameter                                                    | Test Conditions and Comments                                                          | Min          | Тур        | Max         | Unit           |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|------------|-------------|----------------|

| Supply voltage                                               |                                                                                       | _            | 3          | 3.7         | V              |

|                                                              | $T_A = -40^{\circ}C$                                                                  | _            | 2.04       | 2.11        | V              |

|                                                              | T <sub>A</sub> = -20°C                                                                | _            | 1.99       | 2.06        | V              |

| Shutdown voltage                                             | T <sub>A</sub> = 25°C                                                                 | _            | 1.86       | 1.95        | V              |

| threshold                                                    | T <sub>A</sub> = 60°C                                                                 | _            | 1.76       | 1.84        | V              |

|                                                              | T <sub>A</sub> = 85°C                                                                 | _            | 1.68       | 1.78        | V              |

|                                                              | T <sub>A</sub> = 125°C                                                                | _            | 1.56       | 1.67        | V              |

| RF Parameters                                                | (assuming a 50 $\Omega$ matching network                                              | connected to | o the D.U. | T. output)  |                |

| R <sub>EXT</sub> value                                       |                                                                                       | 12           |            | 21          | kΩ             |

|                                                              | 315 and 434 MHz bands, with 50 $\Omega$ matching network                              | _            | 5          | _           | dBm            |

| Output                                                       | 868 MHz band, with 50 $\Omega$ matching network                                       | _            | 1          | _           | dBm            |

| Output power                                                 | 315 and 434 MHz bands, $-40^{\circ}\text{C} \le T_{\text{A}} \le 125^{\circ}\text{C}$ | -3           | 0          | 3           | dBm            |

|                                                              | 868 MHz band,<br>$-40$ °C $\leq$ T <sub>A</sub> $\leq$ 125°C                          | -7           | -3         | 0           | dBm            |

| Current and output power variation vs R <sub>EXT</sub> value | 314 and 434 MHz bands,<br>with 50 Ω matching network                                  | _            | -0.35      | _           | dB/kΩ<br>mA/kΩ |

|                                                              | 315 and 434 MHz bands, with 50 Ω matching network                                     | _            | -34        | _           | dBc            |

| Harmonic 2 level                                             | 868 MHz band, with 50 $\Omega$ matching network                                       | _            | -49        | _           | dBc            |

|                                                              | 315 and 434 MHz bands                                                                 | _            | -23        | -17         | dBc            |

|                                                              | 868 MHz band                                                                          | _            | -38        | -27         | dBc            |

|                                                              | 315 and 434MHz bands, with 50 Ω matching network                                      | _            | -32        | _           | dBc            |

| Harmonic 3 level                                             | 868 MHz band, with 50 $\Omega$ matching network                                       | _            | -57        | _           | dBc            |

|                                                              | 315 and 434 MHz bands                                                                 | _            | -21        | -15         | dBc            |

|                                                              | 868 MHz band                                                                          | _            | -48        | -39         | dBc            |

| Spurious level                                               | 315 and 434 MHz bands                                                                 | _            | -36        | -24         | dBc            |

| @ f <sub>Carrier</sub> ± f <sub>DATACLK</sub>                | 868 MHz band                                                                          |              | -29        | -17         | dBc            |

| Spurious level                                               | 315 MHz band                                                                          | _            | -37        | -30         | dBc            |

| @ f <sub>Carrier</sub> ± f <sub>Reference</sub>              | 434 MHz band                                                                          |              | -44        | -34         | dBc            |

|                                                              | 868 MHz band                                                                          |              | -37        | -27         | dBc            |

| Spurious level                                               | 315 MHz bands                                                                         | _            | -62        | <b>-</b> 53 | dBc            |

| @ f <sub>Carrier</sub> /2                                    | 434 MHz bands                                                                         | _            | -80        | -60         | dBc            |

|                                                              | 868 MHz band                                                                          | _            | -45        | -39         | dBc            |

Table concluded on next page

MC68HC908RF2 — Rev. 4.0

Data Sheet

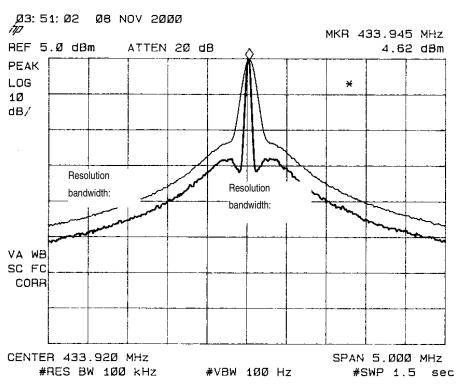

Figure 14-1. RF Spectrum at 434-MHz Frequency Band Displayed with a 5-MHz Span

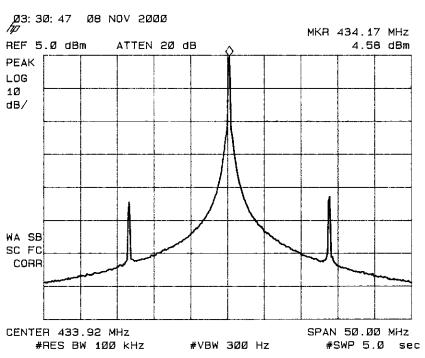

Figure 14-2. RF Spectrum at 434-MHz Frequency Band Displayed with a 50-MHz Span