Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 4MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | LVD, POR, PWM, RF Mod                                        |

| Number of I/O              | 12                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 32-LQFP                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908rf2mfa |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

## **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                                                        | Page<br>Number(s) |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                   |                   | First bulleted paragraph under the subsection <b>11.5 Interrupts</b> reworded for clarity                                                                          | 137               |

|                   |                   | Revision to the description of the CHxMAX bit and the note that follows that description                                                                           | 145               |

| June, 1.0<br>2001 |                   | 14.2 Absolute Maximum Ratings — ESD HBM and ESD MM entries added                                                                                                   | 171               |

|                   | · 10              | <b>14.8 UHF Transmitter Module</b> — Table entries and figures revised throughout                                                                                  | 176               |

|                   |                   | <b>14.11 LVI Characteristics</b> — $V_{LVS}$ and $V_{LVR}$ specifications updated — low voltage reset and detection entries deleted                                | 183               |

|                   |                   | <b>14.12 Memory Characteristics</b> — Maximum value for FLASH page program pulses updated                                                                          | 184               |

| December,<br>2001 | 2.0               | <b>Section 11. Timer Interface Module (TIM)</b> — Timer discrepancies corrected throughout this section.                                                           | 129               |

| March,<br>2004    | 3.0               | Document reformatted to meet current publications standards                                                                                                        | Throughout        |

|                   |                   | 1.2 Features — Added –40°C to 125°C operation.                                                                                                                     | 16                |

|                   |                   | 14.3 Functional Operating Range — Corrected oprating temperature range                                                                                             | 172               |

|                   | . 40              | <b>14.5 1.8-Volt to 3.3-Volt DC Electrical Characteristics Excluding UHF Module</b> — Added values for Stop I <sub>DD</sub> at -40°C to 125°C and corrected Note 1 | 173               |

| May,<br>2004      |                   | <b>14.6 3.0-Volt DC Electrical Characteristics Excluding UHF Module</b> — Added values for Stop I <sub>DD</sub> at –40°C to 125°C and corrected Note 1             | 174               |

|                   |                   | <b>14.7 2.0-Volt DC Electrical Characteristics Excluding UHF Module</b> — Added values for Stop I <sub>DD</sub> at -40°C to 125°C and corrected Note 1             | 175               |

|                   |                   | Table 15-1. MC Order Numbers — Added ordering information for -40°C to           125°C temperature range                                                           | 185               |

Data Sheet

MC68HC908RF2 — Rev. 4.0

**Revision History**

| 5.6 | CPU During Break Interrupts | 56 |

|-----|-----------------------------|----|

| 5.7 | Instruction Set Summary     | 57 |

| 5.8 | Opcode Map                  | 63 |

## Section 6. Internal Clock Generator Module (ICG)

| 6.1          | Introduction                                       | . 65 |

|--------------|----------------------------------------------------|------|

| 6.2          | Features                                           | . 65 |

| 6.3          | Functional Description                             | . 65 |

| 6.3.1        | Clock Enable Circuit                               |      |

| 6.3.2        | Internal Clock Generator.                          | . 67 |

| 6.3.2.1      | Digitally Controlled Oscillator                    | . 68 |

| 6.3.2.2      | Modulo N Divider                                   | . 68 |

| 6.3.2.3      | Frequency Comparator                               | . 68 |

| 6.3.2.4      | <b>U</b>                                           |      |

| 6.3.3        | External Clock Generator                           |      |

| 6.3.3.1      |                                                    |      |

| 6.3.3.2      |                                                    |      |

| 6.3.4        | Clock Monitor Circuit.                             |      |

| 6.3.4.1      |                                                    |      |

| 6.3.4.2      |                                                    |      |

| 6.3.4.3      |                                                    |      |

| 6.3.5        | Clock Selection Circuit                            |      |

| 6.3.5.1      |                                                    |      |

| 6.3.5.2      | 5                                                  |      |

| 6.4          | Usage Notes                                        |      |

| 6.4.1        | Switching Clock Sources                            |      |

| 6.4.2        | Enabling the Clock Monitor                         |      |

| 6.4.3        | Clock Monitor Interrupts                           |      |

| 6.4.4        | Quantization Error in DCO Output                   |      |

| 6.4.4.1      | <b>J J</b>                                         |      |

| 6.4.4.2      |                                                    |      |

| 6.4.4.3      |                                                    |      |

| 6.4.4.4      |                                                    |      |

| 6.4.5        | Switching Internal Clock Frequencies.              |      |

| 6.4.6        | Nominal Frequency Settling Time.                   |      |

| 6.4.6.1      | 0                                                  |      |

| 6.4.6.2      | 5                                                  |      |

| 6.4.6.3      |                                                    |      |

| 6.4.7        | Improving Settling Time                            |      |

| 6.4.8        | Trimming Frequency on the Internal Clock Generator | . 84 |

|              |                                                    |      |

| 6.5          | Low-Power Modes                                    | . 85 |

| 6.5<br>6.5.1 |                                                    |      |

MC68HC908RF2 — Rev. 4.0

Table of Contents

#### For More Information On This Product, Go to: www.freescale.com

# **Table of Contents**

|       | Configuration Register Option                                                                                                                 |                      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 6.7.1 | I/O Registers.<br>ICG Control Register<br>ICG Multiplier Register<br>ICG Trim Register.<br>ICG DCO Divider Register<br>ICG DCO Stage Register | 88<br>90<br>90<br>91 |

## Section 7. Keyboard/External Interrupt Module (KBI)

| 7.1            | Introduction                                               |

|----------------|------------------------------------------------------------|

| 7.2            | Features                                                   |

| 7.3<br>7.3.1   | Functional Description    93      External Interrupt    93 |

| 7.3.2          | IRQ Pin                                                    |

| 7.3.3<br>7.3.4 | KBI Module During Break Interrupts                         |

| 7.3.5          | Keyboard Initialization 100                                |

| 7.4<br>7.4.1   | Low-Power Modes                                            |

| 7.4.2          | Stop Mode                                                  |

| 7.5<br>7.5.1   | I/O Registers                                              |

| 7.5.2          | Keyboard Interrupt Enable Register                         |

#### Section 8. Low-Voltage Inhibit (LVI)

| 8.1 Introduction                                                                                                              | 103 |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.2 Features                                                                                                                  | 103 |

| <ul> <li>8.3 Functional Description</li> <li>8.3.1 False Trip Protection</li> <li>8.3.2 Short Stop Recovery Option</li> </ul> | 104 |

| 8.4 LVI Status Register                                                                                                       | 105 |

| 8.5 LVI Interrupts                                                                                                            | 105 |

| 8.6         Low-Power Modes           8.6.1         Wait Mode           8.6.2         Stop Mode                               | 105 |

## Section 9. Input/Output (I/O) Ports

| 9.1   | Introduction              | 107 |

|-------|---------------------------|-----|

| 9.2   | Port A                    | 108 |

| 9.2.1 | Port A Data Register      | 108 |

| 9.2.2 | Data Direction Register A | 109 |

**Freescale Semiconductor, Inc.**

MC68HC908RF2 — Rev. 4.0

#### For More Information On This Product, Go to: www.freescale.com

## **General Description**

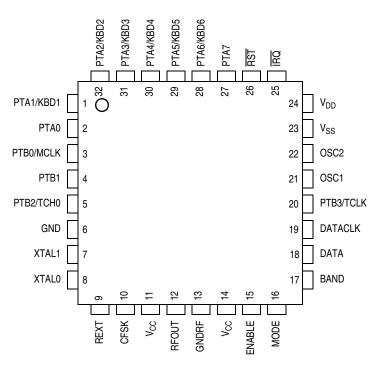

#### 1.4 Pin Assignments

Figure 1-2 shows the pin assignments.

Figure 1-2. LQFP Pin Assignments

#### 1.4.1 Power Supply Pins (V<sub>DD</sub> and V<sub>SS</sub>)

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins. The MCU operates from a single power supply.

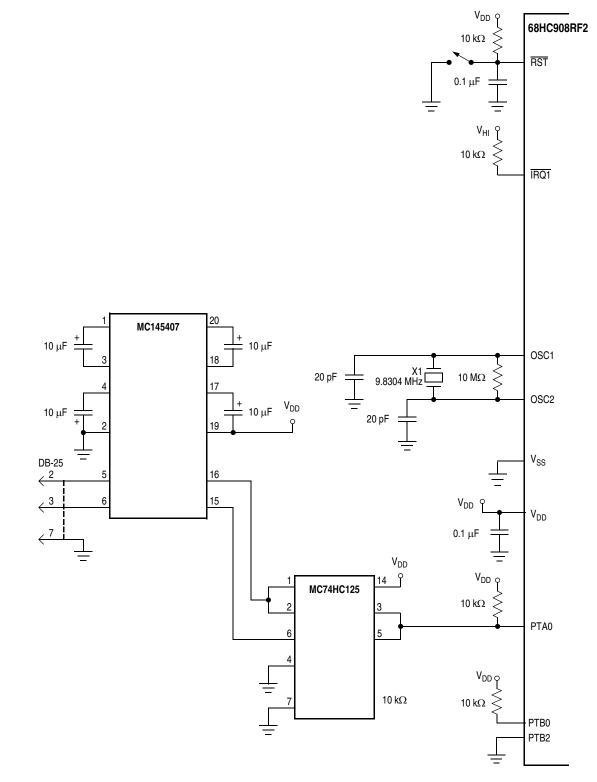

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as shown in **Figure 1-3**. Place the bypass capacitors as close to the MCU power pins as possible. Use high-frequency-response ceramic capacitors for  $C_{Bypass}$ .  $C_{Bulk}$  are optional bulk current bypass capacitors for use in applications that require the port pins to source high-current levels.

MC68HC908RF2 - Rev. 4.0

Semiconductor, Inc

reescale

## Memory

#### 2.4 Random-Access Memory (RAM)

Addresses \$0080–\$00FF are RAM locations. The location of the stack RAM is programmable.

**NOTE:** For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

**NOTE:** For M68HC05, M6805, and M146805 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

**NOTE:** Be careful when using nested subroutines. The CPU could overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

#### 2.5 FLASH 2TS Memory

This section describes the operation of the embedded FLASH 2TS memory. This memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

The FLASH 2TS memory is appropriately named to describe its 2-transistor source-select bit cell. The FLASH 2TS memory is an array of 2031 bytes with an additional 14 bytes of user vectors and one byte for block protection. An erased bit reads as a 0 and a programmed bit reads as a 1.

The address ranges for the user memory, control register, and vectors are:

- \$7800-\$7FEE, user space

- \$7FEF, reserved optional ICG trim value, see 6.7.3 ICG Trim Register

- \$FFF0, block protect register

- \$FE08, FLASH 2TS control register

- \$FFF2-\$FFFF, these locations are reserved for user-defined interrupt and reset vectors

This list is the row architecture for the user space array:

\$7800-\$7807 (Row 0) \$7808-\$780F (Row 1) \$7810-\$7817 (Row 2) \$7818-\$781F (Row 3) \$7820-\$7827 (Row 4)

\$7FE8-\$7FEF (Row 253)

Data Sheet

MC68HC908RF2 - Rev. 4.0

MOTOROLA

## Memory

The functions shown in Table 2-4 accept data through the CPU registers and global variables in RAM. Table 2-5 shows the RAM locations that are used for passing parameters.

| Variable Location | Variable Address <sup>(1)</sup> |

|-------------------|---------------------------------|

| CTRLBYT           | RAMSTART + 8                    |

| CPUSPD            | RAMSTART + 9                    |

| LADDR             | RAMSTART + 10                   |

| BUMPS             | RAMSTART + 12                   |

| DERASE            | RAMSTART + 13                   |

| DATA              | RAMSTART + 15                   |

Table 2-5. Embedded FLASH Routine Global Variables

1. RAMSTART is defined as the starting address of the RAM in the memory map. This is address \$0080.

#### 2.5.8 Embedded Function Descriptions

This subsection describes the embedded functions.

#### 2.5.8.1 RDVRRNG Routine

| Name:                       | RDVRRNG    |                                                                                                                                                      |

|-----------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose:                    | Read and/o | r verify a range of FLASH memory                                                                                                                     |

| Entry conditions:           | H:X        | Contains the first address of the range                                                                                                              |

|                             | LADDR      | Contains the last address of the range                                                                                                               |

|                             | DATA       | Contains the data to compare the read data against for read/verify to RAM only (length is user determined)                                           |

|                             | ACC        | Non-zero for read/verify to RAM, 0 for output to PA0                                                                                                 |

| Exit conditions:            | C bit      | Set if good compare for read/verify to RAM only                                                                                                      |

|                             | ACC        | Contains checksum                                                                                                                                    |

|                             | DATA       | Contains read FLASH data for read/verify to RAM only                                                                                                 |

| Ready/verify<br>RAM option: |            | tine both compares data passed in the DATA array to the FLASH data<br>he data from FLASH into the DATA array. It also calculates the<br>of the data. |

| Output to PA0 option:       |            | tine dumps the data from the range to PA0 in the same format as a. It also calculates the checksum of the data.                                      |

| NOTE:                       |            | dump does not circumvent security because the security vectors must<br>sed to make FLASH readable in monitor mode.                                   |

| Data Sheet                  |            | MC68HC908RF2 — Rev. 4.0                                                                                                                              |

36

The row whose cycling bit is different will be erased and the entire row will be programmed with the given data, including a toggled version of the cycling bit.

#### 2.5.8.5 Example Routine Calls

This code is for illustrative purposes only and does not represent valid syntax for any particular assembler.

| RAM                                                                                       |                                                                                                                     | EQU                                                                         | \$80                                                                                                                                                  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDVRRN                                                                                    | G                                                                                                                   | EQU                                                                         | \$F000                                                                                                                                                |

| PRGRNG                                                                                    | E                                                                                                                   | EQU                                                                         | \$F003                                                                                                                                                |

| ERANRG                                                                                    | E                                                                                                                   | EQU                                                                         | \$F006                                                                                                                                                |

| REDPRO                                                                                    |                                                                                                                     | EQU                                                                         | \$F009                                                                                                                                                |

|                                                                                           |                                                                                                                     |                                                                             | ****                                                                                                                                                  |

| ,<br>RAM D                                                                                | efinitic                                                                                                            | ons for                                                                     | Subroutines                                                                                                                                           |

|                                                                                           |                                                                                                                     |                                                                             | ************                                                                                                                                          |

| ,                                                                                         |                                                                                                                     |                                                                             |                                                                                                                                                       |

| ORG                                                                                       | RAM+8                                                                                                               |                                                                             |                                                                                                                                                       |

|                                                                                           | -                                                                                                                   |                                                                             |                                                                                                                                                       |

| CTRLBY                                                                                    | Т                                                                                                                   | RMB                                                                         | 1                                                                                                                                                     |

| CPUSPD                                                                                    |                                                                                                                     | RMB                                                                         | 1                                                                                                                                                     |

| LADDR                                                                                     |                                                                                                                     | RMB                                                                         | 2                                                                                                                                                     |

| BUMPS                                                                                     |                                                                                                                     | RMB                                                                         | 1                                                                                                                                                     |

| DERASE                                                                                    |                                                                                                                     | RMB                                                                         | 2                                                                                                                                                     |

|                                                                                           |                                                                                                                     |                                                                             | 2                                                                                                                                                     |

| ·Alloc                                                                                    | ation of                                                                                                            | יעדעם <i>"</i>                                                              | space is dependent on the device and                                                                                                                  |

| ;appli                                                                                    |                                                                                                                     | Dillii                                                                      | space is dependent on the device and                                                                                                                  |

| ,appir                                                                                    | Cation                                                                                                              |                                                                             |                                                                                                                                                       |

| DATA                                                                                      | RMB                                                                                                                 | 8                                                                           |                                                                                                                                                       |

|                                                                                           |                                                                                                                     | -                                                                           | * * * * * * * * * * * * * * * * * * * *                                                                                                               |

|                                                                                           |                                                                                                                     |                                                                             |                                                                                                                                                       |

|                                                                                           |                                                                                                                     | IPLE FOR                                                                    | READ/VERTEY A RANCE (RDVRRNC)                                                                                                                         |

|                                                                                           |                                                                                                                     |                                                                             | READ/VERIFY A RANGE (RDVRRNG)                                                                                                                         |

| ;****                                                                                     | * * * * * * * *                                                                                                     |                                                                             | * * * * * * * * * * * * * * * * * * * *                                                                                                               |

| ;*****<br>LDA                                                                             | *******<br>#\$FF                                                                                                    | ******                                                                      | **************************************                                                                                                                |

| ;*****<br>LDA<br>LDHX                                                                     | *******<br>#\$FF<br>#\$7807                                                                                         | ******                                                                      | * * * * * * * * * * * * * * * * * * * *                                                                                                               |

| ;*****<br>LDA<br>LDHX<br>STHX                                                             | *******<br>#\$FF<br>#\$7807<br>LADDR                                                                                | *******                                                                     | **************************************                                                                                                                |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX                                                     | ********<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800                                                                    | * * * * * * * *                                                             | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR                                              | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRRN                                                           | * * * * * * * *<br>7<br>)<br>IG                                             | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****                                    | *******<br>#\$FF<br>LADDR<br>#\$7807<br>RDVRRN                                                                      | * * * * * * * * * * * * * * * * * * *                                       | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING                         | ********<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI                                    | x ** * * * * * * * * * * * * * * * * *                                      | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****               | ********<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI                                             | ********<br>)<br>NG<br>.E FOR E:<br>.******                                 | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>************************************</pre>                                                                                                       |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>7<br>NG<br>********<br>LE FOR E:<br>********<br>PUSPD           | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV        | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI              | ********<br>J<br>JG<br>********<br>LE FOR E:<br>********<br>PUSPD<br>TRLBYT | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

| ;*****<br>LDA<br>LDHX<br>STHX<br>LDHX<br>JSR<br>;*****<br>CALLING<br>;*****<br>MOV<br>MOV | *******<br>#\$FF<br>#\$7807<br>LADDR<br>#\$7800<br>RDVRRN<br>*******<br>G EXAMPI<br>*******<br>#\$08,CI<br>#\$60,CT | ********<br>J<br>JG<br>********<br>LE FOR E:<br>********<br>PUSPD<br>TRLBYT | <pre>;TARGET IS RAM<br/>;END AFTER FIRST ROW<br/>;START AT FIRST ROW<br/>;DATA WILL CONTAIN FLASH INFO<br/>************************************</pre> |

MC68HC908RF2 - Rev. 4.0

Memory For More Information On This Product, Go to: www.freescale.com

| Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Operation                                                                                                                                                                                                                                                                                                                                           | Description                                          |  |   |   |    | ect<br>CCF | 2          | Address<br>Mode                       | Opcode                             | Operand        | es                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|---|---|----|------------|------------|---------------------------------------|------------------------------------|----------------|----------------------------|

| Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |                                                      |  |   | н | I  | NZO        |            | Add                                   | Opc                                | Ope            | Cvcles                     |

| SWI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $ \begin{array}{c} PC \leftarrow (PC) + 1; Push (PCL) \\ SP \leftarrow (SP) - 1; Push (PCH) \\ SP \leftarrow (SP) - 1; Push (X) \\ SP \leftarrow (SP) - 1; Push (A) \\ SP \leftarrow (SP) - 1; Push (CR) \\ SP \leftarrow (SP) - 1; I + 1 \\ PCH \leftarrow Interrupt Vector High Byte \\ PCL \leftarrow Interrupt Vector Low Byte \\ \end{array} $ |                                                      |  | _ | _ | 1  |            |            |                                       | 83                                 |                | 9                          |

| TAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer A to CCR                                                                                                                                                                                                                                                                                                                                   | $CCR \gets (A)$                                      |  | ţ | ţ | \$ | \$         | <b>t</b> 1 | INH                                   | 84                                 |                | 2                          |

| TAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer A to X                                                                                                                                                                                                                                                                                                                                     | X ← (A)                                              |  | - | - | -  |            |            | - INH                                 | 97                                 |                | 1                          |

| ТРА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer CCR to A                                                                                                                                                                                                                                                                                                                                   | $A \leftarrow (CCR)$                                 |  | - | - | -  |            |            | - INH                                 | 85                                 |                | 1                          |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Test for Negative or Zero                                                                                                                                                                                                                                                                                                                           | (A) – \$00 or (X) – \$00 or (M) – \$00               |  |   | _ |    | ţ          | ţ -        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 3<br>1<br>1<br>3<br>2<br>4 |

| TSX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer SP to H:X                                                                                                                                                                                                                                                                                                                                  | H:X ← (SP) + 1                                       |  |   |   | -  | -          |            | - INH                                 | 95                                 |                | 2                          |

| ТХА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer X to A $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                  |                                                      |  | - | - | -  |            |            | - INH                                 | 9F                                 |                | 1                          |

| TXS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer H:X to SP                                                                                                                                                                                                                                                                                                                                  | (SP) ← (H:X) – 1                                     |  | - | - | -  | - ·        |            | - INH                                 | 94                                 |                | 2                          |

| WAIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Enable Interrupts; Wait for Interrupt                                                                                                                                                                                                                                                                                                               | I bit ← 0; Inhibit CPU clocking<br>until interrupted |  |   | - | 0  | _ ·        |            | - INH                                 | 8F                                 |                | 1                          |

| A       Accumulator       n       Any bit         C       Carry/borrow bit       opr       Operand (one or two bytes)         CCR       Condition code register       PC       Program counter         dd       Direct address of operand and relative offset of branch instruction       PCL       Program counter low byte         DD       Direct addressing mode       rel       Relative addressing mode       REL         DIR       Direct addressing mode       rel       Relative program counter offset byte         DIX+       Direct to indexed with post increment addressing mode       rr       Relative program counter offset byte         EXT       Extended addressing mode       SP1       Stack pointer, 8-bit offset addressing mode         FT       Extended addressing mode       SP2       Stack pointer, 8-bit offset addressing mode         H       Half-carry bit       U       Undefined       U         H       Index register high byte       V       Overflow bit         hh II       High and low bytes of operand address in extended addressing       Z zoro bit       Index register low byte         I       Interrupt mask       Z zoro bit       Logical CR       Index register low byte         I       Interrupt mask       Z zoro bit       Logical CR       Indexe |                                                                                                                                                                                                                                                                                                                                                     |                                                      |  |   |   |    |            |            |                                       |                                    |                |                            |

#### Table 5-1. Instruction Set Summary (Sheet 7 of 7)

#### See Table 5-2.

#### 6.3.1 Clock Enable Circuit

The clock enable circuit is used to enable the internal clock (ICLK) or external clock (ECLK). The clock enable circuit generates an ICG stop (ICGSTOP) signal which stops all clocks (ICLK, ECLK, and the low-frequency base clock, IBASE) low. ICGSTOP is set and the ICG is disabled in stop mode.

The internal clock enable signal (ICGEN) turns on the internal clock generator which generates ICLK. ICGEN is set (active) whenever the ICGON bit is set and the ICGSTOP signal is clear. When ICGEN is clear, ICLK and IBASE are both low.

The external clock enable signal (ECGEN) turns on the external clock generator which generates ECLK. ECGEN is set (active) whenever the ECGON bit is set and the ICGSTOP signal is clear. When ECGEN is clear, ECLK is low.

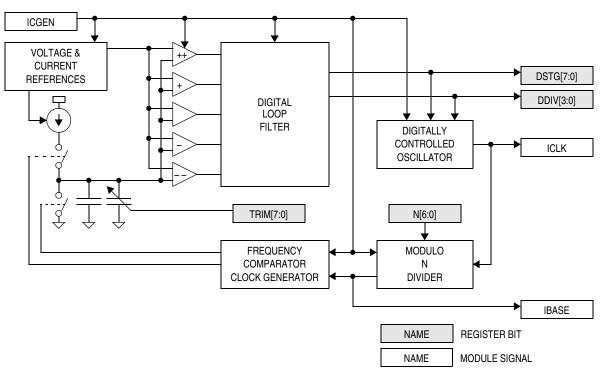

#### 6.3.2 Internal Clock Generator

The internal clock generator, shown in **Figure 6-2**, creates a low-frequency base clock (IBASE), which operates at a nominal frequency ( $f_{NOM}$ ) of 307.2 kHz ±25 percent, and an internal clock (ICLK) which is an integer multiple of IBASE. This multiple is the ICG multiplier factor (N), which is programmed in the ICG multiplier register (ICGMR). The internal clock generator is turned off and the output clocks (IBASE and ICLK) are held low when the internal clock generator enable signal (ICGEN) is clear.

Figure 6-2. Internal Clock Generator Block Diagram

Data Sheet

## Internal Clock Generator Module (ICG)

#### 6.3.4.2 Internal Clock Activity Detector

The internal clock activity detector looks for at least one falling edge on the low-frequency base clock (IBASE) every time the external reference (EREF) is low. Since EREF is less than half the frequency of IBASE, this should occur every time. If it does not occur two consecutive times, the internal clock inactivity indicator (IOFF) is set. IOFF will be cleared the next time there is a falling edge of IBASE while EREF is low.

The internal clock stable bit (ICGS) is set when IBASE is within approximately 5 percent of the target 307.2 kHz  $\pm$ 25 percent for two consecutive measurements. ICGS is cleared when IBASE is outside the 5 percent of the target 307.2 kHz  $\pm$ 25 percent, the internal clock generator is disabled (ICGEN is clear), or when IOFF is set.

#### 6.3.4.3 External Clock Activity Detector

The external clock activity detector looks for at least one falling edge on the external clock (ECLK) every time the internal reference (IREF) is low. Since IREF is less than half the frequency of ECLK, this should occur every time. If it does not occur two consecutive times, the external clock inactivity indicator (EOFF) is set. EOFF will be cleared the next time there is a falling edge of ECLK while IREF is low.

The external clock stable bit (ECGS) is also generated in the external clock activity detector. ECGS is set on a falling edge of the external stabilization clock (ESTBCLK). This will be 4096 ECLK cycles after the external clock generator on bit (ECGON) is set. ECGS is cleared when the external clock generator is disabled (ECGON is clear) or when EOFF is set.

#### 6.3.5 Clock Selection Circuit

The clock selection circuit, shown in **Figure 6-5**, contains two clock switches which generate the oscillator output clock (CGMXCLK) from either the internal clock (ICLK) or the external clock (ECLK). The clock selection circuit also contains a divide-by-two circuit which creates the clock generator output clock (CGMOUT), which generates the bus clocks.

#### 6.3.5.1 Clock Selection Switch

The clock select switch creates the oscillator output clock (CGMXCLK) from either the internal clock (ICLK) or the external clock (ECLK), based on the clock select bit (CS; set selects ECLK, clear selects ICLK). When switching the CS bit, both ICLK and ECLK must be on (ICGON and ECGON set). The clock being switched to must also be stable (ICGS or ECGS set).

MC68HC908RF2 - Rev. 4.0

Semiconductor, Inc

0

eescal

## Internal Clock Generator Module (ICG)

#### 6.6 Configuration Register Option

One configuration register option affects the functionality of the ICG: EXTSLOW (slow external clock).

All configuration register options will have a default setting. Refer to **Section 3**. **Configuration Register (CONFIG)** on how the configuration register is used.

#### 6.6.1 EXTSLOW

Slow external clock (EXTSLOW), when set, will decrease the drive strength of the oscillator amplifier, enabling low-frequency crystal operation (30 kHz–100 kHz). When clear, EXTSLOW enables high frequency crystal operation (1 MHz to 8 MHz).

EXTSLOW, when set, also configures the clock monitor to expect an external clock source that is slower than the low-frequency base clock (60 Hz–307.2 kHz). When EXTSLOW is clear, the clock monitor will expect an external clock faster than the low-frequency base clock (307.2 kHz–32 MHz).

The default state for this option is clear.

#### 6.7 I/O Registers

The ICG contains five registers, summarized in Figure 6-10. These registers are:

- ICG control register, ICGCR

- ICG multiplier register, ICGMR

- ICG trim register, ICGTR

- ICG DCO divider control register, ICGDVR

- ICG DCO stage control register, ICGDSR

Several of the bits in these registers have interaction where the state of one bit may force another bit to a particular state or prevent another bit from being set or cleared. A summary of this interaction is shown in **Table 6-5**.

| Addr.                                                        | Register Name            |        | Bit 7 | 6     | 5    | 4     | 3     | 2     | 1     | Bit 0 |

|--------------------------------------------------------------|--------------------------|--------|-------|-------|------|-------|-------|-------|-------|-------|

|                                                              | Internal Clock Generator | Read:  | CMIE  | CMF   | CMON | CS    | ICGON | ICGS  | ECGON | ECGS  |

| \$0036                                                       | <b>o</b> ( )             | Write: |       | OWION |      | ICCON |       | LOUON |       |       |

| See page 88.                                                 | Reset:                   | 0      | 0     | 0     | 0    | 1     | 0     | 0     | 0     |       |

| Internal Clock Generato<br>\$0037 Multiplier Register (ICGMR | Read:                    | R      | N6    | N5    | N4   | N3    | N2    | N1    | NO    |       |

|                                                              |                          | Write: |       |       | -    |       |       |       |       |       |

|                                                              | See page 90.             | Reset: | 0     | 0     | 0    | 1     | 0     | 1     | 0     | 1     |

|                                                              |                          |        |       |       |      | -     |       |       |       |       |

Figure 6-10. ICG I/O Register Summary

Data Sheet

MOTOROLA

# Input/Output (I/O) Ports

#### 9.2 Port A

Port A is an 8-bit special function port that shares six of its pins with the keyboard interrupt module (KBD). PTA6–PTA1 contain pullup resistors enabled when the port pin is enabled as a keyboard interrupt. Port A pins are also high-current port pins with 3-mA sink capabilities.

#### 9.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

| Address:            | \$0000 |      |      |           |            |      |      |       |

|---------------------|--------|------|------|-----------|------------|------|------|-------|

|                     | Bit 7  | 6    | 5    | 4         | 3          | 2    | 1    | Bit 0 |

| Read:<br>Write:     | PTA7   | PTA6 | PTA5 | PTA4      | PTA3       | PTA2 | PTA1 | PTA0  |

| Reset:              |        |      |      | Unaffecte | d by reset |      |      |       |

| Alternate Function: |        | KBD6 | KBD5 | KBD4      | KBD3       | KBD2 | KBD1 |       |

| _                   |        |      |      |           |            |      |      |       |

= Unimplemented

#### Figure 9-2. Port A Data Register (PTA)

PTA[7:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

KBD[6:1] — Keyboard Wakeup Pins

The keyboard interrupt enable bits, KBIE[6:1], in the keyboard interrupt control register enable the port A pin as external interrupt pins and related internal pullup resistor. See Section 7. Keyboard/External Interrupt Module (KBI).

**NOTE:** The enabling of a keyboard interrupt pin will override the corresponding definition of the pin in the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

Data Sheet

MOTOROLA

# Input/Output (I/O) Ports

| KBIE <sup>(2)</sup> | DDRA<br>Bit | PTA<br>Bit       | I/O Pin<br>Mode                       |            | Access   | sses to PTA             |  |

|---------------------|-------------|------------------|---------------------------------------|------------|----------|-------------------------|--|

| Bit                 | ы           | ы                | Mode                                  | Read/Write | Read     | Write                   |  |

| 1                   | Х           | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(4)</sup> | DDRA[7:0]  | Pin      | PTA[7:0] <sup>(3)</sup> |  |

| 0                   | 0           | Х                | Input, Hi-Z <sup>(5)</sup>            | DDRA[7:0]  | Pin      | PTA[7:0] <sup>(3)</sup> |  |

| 0                   | 1           | Х                | Output                                | DDRA[7:0]  | PTA[7:0] | PTA[7:0]                |  |

#### Table 9-1. Port A Pin Functions

Notes:

1. X = Don't care

2. Keyboard interrupt enable bit (see 7.5.2 Keyboard Interrupt Enable Register)

3. Writing affects data register, but does not affect input.

4. I/O pin pulled up to  $V_{\mbox{\scriptsize DD}}$  by internal pullup device

5. Hi-Z = High impedance

**NOTE:** Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

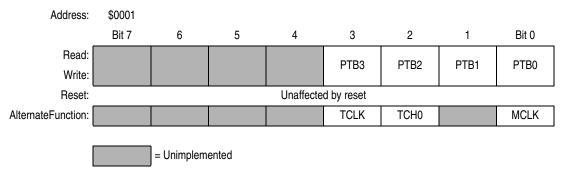

#### 9.3 Port B

Port B is a 4-bit special function port that shares two of its pins with the timer (TIM) module and one with the buffered internal bus clock MCLK.

#### 9.3.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the four port B pins.

Figure 9-5. Port B Data Register (PTB)

PTB[3:0] - Port B Data Bits

These read/write bits are software-programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### For More Information On This Product, Go to: www.freescale.com

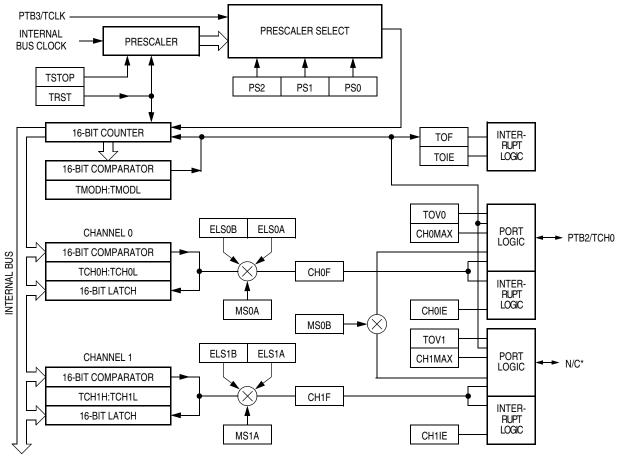

#### **11.4 Functional Description**

**Figure 11-2** shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH and TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

TIM channel 0 is programmable independently as input capture or output compare. TIM channel 1 is programmable only as output compare. The output compare is detected only through an interrupt.

# WARNING: TIM channel 1 should not be configured as an input capture because this would result in a floating input that would cause a higher I<sub>DD</sub>.

Refer to Figure 11-3 for a summary of the TIM I/O registers.

\*This pin is not available on the MC68HC908RF2.

Figure 11-2. TIM Block Diagram

Timer Interface Module (TIM)

#### 11.4.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs or the TIM clock pin, TCLK. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

#### 11.4.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH and TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM CPU interrupt requests.

#### **NOTE:** TIM channel 1 should not be configured in this mode.

#### 11.4.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM channel 0 can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests for both TIM channel 0 and TIM channel 1.

NOTE: TIM channel 1 does not have an external pin associated with it.

#### 11.4.4 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in **11.4.3 Output Compare**. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.