Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091cbu6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

12/128

DocID026284 Rev 4

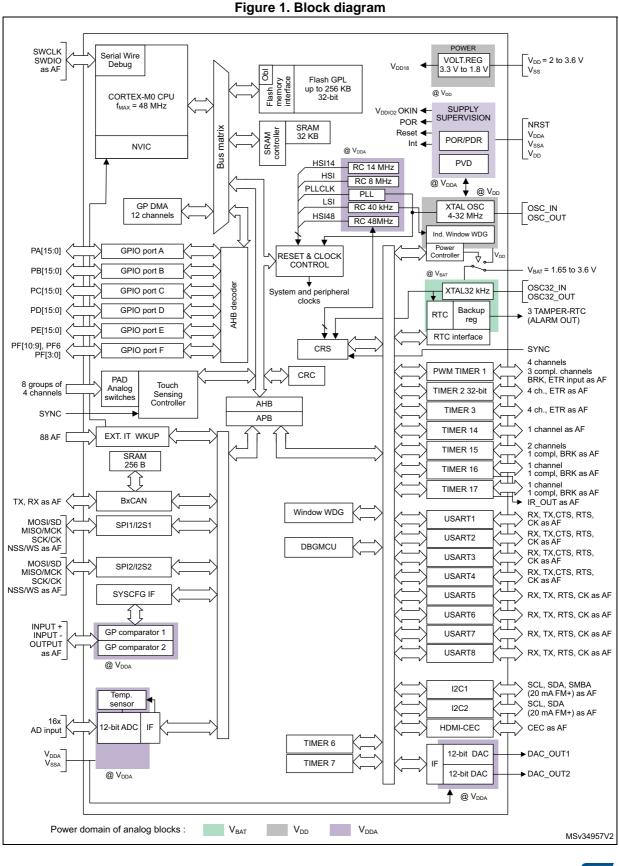

#### STM32F091xB STM32F091xC

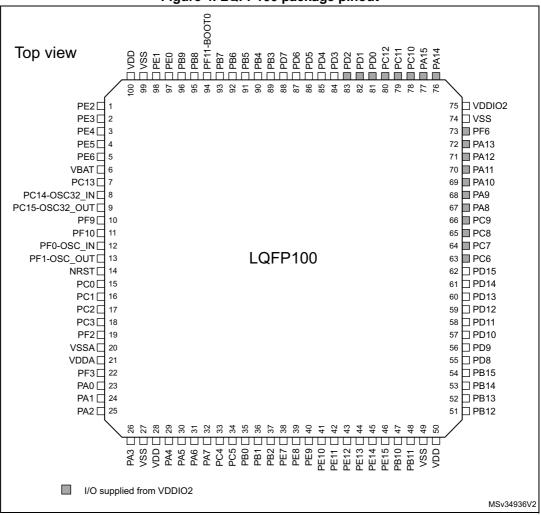

Figure 4. LQFP100 package pinout

|          | Pi      | n nui   | mber   | s       |                 |                                      |          |                        |  | Pin functions                                                                    |                                                    |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|------------------------|--|----------------------------------------------------------------------------------|----------------------------------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure<br>Notes |  | Alternate functions                                                              | Additional<br>functions                            |  |

| J1       | 19      | -       | -      | -       | -               | PF2                                  | I/O      | FT                     |  | EVENTOUT,<br>USART7_TX,<br>USART7_CK_RTS                                         | WKUP8                                              |  |

| K1       | 20      | F1      | 12     | G8      | 8               | VSSA                                 | S        | -                      |  | Analog grou                                                                      | nd                                                 |  |

| M1       | 21      | H1      | 13     | H8      | 9               | VDDA                                 | S        | -                      |  | Analog power s                                                                   | upply                                              |  |

| L1       | 22      | -       | -      | -       | -               | PF3                                  | I/O      | FT                     |  | EVENTOUT,<br>USART7_RX,<br>USART6_CK_RTS                                         |                                                    |  |

| L2       | 23      | G2      | 14     | F7      | 10              | PA0                                  | I/O      | TTa                    |  | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX<br>COMP1_OUT            | RTC_ TAMP2,<br>WKUP1,<br>ADC_IN0,<br>COMP1_INM6    |  |

| M2       | 24      | H2      | 15     | F6      | 11              | PA1                                  | I/O      | ТТа                    |  | USART2_RTS,<br>TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX,<br>EVENTOUT | ADC_IN1,<br>COMP1_INP                              |  |

| КЗ       | 25      | F3      | 16     | E5      | 12              | PA2                                  | I/O      | TTa                    |  | USART2_TX, TIM2_CH3,<br>TIM15_CH1,<br>TSC_G1_IO3<br>COMP2_OUT                    | ADC_IN2,<br>WKUP4,<br>COMP2_INM6                   |  |

| L3       | 26      | G3      | 17     | H7      | 13              | PA3                                  | I/O      | ТТа                    |  | USART2_RX,TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4                                  | ADC_IN3,<br>COMP2_INP                              |  |

| D3       | 27      | C2      | 18     | G7      | -               | VSS                                  | S        | -                      |  | Ground                                                                           |                                                    |  |

| H3       | 28      | D2      | 19     | G6      | -               | VDD                                  | S        | -                      |  | Digital power s                                                                  | upply                                              |  |

| М3       | 29      | H3      | 20     | H6      | 14              | PA4                                  | I/O      | TTa                    |  | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK,<br>USART6_TX       | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |  |

| K4       | 30      | F4      | 21     | F5      | 15              | PA5                                  | I/O      | ТТа                    |  | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2,<br>USART6_RX          | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |  |

| Table 13. STM32F091xB/xC pin definitions (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

\_\_\_\_

| Table To. Alternate functions selected through GFIOC_AFK registers for port C |            |                     |           |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|------------|---------------------|-----------|--|--|--|--|--|--|

| Pin name                                                                      | AF0        | AF1                 | AF2       |  |  |  |  |  |  |

| PC0                                                                           | EVENTOUT   | USART7_TX           | USART6_TX |  |  |  |  |  |  |

| PC1                                                                           | EVENTOUT   | USART7_RX           | USART6_RX |  |  |  |  |  |  |

| PC2                                                                           | EVENTOUT   | SPI2_MISO, I2S2_MCK | USART8_TX |  |  |  |  |  |  |

| PC3                                                                           | EVENTOUT   | SPI2_MOSI, I2S2_SD  | USART8_RX |  |  |  |  |  |  |

| PC4                                                                           | EVENTOUT   | USART3_TX           | -         |  |  |  |  |  |  |

| PC5                                                                           | TSC_G3_IO1 | USART3_RX           | -         |  |  |  |  |  |  |

| PC6                                                                           | TIM3_CH1   | USART7_TX           | -         |  |  |  |  |  |  |

| PC7                                                                           | TIM3_CH2   | USART7_RX           | -         |  |  |  |  |  |  |

| PC8                                                                           | TIM3_CH3   | USART8_TX           | -         |  |  |  |  |  |  |

| PC9                                                                           | TIM3_CH4   | USART8_RX           | -         |  |  |  |  |  |  |

| PC10                                                                          | USART4_TX  | USART3_TX           | -         |  |  |  |  |  |  |

| PC11                                                                          | USART4_RX  | USART3_RX           | -         |  |  |  |  |  |  |

| PC12                                                                          | USART4_CK  | USART3_CK           | USART5_TX |  |  |  |  |  |  |

| PC13                                                                          | -          | -                   | -         |  |  |  |  |  |  |

| PC14                                                                          | -          | -                   | -         |  |  |  |  |  |  |

| PC15                                                                          | -          | -                   | -         |  |  |  |  |  |  |

## Table 16. Alternate functions selected through GPIOC\_AFR registers for port C

### Table 17. Alternate functions selected through GPIOD\_AFR registers for port D

| Pin name | AF0        | AF1                 | AF2           |

|----------|------------|---------------------|---------------|

| PD0      | CAN_RX     | SPI2_NSS, I2S2_WS   | -             |

| PD1      | CAN_TX     | SPI2_SCK, I2S2_CK   | -             |

| PD2      | TIM3_ETR   | USART3_RTS          | USART5_RX     |

| PD3      | USART2_CTS | SPI2_MISO, I2S2_MCK | -             |

| PD4      | USART2_RTS | SPI2_MOSI, I2S2_SD  | -             |

| PD5      | USART2_TX  | -                   | -             |

| PD6      | USART2_RX  | -                   | -             |

| PD7      | USART2_CK  | -                   | -             |

| PD8      | USART3_TX  | -                   | -             |

| PD9      | USART3_RX  | -                   | -             |

| PD10     | USART3_CK  | -                   | -             |

| PD11     | USART3_CTS | -                   | -             |

| PD12     | USART3_RTS | TSC_G8_IO1          | USART8_CK_RTS |

| PD13     | USART8_TX  | TSC_G8_IO2          |               |

| PD14     | USART8_RX  | TSC_G8_IO3          | -             |

| PD15     | CRS_SYNC   | TSC_G8_IO4          | USART7_CK_RTS |

| Bus | Boundary address          | Size  | Peripheral    |

|-----|---------------------------|-------|---------------|

|     | 0x4001 5C00 - 0x4001 7FFF | 9 KB  | Reserved      |

|     | 0x4001 5800 - 0x4001 5BFF | 1 KB  | DBGMCU        |

|     | 0x4001 4C00 - 0x4001 57FF | 3 KB  | Reserved      |

|     | 0x4001 4800 - 0x4001 4BFF | 1 KB  | TIM17         |

|     | 0x4001 4400 - 0x4001 47FF | 1 KB  | TIM16         |

|     | 0x4001 4000 - 0x4001 43FF | 1 KB  | TIM15         |

|     | 0x4001 3C00 - 0x4001 3FFF | 1 KB  | Reserved      |

|     | 0x4001 3800 - 0x4001 3BFF | 1 KB  | USART1        |

|     | 0x4001 3400 - 0x4001 37FF | 1 KB  | Reserved      |

|     | 0x4001 3000 - 0x4001 33FF | 1 KB  | SPI1/I2S1     |

| APB | 0x4001 2C00 - 0x4001 2FFF | 1 KB  | TIM1          |

|     | 0x4001 2800 - 0x4001 2BFF | 1 KB  | Reserved      |

|     | 0x4001 2400 - 0x4001 27FF | 1 KB  | ADC           |

|     | 0x4001 2000 - 0x4001 23FF | 1 KB  | Reserved      |

|     | 0x4001 1C00 – 0x4001 1FFF | 1 KB  | USART8        |

|     | 0x4001 1800 – 0x4001 1BFF | 1 KB  | USART7        |

|     | 0x4001 1400 – 0x4001 17FF | 1 KB  | USART6        |

|     | 0x4001 0800 - 0x4001 13FF | 3 KB  | Reserved      |

|     | 0x4001 0400 - 0x4001 07FF | 1 KB  | EXTI          |

|     | 0x4001 0000 - 0x4001 03FF | 1 KB  | SYSCFG + COMP |

|     | 0x4000 8000 - 0x4000 FFFF | 32 KB | Reserved      |

# Table 20. STM32F091xB/xC peripheral register boundary addresses (continued)

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

|                                      | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                                      | Injected current on FT and FTf pins                                             | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  | 1    |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 | 1    |

#### Table 22. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. On these I/Os, a positive injection is induced by  $V_{IN} > V_{DDA}$ . Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 59: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 23. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 29* to *Table 32* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

1. Data based on characterization results, not tested in production unless otherwise specified.

|                  | er                |                       |                   |      | V <sub>DDA</sub> | = 2.4 V             | 1      |      | V <sub>DDA</sub> | = 3.6 \ | /                |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|------------------|-------------------|-----------------------|-------------------|------|------------------|---------------------|--------|------|------------------|---------|------------------|------|------|------|----|--------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Symbol           | Para-meter        | Conditions            | f <sub>HCLK</sub> |      | м                | ax @ T <sub>A</sub> | (2)    |      | Μ                | lax @ T | A <sup>(2)</sup> | Unit |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | Para              |                       |                   | Тур  | 25 °C            | 85 °C               | 105 °C | Тур  | 25 °C            | 85 °C   | 105 °C           |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  |                   | HSI48                 | 48 MHz            | 312  | 333              | 338                 | 347    | 316  | 334              | 341     | 350              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  |                   | HSE                   | 48 MHz            | 147  | 168              | 178                 | 181    | 160  | 181              | 192     | 197              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | Supply current in | bypass,<br>n PLL on   | 32 MHz            | 101  | 119              | 125                 | 127    | 109  | 127              | 135     | 138              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | Run or            |                       | 24 MHz            | 80   | 96               | 98                  | 100    | 87   | 101              | 106     | 109              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | Sleep<br>mode,    | HSE                   | 8 MHz             | 2.8  | 3.5              | 3.7                 | 3.9    | 3.7  | 4.3              | 4.6     | 4.7              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

| I <sub>DDA</sub> | code<br>executing | ode bypass,           | 1 MHz             | 2.7  | 3.2              | 3.5                 | 3.8    | 3.3  | 3.9              | 4.4     | 4.7              | μA   |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | from              | from                  | from              | from | from             | from                | from   | from | from             | from    | from             | from | from | from | om | 48 MHz | 214 | 243 | 254 | 259 | 235 | 262 | 275 | 281 |  |

| mem              | Flash<br>memory   |                       | 32 MHz            | 166  | 193              | 203                 | 204    | 185  | 207              | 216     | 220              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  | or RAM            |                       | 24 MHz            | 144  | 171              | 177                 | 178    | 161  | 180              | 187     | 190              |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

|                  |                   | HSI clock,<br>PLL off | 8 MHz             | 65   | 83               | 85                  | 86     | 77   | 90               | 92      | 93               |      |      |      |    |        |     |     |     |     |     |     |     |     |  |

| Table 30. Typical and maximum current consumption from the $\rm V_{DDA}$ supply |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

## 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 36* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop or Standby mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode. The wakeup source from Standby mode is the WKUP1 pin (PA0).

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol     | Parameter                   | Conditions                  | Typ @Vdd = Vdda |         |         |       |         |     | Unit |

|------------|-----------------------------|-----------------------------|-----------------|---------|---------|-------|---------|-----|------|

|            |                             |                             | = 2.0 V         | = 2.4 V | = 2.7 V | = 3 V | = 3.3 V | Max | Unit |

| twustop    | Wakeup from Stop<br>mode    | Regulator in run<br>mode    | 3.2             | 3.1     | 2.9     | 2.9   | 2.8     | 5   |      |

|            |                             | Regulator in low power mode | 7.0             | 5.8     | 5.2     | 4.9   | 4.6     | 9   |      |

| twustandby | Wakeup from<br>Standby mode | -                           | 60.4            | 55.6    | 53.5    | 52    | 51      | -   | μs   |

| twusleep   | Wakeup from Sleep<br>mode   | -                           | 4 SYSCLK cycles |         |         |       |         | -   |      |

Table 36. Low-power mode wakeup timings

# 6.3.7 External clock source characteristics

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 15: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time             | -                      | -   | 20                     | 113  |

| Table 37  | High-speed   | ovtornal | lisor | clock | characteristics |

|-----------|--------------|----------|-------|-------|-----------------|

| Table Jr. | iligii-speeu | EXICILIA | usei  | CIUCK | characteristics |

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Мах                | Unit |  |  |

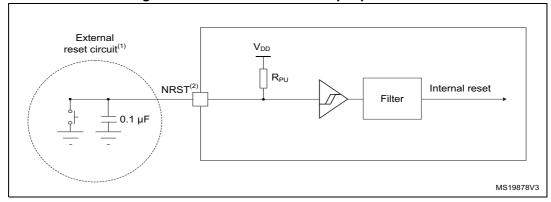

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|--|--|

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                  | 200 | -                  | mV   |  |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |  |  |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |  |  |

| V                      | NRST input not filtered pulse                   | $2.7 < V_{DD} < 3.6$              | 300 <sup>(3)</sup> | -   | _                  | ns   |  |  |

| V <sub>NF(NRST)</sub>  |                                                 | $2.0 < V_{DD} < 3.6$              | 500 <sup>(3)</sup> | -   | -                  | 115  |  |  |

Table 56. NRST pin characteristics (continued)

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

3. Data based on design simulation only. Not tested in production.

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

## 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Table 57. ADC c | haracteristics |

|-----------------|----------------|

|-----------------|----------------|

| Symbol                        | Parameter                                     | Conditions               | Min   | Тур | Max | Unit |  |  |

|-------------------------------|-----------------------------------------------|--------------------------|-------|-----|-----|------|--|--|

| V <sub>DDA</sub>              | Analog supply voltage for<br>ADC ON           | -                        | 2.4   | -   | 3.6 | V    |  |  |

| I <sub>DDA (ADC)</sub>        | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V | -     | 0.9 | -   | mA   |  |  |

| f <sub>ADC</sub>              | ADC clock frequency                           | -                        | 0.6   | -   | 14  | MHz  |  |  |

| f <sub>S</sub> <sup>(2)</sup> | Sampling rate                                 | 12-bit resolution        | 0.043 | -   | 1   | MHz  |  |  |

### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| Table 58. R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz |                                                                            |      |  |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------------------|------|--|--|--|--|--|--|

| T <sub>s</sub> (cycles)                                      | T <sub>s</sub> (cycles) t <sub>S</sub> (μs) $R_{AIN} \max (k\Omega)^{(1)}$ |      |  |  |  |  |  |  |

| 1.5                                                          | 0.11                                                                       | 0.4  |  |  |  |  |  |  |

| 7.5                                                          | 0.54                                                                       | 5.9  |  |  |  |  |  |  |

| 13.5                                                         | 0.96                                                                       | 11.4 |  |  |  |  |  |  |

| 28.5                                                         | 2.04                                                                       | 25.2 |  |  |  |  |  |  |

| 41.5                                                         | 2.96                                                                       | 37.2 |  |  |  |  |  |  |

| 55.5                                                         | 3.96                                                                       | 50   |  |  |  |  |  |  |

| 71.5                                                         | 5.11                                                                       | NA   |  |  |  |  |  |  |

| 239.5                                                        | 17.1                                                                       | NA   |  |  |  |  |  |  |

1. Guaranteed by design, not tested in production.

## Table 59. ADC accuracy<sup>(1)(2)(3)</sup>

| Symbol | Parameter                    | Test conditions                                                                          | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                          | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{PCLK} = 48 \text{ MHz},$                                                             | ±1   | ±1.5               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V   | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | $T_A = 25 $ °C                                                                           | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     |                                                                                          | ±0.8 | ±1.5               |      |

| ET     | Total unadjusted error       |                                                                                          | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                              | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.7 V to 3.6 V | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_{A} = -40 \text{ to } 105 \text{ °C}$                                                 | ±0.7 | ±1.3               |      |

| EL     | Integral linearity error     |                                                                                          | ±1.2 | ±1.7               |      |

| ET     | Total unadjusted error       |                                                                                          | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                              | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | $f_{ADC}$ = 14 MHz, $R_{AIN}$ < 10 k $\Omega$<br>V <sub>DDA</sub> = 2.4 V to 3.6 V       | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_A = 25 \text{°C}$                                                                     | ±0.7 | ±1.3               | 1    |

| EL     | Integral linearity error     |                                                                                          | ±1.2 | ±1.7               |      |

1. ADC DC accuracy values are measured after internal calibration.

| Prescaler divider PR[2:0] bits |        | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |  |  |

|--------------------------------|--------|--------------------------------|--------------------------------|------|--|--|--|--|

| /4                             | 0      | 0.1                            | 409.6                          |      |  |  |  |  |

| /8                             | 1      | 0.2                            | 819.2                          |      |  |  |  |  |

| /16                            | 2      | 0.4                            | 1638.4                         |      |  |  |  |  |

| /32                            | 3      | 0.8                            | 3276.8                         | ms   |  |  |  |  |

| /64                            | 4      | 1.6                            | 6553.6                         |      |  |  |  |  |

| /128                           | 5      | 3.2                            | 13107.2                        |      |  |  |  |  |

| /256                           | 6 or 7 | 6.4                            | 26214.4                        |      |  |  |  |  |

Table 65. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value Max timeout valu |         | Unit |

|-----------|-------|------------------------------------|---------|------|

| 1         | 0     | 0.0853                             | 5.4613  |      |

| 2         | 1     | 0.1706                             | 10.9226 | ms   |

| 4         | 2     | 0.3413                             | 21.8453 | ms   |

| 8         | 3     | 0.6826                             | 43.6906 |      |

Table 66. WWDG min/max timeout value at 48 MHz (PCLK)

## 6.3.22 Communication interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

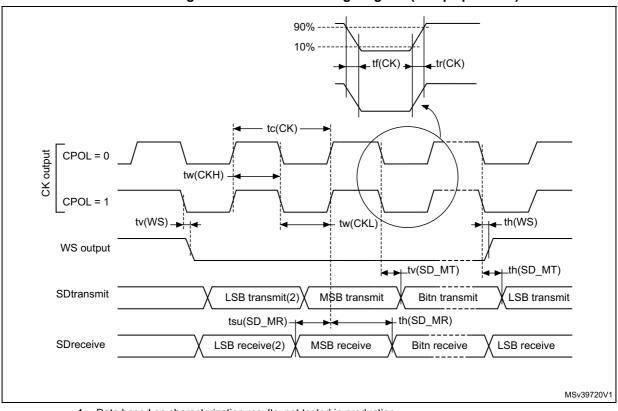

## Figure 32. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

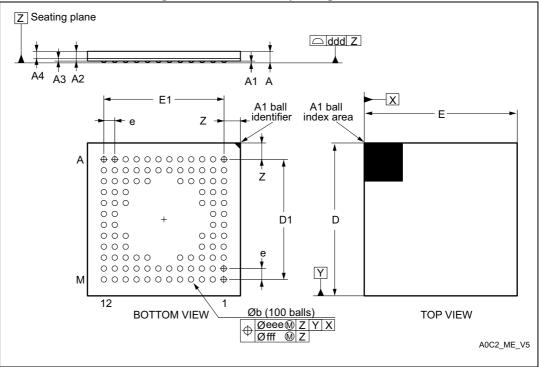

# 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 33. UFBGA100 package outline

1. Drawing is not to scale.

| Symbol |      | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|------|-------------|-------|-----------------------|--------|--------|

| Symbol | Min. | Тур.        | Max.  | Min.                  | Тур.   | Max.   |

| A      | -    | -           | 0.600 | -                     | -      | 0.0236 |

| A1     | -    | -           | 0.110 | -                     | -      | 0.0043 |

| A2     | -    | 0.450       | -     | -                     | 0.0177 | -      |

| A3     | -    | 0.130       | -     | -                     | 0.0051 | 0.0094 |

| A4     | -    | 0.320       | -     | -                     | 0.0126 | -      |

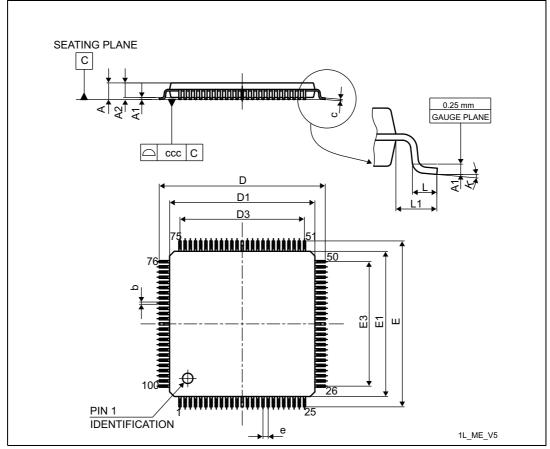

# 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

1. Drawing is not to scale.

| Table 72. LQPF100 pa | ackage mechanical data |

|----------------------|------------------------|

|----------------------|------------------------|

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

DocID026284 Rev 4

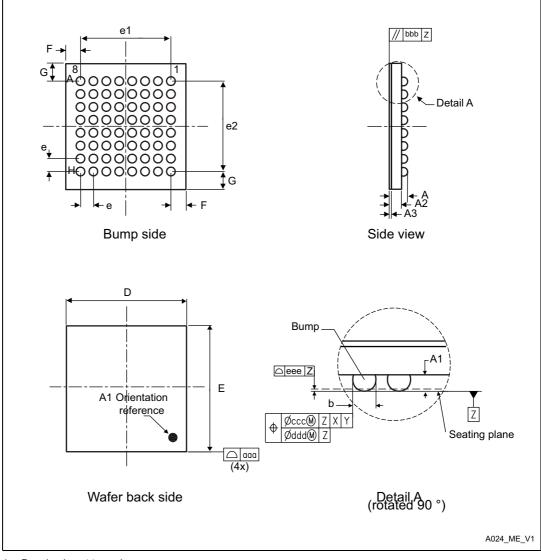

# 7.4 WLCSP64 package information

WLCSP64 is a 64-ball, 3.347 x 3.585 mm, 0.4 mm pitch wafer-level chip-scale package.

1. Drawing is not to scale.

| Symbol | millimeters inches <sup>(1)</sup> |       |       |        |        |        |

|--------|-----------------------------------|-------|-------|--------|--------|--------|

| Symbol | Min                               | Тур   | Max   | Min    | Тур    | Max    |

| А      | 0.525                             | 0.555 | 0.585 | 0.0207 | 0.0219 | 0.0230 |

| A1     | -                                 | 0.175 | -     | -      | 0.0069 | -      |

| A2     | -                                 | 0.380 | -     | -      | 0.0150 | -      |

| A3     | -                                 | 0.025 | -     | -      | 0.0010 | -      |

| Table 75. WLCSP64 package mechanical data (continued) |             |        |       |                       |        |        |  |

|-------------------------------------------------------|-------------|--------|-------|-----------------------|--------|--------|--|

| Symbol                                                | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|                                                       | Min         | Тур    | Max   | Min                   | Тур    | Мах    |  |

| b <sup>(2)</sup>                                      | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |

| D                                                     | 3.312       | 3.347  | 3.382 | 0.1304                | 0.1318 | 0.1331 |  |

| E                                                     | 3.550       | 3.585  | 3.620 | 0.1398                | 0.1411 | 0.1425 |  |

| е                                                     | -           | 0.400  | -     | -                     | 0.0157 | -      |  |

| e1                                                    | -           | 2.800  | -     | -                     | 0.1102 | -      |  |

| e2                                                    | -           | 2.800  | -     | -                     | 0.1102 | -      |  |

| F                                                     | -           | 0.2735 | -     | -                     | 0.0108 | -      |  |

| G                                                     | -           | 0.3925 | -     | -                     | 0.0155 | -      |  |

| aaa                                                   | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| bbb                                                   | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| CCC                                                   | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| ddd                                                   | -           | -      | 0.050 | -                     | -      | 0.0020 |  |

| eee                                                   | -           | -      | 0.050 | -                     | -      | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

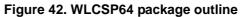

## Figure 43. Recommended footprint for WLCSP64 package

Table 76. WLCSP64 recommended PCB design rules

| Dimension      | Recommended values                             |  |  |

|----------------|------------------------------------------------|--|--|

| Pitch          | 0.4                                            |  |  |

| Drod           | 260 µm max. (circular)                         |  |  |

| Dpad           | 220 µm recommended                             |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |

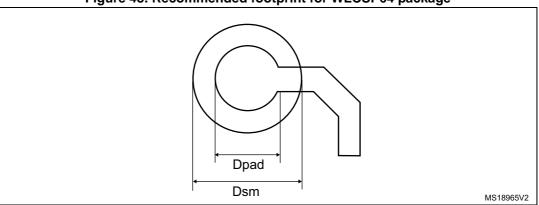

# 7.5 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 45. LQFP64 package outline

1. Drawing is not to scale.

| Table 77. LQFP64 | package | mechanical data |

|------------------|---------|-----------------|

|------------------|---------|-----------------|

| Cumhal | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Max   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| 17-Dec-2015       3         17-Dec-2015       3         (continued)       -         (continued)       -         (continued)       -         (continued)       -         (continued)       -         (continued)       - <td< th=""></td<> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| value added for t <sub>v(SD_ST)</sub><br>- <i>Figure 32: I<sup>2</sup>S master timing diagram (Philips protocol)</i><br>added definition of edge level references<br><b>Section 7: Package information:</b><br>- <i>Figure 33: UFBGA100 package outline</i> and<br>associated <i>Table 70</i> updated<br>- <i>Figure 34</i> and associated <i>Table 71</i> updated<br>- <i>Figure 35: UFBGA100 package marking example</i> and<br>associated text updated<br>- <i>Figure 38: LQFP100 package marking example</i> and<br>associated text updated<br>- <i>Table 74: UFBGA64 recommended PCB design rules</i><br>added                                                                                                                                                                                                                                                                                                                       |

| Table 82. Docume | nt revision | history ( | continued) |

|------------------|-------------|-----------|------------|

|------------------|-------------|-----------|------------|

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID026284 Rev 4