Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                 |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |

| Number of I/O              | 38                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 13x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091ccu7tr |

|   |      | 3.14.6    | SysTick timer                                                                    | 23   |

|---|------|-----------|----------------------------------------------------------------------------------|------|

|   | 3.15 | Real-tir  | me clock (RTC) and backup registers                                              | . 23 |

|   | 3.16 | Inter-in  | tegrated circuit interface (I <sup>2</sup> C)                                    | . 24 |

|   | 3.17 | Univers   | sal synchronous/asynchronous receiver/transmitter (USART)                        | . 25 |

|   | 3.18 | Serial p  | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) | . 26 |

|   | 3.19 |           | efinition multimedia interface (HDMI) - consumer nics control (CEC)              | . 27 |

|   | 3.20 | Control   | ller area network (CAN)                                                          | . 27 |

|   | 3.21 |           | ecovery system (CRS)                                                             |      |

|   | 3.22 |           | vire debug port (SW-DP)                                                          |      |

| 4 | Pino | uts and   | pin descriptions                                                                 | . 28 |

| 5 | Mem  | ory ma    | oping                                                                            | . 45 |

| 6 | Elec | trical ch | aracteristics                                                                    | . 49 |

|   | 6.1  | Parame    | eter conditions                                                                  | . 49 |

|   |      | 6.1.1     | Minimum and maximum values                                                       | 49   |

|   |      | 6.1.2     | Typical values                                                                   | 49   |

|   |      | 6.1.3     | Typical curves                                                                   | 49   |

|   |      | 6.1.4     | Loading capacitor                                                                | 49   |

|   |      | 6.1.5     | Pin input voltage                                                                | 49   |

|   |      | 6.1.6     | Power supply scheme                                                              | 50   |

|   |      | 6.1.7     | Current consumption measurement                                                  | 51   |

|   | 6.2  | Absolu    | te maximum ratings                                                               | . 52 |

|   | 6.3  | Operat    | ing conditions                                                                   | . 54 |

|   |      | 6.3.1     | General operating conditions                                                     | 54   |

|   |      | 6.3.2     | Operating conditions at power-up / power-down                                    | 54   |

|   |      | 6.3.3     | Embedded reset and power control block characteristics                           | 55   |

|   |      | 6.3.4     | Embedded reference voltage                                                       | 56   |

|   |      | 6.3.5     | Supply current characteristics                                                   | 56   |

|   |      | 6.3.6     | Wakeup time from low-power mode                                                  | 67   |

|   |      | 6.3.7     | External clock source characteristics                                            | 67   |

|   |      | 6.3.8     | Internal clock source characteristics                                            | 71   |

|   |      | 6.3.9     | PLL characteristics                                                              | 75   |

|   |      | 6.3.10    | Memory characteristics                                                           | 75   |

|   |      |           |                                                                                  |      |

# List of tables

| Table 1.  | Device summary                                                                   | 1  |

|-----------|----------------------------------------------------------------------------------|----|

| Table 2.  | STM32F091xB/xC family device features and peripheral counts                      |    |

| Table 3.  | Temperature sensor calibration values                                            |    |

| Table 4.  | Internal voltage reference calibration values                                    | 19 |

| Table 5.  | Capacitive sensing GPIOs available on STM32F091xB/xC devices                     | 20 |

| Table 6.  | Number of capacitive sensing channels available                                  |    |

|           | on STM32F091xB/xC devices                                                        | 21 |

| Table 7.  | Timer feature comparison                                                         | 21 |

| Table 8.  | Comparison of I <sup>2</sup> C analog and digital filters                        | 24 |

| Table 9.  | STM32F091xB/xC I <sup>2</sup> C implementation                                   | 25 |

| Table 10. | STM32F091xB/xC USART implementation                                              | 25 |

| Table 11. | STM32F091xB/xC SPI/I <sup>2</sup> S implementation                               | 26 |

| Table 12. | Legend/abbreviations used in the pinout table                                    | 33 |

| Table 13. | STM32F091xB/xC pin definitions                                                   |    |

| Table 14. | Alternate functions selected through GPIOA_AFR registers for port A              |    |

| Table 15. | Alternate functions selected through GPIOB_AFR registers for port B              |    |

| Table 16. | Alternate functions selected through GPIOC_AFR registers for port C              |    |

| Table 17. | Alternate functions selected through GPIOD_AFR registers for port D              |    |

| Table 18. | Alternate functions selected through GPIOE_AFR registers for port E              |    |

| Table 19. | Alternate functions selected through GPIOF_AFR registers for port F              |    |

| Table 20. | STM32F091xB/xC peripheral register boundary addresses                            |    |

| Table 21. | Voltage characteristics                                                          |    |

| Table 22. | Current characteristics                                                          |    |

| Table 23. | Thermal characteristics                                                          |    |

| Table 24. | General operating conditions                                                     |    |

| Table 25. | Operating conditions at power-up / power-down                                    |    |

| Table 26. | Embedded reset and power control block characteristics                           |    |

| Table 27. | Programmable voltage detector characteristics                                    |    |

| Table 28. | Embedded internal reference voltage                                              |    |

| Table 29. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD}$ = 3.6 V |    |

| Table 30. | Typical and maximum current consumption from the V <sub>DDA</sub> supply         |    |

| Table 31. | Typical and maximum consumption in Stop and Standby modes                        |    |

| Table 32. | Typical and maximum current consumption from the V <sub>BAT</sub> supply         | 61 |

| Table 33. | Typical current consumption, code executing from Flash memory,                   |    |

|           | running from HSE 8 MHz crystal                                                   |    |

| Table 34. | Switching output I/O current consumption                                         |    |

| Table 35. | Peripheral current consumption                                                   |    |

| Table 36. | Low-power mode wakeup timings                                                    | 67 |

| Table 37. | High-speed external user clock characteristics                                   | 67 |

| Table 38. | Low-speed external user clock characteristics                                    |    |

| Table 39. | HSE oscillator characteristics                                                   | 69 |

| Table 40. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                   |    |

| Table 41. | HSI oscillator characteristics.                                                  |    |

| Table 42. | HSI14 oscillator characteristics                                                 |    |

| Table 43. | HSI48 oscillator characteristics                                                 |    |

| Table 44. | LSI oscillator characteristics                                                   |    |

| Table 45. | PLL characteristics                                                              |    |

| Table 46. | riash memory characteristics                                                     | /5 |

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F091xB/xC microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website <a href="https://www.st.com">www.st.com</a>.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

Table 2. STM32F091xB/xC family device features and peripheral counts

| Perip               | heral                                 | STM32                                                                                                                | F091Cx      | STM32 | F091Rx                | STM32 | 2F091Vx        |  |  |  |  |  |

|---------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|-------|-----------------------|-------|----------------|--|--|--|--|--|

| Flash mem           | nory (Kbyte)                          | 128                                                                                                                  | 256         | 128   | 256                   | 128   | 256            |  |  |  |  |  |

| SRAM                | (Kbyte)                               |                                                                                                                      | 32          |       |                       |       |                |  |  |  |  |  |

|                     | Advanced control                      |                                                                                                                      | 1 (16-bit)  |       |                       |       |                |  |  |  |  |  |

| Timers              | General purpose                       | 5 (16-bit)<br>1 (32-bit)                                                                                             |             |       |                       |       |                |  |  |  |  |  |

|                     | Basic                                 | 2 (16-bit)                                                                                                           |             |       |                       |       |                |  |  |  |  |  |

|                     | SPI [I <sup>2</sup> S] <sup>(1)</sup> |                                                                                                                      | 2 [2]       |       |                       |       |                |  |  |  |  |  |

| Comm.<br>interfaces | I <sup>2</sup> C                      |                                                                                                                      |             |       | 2                     |       |                |  |  |  |  |  |

|                     | USART                                 | (                                                                                                                    | 3           |       |                       | 8     |                |  |  |  |  |  |

|                     | CAN                                   | 1                                                                                                                    |             |       |                       |       |                |  |  |  |  |  |

|                     | CEC                                   | 1                                                                                                                    |             |       |                       |       |                |  |  |  |  |  |

|                     | t ADC<br>f channels)                  | 1 (10 ext. + 3 int.) 1 (16 ext. + 3 int.)                                                                            |             |       |                       |       |                |  |  |  |  |  |

|                     | t DAC<br>f channels)                  | 1 (2)                                                                                                                |             |       |                       |       |                |  |  |  |  |  |

| Analog co           | omparator                             | 2                                                                                                                    |             |       |                       |       |                |  |  |  |  |  |

| GP                  | lOs                                   | 3                                                                                                                    | 8           |       | 52                    |       | 38             |  |  |  |  |  |

|                     | re sensing<br>nnels                   | 1                                                                                                                    | 7           | ,     | 18                    | 2     | 24             |  |  |  |  |  |

| Max. CPU            | frequency                             | 48 MHz                                                                                                               |             |       |                       |       |                |  |  |  |  |  |

| Operatin            | g voltage                             |                                                                                                                      |             | 2.0   | to 3.6 V              |       |                |  |  |  |  |  |

| Operating t         | emperature                            | Ambient operating temperature: -40°C to 85°C / -40°C to 105°C  Junction temperature: -40°C to 105°C / -40°C to 125°C |             |       |                       |       |                |  |  |  |  |  |

| Pack                | kages                                 | LQF<br>UFQF                                                                                                          | P48<br>PN48 | UFB   | FP64<br>GA64<br>CSP64 |       | FP100<br>GA100 |  |  |  |  |  |

<sup>1.</sup> The SPI interface can be used either in SPI mode or in I<sup>2</sup>S audio mode.

### 3 Functional overview

Figure 1 shows the general block diagram of the STM32F091xB/xC devices.

## 3.1 ARM®-Cortex®-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F091xB/xC devices embed ARM core and are compatible with all ARM tools and software.

#### 3.2 Memories

The device has the following features:

- 32 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- up to 256 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

### 3.3 Boot modes

At startup, the boot pin and boot selector option bits are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot pin is shared with the standard GPIO and can be disabled through the boot selector option bits. The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10 or I<sup>2</sup>C on pins PB6/PB7.

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

### 3.8 Direct memory access controller (DMA)

The 12-channel general-purpose DMAs (seven channels for DMA1 and five channels for DMA2) manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMAs support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

### 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

Table 13. STM32F091xB/xC pin definitions (continued)

|          | Pi      | n nui   | mber   | s       |                 |                                      |          |                        |                    | Pin functions                                                                  |                         |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|------------------------|--------------------|--------------------------------------------------------------------------------|-------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure<br>Notes |                    | Alternate functions                                                            | Additional<br>functions |  |

| C5       | 91      | C4      | 57     | C5      | 41              | PB5                                  | I/O      | FT                     |                    | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2,<br>USART5_CK_RTS | WKUP6                   |  |

| B5       | 92      | D3      | 58     | A5      | 42              | PB6                                  | I/O      | FTf                    |                    | I2C1_SCL, USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                              | -                       |  |

| B4       | 93      | C3      | 59     | B5      | 43              | PB7                                  | I/O      | FTf                    |                    | I2C1_SDA, USART1_RX,<br>USART4_CTS,<br>TIM17_CH1N,<br>TSC_G5_IO4               | -                       |  |

| A4       | 94      | B4      | 60     | C6      | 44              | PF11-BOOT0                           | I/O      | FT                     |                    | -                                                                              | Boot memory selection   |  |

| A3       | 95      | В3      | 61     | A6      | 45              | PB8                                  | I/O      | FTf                    |                    | I2C1_SCL, CEC,<br>TIM16_CH1, TSC_SYNC,<br>CAN_RX                               | -                       |  |

| В3       | 96      | A3      | 62     | В6      | 46              | PB9                                  | I/O      | FTf                    | SPI2_NSS, I2S2_WS, |                                                                                | -                       |  |

| СЗ       | 97      | ı       | -      | -       | ı               | PE0                                  | I/O      | FT                     |                    | EVENTOUT, TIM16_CH1                                                            | -                       |  |

| A2       | 98      | -       | -      | -       | -               | PE1                                  | I/O      | FT                     |                    | EVENTOUT, TIM17_CH1                                                            | -                       |  |

| D3       | 99      | D4      | 63     | A7      | 47              | VSS                                  | S        | -                      |                    | Ground                                                                         |                         |  |

| C4       | 100     | E4      | 64     | A8      | 48              | VDD                                  | S        | -                      |                    | Digital power su                                                               | ıpply                   |  |

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

- The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These GPIOs must not be used as current sources (e.g. to drive an LED).

DocID026284 Rev 4 40/128

<sup>2.</sup> After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

<sup>3.</sup> PC6, PC7, PC8, PC9, PA8, PA9, PA10, PA11, PA12, PA13, PF6, PA14, PA15, PC10, PC11, PC12, PD0, PD1 and PD2 I/Os are supplied by VDDIO2

<sup>4.</sup> After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

Table 14. Alternate functions selected through GPIOA\_AFR registers for port A

| Pin name | AF0                 | AF1        | AF2          | AF3        | AF4        | AF5        | AF6      | AF7       |

|----------|---------------------|------------|--------------|------------|------------|------------|----------|-----------|

| PA0      | -                   | USART2_CTS | TIM2_CH1_ETR | TSC_G1_IO1 | USART4_TX  | -          | -        | COMP1_OUT |

| PA1      | EVENTOUT            | USART2_RTS | TIM2_CH2     | TSC_G1_IO2 | USART4_RX  | TIM15_CH1N | -        | -         |

| PA2      | TIM15_CH1           | USART2_TX  | TIM2_CH3     | TSC_G1_IO3 | -          | -          | -        | COMP2_OUT |

| PA3      | TIM15_CH2           | USART2_RX  | TIM2_CH4     | TSC_G1_IO4 | -          | -          | -        | -         |

| PA4      | SPI1_NSS, I2S1_WS   | USART2_CK  | -            | TSC_G2_IO1 | TIM14_CH1  | USART6_TX  | -        | -         |

| PA5      | SPI1_SCK, I2S1_CK   | CEC        | TIM2_CH1_ETR | TSC_G2_IO2 | -          | USART6_RX  | -        | -         |

| PA6      | SPI1_MISO, I2S1_MCK | TIM3_CH1   | TIM1_BKIN    | TSC_G2_IO3 | USART3_CTS | TIM16_CH1  | EVENTOUT | COMP1_OUT |

| PA7      | SPI1_MOSI, I2S1_SD  | TIM3_CH2   | TIM1_CH1N    | TSC_G2_IO4 | TIM14_CH1  | TIM17_CH1  | EVENTOUT | COMP2_OUT |

| PA8      | MCO                 | USART1_CK  | TIM1_CH1     | EVENTOUT   | CRS_SYNC   | -          | -        | -         |

| PA9      | TIM15_BKIN          | USART1_TX  | TIM1_CH2     | TSC_G4_IO1 | I2C1_SCL   | MCO        | -        | -         |

| PA10     | TIM17_BKIN          | USART1_RX  | TIM1_CH3     | TSC_G4_IO2 | I2C1_SDA   | -          | -        | -         |

| PA11     | EVENTOUT            | USART1_CTS | TIM1_CH4     | TSC_G4_IO3 | CAN_RX     | I2C2_SCL   | -        | COMP1_OUT |

| PA12     | EVENTOUT            | USART1_RTS | TIM1_ETR     | TSC_G4_IO4 | CAN_TX     | I2C2_SDA   | -        | COMP2_OUT |

| PA13     | SWDIO               | IR_OUT     | -            | -          | -          | -          | -        | -         |

| PA14     | SWCLK               | USART2_TX  | -            | -          | -          | -          | -        | -         |

| PA15     | SPI1_NSS, I2S1_WS   | USART2_RX  | TIM2_CH1_ETR | EVENTOUT   | USART4_RTS | -          | -        | -         |

|          | Table 15. Alternate functions selected through GPIOB_AFR registers for port B |           |            |            |               |                   |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------|-----------|------------|------------|---------------|-------------------|--|--|--|--|--|--|

| Pin name | AF0                                                                           | AF1       | AF2        | AF3        | AF4           | AF5               |  |  |  |  |  |  |

| PB0      | EVENTOUT                                                                      | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 | USART3_CK     | -                 |  |  |  |  |  |  |

| PB1      | TIM14_CH1                                                                     | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 | USART3_RTS    | -                 |  |  |  |  |  |  |

| PB2      | -                                                                             | -         | -          | TSC_G3_IO4 | -             | -                 |  |  |  |  |  |  |

| PB3      | SPI1_SCK, I2S1_CK                                                             | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 | USART5_TX     | -                 |  |  |  |  |  |  |

| PB4      | SPI1_MISO, I2S1_MCK                                                           | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 | USART5_RX     | TIM17_BKIN        |  |  |  |  |  |  |

| PB5      | SPI1_MOSI, I2S1_SD                                                            | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  | USART5_CK_RTS | -                 |  |  |  |  |  |  |

| PB6      | USART1_TX                                                                     | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 | -             | -                 |  |  |  |  |  |  |

| PB7      | USART1_RX                                                                     | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 | USART4_CTS    | -                 |  |  |  |  |  |  |

| PB8      | CEC                                                                           | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   | CAN_RX        | -                 |  |  |  |  |  |  |

| PB9      | IR_OUT                                                                        | I2C1_SDA  | TIM17_CH1  | EVENTOUT   | CAN_TX        | SPI2_NSS, I2S2_WS |  |  |  |  |  |  |

| PB10     | CEC                                                                           | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   | USART3_TX     | SPI2_SCK, I2S2_CK |  |  |  |  |  |  |

| PB11     | EVENTOUT                                                                      | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 | USART3_RX     | -                 |  |  |  |  |  |  |

| PB12     | SPI2_NSS, I2S2_WS                                                             | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 | USART3_CK     | TIM15_BKIN        |  |  |  |  |  |  |

| PB13     | SPI2_SCK, I2S2_CK                                                             | -         | TIM1_CH1N  | TSC_G6_IO3 | USART3_CTS    | I2C2_SCL          |  |  |  |  |  |  |

| PB14     | SPI2_MISO, I2S2_MCK                                                           | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 | USART3_RTS    | I2C2_SDA          |  |  |  |  |  |  |

| PB15     | SPI2_MOSI, I2S2_SD                                                            | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N | -             | -                 |  |  |  |  |  |  |

Table 18. Alternate functions selected through GPIOE\_AFR registers for port E

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_IO2          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | USART5_CK_RTS       |

| PE8      | TIM1_CH1N | USART4_TX           |

| PE9      | TIM1_CH1  | USART4_RX           |

| PE10     | TIM1_CH2N | USART5_TX           |

| PE11     | TIM1_CH2  | USART5_RX           |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

Table 19. Alternate functions selected through GPIOF\_AFR registers for port F

| Pin<br>name | AF0       | AF1       | AF2           |

|-------------|-----------|-----------|---------------|

| PF0         | CRS_SYNC  | I2C1_SDA  | -             |

| PF1         | -         | I2C1_SCL  | -             |

| PF2         | EVENTOUT  | USART7_TX | USART7_CK_RTS |

| PF3         | EVENTOUT  | USART7_RX | USART6_CK_RTS |

| PF6         | -         | -         | -             |

| PF9         | TIM15_CH1 | USART6_TX | -             |

| PF10        | TIM15_CH2 | USART6_RX | -             |

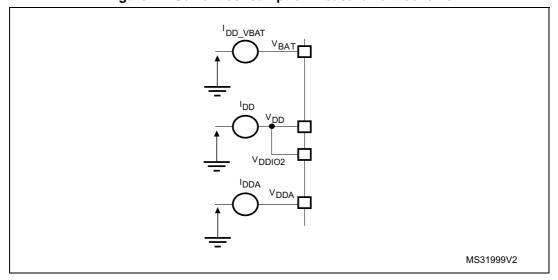

## 6.1.7 Current consumption measurement

Figure 14. Current consumption measurement scheme

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 29* to *Table 32* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

1. Data based on characterization results, not tested in production unless otherwise specified.

Table 30. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

|                  | Para-meter                     |                       |                   |     | V <sub>DDA</sub> | = 2.4 V             | 1      |     | V <sub>DDA</sub> | = 3.6 \ | /                |      |

|------------------|--------------------------------|-----------------------|-------------------|-----|------------------|---------------------|--------|-----|------------------|---------|------------------|------|

| Symbol           |                                | Conditions (1)        | f <sub>HCLK</sub> |     | М                | ax @ T <sub>A</sub> | (2)    |     | М                | ax @ T  | A <sup>(2)</sup> | Unit |

|                  |                                |                       |                   | Тур | 25 °C            | 85 °C               | 105 °C | Тур | 25 °C            | 85 °C   | 105 °C           |      |

|                  |                                | HSI48                 | 48 MHz            | 312 | 333              | 338                 | 347    | 316 | 334              | 341     | 350              |      |

|                  | Supply<br>current in<br>Run or | HSE                   | 48 MHz            | 147 | 168              | 178                 | 181    | 160 | 181              | 192     | 197              |      |

|                  |                                | bypass,<br>PLL on     | 32 MHz            | 101 | 119              | 125                 | 127    | 109 | 127              | 135     | 138              |      |

|                  |                                |                       | 24 MHz            | 80  | 96               | 98                  | 100    | 87  | 101              | 106     | 109              |      |

|                  | Sleep<br>mode,                 | HSE                   | 8 MHz             | 2.8 | 3.5              | 3.7                 | 3.9    | 3.7 | 4.3              | 4.6     | 4.7              |      |

| I <sub>DDA</sub> | code                           | bypass,<br>PLL off    | 1 MHz             | 2.7 | 3.2              | 3.5                 | 3.8    | 3.3 | 3.9              | 4.4     | 4.7              | μA   |

|                  | from                           |                       | 48 MHz            | 214 | 243              | 254                 | 259    | 235 | 262              | 275     | 281              |      |

| m                | Flash<br>memory                | HSI clock,<br>PLL on  | 32 MHz            | 166 | 193              | 203                 | 204    | 185 | 207              | 216     | 220              |      |

|                  | or RAM                         | . 22 011              | 24 MHz            | 144 | 171              | 177                 | 178    | 161 | 180              | 187     | 190              |      |

|                  |                                | HSI clock,<br>PLL off | 8 MHz             | 65  | 83               | 85                  | 86     | 77  | 90               | 92      | 93               |      |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

<sup>2.</sup> Data based on characterization results, not tested in production unless otherwise specified.

Table 31. Typical and maximum consumption in Stop and Standby modes

| Sym-             | Para-                                |                                |                                                              |                       | Тур   | @V <sub>DD</sub> ( | V <sub>DD</sub> = \ | / <sub>DDA</sub> ) | -     | ,                      | Max <sup>(1)</sup>     |                         |      |  |

|------------------|--------------------------------------|--------------------------------|--------------------------------------------------------------|-----------------------|-------|--------------------|---------------------|--------------------|-------|------------------------|------------------------|-------------------------|------|--|

| bol              | meter                                |                                | Conditions                                                   | 2.0 V                 | 2.4 V | 2.7 V              | 3.0 V               | 3.3 V              | 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                  | Supply current in                    | mod                            | gulator in run<br>de, all<br>illators OFF                    | 14.6                  | 14.8  | 14.9               | 15.1                | 15.4               | 15.8  | 18                     | 51                     | 97                      |      |  |

| I <sub>DD</sub>  | Stop<br>mode                         | pow                            | gulator in low-<br>ver mode, all<br>illators OFF             | 3.3                   | 3.4   | 3.6                | 3.8                 | 4.1                | 4.4   | 11                     | 53                     | 106                     |      |  |

|                  | Supply current in                    | LSI<br>ON                      | ON and IWDG                                                  | 0.9                   | 1.0   | 1.1                | 1.2                 | 1.3                | 1.4   | 2.3                    | 2.7                    | 3.6                     |      |  |

|                  | Standby<br>mode                      | LSI<br>OF                      | OFF and IWDG                                                 | 0.6                   | 0.7   | 0.8                | 0.9                 | 1.0                | 1.1   | 1.9                    | 2.3                    | 3.0                     |      |  |

|                  | Supply<br>current in<br>Stop<br>mode | NO                             | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.9                   | 2.0   | 2.2                | 2.3                 | 2.4                | 2.6   | 3.8                    | 4.2                    | 4.6                     |      |  |

|                  |                                      | V <sub>DDA</sub> monitoring O  | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.9                   | 2.0   | 2.2                | 2.3                 | 2.4                | 2.6   | 3.8                    | 4.2                    | 4.6                     | μА   |  |

|                  | Supply current in                    |                                | V <sub>DE</sub>                                              | LSI ON and<br>IWDG ON | 2.3   | 2.5                | 2.7                 | 2.8                | 3.0   | 3.3                    | 3.8                    | 4.2                     | 4.8  |  |

| I <sub>DDA</sub> | Standby<br>mode                      |                                | LSI OFF and<br>IWDG OFF                                      | 1.8                   | 1.9   | 2.0                | 2.2                 | 2.3                | 2.5   | 3.6                    | 3.9                    | 4.2                     |      |  |

| IDDA             | Supply                               | OFF                            | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.2                   | 1.2   | 1.3                | 1.3                 | 1.4                | 1.4   | -                      | -                      | -                       |      |  |

|                  | current in<br>Stop<br>mode           | V <sub>DDA</sub> monitoring OF | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.2                   | 1.2   | 1.3                | 1.3                 | 1.4                | 1.4   | -                      | -                      | -                       |      |  |

|                  | Supply current in                    | V <sub>DD</sub>                | LSI ON and<br>IWDG ON                                        | 1.6                   | 1.7   | 1.8                | 1.9                 | 2.0                | 2.1   | -                      | -                      | -                       |      |  |

|                  | Standby<br>mode                      | tandby                         | LSI OFF and IWDG OFF                                         | 1.1                   | 1.1   | 1.1                | 1.2                 | 1.3                | 1.3   | -                      | -                      | -                       |      |  |

<sup>1.</sup> Data based on characterization results, not tested in production unless otherwise specified.

Table 35. Peripheral current consumption (continued)

|     | Peripheral                | Typical consumption at 25 °C | Unit   |  |  |  |  |  |

|-----|---------------------------|------------------------------|--------|--|--|--|--|--|

|     | APB-Bridge <sup>(2)</sup> | 3.6                          |        |  |  |  |  |  |

|     | ADC <sup>(3)</sup>        | 4.3                          |        |  |  |  |  |  |

|     | CAN                       | 12.4                         |        |  |  |  |  |  |

|     | CEC                       | 0.4                          |        |  |  |  |  |  |

|     | CRS                       | 0.0                          |        |  |  |  |  |  |

|     | DAC <sup>(3)</sup>        | 4.2                          |        |  |  |  |  |  |

|     | DBG (MCU Debug Support)   | 0.2                          |        |  |  |  |  |  |

|     | I2C1                      | 2.9                          |        |  |  |  |  |  |

|     | I2C2                      | 2.4                          |        |  |  |  |  |  |

|     | PWR                       | 0.6                          |        |  |  |  |  |  |

|     | SPI1                      | 8.8                          |        |  |  |  |  |  |

|     | SPI2                      | 7.8                          |        |  |  |  |  |  |

|     | SYSCFG and COMP           | 1.9                          |        |  |  |  |  |  |

|     | TIM1                      | 15.2                         |        |  |  |  |  |  |

|     | TIM14                     | 2.6                          |        |  |  |  |  |  |

| APB | TIM15                     | M15 8.7                      |        |  |  |  |  |  |

| APB | TIM16                     | 5.8                          | μA/MHz |  |  |  |  |  |

|     | TIM17                     | 7.0                          |        |  |  |  |  |  |

|     | TIM2                      | 16.2                         |        |  |  |  |  |  |

|     | TIM3                      | 11.9                         |        |  |  |  |  |  |

|     | TIM6                      | 11.8                         |        |  |  |  |  |  |

|     | TIM7                      | 2.5                          |        |  |  |  |  |  |

|     | USART1                    | 17.6                         |        |  |  |  |  |  |

|     | USART2                    | 16.3                         |        |  |  |  |  |  |

|     | USART3                    | 16.2                         |        |  |  |  |  |  |

|     | USART4                    | 4.7                          |        |  |  |  |  |  |

|     | USART5                    | 4.4                          |        |  |  |  |  |  |

|     | USART6                    | 5.5                          |        |  |  |  |  |  |

|     | USART7                    | 5.2                          |        |  |  |  |  |  |

|     | USART8                    | 5.1                          |        |  |  |  |  |  |

|     | WWDG                      | 1.1                          |        |  |  |  |  |  |

|     | All APB peripherals       | 207.2                        |        |  |  |  |  |  |

<sup>1.</sup> The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

<sup>2.</sup> The APB Bridge is automatically active when at least one peripheral is ON on the Bus.

The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, comparators, is not included. Refer to the tables of characteristics in the subsequent sections.

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |

Table 47. Flash memory endurance and data retention

- 1. Data based on characterization results, not tested in production.

- 2. Cycling performed over the whole temperature range.

### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                   | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 3.3 V, LQFP100, $T_A$ = +25 °C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-2  | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, $T_{A}$ = +25°C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-4 | 4B              |

**Table 48. EMS characteristics**

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Max                | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis         | -                                 | -                  | 200 | -                  | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | 2.7 < V <sub>DD</sub> < 3.6       | 300 <sup>(3)</sup> | -   | -                  | ns   |

|                        | TVIXOT Input flot lilitered pulse               | 2.0 < V <sub>DD</sub> < 3.6       | 500 <sup>(3)</sup> | -   | -                  | 113  |

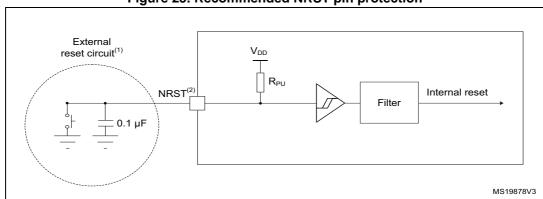

Table 56. NRST pin characteristics (continued)

- 1. Data based on design simulation only. Not tested in production.

- 2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

- 3. Data based on design simulation only. Not tested in production.

Figure 25. Recommended NRST pin protection

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

### 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Symbol Conditions** Unit **Parameter** Min Тур Max Analog supply voltage for 2.4 3.6 ٧  $V_{DDA}$ ADC ON Current consumption of  $V_{DDA} = 3.3 V$ 0.9 mA I<sub>DDA</sub> (ADC) the ADC<sup>(1)</sup> ADC clock frequency 0.6 14 MHz  $f_{ADC}$  $f_S^{(2)}$ Sampling rate 12-bit resolution 0.043 1 MHz

Table 57. ADC characteristics

Table 61. Comparator characteristics (continued)

| Symbol           | Parameter             | Condition                                | Min <sup>(1)</sup>    | Тур | Max <sup>(1)</sup> | Unit |    |

|------------------|-----------------------|------------------------------------------|-----------------------|-----|--------------------|------|----|

|                  | Comparator hysteresis | No hysteresis (COMPxHYST[1:0]=00)        | -                     | -   | 0                  | -    |    |

|                  |                       | Low hysteresis<br>(COMPxHYST[1:0]=01)    | High speed mode       | 3   | 8                  | 13   | mV |

|                  |                       |                                          | All other power modes | 5   |                    | 10   |    |

| V <sub>hys</sub> |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7   | 15                 | 26   |    |

|                  |                       |                                          | All other power modes | 9   |                    | 19   |    |

|                  |                       | High hystoropia                          | High speed mode       | 18  |                    | 49   |    |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | All other power modes | 19  | 31                 | 40   |    |

<sup>1.</sup> Data based on characterization results, not tested in production.

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

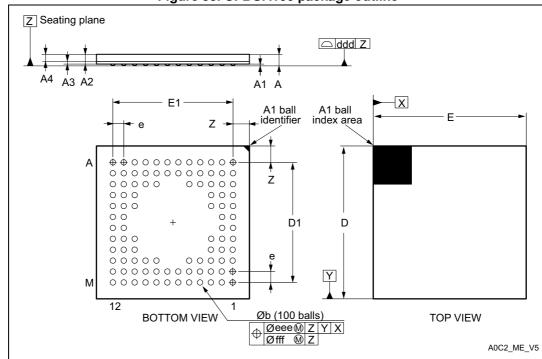

## 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 33. UFBGA100 package outline

1. Drawing is not to scale.

100/128

Table 70. UFBGA100 package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| Α      | -           | -     | 0.600 | -                     | -      | 0.0236 |  |

| A1     | -           | -     | 0.110 | -                     | -      | 0.0043 |  |

| A2     | -           | 0.450 | -     | -                     | 0.0177 | -      |  |

| A3     | -           | 0.130 | -     | -                     | 0.0051 | 0.0094 |  |

| A4     | -           | 0.320 | -     | -                     | 0.0126 | -      |  |

DocID026284 Rev 4

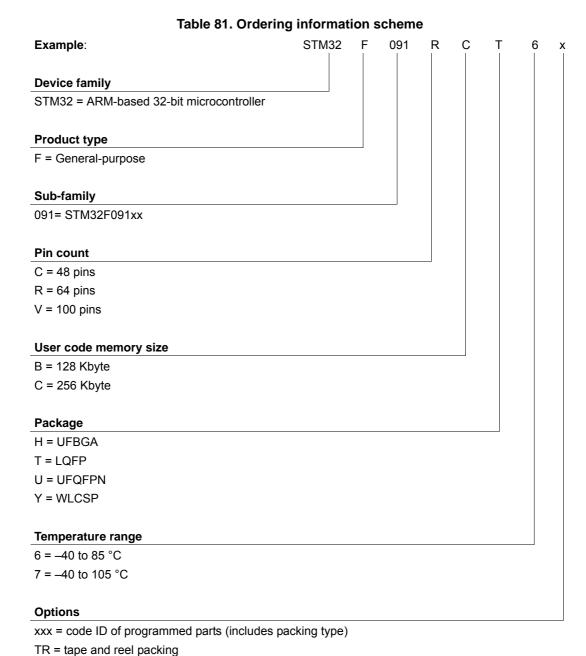

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID026284 Rev 4

blank = tray packing