Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

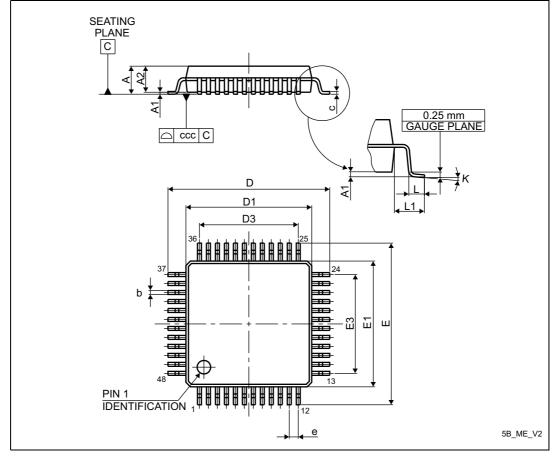

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091rbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F091xB/xC microcontrollers incorporate the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC core operating at up to 48 MHz frequency, high-speed embedded memories (up to 256 Kbytes of Flash memory and 32 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. The device offers standard communication interfaces (two I<sup>2</sup>Cs, two SPIs/one I<sup>2</sup>S, one HDMI CEC and up to eight USARTs), one CAN, one 12-bit ADC, one 12-bit DAC with two channels, seven 16-bit timers, one 32-bit timer and an advanced-control PWM timer.

The STM32F091xB/xC microcontrollers operate in the -40 to +85 °C and -40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F091xB/xC microcontrollers include devices in seven different packages ranging from 48 pins to 100 pins with a die form also available upon request. Depending on the device chosen, different sets of peripherals are included.

These features make the STM32F091xB/xC microcontrollers suitable for a wide range of applications such as application control and user interfaces, hand-held equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms and HVACs.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 88 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

| USART modes/features <sup>(1)</sup>         | USART1<br>USART2<br>USART3 | USART4 | USART5<br>USART6<br>USART7<br>USART8 |  |  |  |  |  |  |

|---------------------------------------------|----------------------------|--------|--------------------------------------|--|--|--|--|--|--|

| Single-wire half-duplex communication       | Х                          | Х      | Х                                    |  |  |  |  |  |  |

| IrDA SIR ENDEC block                        | Х                          | -      | -                                    |  |  |  |  |  |  |

| LIN mode                                    | Х                          | -      | -                                    |  |  |  |  |  |  |

| Dual clock domain and wakeup from Stop mode | Х                          | -      | -                                    |  |  |  |  |  |  |

| Receiver timeout interrupt                  | Х                          | -      | -                                    |  |  |  |  |  |  |

| Modbus communication                        | Х                          | -      | -                                    |  |  |  |  |  |  |

| Auto baud rate detection                    | Х                          | -      | -                                    |  |  |  |  |  |  |

| Driver Enable                               | Х                          | Х      | Х                                    |  |  |  |  |  |  |

#### Table 10. STM32F091xB/xC USART implementation (continued)

1. X = supported.

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI1 and SPI2 respectively) supporting four different audio standards can operate as master or slave at half-duplex communication mode. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, they can output a clock for an external audio component at 256 times the sampling frequency.

| SPI features <sup>(1)</sup> | SPI1 and SPI2 |

|-----------------------------|---------------|

| Hardware CRC calculation    | Х             |

| Rx/Tx FIFO                  | Х             |

| NSS pulse mode              | Х             |

| I <sup>2</sup> S mode       | Х             |

| TI mode                     | Х             |

Table 11. STM32F091xB/xC SPI/I<sup>2</sup>S implementation

1. X = supported.

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

## 3.20 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.21 Clock recovery system (CRS)

The STM32F091xB/xC embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.22 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

|          | Pi      | n nui   | mber   | s       |                 |                                      |          |                        |  | Pin functions                                                                    |                                                    |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|------------------------|--|----------------------------------------------------------------------------------|----------------------------------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure<br>Notes |  | Alternate functions                                                              | Additional<br>functions                            |  |

| J1       | 19      | -       | -      | -       | -               | PF2                                  | I/O      | FT                     |  | EVENTOUT,<br>USART7_TX,<br>USART7_CK_RTS                                         | WKUP8                                              |  |

| K1       | 20      | F1      | 12     | G8      | 8               | VSSA                                 | S        | -                      |  | Analog grou                                                                      | nd                                                 |  |

| M1       | 21      | H1      | 13     | H8      | 9               | VDDA                                 | S        | -                      |  | Analog power s                                                                   | upply                                              |  |

| L1       | 22      | -       | -      | -       | -               | PF3                                  | I/O      | FT                     |  | EVENTOUT,<br>USART7_RX,<br>USART6_CK_RTS                                         |                                                    |  |

| L2       | 23      | G2      | 14     | F7      | 10              | PA0                                  | I/O      | TTa                    |  | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX<br>COMP1_OUT            | RTC_ TAMP2,<br>WKUP1,<br>ADC_IN0,<br>COMP1_INM6    |  |

| M2       | 24      | H2      | 15     | F6      | 11              | PA1                                  | I/O      | ТТа                    |  | USART2_RTS,<br>TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX,<br>EVENTOUT | ADC_IN1,<br>COMP1_INP                              |  |

| КЗ       | 25      | F3      | 16     | E5      | 12              | PA2                                  | I/O      | TTa                    |  | USART2_TX, TIM2_CH3,<br>TIM15_CH1,<br>TSC_G1_IO3<br>COMP2_OUT                    | ADC_IN2,<br>WKUP4,<br>COMP2_INM6                   |  |

| L3       | 26      | G3      | 17     | H7      | 13              | PA3                                  | I/O      | ТТа                    |  | USART2_RX,TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4                                  | ADC_IN3,<br>COMP2_INP                              |  |

| D3       | 27      | C2      | 18     | G7      | -               | VSS                                  | S        | -                      |  | Ground                                                                           |                                                    |  |

| H3       | 28      | D2      | 19     | G6      | -               | VDD                                  | S        | -                      |  | Digital power supply                                                             |                                                    |  |

| М3       | 29      | H3      | 20     | H6      | 14              | PA4                                  | I/O      | TTa                    |  | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK,<br>USART6_TX       | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |  |

| K4       | 30      | F4      | 21     | F5      | 15              | PA5                                  | I/O      | ТТа                    |  | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2,<br>USART6_RX          | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |  |

| Table 13. STM32F091xB/xC pin definitions (continued) |

|------------------------------------------------------|

|------------------------------------------------------|

\_\_\_\_

|          | Pi      | in nui  | mber   |         |                 | 13. 01111321 0317                    |          | •             |                                              | Pin functions                                                                    |                         |  |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|----------------------------------------------|----------------------------------------------------------------------------------|-------------------------|--|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes                                        | Alternate functions                                                              | Additional<br>functions |  |  |

| J10      | 59      | -       | -      | -       | -               | PD12                                 | I/O      | FT            |                                              | USART3_RTS,<br>TSC_G8_IO1,<br>USART8_CK_RTS                                      | -                       |  |  |

| H12      | 60      | -       | -      | -       | -               | PD13                                 | I/O      | FT            |                                              | TSC_G8_IO2,<br>USART8_TX                                                         | -                       |  |  |

| H11      | 61      | -       | -      | -       | -               | PD14                                 | I/O      | FT            |                                              | TSC_G8_IO3,<br>USART8_RX                                                         | -                       |  |  |

| H10      | 62      | -       | -      | -       | -               | PD15                                 | I/O      | FT            | TSC_G8_IO4,<br>FT CRS_SYNC,<br>USART7_CK_RTS |                                                                                  | -                       |  |  |

| E12      | 63      | F6      | 37     | E1      | -               | PC6                                  | I/O      | FT            | (3)                                          | TIM3_CH1, USART7_TX                                                              | -                       |  |  |

| E11      | 64      | E7      | 38     | D1      | -               | PC7                                  | I/O      | FT            | (3)                                          | TIM3_CH2, USART7_RX                                                              | -                       |  |  |

| E10      | 65      | E8      | 39     | E2      | -               | PC8                                  | I/O      | FT            | (3)                                          | TIM3_CH3, USART8_TX                                                              | -                       |  |  |

| D12      | 66      | D8      | 40     | E3      | -               | PC9                                  | I/O      | FT            | FT <sup>(3)</sup> TIM3_CH4, USART8_RX        |                                                                                  | -                       |  |  |

| D11      | 67      | D7      | 41     | D2      | 29              | PA8                                  | I/O      | FT            | (3)                                          | USART1_CK, TIM1_CH1,<br>EVENTOUT, MCO,<br>CRS_SYNC                               | -                       |  |  |

| D10      | 68      | C7      | 42     | C1      | 30              | PA9                                  | I/O      | FT            | (3)                                          | USART1_TX, TIM1_CH2,<br>TIM15_BKIN, MCO,<br>TSC_G4_IO1, I2C1_SCL                 | -                       |  |  |

| C12      | 69      | C6      | 43     | C2      | 31              | PA10                                 | I/O      | FT            | (3)                                          | USART1_RX, TIM1_CH3,<br>TIM17_BKIN,<br>TSC_G4_IO2, I2C1_SDA                      | -                       |  |  |

| B12      | 70      | C8      | 44     | D3      | 32              | PA11                                 | I/O      | FT            | (3)                                          | CAN_RX, USART1_CTS,<br>TIM1_CH4, COMP1_OUT,<br>TSC_G4_IO3,<br>EVENTOUT, I2C2_SCL | -                       |  |  |

| A12      | 71      | B8      | 45     | B1      | 33              | PA12                                 | I/O      | FT            | (3)                                          | CAN_TX, USART1_RTS,<br>TIM1_ETR, COMP2_OUT,<br>TSC_G4_IO4,<br>EVENTOUT, I2C2_SDA | -                       |  |  |

| A11      | 72      | A8      | 46     | C3      | 34              | PA13                                 | I/O      | FT            | (3)<br>(4)                                   | IR_OUT, SWDIO                                                                    | -                       |  |  |

| C11      | 73      | -       | -      | -       | -               | PF6                                  | I/O      | FT            | (3)                                          | -                                                                                | -                       |  |  |

| F11      | 74      | D6      | 47     | B2      | 35              | VSS                                  | S        | -             |                                              | Ground                                                                           |                         |  |  |

| G11      | 75      | E6      | 48     | A1      | 36              | VDDIO2                               | S        | -             |                                              | Digital power su                                                                 | ıpply                   |  |  |

Table 13. STM32F091xB/xC pin definitions (continued)

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

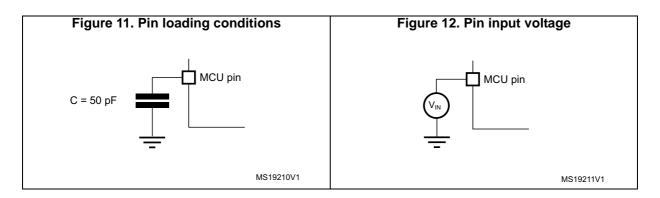

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

## 6.1.5 Pin input voltage

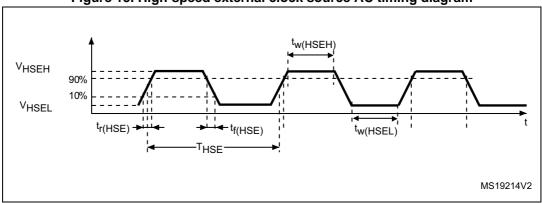

The input voltage measurement on a pin of the device is described in *Figure 12*.

1. Data based on characterization results, not tested in production unless otherwise specified.

|                  | er                       |                       |                   |     | V <sub>DDA</sub> | = 2.4 V             | 1      |     | V <sub>DDA</sub> | = 3.6 \ | /      |    |

|------------------|--------------------------|-----------------------|-------------------|-----|------------------|---------------------|--------|-----|------------------|---------|--------|----|

| Symbol           | Bara-meter<br>Bara-meter | Conditions            | f <sub>HCLK</sub> |     | м                | ax @ T <sub>A</sub> | (2)    |     | Μ                | Unit    |        |    |

|                  | Para                     |                       |                   | Тур | 25 °C            | 85 °C               | 105 °C | Тур | 25 °C            | 85 °C   | 105 °C |    |

|                  |                          | HSI48                 | 48 MHz            | 312 | 333              | 338                 | 347    | 316 | 334              | 341     | 350    |    |

|                  |                          | HSE                   | 48 MHz            | 147 | 168              | 178                 | 181    | 160 | 181              | 192     | 197    |    |

|                  | Supply current in        | bypass.               | 32 MHz            | 101 | 119              | 125                 | 127    | 109 | 127              | 135     | 138    |    |

|                  | Run or                   |                       | 24 MHz            | 80  | 96               | 98                  | 100    | 87  | 101              | 106     | 109    |    |

|                  | Sleep<br>mode,           | HSE                   | 8 MHz             | 2.8 | 3.5              | 3.7                 | 3.9    | 3.7 | 4.3              | 4.6     | 4.7    |    |

| I <sub>DDA</sub> | code<br>executing        | bypass,<br>PLL off    | 1 MHz             | 2.7 | 3.2              | 3.5                 | 3.8    | 3.3 | 3.9              | 4.4     | 4.7    | μA |

|                  | from<br>Flash<br>memory  | HSI clock,<br>PLL on  | 48 MHz            | 214 | 243              | 254                 | 259    | 235 | 262              | 275     | 281    |    |

|                  |                          |                       | 32 MHz            | 166 | 193              | 203                 | 204    | 185 | 207              | 216     | 220    |    |

| or RAM           | or RAM                   |                       | 24 MHz            | 144 | 171              | 177                 | 178    | 161 | 180              | 187     | 190    |    |

|                  |                          | HSI clock,<br>PLL off | 8 MHz             | 65  | 83               | 85                  | 86     | 77  | 90               | 92      | 93     |    |

| Table 30. Typical and maximum current consumption from the $\rm V_{DDA}$ supply |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

|                      | Parameter         | Conditions                                                                       | Тур @ V <sub>BAT</sub> |       |       |       |       |       |                           |                           |                            |      |

|----------------------|-------------------|----------------------------------------------------------------------------------|------------------------|-------|-------|-------|-------|-------|---------------------------|---------------------------|----------------------------|------|

| Symbol               |                   |                                                                                  | 1.65 V                 | 1.8 V | 2.4 V | 2.7 V | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | RTC<br>domain     | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5                    | 0.5   | 0.6   | 0.7   | 0.9   | 1.0   | 1.0                       | 1.3                       | 1.8                        |      |

| I <sub>DD_VBAT</sub> | supply<br>current | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8                    | 0.8   | 0.9   | 1.0   | 1.2   | 1.3   | 1.4                       | 1.7                       | 2.2                        | μA   |

Table 32. Typical and maximum current consumption from the  $\rm V_{BAT}$  supply

1. Data based on characterization results, not tested in production.

## Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

## **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 35*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 21: Voltage characteristics*

|     | Peripheral               | Typical consumption at 25 °C | Unit   |  |

|-----|--------------------------|------------------------------|--------|--|

|     | BusMatrix <sup>(1)</sup> | 3.1                          |        |  |

|     | CRC                      | 2.0                          |        |  |

|     | DMA1                     | 5.5                          |        |  |

|     | DMA2                     | 5.1                          |        |  |

|     | Flash memory interface   | 15.4                         |        |  |

|     | GPIOA                    | 5.5                          |        |  |

| AHB | GPIOB                    | 5.4                          | µA/MHz |  |

| АПБ | GPIOC                    | 3.2                          |        |  |

|     | GPIOD                    | 3.1                          |        |  |

|     | GPIOE                    | 4.0                          |        |  |

|     | GPIOF                    | 2.5                          |        |  |

|     | SRAM                     | 0.8                          |        |  |

|     | TSC                      | 5.5                          |        |  |

|     | All AHB peripherals      | 61.0                         |        |  |

#### Table 35. Peripheral current consumption

|     | Peripheral                | Typical consumption (continued | /<br>Unit |

|-----|---------------------------|--------------------------------|-----------|

|     | APB-Bridge <sup>(2)</sup> | 3.6                            |           |

|     | ADC <sup>(3)</sup>        | 4.3                            |           |

|     | CAN                       | 12.4                           |           |

|     | CEC                       | 0.4                            |           |

|     | CRS                       | 0.0                            |           |

|     | DAC <sup>(3)</sup>        | 4.2                            |           |

|     | DBG (MCU Debug Support)   | 0.2                            |           |

|     | 12C1                      | 2.9                            |           |

|     | 12C2                      | 2.4                            |           |

|     | PWR                       | 0.6                            |           |

|     | SPI1                      | 8.8                            |           |

|     | SPI2                      | 7.8                            |           |

|     | SYSCFG and COMP           | 1.9                            |           |

|     | TIM1                      | 15.2                           |           |

|     | TIM14                     | 2.6                            |           |

|     | TIM15                     | 8.7                            |           |

| APB | TIM16                     | 5.8                            | µA/MHz    |

|     | TIM17                     | 7.0                            |           |

|     | TIM2                      | 16.2                           |           |

|     | TIM3                      | 11.9                           |           |

|     | TIM6                      | 11.8                           |           |

|     | TIM7                      | 2.5                            |           |

|     | USART1                    | 17.6                           |           |

|     | USART2                    | 16.3                           |           |

|     | USART3                    | 16.2                           |           |

|     | USART4                    | 4.7                            |           |

|     | USART5                    | 4.4                            |           |

|     | USART6                    | 5.5                            |           |

|     | USART7                    | 5.2                            |           |

|     | USART8                    | 5.1                            |           |

|     | 00/11/10                  | 1                              |           |

|     | WWDG                      | 1.1                            |           |

Table 35. Peripheral current consumption (continued)

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

2. The APB Bridge is automatically active when at least one peripheral is ON on the Bus.

3. The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, comparators, is not included. Refer to the tables of characteristics in the subsequent sections.

1. Guaranteed by design, not tested in production.

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

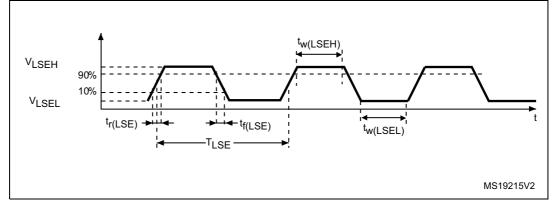

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | $V_{SS}$               | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 38. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

DocID026284 Rev 4

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter                     | Conditions                                       | Conditions Monitored |    | Unit |

|--------|-------------------------------|--------------------------------------------------|----------------------|----|------|

|        |                               | oonaniono                                        | frequency band       |    | onit |

|        |                               | V <sub>DD</sub> = 3.6 V, T <sub>Δ</sub> = 25 °C, | 0.1 to 30 MHz        | 3  |      |

| 6      | Peak level                    |                                                  | 30 to 130 MHz        | 23 | dBµV |

|        | compliant with<br>IEC 61967-2 | 130 MHz to 1 GHz                                 | 15                   |    |      |

|        |                               |                                                  | EMI Level            | 4  | -    |

#### Table 49. EMI characteristics

## 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Мах                | Unit |  |

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|--|

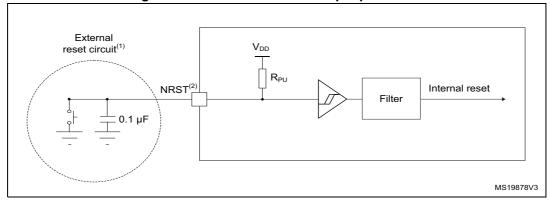

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                  | 200 | -                  | mV   |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |  |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |  |

| V                      | NRST input not filtered pulse                   | $2.7 < V_{DD} < 3.6$              | 300 <sup>(3)</sup> | -   | _                  | ns   |  |

| V <sub>NF(NRST)</sub>  |                                                 | $2.0 < V_{DD} < 3.6$              | 500 <sup>(3)</sup> | -   | -                  | 115  |  |

Table 56. NRST pin characteristics (continued)

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

3. Data based on design simulation only. Not tested in production.

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

## 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Table 57. ADC c | haracteristics |

|-----------------|----------------|

|-----------------|----------------|

| Symbol                        | Parameter                                     | Conditions               | Min   | Тур | Max | Unit |  |

|-------------------------------|-----------------------------------------------|--------------------------|-------|-----|-----|------|--|

| V <sub>DDA</sub>              | Analog supply voltage for<br>ADC ON           | -                        | 2.4   | -   | 3.6 | V    |  |

| I <sub>DDA (ADC)</sub>        | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V | -     | 0.9 | -   | mA   |  |

| f <sub>ADC</sub>              | ADC clock frequency                           | -                        | 0.6   | -   | 14  | MHz  |  |

| f <sub>S</sub> <sup>(2)</sup> | Sampling rate                                 | 12-bit resolution        | 0.043 | -   | 1   | MHz  |  |

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| Table 58. R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz |                     |                                          |  |  |  |  |

|--------------------------------------------------------------|---------------------|------------------------------------------|--|--|--|--|

| T <sub>s</sub> (cycles)                                      | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |  |  |  |  |

| 1.5                                                          | 0.11                | 0.4                                      |  |  |  |  |

| 7.5                                                          | 0.54                | 5.9                                      |  |  |  |  |

| 13.5                                                         | 0.96                | 11.4                                     |  |  |  |  |

| 28.5                                                         | 2.04                | 25.2                                     |  |  |  |  |

| 41.5                                                         | 2.96                | 37.2                                     |  |  |  |  |

| 55.5                                                         | 3.96                | 50                                       |  |  |  |  |

| 71.5                                                         | 5.11                | NA                                       |  |  |  |  |

| 239.5                                                        | 17.1                | NA                                       |  |  |  |  |

1. Guaranteed by design, not tested in production.

## Table 59. ADC accuracy $^{(1)(2)(3)}$

| Symbol | Parameter                    | Test conditions                                                                                                    | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                                                    | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{PCLK} = 48 \text{ MHz},$                                                                                       | ±1   | ±1.5               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V                             | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | $T_A = 25 $ °C                                                                                                     | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     |                                                                                                                    | ±0.8 | ±1.5               |      |

| ET     | Total unadjusted error       |                                                                                                                    | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                                        | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.7 V to 3.6 V                           | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_{A} = -40 \text{ to } 105 \text{ °C}$                                                                           | ±0.7 | ±1.3               |      |

| EL     | Integral linearity error     |                                                                                                                    | ±1.2 | ±1.7               |      |

| ET     | Total unadjusted error       |                                                                                                                    | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                                        | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.4 V to 3.6 V<br>T <sub>A</sub> = 25 °C | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error |                                                                                                                    | ±0.7 | ±1.3               | 1    |

| EL     | Integral linearity error     |                                                                                                                    | ±1.2 | ±1.7               |      |

1. ADC DC accuracy values are measured after internal calibration.

## 6.3.19 Temperature sensor characteristics

| Table 62. TS characteristic |

|-----------------------------|

|-----------------------------|

| Symbol                             | Parameter                                     | Min  | Тур  | Max  | Unit  |

|------------------------------------|-----------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                 | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>      | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                  |      | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC compliant time when reading the           |      | -    | -    | μs    |

1. Guaranteed by design, not tested in production.

2. Measured at  $V_{DDA}$  = 3.3 V ± 10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 3: Temperature sensor calibration values.

## 6.3.20 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                           |  | Тур    | Max | Unit |

|------------------------------------|-----------------------------------------------------|--|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                |  | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement               |  | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                          |  | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the V <sub>BAT</sub> |  | -      | -   | μs   |

#### Table 63. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design, not tested in production.

## 6.3.21 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                | Parameter                                          | Conditions                    | Min | Тур                     | Max | Unit                 |

|-----------------------|----------------------------------------------------|-------------------------------|-----|-------------------------|-----|----------------------|

| t mu                  | Timer resolution time                              | -                             | -   | 1                       | -   | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub> | Timer resolution time                              | f <sub>TIMxCLK</sub> = 48 MHz | -   | 20.8                    | -   | ns                   |

| f <sub>EXT</sub>      | Timer external clock<br>frequency on CH1 to<br>CH4 | -                             | -   | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

|                       |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 24                      | -   | MHz                  |

| tmax_count            | 16-bit timer maximum period                        | -                             | -   | 2 <sup>16</sup>         | -   | t <sub>TIMxCLK</sub> |

|                       |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 1365                    | -   | μs                   |

|                       | 32-bit counter<br>maximum period                   | -                             | -   | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                       |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 89.48                   | -   | S                    |

Table 64. TIMx characteristics

## **Device marking**

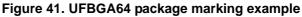

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

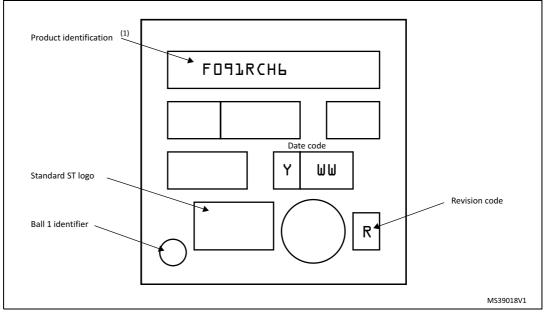

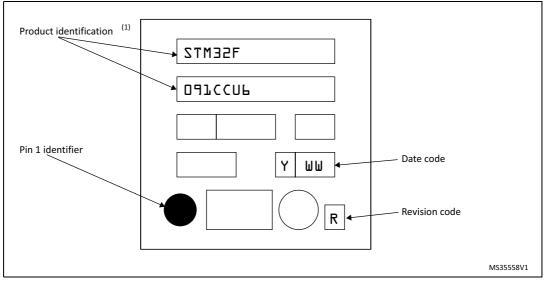

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7.6 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 53. UFQFPN48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.