Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                |                                                                       |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-UFBGA                                                              |

| Supplier Device Package    | 64-UFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091rch6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 6.3.11    | EMC characteristics                           |

|---|------|-----------|-----------------------------------------------|

|   |      | 6.3.12    | Electrical sensitivity characteristics77      |

|   |      | 6.3.13    | I/O current injection characteristics78       |

|   |      | 6.3.14    | I/O port characteristics                      |

|   |      | 6.3.15    | NRST pin characteristics                      |

|   |      | 6.3.16    | 12-bit ADC characteristics                    |

|   |      | 6.3.17    | DAC electrical specifications                 |

|   |      | 6.3.18    | Comparator characteristics91                  |

|   |      | 6.3.19    | Temperature sensor characteristics    93      |

|   |      | 6.3.20    | V <sub>BAT</sub> monitoring characteristics93 |

|   |      | 6.3.21    | Timer characteristics                         |

|   |      | 6.3.22    | Communication interfaces                      |

| 7 | Pack | age info  | ormation                                      |

|   | 7.1  | UFBGA     | A100 package information 100                  |

|   | 7.2  | LQFP1     | 00 package information 103                    |

|   | 7.3  | UFBG/     | A64 package information                       |

|   | 7.4  | WLCSI     | P64 package information 109                   |

|   | 7.5  | LQFP6     | 4 package information                         |

|   | 7.6  | LQFP4     | 8 package information                         |

|   | 7.7  | UFQFF     | PN48 package information118                   |

|   | 7.8  | Therma    | al characteristics                            |

|   |      | 7.8.1     | Reference document                            |

|   |      | 7.8.2     | Selecting the product temperature range       |

| 8 | Orde | ering inf | ormation                                      |

| 9 | Revi | sion his  | tory                                          |

# 3 Functional overview

*Figure 1* shows the general block diagram of the STM32F091xB/xC devices.

# 3.1 ARM<sup>®</sup>-Cortex<sup>®</sup>-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F091xB/xC devices embed ARM core and are compatible with all ARM tools and software.

## 3.2 Memories

The device has the following features:

- 32 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- up to 256 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

# 3.3 Boot modes

At startup, the boot pin and boot selector option bits are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot pin is shared with the standard GPIO and can be disabled through the boot selector option bits. The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10 or I<sup>2</sup>C on pins PB6/PB7.

DocID026284 Rev 4

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.5 **Power management**

## 3.5.1 Power supply schemes

- V<sub>DD</sub> = V<sub>DDIO1</sub> = 2.0 to 3.6 V: external power supply for I/Os (V<sub>DDIO1</sub>) and the internal regulator. It is provided externally through VDD pins.

- V<sub>DDA</sub> = from V<sub>DD</sub> to 3.6 V: external analog power supply for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC are used). It is provided externally through VDDA pin. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be established first.

- V<sub>DDIO2</sub> = 1.65 to 3.6 V: external power supply for marked I/Os. V<sub>DDIO2</sub> is provided externally through the VDDIO2 pin. The V<sub>DDIO2</sub> voltage level is completely independent from V<sub>DD</sub> or V<sub>DDA</sub>, but it must not be provided without a valid supply on V<sub>DD</sub>. The V<sub>DDIO2</sub> supply is monitored and compared with the internal reference voltage (V<sub>REFINT</sub>). When the V<sub>DDIO2</sub> is below this threshold, all the I/Os supplied from this rail are disabled by hardware. The output of this comparator is connected to EXTI line 31 and it can be used to generate an interrupt. Refer to the pinout diagrams or tables for concerned I/Os list.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 13: Power supply scheme*.

## 3.5.2 Power supply supervisors

The device has integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold,  $V_{\text{POR/PDR}}$ , without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$

back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

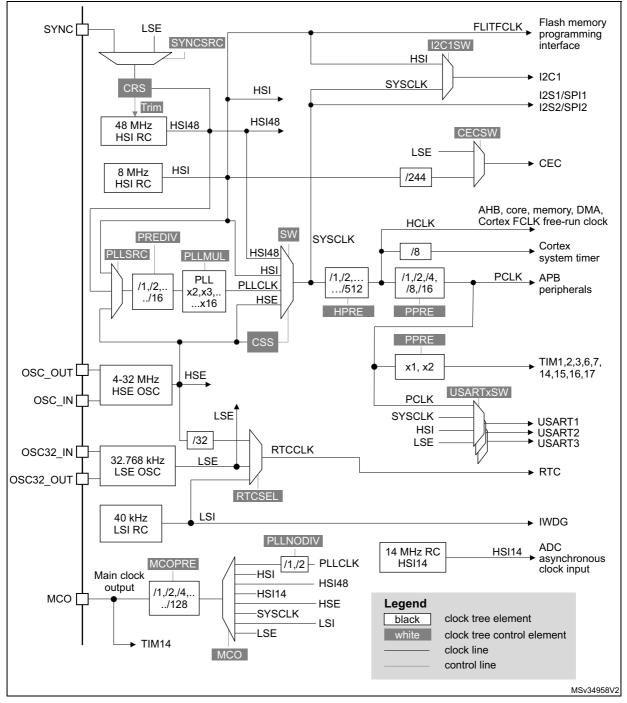

Figure 2. Clock tree

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

DocID026284 Rev 4

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 88 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

## 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

|                                       | Number of capacitive sensing channels |             |             |  |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|--|

| Analog I/O group                      | STM32F091Vx                           | STM32F091Rx | STM32F091Cx |  |  |  |

| G1                                    | 3                                     | 3           | 3           |  |  |  |

| G2                                    | 3                                     | 3           | 3           |  |  |  |

| G3                                    | 3                                     | 3           | 2           |  |  |  |

| G4                                    | 3                                     | 3           | 3           |  |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |  |

| G6                                    | 3                                     | 3           | 3           |  |  |  |

| G7                                    | 3                                     | 0           | 0           |  |  |  |

| G8                                    | 3                                     | 0           | 0           |  |  |  |

| Number of capacitive sensing channels | 24                                    | 18          | 17          |  |  |  |

#### Table 6. Number of capacitive sensing channels available on STM32F091xB/xC devices

# 3.14 Timers and watchdogs

The STM32F091xB/xC devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 7 compares the features of the different timers.

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|--------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |

|                    | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

|                    | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

| General<br>purpose | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                           | -                        |

|                    | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |

|                    | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |

| Basic              | TIM6<br>TIM7   | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                           | -                        |

Table 7. Timer feature comparison

# 4 Pinouts and pin descriptions

| Тор | op view               |           |        |                  |       |       |       |        |        |        |        |        |

|-----|-----------------------|-----------|--------|------------------|-------|-------|-------|--------|--------|--------|--------|--------|

| F   | 1                     | 2         | 3      | 4                | 5     | 6     | 7     | 8      | 9      | 10     | 11     | 12     |

|     |                       |           |        |                  |       |       |       |        |        |        |        |        |

| A   | (PE3)                 | (PE1)     | (PB8)  | (PF11-)<br>BOOT0 | (PD7) | (PD5) | (РВ4) | (РВЗ)  | (PA15) | PA14   | PA13   | PA12   |

| в   | (PE4)                 | (PE2)     | (PB9)  | (PB7)            | (PB6) | (PD6) | (PD4) | (PD3)  | (PD1)  | PC12   | PC10   | PA11   |

| с   | (PC13)                | (PE5)     | PEO    |                  | (PB5) |       |       | PD2    | PD0    | PC11   | PF6    | PA10   |

| D   | PC14-<br>OSC32        | PE6       | vss    |                  |       |       |       |        |        | PA9    | PA8    | PC9    |

| Е   | OSC32                 | VBAT      | NC     |                  |       |       |       |        |        | PC8    | PC7    | PC6    |

| F   | (PF0-<br>OSC_)<br>IN_ | (PF9)     |        |                  |       |       |       |        |        |        | vss    | vss    |

| G   | (OSC_)                | (PF10)    |        |                  |       |       |       |        |        |        | VDDIO2 | VDD    |

| н   | PC0                   |           |        |                  |       |       |       |        |        | (PD15) | (PD14) | (PD13) |

| J   | PF2                   | (PC1)     | PC2    |                  |       |       |       |        |        | (PD12) | (PD11) | (PD10) |

| к   | (VSSA)                | (PC3)     | (PA2)  | (PA5)            | (PC4) |       |       | (PD9)  | (PD8)  | (PB15) | (PB14) | (PB13) |

| L   | (PF3)                 | PA0       | (PA3)  | PA6              | (PC5) | (PB2) | (PE8) | (PE10) | (PE12) | (PB10) | (PB11) | (PB12) |

| М   | (VDDA)                | (PA1)     | (PA4)  | (PA7)            | РВО   | (РВ1) | (PE7) | (PE9)  | (PE11) | (PE13) | (PE14) | (PE15) |

|     | UFBGA100              |           |        |                  |       |       |       |        |        |        |        |        |

|     | I/O supp              | lied from | VDDIO2 |                  |       | OFBG  | 5A100 |        |        |        |        | MS     |

Figure 3. UFBGA100 package pinout

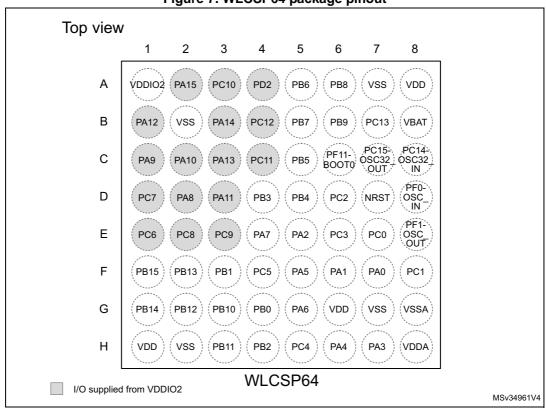

Figure 7. WLCSP64 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

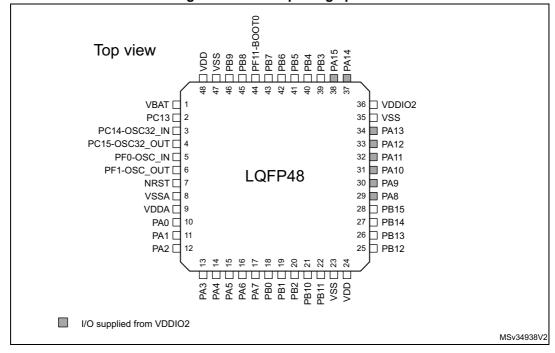

Figure 8. LQFP48 package pinout

DocID026284 Rev 4

| Table To. Alter | Table 16. Alternate functions selected through GFIOC_AFK registers for port C |                     |           |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------|---------------------|-----------|--|--|--|--|--|

| Pin name        | AF0                                                                           | AF1                 | AF2       |  |  |  |  |  |

| PC0             | EVENTOUT                                                                      | USART7_TX           | USART6_TX |  |  |  |  |  |

| PC1             | EVENTOUT                                                                      | USART7_RX           | USART6_RX |  |  |  |  |  |

| PC2             | EVENTOUT                                                                      | SPI2_MISO, I2S2_MCK | USART8_TX |  |  |  |  |  |

| PC3             | EVENTOUT                                                                      | SPI2_MOSI, I2S2_SD  | USART8_RX |  |  |  |  |  |

| PC4             | EVENTOUT                                                                      | USART3_TX           | -         |  |  |  |  |  |

| PC5             | TSC_G3_IO1                                                                    | USART3_RX           | -         |  |  |  |  |  |

| PC6             | TIM3_CH1                                                                      | USART7_TX           | -         |  |  |  |  |  |

| PC7             | TIM3_CH2                                                                      | USART7_RX           | -         |  |  |  |  |  |

| PC8             | TIM3_CH3                                                                      | USART8_TX           | -         |  |  |  |  |  |

| PC9             | TIM3_CH4                                                                      | USART8_RX           | -         |  |  |  |  |  |

| PC10            | USART4_TX                                                                     | USART3_TX           | -         |  |  |  |  |  |

| PC11            | USART4_RX                                                                     | USART3_RX           | -         |  |  |  |  |  |

| PC12            | USART4_CK                                                                     | USART3_CK           | USART5_TX |  |  |  |  |  |

| PC13            | -                                                                             | -                   | -         |  |  |  |  |  |

| PC14            | -                                                                             | -                   | -         |  |  |  |  |  |

| PC15            | -                                                                             | -                   | -         |  |  |  |  |  |

## Table 16. Alternate functions selected through GPIOC\_AFR registers for port C

### Table 17. Alternate functions selected through GPIOD\_AFR registers for port D

| Pin name | AF0        | AF1                 | AF2           |

|----------|------------|---------------------|---------------|

| PD0      | CAN_RX     | SPI2_NSS, I2S2_WS   | -             |

| PD1      | CAN_TX     | SPI2_SCK, I2S2_CK   | -             |

| PD2      | TIM3_ETR   | USART3_RTS          | USART5_RX     |

| PD3      | USART2_CTS | SPI2_MISO, I2S2_MCK | -             |

| PD4      | USART2_RTS | SPI2_MOSI, I2S2_SD  | -             |

| PD5      | USART2_TX  | -                   | -             |

| PD6      | USART2_RX  | -                   | -             |

| PD7      | USART2_CK  | -                   | -             |

| PD8      | USART3_TX  | -                   | -             |

| PD9      | USART3_RX  | -                   | -             |

| PD10     | USART3_CK  | -                   | -             |

| PD11     | USART3_CTS | -                   | -             |

| PD12     | USART3_RTS | TSC_G8_IO1          | USART8_CK_RTS |

| PD13     | USART8_TX  | TSC_G8_IO2          |               |

| PD14     | USART8_RX  | TSC_G8_IO3          | -             |

| PD15     | CRS_SYNC   | TSC_G8_IO4          | USART7_CK_RTS |

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Symbol             | Parameter                                          | Conditions                                      | Min      | Мах                                  | Unit |  |

|--------------------|----------------------------------------------------|-------------------------------------------------|----------|--------------------------------------|------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency -                     |                                                 | 0        | 48                                   | MHz  |  |

| f <sub>PCLK</sub>  | Internal APB clock frequency                       | -                                               | 0        | 48                                   | MHZ  |  |

| V <sub>DD</sub>    | Standard operating voltage                         | -                                               | 2.0      | 3.6                                  | V    |  |

| V <sub>DDIO2</sub> | I/O supply voltage                                 | Must not be supplied if $V_{DD}$ is not present | 1.65     | 3.6                                  | V    |  |

| M                  | Analog operating voltage<br>(ADC and DAC not used) | Must have a potential equal                     | $V_{DD}$ | 3.6                                  | V    |  |

| V <sub>DDA</sub>   | Analog operating voltage<br>(ADC and DAC used)     | to or higher than V <sub>DD</sub>               | 2.4      | 3.6                                  | V    |  |

| V <sub>BAT</sub>   | Backup operating voltage                           | -                                               | 1.65     | 3.6                                  | V    |  |

|                    | I/O input voltage                                  | TC and RST I/O                                  | -0.3     | V <sub>DDIOx</sub> +0.3              | V    |  |

| V <sub>IN</sub>    |                                                    | TTa I/O                                         | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> |      |  |

|                    |                                                    | FT and FTf I/O                                  | -0.3     | 5.5 <sup>(1)</sup>                   |      |  |

|                    |                                                    | UFBGA100                                        | -        | 364                                  | mW   |  |

|                    |                                                    | LQFP100                                         | -        | 476                                  |      |  |

|                    | Power dissipation at T <sub>A</sub> = 85 °C        | LQFP64                                          | -        | 455                                  |      |  |

| P <sub>D</sub>     | for suffix 6 or $T_{\Delta}$ = 105 °C for          | WLCSP64                                         | -        | 377                                  |      |  |

|                    | suffix 7 <sup>(2)</sup>                            | UFBGA64                                         | -        | 308                                  |      |  |

|                    |                                                    | LQFP48                                          | -        | 370                                  |      |  |

|                    |                                                    | UFQFPN48                                        | -        | 625                                  |      |  |

|                    | Ambient temperature for the                        | Maximum power dissipation                       | -40      | 85                                   | •    |  |

| т.                 | suffix 6 version                                   | Low power dissipation <sup>(3)</sup>            | -40      | 105                                  | °C   |  |

| ΤΑ                 | Ambient temperature for the                        | Maximum power dissipation                       | -40      | 105                                  |      |  |

|                    | suffix 7 version                                   | Low power dissipation <sup>(3)</sup>            | -40      | 125                                  | °C   |  |

| <b>T</b> /         | lunation towns return respect                      | Suffix 6 version                                | -40      | 105                                  | •    |  |

| TJ                 | Junction temperature range                         | Suffix 7 version                                | -40      | 125                                  | °C   |  |

#### Table 24. General operating conditions

1. For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

2. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.8: Thermal characteristics

3. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.8: Thermal characteristics).

## 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 25* are derived from tests performed under the ambient temperature condition summarized in *Table 24*.

## **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 35*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 21: Voltage characteristics*

|     | Peripheral               | Typical consumption at 25 °C | Unit   |

|-----|--------------------------|------------------------------|--------|

|     | BusMatrix <sup>(1)</sup> | 3.1                          |        |

|     | CRC                      | 2.0                          |        |

|     | DMA1                     | 5.5                          |        |

|     | DMA2                     | 5.1                          |        |

|     | Flash memory interface   | 15.4                         |        |

|     | GPIOA                    | 5.5                          |        |

| AHB | GPIOB                    | 5.4                          |        |

| АПБ | GPIOC                    | 3.2                          | µA/MHz |

|     | GPIOD                    | 3.1                          |        |

|     | GPIOE                    | 4.0                          |        |

|     | GPIOF                    | 2.5                          |        |

|     | SRAM                     | 0.8                          |        |

|     | TSC                      | 5.5                          |        |

|     | All AHB peripherals      | 61.0                         |        |

#### Table 35. Peripheral current consumption

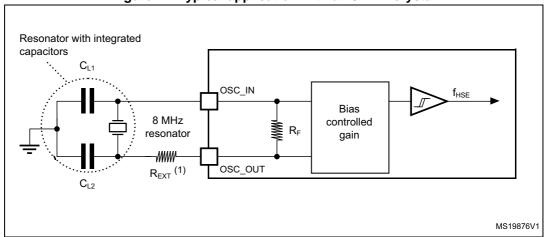

Figure 17. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

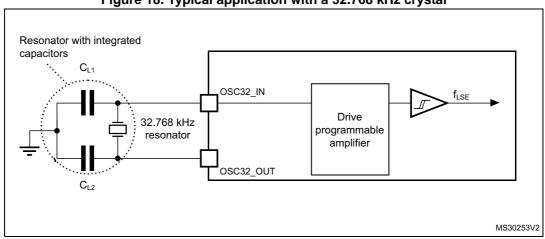

## Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                      | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|--------------------------------|----------------------------------|--------------------|-----|--------------------|------|

|                                     |                                | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current consumption        | medium-low drive capability      | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     | LSE current consumption        | medium-high drive capability     | -                  | -   | 1.3                | μA   |

|                                     |                                | high drive capability            | -                  | -   | 1.6                |      |

|                                     | Oscillator<br>transconductance | low drive capability             | 5                  | -   | -                  |      |

| ~                                   |                                | medium-low drive capability      | 8                  | -   | -                  | μΑ/V |

| 9 <sub>m</sub>                      |                                | medium-high drive capability     | 15                 | -   | -                  |      |

|                                     |                                | high drive capability            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                   | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

| Table 40. LSE oscillator | characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|--------------------------|-----------------|---------------------------------|

|--------------------------|-----------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 18. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## 6.3.8 Internal clock source characteristics

The parameters given in *Table 41* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. The provided curves are characterization results, not tested in production.

## High-speed internal 14 MHz (HSI14) RC oscillator (dedicated to ADC)

| Symbol                  | Parameter Conditions Min                                 |                                | Min                 | Тур | Max                | Unit |  |  |

|-------------------------|----------------------------------------------------------|--------------------------------|---------------------|-----|--------------------|------|--|--|

| f <sub>HSI14</sub>      | Frequency                                                | -                              | -                   | 14  | -                  | MHz  |  |  |

| TRIM                    | HSI14 user-trimming step                                 | -                              | -                   | -   | 1 <sup>(2)</sup>   | %    |  |  |

| DuCy <sub>(HSI14)</sub> | Duty cycle                                               | -                              | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |  |  |

|                         | Accuracy of the HSI14<br>oscillator (factory calibrated) | T <sub>A</sub> = -40 to 105 °C | -4.2 <sup>(3)</sup> | -   | 5.1 <sup>(3)</sup> | %    |  |  |

| ACC                     |                                                          | T <sub>A</sub> = −10 to 85 °C  | -3.2 <sup>(3)</sup> | -   | 3.1 <sup>(3)</sup> | %    |  |  |

| ACC <sub>HSI14</sub>    |                                                          | T <sub>A</sub> = 0 to 70 °C    | -2.5 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |  |  |

|                         |                                                          | T <sub>A</sub> = 25 °C         | -1                  | -   | 1                  | %    |  |  |

| t <sub>su(HSI14)</sub>  | HSI14 oscillator startup time                            | -                              | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |  |  |

| I <sub>DDA(HSI14)</sub> | HSI14 oscillator power<br>consumption                    | -                              | -                   | 100 | 150 <sup>(2)</sup> | μA   |  |  |

## Table 42. HSI14 oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

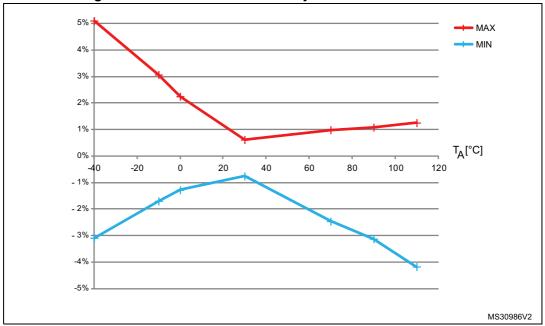

#### Figure 20. HSI14 oscillator accuracy characterization results

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |  |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |  |  |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |  |  |

Table 47. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

| Table 48. EMS c | haracteristics |

|-----------------|----------------|

|-----------------|----------------|

| Symb             | ol Parameter                                                                                                                      | Conditions                                                                                                        | Level/<br>Class |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FES</sub> | Voltage limits to be applied on any I/O pi<br>to induce a functional disturbance                                                  | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2 | 2B              |

| V <sub>EFT</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4  | 4B              |

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

# 6.3.17 DAC electrical specifications

| Symbol         Parameter         Min         Typ         Max         Unit         Comments |                                                                                                                                                               |     |     |                         |      |                                                                                                                                |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| Cymbol                                                                                     |                                                                                                                                                               |     | .96 | max                     | onit |                                                                                                                                |

| V <sub>DDA</sub>                                                                           | Analog supply voltage for<br>DAC ON                                                                                                                           | 2.4 | -   | 3.6                     | V    | -                                                                                                                              |

| R <sub>LOAD</sub> <sup>(1)</sup>                                                           | Resistive load with buffer                                                                                                                                    | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                             |

| INLOAD                                                                                     | ON                                                                                                                                                            | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                             |

| R <sub>O</sub> <sup>(1)</sup>                                                              | Impedance output with<br>buffer OFF                                                                                                                           | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and V <sub>SS</sub> to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup>                                                           | Capacitive load                                                                                                                                               | -   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                |

| DAC_OUT<br>min <sup>(1)</sup>                                                              | Lower DAC_OUT voltage with buffer ON                                                                                                                          | 0.2 | -   | -                       | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at           |

| DAC_OUT<br>max <sup>(1)</sup>                                                              | Higher DAC_OUT voltage with buffer ON                                                                                                                         | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{DDA} = 3.6 V and (0x155) and (0xEAB) at V_{DDA} = 2.4 V$                                                                   |

| DAC_OUT<br>min <sup>(1)</sup>                                                              | Lower DAC_OUT voltage with buffer OFF                                                                                                                         | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                                    |

| DAC_OUT<br>max <sup>(1)</sup>                                                              | Higher DAC_OUT voltage<br>with buffer OFF                                                                                                                     | -   | -   | V <sub>DDA</sub> – 1LSB | V    | excursion of the DAC.                                                                                                          |

| I <sub>DDA</sub> <sup>(1)</sup>                                                            | DAC DC current<br>consumption in quiescent<br>mode <sup>(2)</sup>                                                                                             | -   | -   | 600                     | μA   | With no load, middle code<br>(0x800) on the input                                                                              |

| 'DDA'                                                                                      |                                                                                                                                                               | -   | -   | 700                     | μA   | With no load, worst code<br>(0xF1C) on the input                                                                               |

| DNL <sup>(3)</sup>                                                                         | Differential non linearity<br>Difference between two<br>consecutive code-1LSB)                                                                                | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                                      |

|                                                                                            |                                                                                                                                                               | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |

|                                                                                            | Integral non linearity<br>(difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                                      |

| INL <sup>(3)</sup>                                                                         |                                                                                                                                                               | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |

|                                                                                            | Offset error                                                                                                                                                  | -   | -   | ±10                     | mV   | -                                                                                                                              |

| Offset <sup>(3)</sup>                                                                      | (difference between<br>measured value at Code                                                                                                                 | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at $V_{DDA}$ = 3.6 V                                                                               |

|                                                                                            | (0x800) and the ideal value = $V_{DDA}/2$ )                                                                                                                   | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at $V_{DDA}$ = 3.6 V                                                                               |

### Table 60. DAC characteristics

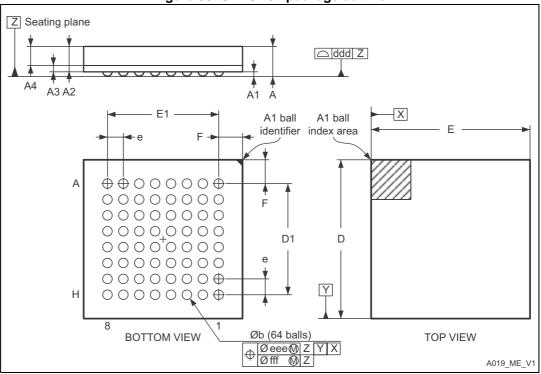

# 7.3 UFBGA64 package information

UFBGA64 is a 64-ball, 5 x 5 mm, 0.5 mm pitch ultra-fine-profile ball grid array package.

1. Drawing is not to scale.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А      | 0.460 | 0.530       | 0.600 | 0.0181 | 0.0209                | 0.0236 |

| A1     | 0.050 | 0.080       | 0.110 | 0.0020 | 0.0031                | 0.0043 |

| A2     | 0.400 | 0.450       | 0.500 | 0.0157 | 0.0177                | 0.0197 |

| A3     | 0.080 | 0.130       | 0.180 | 0.0031 | 0.0051                | 0.0071 |

| A4     | 0.270 | 0.320       | 0.370 | 0.0106 | 0.0126                | 0.0146 |

| b      | 0.170 | 0.280       | 0.330 | 0.0067 | 0.0110                | 0.0130 |

| D      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| D1     | 3.450 | 3.500       | 3.550 | 0.1358 | 0.1378                | 0.1398 |

| E      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| E1     | 3.450 | 3.500       | 3.550 | 0.1358 | 0.1378                | 0.1398 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| F      | 0.700 | 0.750       | 0.800 | 0.0276 | 0.0295                | 0.0315 |

#### Table 73. UFBGA64 package mechanical data

| Table For Di Device publicago mochamoar data (continuou) |             |       |       |                       |        |        |  |

|----------------------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                                                   | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|                                                          | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| А                                                        | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| ddd                                                      | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

| eee                                                      | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff                                                      | -           | -     | 0.050 | -                     | -      | 0.0020 |  |

#### Table 73. UFBGA64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

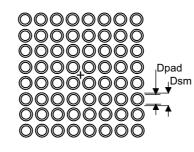

#### Figure 40. Recommended footprint for UFBGA64 package

A019\_FP\_V2

#### Table 74. UFBGA64 recommended PCB design rules

| Dimension         | Recommended values                                               |  |  |  |  |

|-------------------|------------------------------------------------------------------|--|--|--|--|

| Pitch             | 0.5                                                              |  |  |  |  |

| Dpad              | 0.280 mm                                                         |  |  |  |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |  |  |  |

| Stencil opening   | 0.280 mm                                                         |  |  |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |  |  |  |

| Pad trace width   | 0.100 mm                                                         |  |  |  |  |

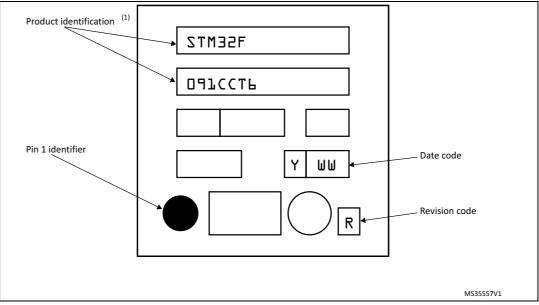

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 50. LQFP48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

|        | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |  |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |  |

| D      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| E      | 6.900 | 7.000       | 7.100 | 0.2717 | 0.2756                | 0.2795 |  |

| D2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| E2     | 5.500 | 5.600       | 5.700 | 0.2165 | 0.2205                | 0.2244 |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| Т      | -     | 0.152       | -     | -      | 0.0060                | -      |  |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

#### Table 79. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 52. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.