Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | ·                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-UFBGA                                                              |

| Supplier Device Package    | 64-UFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091rch7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 3.14.6   | SysTick timer                                                                      | . 23 |  |  |  |  |  |  |

|---|-------|----------|------------------------------------------------------------------------------------|------|--|--|--|--|--|--|

|   | 3.15  | Real-ti  | me clock (RTC) and backup registers                                                | 23   |  |  |  |  |  |  |

|   | 3.16  | Inter-in | ntegrated circuit interface (I <sup>2</sup> C) 24                                  |      |  |  |  |  |  |  |

|   | 3.17  | Univer   | rsal synchronous/asynchronous receiver/transmitter (USART) 25                      |      |  |  |  |  |  |  |

|   | 3.18  | Serial p | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) . | 26   |  |  |  |  |  |  |

|   | 3.19  | -        | efinition multimedia interface (HDMI) - consumer                                   |      |  |  |  |  |  |  |

|   |       | -        | nics control (CEC)                                                                 | 27   |  |  |  |  |  |  |

|   | 3.20  | Contro   | ller area network (CAN)                                                            | 27   |  |  |  |  |  |  |

|   | 3.21  | Clock r  | ecovery system (CRS)                                                               | 27   |  |  |  |  |  |  |

|   | 3.22  | Serial   | wire debug port (SW-DP)                                                            | 27   |  |  |  |  |  |  |

| 4 | Pino  | uts and  | pin descriptions                                                                   | 28   |  |  |  |  |  |  |

| 5 | Mem   | ory ma   | oping                                                                              | 45   |  |  |  |  |  |  |

| 6 | Elect | rical ch | aracteristics                                                                      | 49   |  |  |  |  |  |  |

|   | 6.1   | Param    | eter conditions                                                                    | 49   |  |  |  |  |  |  |

|   |       | 6.1.1    | Minimum and maximum values                                                         | . 49 |  |  |  |  |  |  |

|   |       | 6.1.2    | Typical values                                                                     | . 49 |  |  |  |  |  |  |

|   |       | 6.1.3    | Typical curves                                                                     | . 49 |  |  |  |  |  |  |

|   |       | 6.1.4    | Loading capacitor                                                                  | . 49 |  |  |  |  |  |  |

|   |       | 6.1.5    | Pin input voltage                                                                  | . 49 |  |  |  |  |  |  |

|   |       | 6.1.6    | Power supply scheme                                                                | . 50 |  |  |  |  |  |  |

|   |       | 6.1.7    | Current consumption measurement                                                    | . 51 |  |  |  |  |  |  |

|   | 6.2   | Absolu   | te maximum ratings                                                                 | 52   |  |  |  |  |  |  |

|   | 6.3   | Operat   | ing conditions                                                                     | 54   |  |  |  |  |  |  |

|   |       | 6.3.1    | General operating conditions                                                       | . 54 |  |  |  |  |  |  |

|   |       | 6.3.2    | Operating conditions at power-up / power-down                                      | . 54 |  |  |  |  |  |  |

|   |       | 6.3.3    | Embedded reset and power control block characteristics                             | . 55 |  |  |  |  |  |  |

|   |       | 6.3.4    | Embedded reference voltage                                                         | . 56 |  |  |  |  |  |  |

|   |       | 6.3.5    | Supply current characteristics                                                     | . 56 |  |  |  |  |  |  |

|   |       | 6.3.6    | Wakeup time from low-power mode                                                    | . 67 |  |  |  |  |  |  |

|   |       | 6.3.7    | External clock source characteristics                                              | . 67 |  |  |  |  |  |  |

|   |       | 6.3.8    | Internal clock source characteristics                                              | . 71 |  |  |  |  |  |  |

|   |       | 6.3.9    | PLL characteristics                                                                | . 75 |  |  |  |  |  |  |

|   |       | 6.3.10   | Memory characteristics                                                             | . 75 |  |  |  |  |  |  |

|   |      | 6.3.11    | EMC characteristics                           |

|---|------|-----------|-----------------------------------------------|

|   |      | 6.3.12    | Electrical sensitivity characteristics77      |

|   |      | 6.3.13    | I/O current injection characteristics78       |

|   |      | 6.3.14    | I/O port characteristics                      |

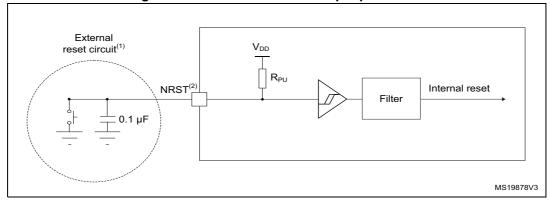

|   |      | 6.3.15    | NRST pin characteristics                      |

|   |      | 6.3.16    | 12-bit ADC characteristics                    |

|   |      | 6.3.17    | DAC electrical specifications                 |

|   |      | 6.3.18    | Comparator characteristics91                  |

|   |      | 6.3.19    | Temperature sensor characteristics    93      |

|   |      | 6.3.20    | V <sub>BAT</sub> monitoring characteristics93 |

|   |      | 6.3.21    | Timer characteristics                         |

|   |      | 6.3.22    | Communication interfaces                      |

| 7 | Pack | age info  | ormation                                      |

|   | 7.1  | UFBGA     | A100 package information 100                  |

|   | 7.2  | LQFP1     | 00 package information 103                    |

|   | 7.3  | UFBG/     | A64 package information                       |

|   | 7.4  | WLCSI     | P64 package information 109                   |

|   | 7.5  | LQFP6     | 4 package information                         |

|   | 7.6  | LQFP4     | 8 package information                         |

|   | 7.7  | UFQFF     | PN48 package information118                   |

|   | 7.8  | Therma    | al characteristics                            |

|   |      | 7.8.1     | Reference document                            |

|   |      | 7.8.2     | Selecting the product temperature range       |

| 8 | Orde | ering inf | ormation                                      |

| 9 | Revi | sion his  | tory                                          |

# 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

# 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F091xB/xC devices (see *Table 7* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

# TIM2, TIM3

STM32F091xB/xC devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

# TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

# 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

# 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

# 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop and Standby mode capability

- Periodic wakeup unit with programmable resolution and period.

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive on most of the associated I/Os.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 8. Comparison of I <sup>2</sup> C | analog and digital filters |

|-----------------------------------------|----------------------------|

|                                         |                            |

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts

| USART modes/features <sup>(1)</sup>         | USART1<br>USART2<br>USART3 | USART4 | USART5<br>USART6<br>USART7<br>USART8 |  |  |  |  |  |

|---------------------------------------------|----------------------------|--------|--------------------------------------|--|--|--|--|--|

| Single-wire half-duplex communication       | Х                          | Х      | Х                                    |  |  |  |  |  |

| IrDA SIR ENDEC block                        | Х                          | -      | -                                    |  |  |  |  |  |

| LIN mode                                    | Х                          | -      | -                                    |  |  |  |  |  |

| Dual clock domain and wakeup from Stop mode | Х                          | -      | -                                    |  |  |  |  |  |

| Receiver timeout interrupt                  | Х                          | -      | -                                    |  |  |  |  |  |

| Modbus communication                        | Х                          | -      | -                                    |  |  |  |  |  |

| Auto baud rate detection                    | Х                          | -      | -                                    |  |  |  |  |  |

| Driver Enable                               | Х                          | Х      | Х                                    |  |  |  |  |  |

#### Table 10. STM32F091xB/xC USART implementation (continued)

1. X = supported.

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI1 and SPI2 respectively) supporting four different audio standards can operate as master or slave at half-duplex communication mode. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, they can output a clock for an external audio component at 256 times the sampling frequency.

| SPI features <sup>(1)</sup> | SPI1 and SPI2 |

|-----------------------------|---------------|

| Hardware CRC calculation    | Х             |

| Rx/Tx FIFO                  | Х             |

| NSS pulse mode              | Х             |

| I <sup>2</sup> S mode       | Х             |

| TI mode                     | Х             |

Table 11. STM32F091xB/xC SPI/I<sup>2</sup>S implementation

1. X = supported.

# 4 Pinouts and pin descriptions

| Тор | Top view              |        |       |                  |       |       |       |        |        |        |        |        |

|-----|-----------------------|--------|-------|------------------|-------|-------|-------|--------|--------|--------|--------|--------|

| F   | 1                     | 2      | 3     | 4                | 5     | 6     | 7     | 8      | 9      | 10     | 11     | 12     |

|     |                       |        |       |                  |       |       |       |        |        |        |        |        |

| A   | (PE3)                 | (PE1)  | (PB8) | (PF11-)<br>BOOT0 | (PD7) | (PD5) | (РВ4) | (РВЗ)  | (PA15) | PA14   | PA13   | PA12   |

| в   | (PE4)                 | (PE2)  | (PB9) | (PB7)            | (PB6) | (PD6) | (PD4) | (PD3)  | (PD1)  | PC12   | PC10   | PA11   |

| с   | (PC13)                | (PE5)  | PEO   |                  | (PB5) |       |       | PD2    | PD0    | PC11   | PF6    | PA10   |

| D   | PC14-<br>OSC32        | PE6    | vss   |                  |       |       |       |        |        | PA9    | PA8    | PC9    |

| Е   | OSC32                 | VBAT   | NC    |                  |       |       |       |        |        | PC8    | PC7    | PC6    |

| F   | (PF0-<br>OSC_)<br>IN_ | PF9    |       |                  |       |       |       |        |        |        | vss    | vss    |

| G   | (OSC_)                | (PF10) |       |                  |       |       |       |        |        |        | VDDIO2 | VDD    |

| н   | PC0                   |        |       |                  |       |       |       |        |        | (PD15) | (PD14) | (PD13) |

| J   | PF2                   | (PC1)  | PC2   |                  |       |       |       |        |        | (PD12) | (PD11) | (PD10) |

| к   | (VSSA)                | (PC3)  | (PA2) | (PA5)            | (PC4) |       |       | (PD9)  | (PD8)  | (PB15) | (PB14) | (PB13) |

| L   | (PF3)                 | PA0    | (PA3) | PA6              | (PC5) | (PB2) | (PE8) | (PE10) | (PE12) | (PB10) | (PB11) | (PB12) |

| М   | (VDDA)                | (PA1)  | (PA4) | (PA7)            | РВО   | (РВ1) | (PE7) | (PE9)  | (PE11) | (PE13) | (PE14) | (PE15) |

|     |                       |        |       |                  |       |       |       |        |        |        |        |        |

|     | UFBGA100              |        |       |                  |       |       |       |        |        |        |        |        |

Figure 3. UFBGA100 package pinout

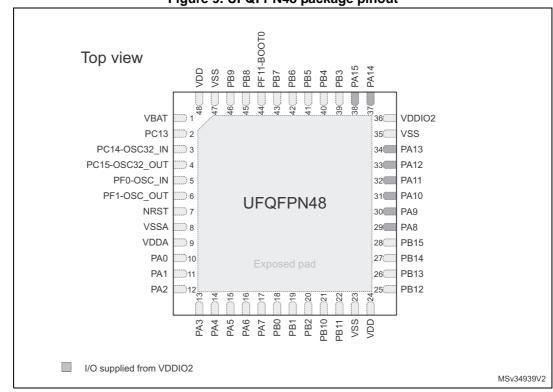

Figure 9. UFQFPN48 package pinout

# Table 12. Legend/abbreviations used in the pinout table

| Na                                                                                    | me                                                                            | Abbreviation                                                                                                                         | Definition         |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| Pin r                                                                                 | name                                                                          | Unless otherwise specified in brackets below the pin name, the pin function during ar after reset is the same as the actual pin name |                    |  |  |  |

|                                                                                       |                                                                               | S                                                                                                                                    | Supply pin         |  |  |  |

| Pin                                                                                   | type                                                                          | I/O                                                                                                                                  | Input / output pin |  |  |  |

|                                                                                       |                                                                               | FT                                                                                                                                   | 5 V-tolerant I/O   |  |  |  |

|                                                                                       |                                                                               | FTf 5 V-tolerant I/O, FM+ capable                                                                                                    |                    |  |  |  |

| I/O str                                                                               | ucture                                                                        | TTa 3.3 V-tolerant I/O directly connected to ADC                                                                                     |                    |  |  |  |

|                                                                                       |                                                                               | TC                                                                                                                                   | Standard 3.3 V I/O |  |  |  |

|                                                                                       |                                                                               | RST Bidirectional reset pin with embedded weak pull-up resistor                                                                      |                    |  |  |  |

| Notes Unless otherwise specified by a note, all I/Os are set as floatin reset.        |                                                                               | specified by a note, all I/Os are set as floating inputs during and after                                                            |                    |  |  |  |

| Pin                                                                                   | Alternate<br>functions         Functions selected through GPIOx_AFR registers |                                                                                                                                      |                    |  |  |  |

| functions Additional functions directly selected/enabled through peripheral registers |                                                                               |                                                                                                                                      |                    |  |  |  |

| S        |

|----------|

| -        |

| $\leq$   |

| ω        |

| <u>N</u> |

|          |

| ž        |

| ž        |

| ×        |

| ω        |

| ŝ        |

| Ч        |

| z        |

| 2        |

| Ň        |

| Ţ        |

| Ö        |

| 2        |

| ×        |

| Ô        |

|          |

|          | Table 1             | 14. Alternate fu | nctions selected | l through GPIC | DA_AFR registe | ers for port A |          |          |

|----------|---------------------|------------------|------------------|----------------|----------------|----------------|----------|----------|

| Pin name | AF0                 | AF1              | AF2              | AF3            | AF4            | AF5            | AF6      | AF7      |

| PA0      | -                   | USART2_CTS       | TIM2_CH1_ETR     | TSC_G1_IO1     | USART4_TX      | -              | -        | COMP1_OU |

| PA1      | EVENTOUT            | USART2_RTS       | TIM2_CH2         | TSC_G1_IO2     | USART4_RX      | TIM15_CH1N     | -        | -        |

| PA2      | TIM15_CH1           | USART2_TX        | TIM2_CH3         | TSC_G1_IO3     | -              | -              | -        | COMP2_OU |

| PA3      | TIM15_CH2           | USART2_RX        | TIM2_CH4         | TSC_G1_IO4     | -              | -              | -        | -        |

| PA4      | SPI1_NSS, I2S1_WS   | USART2_CK        | -                | TSC_G2_IO1     | TIM14_CH1      | USART6_TX      | -        | -        |

| PA5      | SPI1_SCK, I2S1_CK   | CEC              | TIM2_CH1_ETR     | TSC_G2_IO2     | -              | USART6_RX      | -        | -        |

| PA6      | SPI1_MISO, I2S1_MCK | TIM3_CH1         | TIM1_BKIN        | TSC_G2_IO3     | USART3_CTS     | TIM16_CH1      | EVENTOUT | COMP1_OL |

| PA7      | SPI1_MOSI, I2S1_SD  | TIM3_CH2         | TIM1_CH1N        | TSC_G2_IO4     | TIM14_CH1      | TIM17_CH1      | EVENTOUT | COMP2_OL |

| PA8      | MCO                 | USART1_CK        | TIM1_CH1         | EVENTOUT       | CRS_SYNC       | -              | -        | -        |

| PA9      | TIM15_BKIN          | USART1_TX        | TIM1_CH2         | TSC_G4_IO1     | I2C1_SCL       | MCO            | -        | -        |

| PA10     | TIM17_BKIN          | USART1_RX        | TIM1_CH3         | TSC_G4_IO2     | I2C1_SDA       | -              | -        | -        |

| PA11     | EVENTOUT            | USART1_CTS       | TIM1_CH4         | TSC_G4_IO3     | CAN_RX         | I2C2_SCL       | -        | COMP1_OL |

| PA12     | EVENTOUT            | USART1_RTS       | TIM1_ETR         | TSC_G4_IO4     | CAN_TX         | I2C2_SDA       | -        | COMP2_OL |

| PA13     | SWDIO               | IR_OUT           | -                | -              | -              | -              | -        | -        |

| PA14     | SWCLK               | USART2_TX        | -                | -              | -              | -              | -        | -        |

| PA15     | SPI1_NSS, I2S1_WS   | USART2_RX        | TIM2_CH1_ETR     | EVENTOUT       | USART4_RTS     | -              | -        | -        |

41/128

| Bus  | Boundary address          | Size    | Peripheral             |

|------|---------------------------|---------|------------------------|

|      | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved               |

|      | 0x4800 1400 - 0x4800 17FF | 1 KB    | GPIOF                  |

|      | 0x4800 1000 - 0x4800 13FF | 1 KB    | GPIOE                  |

| AHB2 | 0x4800 0C00 - 0x4800 0FFF | 1 KB    | GPIOD                  |

| AND2 | 0x4800 0800 - 0x4800 0BFF | 1 KB    | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF | 1 KB    | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF | 1 KB    | GPIOA                  |

|      | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF | 1 KB    | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF | 1 KB    | Flash memory interface |

|      | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                    |

|      | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved               |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA                    |

|      | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved               |

| Table 20. STM32F091xB/xC | peripheral reg | jister boundary | addresses |

|--------------------------|----------------|-----------------|-----------|

| Bus | Boundary address          | Size  | Peripheral |

|-----|---------------------------|-------|------------|

|     | 0x4000 7C00 - 0x4000 7FFF | 1 KB  | Reserved   |

|     | 0x4000 7800 - 0x4000 7BFF | 1 KB  | CEC        |

|     | 0x4000 7400 - 0x4000 77FF | 1 KB  | DAC        |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB  | PWR        |

|     | 0x4000 6C00 - 0x4000 6FFF | 1 KB  | CRS        |

|     | 0x4000 6800 - 0x4000 6BFF | 1 KB  | Reserved   |

|     | 0x4000 6400 - 0x4000 67FF | 1 KB  | BxCAN      |

|     | 0x4000 6100 - 0x4000 63FF | 768 B | Reserved   |

|     | 0x4000 6000 - 0x4000 60FF | 256 B | CAN RAM    |

|     | 0x4000 5C00 - 0x4000 5FFF | 1 KB  | Reserved   |

|     | 0x4000 5800 - 0x4000 5BFF | 1 KB  | I2C2       |

|     | 0x4000 5400 - 0x4000 57FF | 1 KB  | I2C1       |

|     | 0x4000 5000 - 0x4000 53FF | 1 KB  | USART5     |

| _   | 0x4000 4C00 - 0x4000 4FFF | 1 KB  | USART4     |

|     | 0x4000 4800 - 0x4000 4BFF | 1 KB  | USART3     |

|     | 0x4000 4400 - 0x4000 47FF | 1 KB  | USART2     |

|     | 0x4000 3C00 - 0x4000 43FF | 2 KB  | Reserved   |

| APB | 0x4000 3800 - 0x4000 3BFF | 1 KB  | SPI2       |

|     | 0x4000 3400 - 0x4000 37FF | 1 KB  | Reserved   |

|     | 0x4000 3000 - 0x4000 33FF | 1 KB  | IWDG       |

|     | 0x4000 2C00 - 0x4000 2FFF | 1 KB  | WWDG       |

|     | 0x4000 2800 - 0x4000 2BFF | 1 KB  | RTC        |

|     | 0x4000 2400 - 0x4000 27FF | 1 KB  | Reserved   |

|     | 0x4000 2000 - 0x4000 23FF | 1 KB  | TIM14      |

|     | 0x4000 1800 - 0x4000 1FFF | 2 KB  | Reserved   |

|     | 0x4000 1400 - 0x4000 17FF | 1 KB  | TIM7       |

|     | 0x4000 1000 - 0x4000 13FF | 1 KB  | TIM6       |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB  | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB  | TIM3       |

|     | 0x4000 0000 - 0x4000 03FF | 1 KB  | TIM2       |

# Table 20. STM32F091xB/xC peripheral register boundary addresses (continued)

| Sym-             | Para-                      |                                |                                                              |                                                              |                         |       | V <sub>DD</sub> = \ |       | •     |                           | Max <sup>(1)</sup>        |                            |      |     |  |

|------------------|----------------------------|--------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-------|---------------------|-------|-------|---------------------------|---------------------------|----------------------------|------|-----|--|

| bol              | -                          |                                | Conditions                                                   |                                                              | 2.4 V                   | 2.7 V | 3.0 V               | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |     |  |

|                  | Supply current in          | mod                            | julator in run<br>de, all<br>illators OFF                    | 14.6                                                         | 14.8                    | 14.9  | 15.1                | 15.4  | 15.8  | 18                        | 51                        | 97                         |      |     |  |

| I <sub>DD</sub>  | Stop<br>mode               | pow                            | ulator in low-<br>ver mode, all<br>illators OFF              | 3.3                                                          | 3.4                     | 3.6   | 3.8                 | 4.1   | 4.4   | 11                        | 53                        | 106                        |      |     |  |

|                  | Supply current in          | LSI<br>ON                      | ON and IWDG                                                  | 0.9                                                          | 1.0                     | 1.1   | 1.2                 | 1.3   | 1.4   | 2.3                       | 2.7                       | 3.6                        |      |     |  |

|                  | Standby<br>mode            | LSI<br>OFF                     | OFF and IWDG<br>=                                            | 0.6                                                          | 0.7                     | 0.8   | 0.9                 | 1.0   | 1.1   | 1.9                       | 2.3                       | 3.0                        |      |     |  |

|                  | Supply current in          | NO                             | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.9                                                          | 2.0                     | 2.2   | 2.3                 | 2.4   | 2.6   | 3.8                       | 4.2                       | 4.6                        |      |     |  |

|                  | Stop<br>mode               | Stop                           | V <sub>DDA</sub> monitoring O                                | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.9                     | 2.0   | 2.2                 | 2.3   | 2.4   | 2.6                       | 3.8                       | 4.2                        | 4.6  | μA  |  |

|                  | Supply current in          | V <sub>DC</sub>                | LSI ON and<br>IWDG ON                                        | 2.3                                                          | 2.5                     | 2.7   | 2.8                 | 3.0   | 3.3   | 3.8                       | 4.2                       | 4.8                        |      |     |  |

| I <sub>DDA</sub> | Standby<br>mode            | -                              | mode                                                         |                                                              | LSI OFF and<br>IWDG OFF | 1.8   | 1.9                 | 2.0   | 2.2   | 2.3                       | 2.5                       | 3.6                        | 3.9  | 4.2 |  |

| JDA              | Supply                     | OFF                            | Regulator in<br>run mode, all<br>oscillators<br>OFF          | 1.2                                                          | 1.2                     | 1.3   | 1.3                 | 1.4   | 1.4   | -                         | -                         | -                          |      |     |  |

|                  | current in<br>Stop<br>mode | V <sub>DDA</sub> monitoring Of | Regulator in<br>low-power<br>mode, all<br>oscillators<br>OFF | 1.2                                                          | 1.2                     | 1.3   | 1.3                 | 1.4   | 1.4   | -                         | -                         | -                          |      |     |  |

|                  | Supply current in          | V <sub>DD</sub>                | LSI ON and<br>IWDG ON                                        | 1.6                                                          | 1.7                     | 1.8   | 1.9                 | 2.0   | 2.1   | -                         | -                         | -                          |      |     |  |

|                  | Standby<br>mode            |                                | LSI OFF and<br>IWDG OFF                                      | 1.1                                                          | 1.1                     | 1.1   | 1.2                 | 1.3   | 1.3   | -                         | -                         | -                          |      |     |  |

Table 31. Typical and maximum consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production unless otherwise specified.

|     | Peripheral                | Typical consumption (continued | /<br>Unit |

|-----|---------------------------|--------------------------------|-----------|

|     | APB-Bridge <sup>(2)</sup> | 3.6                            |           |

|     | ADC <sup>(3)</sup>        | 4.3                            |           |

|     | CAN                       | 12.4                           |           |

|     | CEC                       | 0.4                            |           |

|     | CRS                       | 0.0                            |           |

|     | DAC <sup>(3)</sup>        | 4.2                            |           |

|     | DBG (MCU Debug Support)   | 0.2                            |           |

|     | 12C1                      | 2.9                            |           |

|     | 12C2                      | 2.4                            |           |

|     | PWR                       | 0.6                            |           |

|     | SPI1                      | 8.8                            |           |

|     | SPI2                      | 7.8                            |           |

|     | SYSCFG and COMP           | 1.9                            |           |

|     | TIM1                      | 15.2                           |           |

|     | TIM14                     | 2.6                            |           |

|     | TIM15                     | 8.7                            |           |

| APB | TIM16                     | 5.8                            | µA/MHz    |

|     | TIM17                     | 7.0                            |           |

|     | TIM2                      | 16.2                           |           |

|     | TIM3                      | 11.9                           |           |

|     | TIM6                      | 11.8                           |           |

|     | TIM7                      | 2.5                            |           |

|     | USART1                    | 17.6                           |           |

|     | USART2                    | 16.3                           |           |

|     | USART3                    | 16.2                           |           |

|     | USART4                    | 4.7                            |           |

|     | USART5                    | 4.4                            |           |

|     | USART6                    | 5.5                            |           |

|     | USART7                    | 5.2                            |           |

|     | USART8                    | 5.1                            |           |

|     | 00/11/10                  | 1                              |           |

|     | WWDG                      | 1.1                            |           |

Table 35. Peripheral current consumption (continued)

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

2. The APB Bridge is automatically active when at least one peripheral is ON on the Bus.

The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, comparators, is not included. Refer to the tables of characteristics in the subsequent sections.

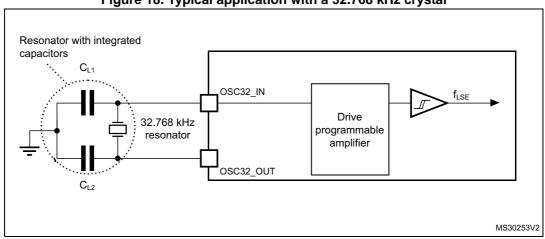

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 18. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

# 6.3.8 Internal clock source characteristics

The parameters given in *Table 41* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. The provided curves are characterization results, not tested in production.

# High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                        | Conditions                    | Min                 | Тур | Мах                | Unit |

|-----------------------|----------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                        | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step           | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                       | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                       |                                  | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       | Accuracy of the HSI oscillator   | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |

|                       |                                  | $T_A = 0$ to $85^{\circ}C$    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

| ACC <sub>HSI</sub>    |                                  | $T_A = 0$ to $70^{\circ}C$    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                  | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time      | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power consumption | -                             | -                   | 80  | 100 <sup>(2)</sup> | μA   |

# Table 41. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V, T<sub>A</sub> = -40 to 105°C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

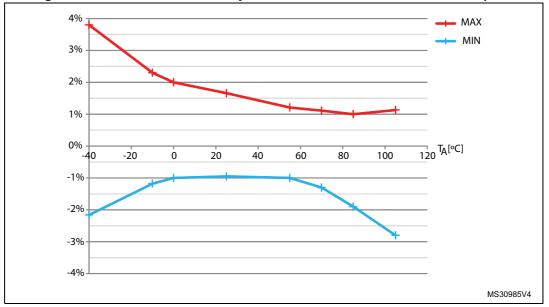

#### Figure 19. HSI oscillator accuracy characterization results for soldered parts

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |  |  |

|------------------|----------------|----------------------------------------------------|--------------------|--------|--|--|

| N <sub>END</sub> | Endurance      | T <sub>A</sub> = -40 to +105 °C                    | 10                 | kcycle |  |  |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |  |  |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |  |  |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |  |  |

Table 47. Flash memory endurance and data retention

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

# 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

# Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

| Table 48. EMS c | haracteristics |

|-----------------|----------------|

|-----------------|----------------|

| Symb             | ol Parameter                                                                                                                      | Conditions                                                                                                        | Level/<br>Class |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FES</sub> | Voltage limits to be applied on any I/O pi<br>to induce a functional disturbance                                                  | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-2 | 2B              |

| V <sub>EFT</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 48 MHz,<br>conforming to IEC 61000-4-4  | 4B              |

# Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol                | Ratings                                               | Conditions                                                  | Packages            | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |  |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------|---------------------|-------|---------------------------------|------|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A$ = +25 °C, conforming<br>to JESD22-A114                | All                 | 2     | 2000                            | V    |  |  |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to ANSI/ESD STM5.3.1 | WLCSP64,<br>LQFP100 | C3    | 250                             | v    |  |  |

|                       |                                                       | 10 ANGI/EGD STMD.3.1                                        | All others          | C4    | 500                             |      |  |  |

#### Table 50. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

# Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 51. Electrical sensitivities

| Symb | ol | Parameter             | Conditions                                    | Class      |

|------|----|-----------------------|-----------------------------------------------|------------|

| LU   |    | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

# 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

# Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in *Table 52*.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

# **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 21: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 21: Voltage characteristics*).

# **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                              | Min                     | Max | Unit |  |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------|-----|------|--|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                | -                       | 0.4 |      |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                 | -                       | 0.4 |      |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | 2.4                     | -   | V    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                               | -                       | 1.3 | v    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                              | V <sub>DDIOx</sub> -1.3 | -   | v    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 6 mA                                | -                       | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2 V                                | V <sub>DDIOx</sub> -0.4 | -   | v    |  |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                    | II I = 4 mA                                             | -                       | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 4 mA                                | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V | -                       | 0.4 | V    |  |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                               | -                       | 0.4 | V    |  |

# Table 54. Output voltage characteristics<sup>(1)</sup>

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 21: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

4. Data based on characterization results. Not tested in production.

| Symbol                 | Parameter                                       | Conditions                        | Min                | Тур | Мах                | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                  | 200 | -                  | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |

| V                      | NRST input not filtered pulse                   | $2.7 < V_{DD} < 3.6$              | 300 <sup>(3)</sup> | -   | _                  | ns   |

| V <sub>NF(NRST)</sub>  |                                                 | $2.0 < V_{DD} < 3.6$              | 500 <sup>(3)</sup> | -   | -                  | 115  |

Table 56. NRST pin characteristics (continued)

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

3. Data based on design simulation only. Not tested in production.

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

# 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Table 57. ADC c | haracteristics |

|-----------------|----------------|

|-----------------|----------------|

| Symbol                        | Parameter                                     | Conditions               | Min   | Тур | Max | Unit |  |

|-------------------------------|-----------------------------------------------|--------------------------|-------|-----|-----|------|--|

| V <sub>DDA</sub>              | Analog supply voltage for<br>ADC ON           | -                        | 2.4   | -   | 3.6 | V    |  |

| I <sub>DDA (ADC)</sub>        | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V | -     | 0.9 | -   | mA   |  |

| f <sub>ADC</sub>              | ADC clock frequency                           | -                        | 0.6   | -   | 14  | MHz  |  |

| f <sub>S</sub> <sup>(2)</sup> | Sampling rate                                 | 12-bit resolution        | 0.043 | -   | 1   | MHz  |  |

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 81 | Ordering | information | scheme |

|----------|----------|-------------|--------|

|----------|----------|-------------|--------|

| Example:                                           | STM32        | F | 091 | R | C | T | 6 x |

|----------------------------------------------------|--------------|---|-----|---|---|---|-----|

| Device family                                      |              |   |     |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller           |              |   |     |   |   |   |     |

|                                                    |              |   |     |   |   |   |     |

| Product type                                       |              |   |     |   |   |   |     |

| F = General-purpose                                |              |   |     |   |   |   |     |

| Sub-family                                         |              |   |     |   |   |   |     |

| 091= STM32F091xx                                   |              |   |     |   |   |   |     |

| Dir court                                          |              |   |     |   |   |   |     |

| Pin count<br>C = 48 pins                           |              |   |     |   |   |   |     |

| R = 64  pins                                       |              |   |     |   |   |   |     |

| V = 100  pins                                      |              |   |     |   |   |   |     |

|                                                    |              |   |     |   |   |   |     |

| User code memory size                              |              |   |     |   |   |   |     |

| B = 128 Kbyte                                      |              |   |     |   |   |   |     |

| C = 256 Kbyte                                      |              |   |     |   |   |   |     |

| Deskews                                            |              |   |     |   |   |   |     |

| Package<br>H = UFBGA                               |              |   |     |   |   |   |     |

| T = LQFP                                           |              |   |     |   |   |   |     |

| U = UFQFPN                                         |              |   |     |   |   |   |     |

| Y = WLCSP                                          |              |   |     |   |   |   |     |

| T - WLCGF                                          |              |   |     |   |   |   |     |

| Temperature range                                  |              |   |     |   |   |   |     |

| 6 = -40 to 85 °C                                   |              |   |     |   |   |   |     |

| 7 = -40 to 105 °C                                  |              |   |     |   |   |   |     |

|                                                    |              |   |     |   |   |   |     |

| Options                                            |              |   |     |   |   |   |     |

| xxx = code ID of programmed parts (includes parts) | ocking type) |   |     |   |   |   |     |

xxx = code ID of programmed parts (includes packing type)

TR = tape and reel packing

blank = tray packing