Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                 |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 52                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091rct6tr |

# List of figures

| Figure 1.                | Block diagram                                                       | . 12 |

|--------------------------|---------------------------------------------------------------------|------|

| Figure 2.                | Clock tree                                                          |      |

| Figure 3.                | UFBGA100 package pinout                                             |      |

| Figure 4.                | LQFP100 package pinout                                              |      |

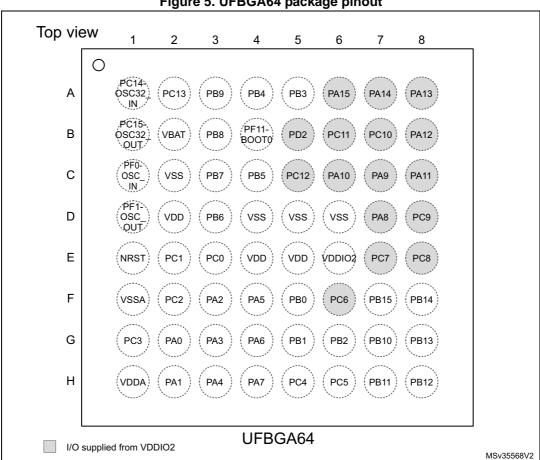

| Figure 5.                | UFBGA64 package pinout                                              |      |

| Figure 6.                | LQFP64 package pinout                                               |      |

| Figure 7.                | WLCSP64 package pinout                                              |      |

| Figure 8.                | LQFP48 package pinout                                               |      |

| Figure 9.                | UFQFPN48 package pinout                                             |      |

| Figure 10.               | STM32F091xC memory map                                              |      |

| Figure 11.               | Pin loading conditions                                              |      |

| Figure 12.               | Pin input voltage                                                   |      |

| Figure 13.               | Power supply scheme                                                 |      |

| Figure 14.               | Current consumption measurement scheme                              |      |

| Figure 15.               | High-speed external clock source AC timing diagram                  |      |

| Figure 16.               | Low-speed external clock source AC timing diagram                   |      |

| Figure 17.               | Typical application with an 8 MHz crystal                           |      |

| Figure 17.               | Typical application with a 32.768 kHz crystal                       |      |

| Figure 19.               | HSI oscillator accuracy characterization results for soldered parts |      |

| Figure 19.               | HSI14 oscillator accuracy characterization results                  |      |

| Figure 20.<br>Figure 21. | HSI48 oscillator accuracy characterization results                  |      |

| Figure 21.               |                                                                     |      |

| •                        | TC and TTa I/O input characteristics                                |      |

| Figure 23.               |                                                                     |      |

| Figure 24.               | I/O AC characteristics definition                                   |      |

| Figure 25.               | Recommended NRST pin protection                                     |      |

| Figure 26.               | ADC accuracy characteristics                                        |      |

| Figure 27.               | Typical connection diagram using the ADC                            |      |

| Figure 28.               | SPI timing diagram - slave mode and CPHA = 0                        |      |

| Figure 29.               | SPI timing diagram - slave mode and CPHA = 1                        |      |

| Figure 30.               | SPI timing diagram - master mode                                    |      |

| Figure 31.               | I <sup>2</sup> S slave timing diagram (Philips protocol)            |      |

| Figure 32.               | I <sup>2</sup> S master timing diagram (Philips protocol)           |      |

| Figure 33.               | UFBGA100 package outline                                            |      |

| Figure 34.               | Recommended footprint for UFBGA100 package                          |      |

| Figure 35.               | UFBGA100 package marking example                                    |      |

| Figure 36.               | LQFP100 package outline                                             |      |

| Figure 37.               | Recommended footprint for LQFP100 package                           |      |

| Figure 38.               | LQFP100 package marking example                                     |      |

| Figure 39.               | UFBGA64 package outline                                             | 106  |

| Figure 40.               | Recommended footprint for UFBGA64 package                           |      |

| Figure 41.               | UFBGA64 package marking example                                     |      |

| Figure 42.               | WLCSP64 package outline                                             |      |

| Figure 43.               | Recommended footprint for WLCSP64 package                           |      |

| Figure 44.               | WLCSP64 package marking example                                     |      |

| Figure 45.               | LQFP64 package outline                                              | 112  |

| Figure 46.               | Recommended footprint for LQFP64 package                            |      |

| Figure 47.               | LQFP64 package marking example                                      |      |

| Figure 48.               | LQFP48 package outline                                              | 115  |

# List of figures

### STM32F091xB STM32F091xC

| Figure 49. | Recommended footprint for LQFP48 package        | 116 |

|------------|-------------------------------------------------|-----|

| Figure 50. | LQFP48 package marking example                  | 117 |

| Figure 51. | UFQFPN48 package outline                        | 118 |

| Figure 52. | Recommended footprint for UFQFPN48 package      | 119 |

| Figure 53. | UFQFPN48 package marking example                | 120 |

| Figure 54. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 123 |

Table 2. STM32F091xB/xC family device features and peripheral counts

| Perip                 | heral                                 | STM32        | F091Cx                                                                                                               | STM32 | F091Rx                | STM32            | 2F091Vx        |  |

|-----------------------|---------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------|------------------|----------------|--|

| Flash mem             | nory (Kbyte)                          | 128          | 256                                                                                                                  | 128   | 256                   | 128              | 256            |  |

| SRAM                  | (Kbyte)                               |              |                                                                                                                      | 1     | 32                    | 1                | 1              |  |

|                       | Advanced control                      |              |                                                                                                                      | 1     | (16-bit)              |                  |                |  |

| Timers                | General purpose                       |              |                                                                                                                      |       | (16-bit)<br>(32-bit)  |                  |                |  |

| Comm.<br>interfaces   | Basic                                 |              |                                                                                                                      | 2     | (16-bit)              |                  |                |  |

|                       | SPI [I <sup>2</sup> S] <sup>(1)</sup> |              |                                                                                                                      |       | 2 [2]                 |                  |                |  |

|                       | I <sup>2</sup> C                      |              | 2                                                                                                                    |       |                       |                  |                |  |

|                       | USART                                 | (            | 6 8                                                                                                                  |       |                       |                  |                |  |

| mionacco              | CAN                                   | 1            |                                                                                                                      |       |                       |                  |                |  |

|                       | CEC                                   |              | 1                                                                                                                    |       |                       |                  |                |  |

|                       | t ADC<br>f channels)                  |              | 1<br>+ 3 int.)                                                                                                       |       |                       | 1<br>. + 3 int.) |                |  |

|                       | t DAC<br>f channels)                  | 1<br>(2)     |                                                                                                                      |       |                       |                  |                |  |

| Analog co             | omparator                             |              |                                                                                                                      |       | 2                     |                  |                |  |

| GP                    | lOs                                   | 3            | 8                                                                                                                    |       | 52                    | 3                | 38             |  |

|                       | re sensing<br>nnels                   | 17 18        |                                                                                                                      | 2     | 24                    |                  |                |  |

| Max. CPU              | frequency                             | 48 MHz       |                                                                                                                      |       |                       |                  |                |  |

| Operating voltage     |                                       | 2.0 to 3.6 V |                                                                                                                      |       |                       |                  |                |  |

| Operating temperature |                                       | A            | Ambient operating temperature: -40°C to 85°C / -40°C to 105°C  Junction temperature: -40°C to 105°C / -40°C to 125°C |       |                       |                  | 5°C            |  |

| Pack                  | kages                                 | LQF<br>UFQF  | P48<br>PN48                                                                                                          | UFB   | FP64<br>GA64<br>CSP64 |                  | FP100<br>GA100 |  |

<sup>1.</sup> The SPI interface can be used either in SPI mode or in I<sup>2</sup>S audio mode.

threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.5.3 Voltage regulator

The regulator has two operating modes and it is always enabled after reset.

- Main (MR) is used in normal operating mode (Run).

- Low power (LPR) can be used in Stop mode where the power demand is reduced.

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

#### 3.5.4 Low-power modes

The STM32F091xB/xC microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, the PVD output, RTC, I2C1, USART1, USART2, USART3, COMPx,  $V_{DDIO2}$  supply comparator or the CEC.

The CEC, USART1, USART2, USART3 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data. If this is used when the voltage regulator is put in low power mode, the regulator is first switched to normal mode before the clock is provided to the given peripheral.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

# 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches

Note:

precise voltage of  $V_{\mathsf{REFINT}}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Table 4. Internal voltage reference calibration values

| Calibration value name | Description                                                                              | Memory address            |

|------------------------|------------------------------------------------------------------------------------------|---------------------------|

|                        | Raw data acquired at a temperature of 30 °C (± 5 °C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

### 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the  $V_{BAT}$  battery voltage using the internal ADC channel ADC\_IN18. As the  $V_{BAT}$  voltage may be higher than  $V_{DDA}$ , and thus outside the ADC input range, the  $V_{BAT}$  pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the  $V_{BAT}$  voltage.

## 3.11 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This digital Interface supports the following features:

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

Six DAC trigger inputs are used in the device. The DAC is triggered through the timer trigger outputs and the DAC interface is generating its own DMA requests.

# 3.12 Comparators (COMP)

The device embeds two fast rail-to-rail low-power comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pins

- Internal reference voltage or submultiple (1/4, 1/2, 3/4). Refer to Table 28: Embedded internal reference voltage for the value and precision of the internal reference voltage.

Figure 5. UFBGA64 package pinout

Table 20. STM32F091xB/xC peripheral register boundary addresses (continued)

| Bus | Boundary address          | Size  | Peripheral    |

|-----|---------------------------|-------|---------------|

|     | 0x4001 5C00 - 0x4001 7FFF | 9 KB  | Reserved      |

|     | 0x4001 5800 - 0x4001 5BFF | 1 KB  | DBGMCU        |

|     | 0x4001 4C00 - 0x4001 57FF | 3 KB  | Reserved      |

|     | 0x4001 4800 - 0x4001 4BFF | 1 KB  | TIM17         |

|     | 0x4001 4400 - 0x4001 47FF | 1 KB  | TIM16         |

|     | 0x4001 4000 - 0x4001 43FF | 1 KB  | TIM15         |

|     | 0x4001 3C00 - 0x4001 3FFF | 1 KB  | Reserved      |

|     | 0x4001 3800 - 0x4001 3BFF | 1 KB  | USART1        |

|     | 0x4001 3400 - 0x4001 37FF | 1 KB  | Reserved      |

|     | 0x4001 3000 - 0x4001 33FF | 1 KB  | SPI1/I2S1     |

| APB | 0x4001 2C00 - 0x4001 2FFF | 1 KB  | TIM1          |

|     | 0x4001 2800 - 0x4001 2BFF | 1 KB  | Reserved      |

|     | 0x4001 2400 - 0x4001 27FF | 1 KB  | ADC           |

|     | 0x4001 2000 - 0x4001 23FF | 1 KB  | Reserved      |

|     | 0x4001 1C00 – 0x4001 1FFF | 1 KB  | USART8        |

|     | 0x4001 1800 – 0x4001 1BFF | 1 KB  | USART7        |

|     | 0x4001 1400 – 0x4001 17FF | 1 KB  | USART6        |

|     | 0x4001 0800 - 0x4001 13FF | 3 KB  | Reserved      |

|     | 0x4001 0400 - 0x4001 07FF | 1 KB  | EXTI          |

|     | 0x4001 0000 - 0x4001 03FF | 1 KB  | SYSCFG + COMP |

|     | 0x4000 8000 - 0x4000 FFFF | 32 KB | Reserved      |

**Table 22. Current characteristics**

| Symbol                   | Ratings                                                                         | Max.                 | Unit |

|--------------------------|---------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>        | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>        | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>    | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>    | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                          | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>     | Output current source by any I/O and control pin                                | -25                  |      |

|                          | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| $\Sigma I_{IO(PIN)}$     | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                          | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                          | Injected current on FT and FTf pins                                             | -5/+0 <sup>(4)</sup> |      |

| $I_{\rm INJ(PIN)}^{(3)}$ | Injected current on TC and RST pin                                              | ± 5                  | 1    |

|                          | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  |      |

| ΣΙ <sub>ΙΝJ(PIN)</sub>   | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

- 1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

- 2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

- 3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

- 4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 59: ADC accuracy*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

**Table 23. Thermal characteristics**

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

Note:

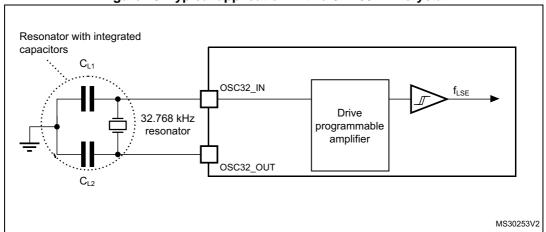

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 18. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

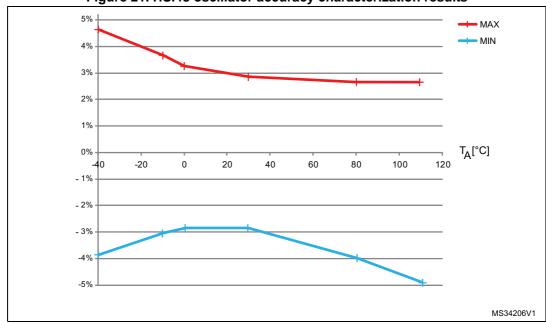

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 41* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. The provided curves are characterization results, not tested in production.

# High-speed internal 48 MHz (HSI48) RC oscillator

Table 43. HSI48 oscillator characteristics<sup>(1)</sup>

| Symbol                  | Parameter                          | Conditions                                   | Min                 | Тур                | Max                                                                                                                                                       | Unit |

|-------------------------|------------------------------------|----------------------------------------------|---------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| f <sub>HSI48</sub>      | Frequency                          | -                                            | -                   | 48                 | -                                                                                                                                                         | MHz  |

| TRIM                    | HSI48 user-trimming step           | -                                            | 0.09 <sup>(2)</sup> | 0.14               | 0.2 <sup>(2)</sup>                                                                                                                                        | %    |

| DuCy <sub>(HSI48)</sub> | Duty cycle                         | -                                            | 45 <sup>(2)</sup>   | -                  | 55 <sup>(2)</sup>                                                                                                                                         | %    |

|                         | Accuracy of the HSI48              | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -4.9 <sup>(3)</sup> | -                  | 4.7 <sup>(3)</sup>                                                                                                                                        | %    |

| ACC                     |                                    | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}$  | -4.1 <sup>(3)</sup> | -                  | 3.7 <sup>(3)</sup>                                                                                                                                        | %    |

| ACC <sub>HSI48</sub>    | oscillator (factory calibrated)    | ICTIOI40                                     | -                   | 3.4 <sup>(3)</sup> | %                                                                                                                                                         |      |

|                         |                                    | T <sub>A</sub> = 25 °C                       | -2.8                | -                  | - M<br>0.2 <sup>(2)</sup> 9<br>55 <sup>(2)</sup> 9<br>4.7 <sup>(3)</sup> 9<br>3.7 <sup>(3)</sup> 9<br>3.4 <sup>(3)</sup> 9<br>2.9 9<br>6 <sup>(2)</sup> µ | %    |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time      | -                                            | -                   | -                  | 6 <sup>(2)</sup>                                                                                                                                          | μs   |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power consumption | -                                            | -                   | 312                | 350 <sup>(2)</sup>                                                                                                                                        | μА   |

- 1.  $V_{DDA}$  = 3.3 V,  $T_{A}$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

Figure 21. HSI48 oscillator accuracy characterization results

74/128 DocID026284 Rev 4

Table 53. I/O static characteristics (continued)

| Symbol          | Parameter                                               | Conditions                             | Min | Тур | Max | Unit |

|-----------------|---------------------------------------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>PU</sub> | Weak pull-up<br>equivalent resistor<br>(3)              | V <sub>IN</sub> = V <sub>SS</sub>      | 25  | 40  | 55  | kΩ   |

| R <sub>PD</sub> | Weak pull-down<br>equivalent<br>resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub> | 25  | 40  | 55  | kΩ   |

| C <sub>IO</sub> | I/O pin capacitance                                     | -                                      | -   | 5   | -   | pF   |

- 1. Data based on design simulation only. Not tested in production.

- The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 52: I/O current injection susceptibility.

- 3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* for standard I/Os, and in *Figure 23* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOX</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 21: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 21: Voltage characteristics).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

Table 54. Output voltage characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                               | Conditions                                                  | Min                     | Max | Unit |  |

|-----------------------------------|---------------------------------------------------------|-------------------------------------------------------------|-------------------------|-----|------|--|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                    | -                       | 0.4 | .,   |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | $ I_{IO}  = 8 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$  | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                     | -                       | 0.4 | .,   |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V      | 2.4                     | -   | V    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 20 mA                                   | -                       | 1.3 | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2.7 V                                  | V <sub>DDIOx</sub> -1.3 | -   | ]    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 6 mA                                    | -                       | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2 V                                    | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                 | II I = 4 mA                                                 | -                       | 0.4 | V    |  |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 4 mA                                    | V <sub>DDIOx</sub> -0.4 | -   | V    |  |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in Fm+ mode | $ I_{IO}  = 20 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | -                       | 0.4 | V    |  |

|                                   | Triii+ mode                                             | I <sub>IO</sub>   = 10 mA                                   | -                       | 0.4 | V    |  |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 21:

Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

- 2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

- 3. Data based on characterization results. Not tested in production.

- 4. Data based on characterization results. Not tested in production.

82/128

DocID026284 Rev 4

Table 57. ADC characteristics (continued)

| Symbol                                                                                                                                                                                                                                                                                                                 | Parameter                                              | Conditions                                      | Min                                               | Тур                                                                        | Max                                               | Unit                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------|----------------------------|

| f <sub>TRIG</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                       | External trigger frequency                             | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | -                                                 | -                                                                          | 823                                               | kHz                        |

| 11410                                                                                                                                                                                                                                                                                                                  |                                                        | 12-bit resolution                               | -                                                 | -                                                                          | 17                                                | 1/f <sub>ADC</sub>         |

| V <sub>AIN</sub>                                                                                                                                                                                                                                                                                                       | Conversion voltage range                               | -                                               | 0                                                 | -                                                                          | $V_{DDA}$                                         | V                          |

| R <sub>AIN</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                        | External input impedance                               | See Equation 1 and Table 58 for details         | -                                                 | -                                                                          | 50                                                | kΩ                         |

| R <sub>ADC</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                        | Sampling switch resistance                             | -                                               | -                                                 | -                                                                          | 1                                                 | kΩ                         |

| C <sub>ADC</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                        | Internal sample and hold capacitor                     | -                                               | -                                                 | -                                                                          | 8                                                 | pF                         |

| + (2)(3)                                                                                                                                                                                                                                                                                                               | Calibration time                                       | f <sub>ADC</sub> = 14 MHz                       |                                                   | 5.9                                                                        |                                                   | μs                         |

| CAL, ,, ,                                                                                                                                                                                                                                                                                                              | Calibration time                                       | -                                               |                                                   | 83                                                                         |                                                   | 1/f <sub>ADC</sub>         |

|                                                                                                                                                                                                                                                                                                                        | ADC_DR register ready latency                          | ADC clock = HSI14                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles | -                                                                          | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(2)(4)</sup>                                                                                                                                                                                                                                                                                 |                                                        | ADC clock = PCLK/2                              | -                                                 | 4.5                                                                        | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                                                                                                                                                                                                                                                                                        |                                                        | ADC clock = PCLK/4                              | -                                                 | 8.5                                                                        | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                                                                                                                                                                                                                                                                                        |                                                        | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$         |                                                   | 0.196                                                                      |                                                   | μs                         |

|                                                                                                                                                                                                                                                                                                                        |                                                        | $f_{ADC} = f_{PCLK}/2$                          | 5.5                                               |                                                                            |                                                   | 1/f <sub>PCLK</sub>        |

| $R_{AIN}^{(2)}$ External input $R_{ADC}^{(2)}$ Sampling swaresistance $C_{ADC}^{(2)}$ Internal same capacitor $t_{CAL}^{(2)(3)}$ Calibration to $t_{CAL}^{(2)(3)}$ ADC_DR regulatency $t_{latr}^{(2)}$ Trigger conversion $t_{S}^{(2)}$ Sampling time $t_{STAB}^{(2)}$ Stabilization $t_{STAB}^{(2)}$ Total conversion | Trigger conversion latency                             | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$         | 0.219                                             |                                                                            | μs                                                |                            |

|                                                                                                                                                                                                                                                                                                                        | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 1/f <sub>PCLK</sub>                             |                                                   |                                                                            |                                                   |                            |

|                                                                                                                                                                                                                                                                                                                        |                                                        | $f_{ADC} = f_{HSI14} = 14 \text{ MHz}$          | 0.179                                             | -                                                                          | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                                                                                                                                                                                                                                                                                                  |                                                        | f <sub>ADC</sub> = f <sub>HSI14</sub>           | -                                                 | 1                                                                          | -                                                 | 1/f <sub>HSI14</sub>       |

| <sub>+-</sub> (2)                                                                                                                                                                                                                                                                                                      | Sampling time                                          | f <sub>ADC</sub> = 14 MHz                       | 0.107                                             | -                                                                          | 17.1                                              | μs                         |

| ıs                                                                                                                                                                                                                                                                                                                     | Campling time                                          | -                                               | 1.5                                               | -                                                                          | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                       | Stabilization time                                     | -                                               | 14                                                |                                                                            | 1/f <sub>ADC</sub>                                |                            |

| too: :(2)                                                                                                                                                                                                                                                                                                              |                                                        |                                                 | 1                                                 | -                                                                          | 18                                                | μs                         |

| *CONV* 7                                                                                                                                                                                                                                                                                                               | (including sampling time)                              | 12-bit resolution                               |                                                   | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                                                   | 1/f <sub>ADC</sub>         |

<sup>1.</sup> During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu A$  on  $I_{DD}$  and 60  $\mu A$  on  $I_{DD}$  should be taken into account.

86/128 DocID026284 Rev 4

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> Specified value includes only ADC timing. It does not include the latency of the register access.

<sup>4.</sup> This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

# 6.3.17 DAC electrical specifications

Table 60. DAC characteristics

| Symbol                           | Parameter                                                                                                                                                     | Min | Тур | Max                     | Unit | Comments                                                                                                               |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage for DAC ON                                                                                                                              | 2.4 | -   | 3.6                     | ٧    | -                                                                                                                      |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer                                                                                                                                    | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                     |

| NLOAD.                           | ON                                                                                                                                                            | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                     |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with buffer OFF                                                                                                                              | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                                                                               | -   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                        |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer ON                                                                                                                          | 0.2 | -   | -                       | ٧    | It gives the maximum output excursion of the DAC. It corresponds to 12-bit input code (0x0E0) to (0xF1C) at            |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer ON                                                                                                                         | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{\rm DDA}$ = 3.6 V and (0x155) and (0xEAB) at $V_{\rm DDA}$ = 2.4 V                                                 |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                                                                         | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                            |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer OFF                                                                                                                        | -   | _   | V <sub>DDA</sub> – 1LSB | ٧    | excursion of the DAC.                                                                                                  |

| I <sub>DDA</sub> <sup>(1)</sup>  | DAC DC current consumption in quiescent mode <sup>(2)</sup>                                                                                                   | -   | -   | 600                     | μA   | With no load, middle code (0x800) on the input                                                                         |

| ·DDA                             |                                                                                                                                                               | -   | -   | 700                     | μA   | With no load, worst code (0xF1C) on the input                                                                          |

| DNL <sup>(3)</sup>               | Differential non linearity Difference between two                                                                                                             | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                              |

|                                  | consecutive code-1LSB)                                                                                                                                        | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                              |

|                                  | Integral non linearity<br>(difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                              |

| INL <sup>(3)</sup>               |                                                                                                                                                               | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                              |

|                                  | Offset error                                                                                                                                                  | -   | -   | ±10                     | mV   | -                                                                                                                      |

| Offset <sup>(3)</sup>            | (difference between measured value at Code                                                                                                                    | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at V <sub>DDA</sub> = 3.6 V                                                                |

|                                  | (0x800) and the ideal value<br>= V <sub>DDA</sub> /2)                                                                                                         | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at V <sub>DDA</sub> = 3.6 V                                                                |

|                                  |                                                                                                                                                               |     |     |                         |      |                                                                                                                        |

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |

|-------------------|--------------|--------------------------------|--------------------------------|------|

| /4                | 0            | 0.1                            | 409.6                          |      |

| /8                | 1            | 0.2                            | 819.2                          |      |

| /16               | 2            | 0.4                            | 1638.4                         |      |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |

| /64               | 4            | 1.6                            | 6553.6                         |      |

| /128              | 5            | 3.2                            | 13107.2                        |      |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |

Table 65. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| rabio ou i i i i bo i i i i i bo i i i i i i i i |       |                   |                   |      |  |  |

|--------------------------------------------------|-------|-------------------|-------------------|------|--|--|

| Prescaler                                        | WDGTB | Min timeout value | Max timeout value | Unit |  |  |

| 1                                                | 0     | 0.0853            | 5.4613            |      |  |  |

| 2                                                | 1     | 0.1706            | 10.9226           | me   |  |  |

| 4                                                | 2     | 0.3413            | 21.8453           | ms   |  |  |

| 8                                                | 3     | 0.6826            | 43.6906           |      |  |  |

Table 66. WWDG min/max timeout value at 48 MHz (PCLK)

#### 6.3.22 Communication interfaces

### I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{\rm DDIOX}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

94/128 DocID026284 Rev 4

Table 67. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                        | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

- 1. Guaranteed by design, not tested in production.

- 2. Spikes with widths below t<sub>AF(min)</sub> are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

### SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 68* for SPI or in *Table 69* for I<sup>2</sup>S are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 24: General operating conditions*.

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 68. SPI characteristics<sup>(1)</sup>

| Symbol                                       | Parameter                        | Conditions                                            | Min         | Max         | Unit   |

|----------------------------------------------|----------------------------------|-------------------------------------------------------|-------------|-------------|--------|

| f <sub>SCK</sub>                             | SPI clock frequency              | Master mode                                           | -           | 18          | MHz    |

| 1/t <sub>c(SCK)</sub>                        | SPI Clock frequency              | Slave mode -                                          |             | 18          | IVIIIZ |

| t <sub>r(SCK)</sub>                          | SPI clock rise and fall time     | Capacitive load: C = 15 pF                            | -           | 6           | ns     |

| t <sub>su(NSS)</sub>                         | NSS setup time                   | Slave mode                                            | 4Tpclk      | -           |        |

| t <sub>h(NSS)</sub>                          | NSS hold time                    | Slave mode                                            | 2Tpclk + 10 | -           |        |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |        |

| t <sub>su(MI)</sub>                          | Data input setup time            | Master mode                                           | 4           | -           |        |

| t <sub>su(SI)</sub>                          | Data input setup time            | Slave mode                                            | 5           | -           |        |

| t <sub>h(MI)</sub>                           | Data input hold time             | Master mode                                           | 4           | -           |        |

| t <sub>h(SI)</sub>                           | Data input hold time             | Slave mode                                            | 5           | -           | ns     |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time          | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |        |

| t <sub>dis(SO)</sub> (3)                     | Data output disable time         | Slave mode                                            | 0           | 18          |        |

| t <sub>v(SO)</sub>                           | Data output valid time           | Slave mode (after enable edge)                        | -           | 22.5        |        |

| t <sub>v(MO)</sub>                           | Data output valid time           | Master mode (after enable edge)                       | -           | 6           |        |

| t <sub>h(SO)</sub>                           | Data output hold time            | Slave mode (after enable edge)                        | 11.5        | -           |        |

| t <sub>h(MO)</sub>                           | Data output noid tille           | Master mode (after enable edge)                       | 2           | -           |        |

| DuCy(SCK)                                    | SPI slave input clock duty cycle | Slave mode 25                                         |             | 75          | %      |

- 1. Data based on characterization results, not tested in production.

- 2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

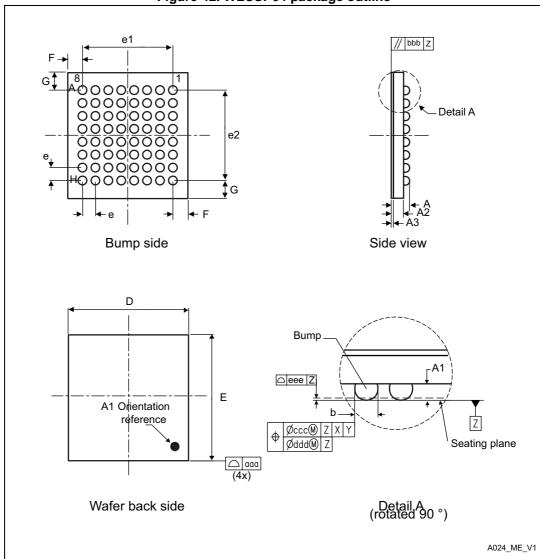

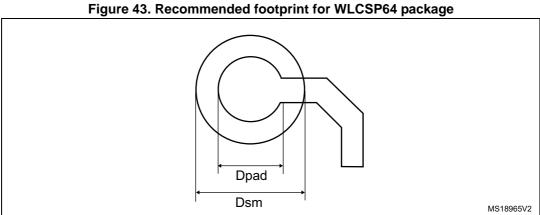

# 7.4 WLCSP64 package information

WLCSP64 is a 64-ball, 3.347 x 3.585 mm, 0.4 mm pitch wafer-level chip-scale package.

Figure 42. WLCSP64 package outline

1. Drawing is not to scale.

Table 75. WLCSP64 package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| Α      | 0.525       | 0.555 | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1     | -           | 0.175 | -     | -                     | 0.0069 | -      |

| A2     | -           | 0.380 | -     | -                     | 0.0150 | -      |

| A3     | -           | 0.025 | -     | -                     | 0.0010 | -      |

| Symbol           | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|------------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol           | Min         | Тур    | Max   | Min                   | Тур    | Max    |

| b <sup>(2)</sup> | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                | 3.312       | 3.347  | 3.382 | 0.1304                | 0.1318 | 0.1331 |

| Е                | 3.550       | 3.585  | 3.620 | 0.1398                | 0.1411 | 0.1425 |

| е                | -           | 0.400  | -     | -                     | 0.0157 | -      |

| e1               | -           | 2.800  | -     | -                     | 0.1102 | -      |

| e2               | -           | 2.800  | -     | -                     | 0.1102 | -      |

| F                | -           | 0.2735 | -     | -                     | 0.0108 | -      |

| G                | -           | 0.3925 | -     | -                     | 0.0155 | -      |

| aaa              | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb              | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ccc              | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd              | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee              | -           | -      | 0.050 | -                     | -      | 0.0020 |

Table 75. WLCSP64 package mechanical data (continued)

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- 2. Dimension is measured at the maximum bump diameter parallel to primary datum  ${\sf Z}$ .

Table 76. WLCSP64 recommended PCB design rules

| Dimension      | Recommended values                             |  |  |

|----------------|------------------------------------------------|--|--|

| Pitch          | 0.4                                            |  |  |

| Dpad           | 260 μm max. (circular)                         |  |  |

| рац            | 220 µm recommended                             |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |

DocID026284 Rev 4 110/128

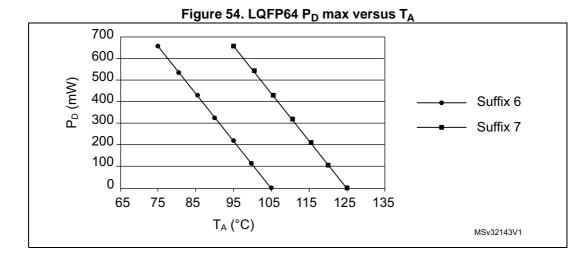

Using the values obtained in  $\textit{Table 80}\,\mathsf{T}_{\mathsf{Jmax}}$  is calculated as follows:

For LQFP64, 45 °C/W

$$T_{Jmax}$$

= 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see Section 8: Ordering information) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to the figure below to select the required temperature range (suffix 6 or 7) according to your temperature or power requirements.

$\Box$

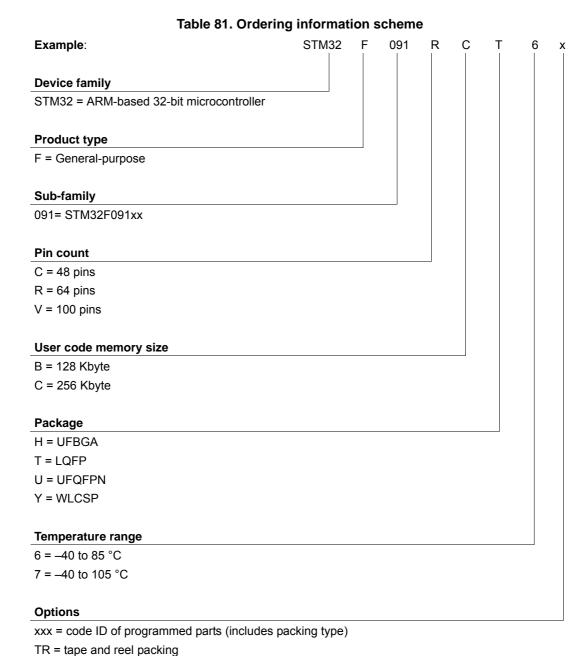

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID026284 Rev 4

blank = tray packing