Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091rct7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 3.14.6   | SysTick timer                                                                      | . 23 |

|---|-------|----------|------------------------------------------------------------------------------------|------|

|   | 3.15  | Real-ti  | me clock (RTC) and backup registers                                                | 23   |

|   | 3.16  | Inter-in | tegrated circuit interface (I <sup>2</sup> C)                                      | 24   |

|   | 3.17  | Univer   | sal synchronous/asynchronous receiver/transmitter (USART)                          | 25   |

|   | 3.18  | Serial p | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) . | 26   |

|   | 3.19  | -        | efinition multimedia interface (HDMI) - consumer                                   |      |

|   |       | -        | nics control (CEC)                                                                 | 27   |

|   | 3.20  | Contro   | ller area network (CAN)                                                            | 27   |

|   | 3.21  | Clock r  | ecovery system (CRS)                                                               | 27   |

|   | 3.22  | Serial   | wire debug port (SW-DP)                                                            | 27   |

| 4 | Pino  | uts and  | pin descriptions                                                                   | 28   |

| 5 | Mem   | ory ma   | oping                                                                              | 45   |

| 6 | Elect | rical ch | aracteristics                                                                      | 49   |

|   | 6.1   | Param    | eter conditions                                                                    | 49   |

|   |       | 6.1.1    | Minimum and maximum values                                                         | . 49 |

|   |       | 6.1.2    | Typical values                                                                     | . 49 |

|   |       | 6.1.3    | Typical curves                                                                     | . 49 |

|   |       | 6.1.4    | Loading capacitor                                                                  | . 49 |

|   |       | 6.1.5    | Pin input voltage                                                                  | . 49 |

|   |       | 6.1.6    | Power supply scheme                                                                | . 50 |

|   |       | 6.1.7    | Current consumption measurement                                                    | . 51 |

|   | 6.2   | Absolu   | te maximum ratings                                                                 | 52   |

|   | 6.3   | Operat   | ing conditions                                                                     | 54   |

|   |       | 6.3.1    | General operating conditions                                                       | . 54 |

|   |       | 6.3.2    | Operating conditions at power-up / power-down                                      | . 54 |

|   |       | 6.3.3    | Embedded reset and power control block characteristics                             | . 55 |

|   |       | 6.3.4    | Embedded reference voltage                                                         | . 56 |

|   |       | 6.3.5    | Supply current characteristics                                                     | . 56 |

|   |       | 6.3.6    | Wakeup time from low-power mode                                                    | . 67 |

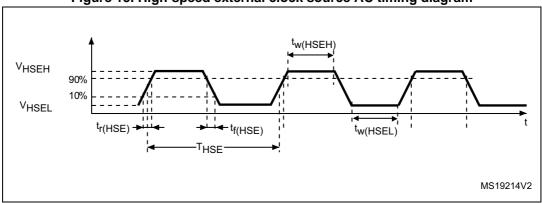

|   |       | 6.3.7    | External clock source characteristics                                              | . 67 |

|   |       | 6.3.8    | Internal clock source characteristics                                              | . 71 |

|   |       | 6.3.9    | PLL characteristics                                                                | . 75 |

|   |       | 6.3.10   | Memory characteristics                                                             | . 75 |

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 88 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

Both comparators can wake up from STOP mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

# 3.13 Touch sensing controller (TSC)

The STM32F091xB/xC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 24 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists in charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate. For operation, one capacitive sensing GPIO in each group is connected to an external capacitor and cannot be used as effective touch sensing channel.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

| Group | Capacitive sensing<br>signal name | Pin<br>name | Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|-----------------------------------|-------------|-------|-----------------------------------|-------------|

|       | TSC_G1_IO1                        | PA0         |       | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                        | PA1         | 5     | TSC_G5_IO2                        | PB4         |

|       | TSC_G1_IO3                        | PA2         | 5     | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                        | PA3         |       | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                        | PA4         |       | TSC_G6_IO1                        | PB11        |

| 2     | TSC_G2_IO2                        | PA5         | 6     | TSC_G6_IO2                        | PB12        |

| 2     | TSC_G2_IO3                        | PA6         | 0     | TSC_G6_IO3                        | PB13        |

|       | TSC_G2_IO4                        | PA7         |       | TSC_G6_IO4                        | PB14        |

|       | TSC_G3_IO1                        | PC5         |       | TSC_G7_IO1                        | PE2         |

| 3     | TSC_G3_IO2                        | PB0         | 7     | TSC_G7_IO2                        | PE3         |

| 5     | TSC_G3_IO3                        | PB1         | /     | TSC_G7_IO3                        | PE4         |

|       | TSC_G3_IO4                        | PB2         |       | TSC_G7_IO4                        | PE5         |

|       | TSC_G4_IO1 PA9                    |             |       | TSC_G8_IO1                        | PD12        |

| 4     | TSC_G4_IO2                        | PA10        | 8     | TSC_G8_IO2                        | PD13        |

| 4     | TSC_G4_IO3                        | PA11        | 0     | TSC_G8_IO3                        | PD14        |

|       | TSC_G4_IO4                        | PA12        |       | TSC_G8_IO4                        | PD15        |

Table 5. Capacitive sensing GPIOs available on STM32F091xB/xC devices

|                                       | Number of capacitive sensing channels |             |             |  |  |  |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|

| Analog I/O group                      | STM32F091Vx                           | STM32F091Rx | STM32F091Cx |  |  |  |  |  |

| G1                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G2                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G3                                    | 3                                     | 3           | 2           |  |  |  |  |  |

| G4                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G6                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G7                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| G8                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| Number of capacitive sensing channels | 24                                    | 18          | 17          |  |  |  |  |  |

### Table 6. Number of capacitive sensing channels available on STM32F091xB/xC devices

# 3.14 Timers and watchdogs

The STM32F091xB/xC devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 7 compares the features of the different timers.

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|--------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |

|                    | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

|                    | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |

| General<br>purpose | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                           | -                        |

|                    | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |

|                    | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |

| Basic              | TIM6<br>TIM7   | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                           | -                        |

Table 7. Timer feature comparison

### STM32F091xB STM32F091xC

## Pinouts and pin descriptions

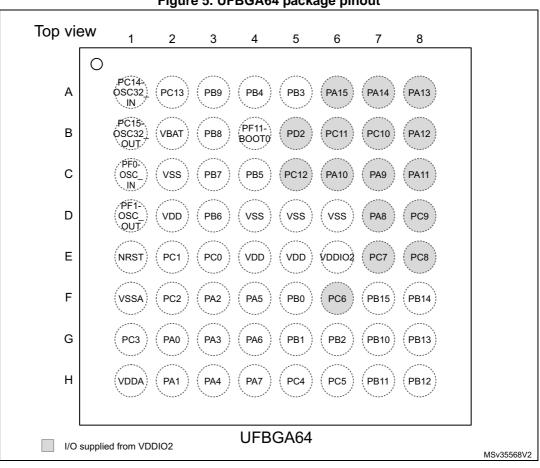

Figure 5. UFBGA64 package pinout

|          | Pi      | in nui  | mber   |         |                 |                                      |          |               |       | tions (continued)<br>Pin function                                                                                  | IS                      |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional<br>functions |

| L4       | 31      | G4      | 22     | G5      | 16              | PA6                                  | I/O      | ТТа           |       | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>COMP1_OUT,<br>TSC_G2_IO3,<br>EVENTOUT,<br>USART3_CTS | ADC_IN6                 |

| M4       | 32      | H4      | 23     | E4      | 17              | PA7                                  | I/O      | ТТа           |       | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N, TIM17_CH1,<br>COMP2_OUT,<br>TSC_G2_IO4,<br>EVENTOUT      | ADC_IN7                 |

| K5       | 33      | H5      | 24     | H5      | -               | PC4                                  | I/O      | TTa           |       | EVENTOUT, USART3_TX                                                                                                | ADC_IN14                |

| L5       | 34      | H6      | 25     | F4      | -               | PC5                                  | I/O      | ТТа           |       | TSC_G3_IO1,<br>USART3_RX                                                                                           | ADC_IN15,<br>WKUP5      |

| M5       | 35      | F5      | 26     | G4      | 18              | PB0                                  | I/O      | ТТа           |       | TIM3_CH3, TIM1_CH2N,<br>TSC_G3_IO2,<br>EVENTOUT,<br>USART3_CK                                                      | ADC_IN8                 |

| M6       | 36      | G5      | 27     | F3      | 19              | PB1                                  | I/O      | TTa           |       | TIM3_CH4,<br>USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                                                    | ADC_IN9                 |

| L6       | 37      | G6      | 28     | H4      | 20              | PB2                                  | I/O      | FT            |       | TSC_G3_IO4                                                                                                         | -                       |

| M7       | 38      | -       | -      | -       | -               | PE7                                  | I/O      | FT            |       | TIM1_ETR,<br>USART5_CK_RTS                                                                                         | -                       |

| L7       | 39      | -       | -      | -       | -               | PE8                                  | I/O      | FT            |       | TIM1_CH1N,<br>USART4_TX                                                                                            | -                       |

| M8       | 40      | -       | -      | -       | -               | PE9                                  | I/O      | FT            |       | TIM1_CH1, USART4_RX                                                                                                | -                       |

| L8       | 41      | -       | -      | -       | -               | PE10                                 | I/O      | FT            |       | TIM1_CH2N,<br>USART5_TX                                                                                            | -                       |

| M9       | 42      | -       | -      | -       | -               | PE11                                 | I/O      | FT            |       | TIM1_CH2, USART5_RX                                                                                                | -                       |

| L9       | 43      | -       | -      | -       | -               | PE12                                 | I/O      | FT            |       | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                                                    | -                       |

| M10      | 44      | _       | -      | -       | -               | PE13                                 | I/O      | FT            |       | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                                                     | -                       |

| Table 13. STM32F091xB/xC | pin definitions ( | (continued) |

|--------------------------|-------------------|-------------|

|                          |                   |             |

|          | Pi      | n nu    | mber   | s       |                 |                                      |          |               |       | Pin functior                                                                   | IS                       |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------|--------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                            | Additional<br>functions  |

| C5       | 91      | C4      | 57     | C5      | 41              | PB5                                  | I/O      | FT            |       | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2,<br>USART5_CK_RTS | WKUP6                    |

| В5       | 92      | D3      | 58     | A5      | 42              | PB6                                  | I/O      | FTf           |       | I2C1_SCL, USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                              | -                        |

| B4       | 93      | C3      | 59     | B5      | 43              | PB7                                  | I/O      | FTf           |       | I2C1_SDA, USART1_RX,<br>USART4_CTS,<br>TIM17_CH1N,<br>TSC_G5_IO4               | -                        |

| A4       | 94      | B4      | 60     | C6      | 44              | PF11-BOOT0                           | I/O      | FT            |       | -                                                                              | Boot memory<br>selection |

| A3       | 95      | В3      | 61     | A6      | 45              | PB8                                  | I/O      | FTf           |       | I2C1_SCL, CEC,<br>TIM16_CH1, TSC_SYNC,<br>CAN_RX                               | -                        |

| В3       | 96      | A3      | 62     | B6      | 46              | PB9                                  | I/O      | FTf           |       | SPI2_NSS, I2S2_WS,<br>I2C1_SDA, IR_OUT,<br>TIM17_CH1, EVENTOUT,<br>CAN_TX      | -                        |

| C3       | 97      | -       | -      | -       | -               | PE0                                  | I/O      | FT            |       | EVENTOUT, TIM16_CH1                                                            | -                        |

| A2       | 98      | -       | -      | -       | -               | PE1                                  | I/O      | FT            |       | EVENTOUT, TIM17_CH1                                                            | -                        |

| D3       | 99      | D4      | 63     | A7      | 47              | VSS                                  | S        | -             |       | Ground                                                                         |                          |

| C4       | 100     | E4      | 64     | A8      | 48              | VDD                                  | S        | -             |       | Digital power su                                                               | ipply                    |

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. - These GPIOs must not be used as current sources (e.g. to drive an LED). 1.

2. After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

3. PC6, PC7, PC8, PC9, PA8, PA9, PA10, PA11, PA12, PA13, PF6, PA14, PA15, PC10, PC11, PC12, PD0, PD1 and PD2 I/Os are supplied by VDDIO2

After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated. 4.

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_I02          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | USART5_CK_RTS       |

| PE8      | TIM1_CH1N | USART4_TX           |

| PE9      | TIM1_CH1  | USART4_RX           |

| PE10     | TIM1_CH2N | USART5_TX           |

| PE11     | TIM1_CH2  | USART5_RX           |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

Table 18. Alternate functions selected through GPIOE\_AFR registers for port E

## Table 19. Alternate functions selected through GPIOF\_AFR registers for port F

| Pin<br>name | AF0       | AF1       | AF2           |

|-------------|-----------|-----------|---------------|

| PF0         | CRS_SYNC  | I2C1_SDA  | -             |

| PF1         | -         | I2C1_SCL  | -             |

| PF2         | EVENTOUT  | USART7_TX | USART7_CK_RTS |

| PF3         | EVENTOUT  | USART7_RX | USART6_CK_RTS |

| PF6         | -         | -         | -             |

| PF9         | TIM15_CH1 | USART6_TX | -             |

| PF10        | TIM15_CH2 | USART6_RX | _             |

| Tabl                                | Table 27. Programmable voltage detector characteristics (continued) |              |      |      |                     |      |  |

|-------------------------------------|---------------------------------------------------------------------|--------------|------|------|---------------------|------|--|

| Symbol                              | Parameter                                                           | Conditions   | Min  | Тур  | Мах                 | Unit |  |

| V <sub>PVD6</sub>                   | PVD threshold 6                                                     | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |  |

|                                     |                                                                     | Falling edge | 2.56 | 2.68 | 2.8                 | V    |  |

| V                                   | PVD threshold 7                                                     | Rising edge  | 2.76 | 2.88 | 3                   | V    |  |

| V <sub>PVD7</sub>                   |                                                                     | Falling edge | 2.66 | 2.78 | 2.9                 | V    |  |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                      | -            | -    | 100  | -                   | mV   |  |

| I <sub>DD(PVD)</sub>                | PVD current consumption                                             | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |  |

Table 27. Programmable voltage detector characteristics (continued)

1. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 28* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                 | Parameter                                                           | Conditions                        | Min                  | Тур  | Max                | Unit   |

|------------------------|---------------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|

| V <sub>REFINT</sub>    | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |

| t <sub>START</sub>     | ADC_IN17 buffer startup time                                        | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |

| t <sub>S_vrefint</sub> | ADC sampling time when<br>reading the internal<br>reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |

| ΔV <sub>REFINT</sub>   | Internal reference voltage<br>spread over the<br>temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |

| T <sub>Coeff</sub>     | Temperature coefficient                                             | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |

Table 28. Embedded internal reference voltage

1. Guaranteed by design, not tested in production.

# 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

1. Guaranteed by design, not tested in production.

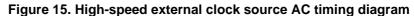

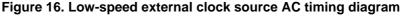

### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | time 50                |        | 50                     | 115  |

Table 38. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

DocID026284 Rev 4

# High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                  | Parameter                                                | Conditions                    | Min                 | Тур  | Мах                | Unit |  |

|-------------------------|----------------------------------------------------------|-------------------------------|---------------------|------|--------------------|------|--|

| f <sub>HSI48</sub>      | Frequency                                                | -                             | -                   | 48   | -                  | MHz  |  |

| TRIM                    | HSI48 user-trimming step                                 | -                             | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |  |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                               | -                             | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |  |

|                         | Accuracy of the HSI48<br>oscillator (factory calibrated) | $T_A = -40$ to 105 °C         | -4.9 <sup>(3)</sup> | -    | 4.7 <sup>(3)</sup> | %    |  |

| 100                     |                                                          | T <sub>A</sub> = −10 to 85 °C | -4.1 <sup>(3)</sup> | -    | 3.7 <sup>(3)</sup> | %    |  |

| ACC <sub>HSI48</sub>    |                                                          | T <sub>A</sub> = 0 to 70 °C   | -3.8 <sup>(3)</sup> | -    | 3.4 <sup>(3)</sup> | %    |  |

|                         |                                                          | T <sub>A</sub> = 25 °C        | -2.8                | -    | 2.9                | %    |  |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                            | -                             | -                   | -    | 6 <sup>(2)</sup>   | μs   |  |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power<br>consumption                    | -                             | -                   | 312  | 350 <sup>(2)</sup> | μA   |  |

# Table 43. HSI48 oscillator characteristics<sup>(1)</sup>

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

#### Figure 21. HSI48 oscillator accuracy characterization results

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 21: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 21: Voltage characteristics*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                              | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------------|-------------------------|-----|------|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                 | -                       | 0.4 |      |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V  | 2.4                     | -   | V    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 20 mA                               | -                       | 1.3 | v    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2.7 V                              | V <sub>DDIOx</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 6 mA -                              |                         | 0.4 | v    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | V <sub>DDIOx</sub> ≥ 2 V                                | V <sub>DDIOx</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                    | II I = 4 mA                                             | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub>   = 4 mA                                | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V | -                       | 0.4 | V    |

|                                   |                                                            | I <sub>IO</sub>   = 10 mA                               | -                       | 0.4 | V    |

## Table 54. Output voltage characteristics<sup>(1)</sup>

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 21: Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. Data based on characterization results. Not tested in production.

4. Data based on characterization results. Not tested in production.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| Table 58. R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz |                     |                                          |  |  |  |  |  |

|--------------------------------------------------------------|---------------------|------------------------------------------|--|--|--|--|--|

| T <sub>s</sub> (cycles)                                      | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |  |  |  |  |  |

| 1.5                                                          | 0.11                | 0.4                                      |  |  |  |  |  |

| 7.5                                                          | 0.54                | 5.9                                      |  |  |  |  |  |

| 13.5                                                         | 0.96                | 11.4                                     |  |  |  |  |  |

| 28.5                                                         | 2.04                | 25.2                                     |  |  |  |  |  |

| 41.5                                                         | 2.96                | 37.2                                     |  |  |  |  |  |

| 55.5                                                         | 3.96                | 50                                       |  |  |  |  |  |

| 71.5                                                         | 5.11                | NA                                       |  |  |  |  |  |

| 239.5                                                        | 17.1                | NA                                       |  |  |  |  |  |

1. Guaranteed by design, not tested in production.

# Table 59. ADC accuracy $^{(1)(2)(3)}$

| Symbol | Parameter                    | Test conditions                                                                                                                    | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                                                                    | ±1.3 | ±2                 |      |

| EO     | Offset error                 | $f_{PCLK} = 48 \text{ MHz},$                                                                                                       | ±1   | ±1.5               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 3 V to 3.6 V                                             | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | $T_A = 25 $ °C                                                                                                                     | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     |                                                                                                                                    | ±0.8 | ±1.5               |      |

| ET     | Total unadjusted error       |                                                                                                                                    | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                                                        | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ<br>V <sub>DDA</sub> = 2.7 V to 3.6 V                                           | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error | $T_{A} = -40 \text{ to } 105 \text{ °C}$                                                                                           | ±0.7 | ±1.3               |      |

| EL     | Integral linearity error     |                                                                                                                                    | ±1.2 | ±1.7               |      |

| ET     | Total unadjusted error       |                                                                                                                                    | ±3.3 | ±4                 |      |

| EO     | Offset error                 | f <sub>PCLK</sub> = 48 MHz,                                                                                                        | ±1.9 | ±2.8               |      |

| EG     | Gain error                   | $f_{ADC} = 14 \text{ MHz}, R_{AIN} < 10 \text{ k}\Omega$ $V_{DDA} = 2.4 \text{ V to } 3.6 \text{ V}$ $T_{A} = 25 ^{\circ}\text{C}$ | ±2.8 | ±3                 | LSB  |

| ED     | Differential linearity error |                                                                                                                                    | ±0.7 | ±1.3               | 1    |

| EL     | Integral linearity error     |                                                                                                                                    | ±1.2 | ±1.7               |      |

1. ADC DC accuracy values are measured after internal calibration.

# 6.3.18 Comparator characteristics

| Symbol                   | Parameter                                               | Condit                                | ions                     | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit  |

|--------------------------|---------------------------------------------------------|---------------------------------------|--------------------------|--------------------|-----|--------------------|-------|

| V <sub>DDA</sub>         | Analog supply voltage                                   | -                                     |                          | V <sub>DD</sub>    | -   | 3.6                | V     |

| V <sub>IN</sub>          | Comparator input voltage range                          | -                                     |                          | 0                  | -   | V <sub>DDA</sub>   | -     |

| V <sub>SC</sub>          | V <sub>REFINT</sub> scaler offset voltage               | -                                     |                          | -                  | ±5  | ±10                | mV    |

| t <sub>s_sc</sub>        | V <sub>REFINT</sub> scaler startup time from power down | -                                     |                          | -                  | -   | 0.2                | ms    |

| t <sub>START</sub>       | Comparator startup time                                 | Startup time to reach pasterification | opagation delay          | -                  | -   | 60                 | μs    |

|                          |                                                         | Ultra-low power mode                  |                          | -                  | 2   | 4.5                |       |

|                          | Propagation delay for                                   | Low power mode                        |                          | -                  | 0.7 | 1.5                | μs    |

|                          | 200 mV step with<br>100 mV overdrive                    | Medium power mode                     |                          | -                  | 0.3 | 0.6                |       |

|                          |                                                         | High speed mode                       | V <sub>DDA</sub> ≥ 2.7 V | -                  | 50  | 100                | 20    |

| 4                        |                                                         | nigh speed mode                       | V <sub>DDA</sub> < 2.7 V | -                  | 100 | 240                | ns    |

| t <sub>D</sub>           |                                                         | Ultra-low power mode                  |                          | -                  | 2   | 7                  |       |

|                          | Propagation delay for                                   | Low power mode                        |                          | -                  | 0.7 | 2.1                | μs    |

|                          | full range step with                                    | Medium power mode                     |                          | -                  | 0.3 | 1.2                |       |

|                          | 100 mV overdrive                                        | High speed mode                       | V <sub>DDA</sub> ≥ 2.7 V | -                  | 90  | 180                |       |

|                          |                                                         | nigh speed mode                       | V <sub>DDA</sub> < 2.7 V | -                  | 110 | 300                | ns    |

| V <sub>offset</sub>      | Comparator offset error                                 | -                                     |                          | -                  | ±4  | ±10                | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                    | -                                     |                          | -                  | 18  | -                  | µV/°C |

|                          |                                                         | Ultra-low power mode                  |                          | -                  | 1.2 | 1.5                |       |

| 1                        | COMP current                                            | Low power mode                        |                          | -                  | 3   | 5                  |       |

| I <sub>DD(COMP)</sub>    | consumption                                             | Medium power mode                     |                          | -                  | 10  | 15                 | μA    |

|                          |                                                         | High speed mode                       |                          | -                  | 75  | 100                |       |

#### Table 61. Comparator characteristics

# 6.3.19 Temperature sensor characteristics

| Symbol                             | Parameter                                      | Min  | Тур  | Max  | Unit  |

|------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>       | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                   | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC sampling time when reading the temperature | 4    | -    | -    | μs    |

1. Guaranteed by design, not tested in production.

2. Measured at  $V_{DDA}$  = 3.3 V ± 10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 3: Temperature sensor calibration values.

# 6.3.20 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                    | Min | Тур    | Мах | Unit |

|------------------------------------|----------------------------------------------|-----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>         | -   | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement        | -   | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                   | -1  | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the $V_{BAT}$ | 4   | -      | -   | μs   |

### Table 63. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design, not tested in production.

# 6.3.21 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                          | Conditions                    | Min | Тур                     | Max | Unit                 |

|------------------------|----------------------------------------------------|-------------------------------|-----|-------------------------|-----|----------------------|

| t <sub>res(TIM)</sub>  | Timer resolution time                              | -                             | -   | 1                       | -   | t <sub>TIMxCLK</sub> |

|                        | Timer resolution time                              | f <sub>TIMxCLK</sub> = 48 MHz | -   | 20.8                    | -   | ns                   |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to<br>CH4 | -                             | -   | f <sub>TIMxCLK</sub> /2 | -   | MHz                  |

|                        |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 24                      | -   | MHz                  |

|                        | 16-bit timer maximum period                        | -                             | -   | 2 <sup>16</sup>         | -   | t <sub>TIMxCLK</sub> |

| t                      |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 1365                    | -   | μs                   |

| t <sub>MAX_COUNT</sub> | 32-bit counter<br>maximum period                   | -                             | -   | 2 <sup>32</sup>         | -   | t <sub>TIMxCLK</sub> |

|                        |                                                    | f <sub>TIMxCLK</sub> = 48 MHz | -   | 89.48                   | -   | S                    |

Table 64. TIMx characteristics

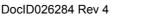

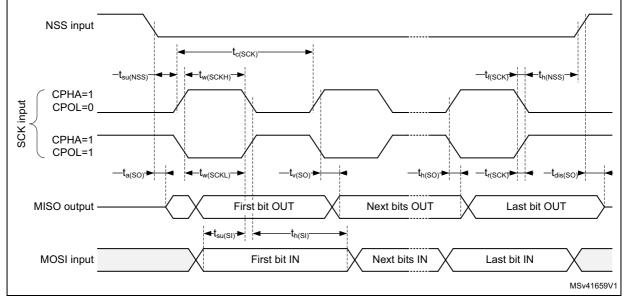

Figure 28. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| b      | 0.240       | 0.290 | 0.340 | 0.0094                | 0.0114 | 0.0134 |  |

| D      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |

| D1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| E      | 6.850       | 7.000 | 7.150 | 0.2697                | 0.2756 | 0.2815 |  |

| E1     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| Z      | -           | 0.750 | -     | -                     | 0.0295 | -      |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |  |

| Table 70. UFBGA100 | package mechanical dat | a (continued) |

|--------------------|------------------------|---------------|

|                    |                        |               |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

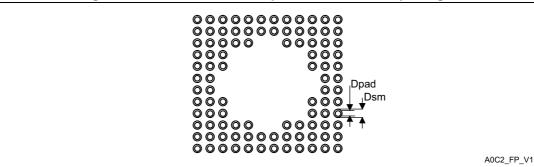

### Table 71. UFBGA100 recommended PCB design rules

| Dimension         | Recommended values                                                |  |  |

|-------------------|-------------------------------------------------------------------|--|--|

| Pitch             | 0.5                                                               |  |  |

| Dpad              | 0.280 mm                                                          |  |  |

| Dsm               | 0.370 mm typ. (depends on the solder mask registration tolerance) |  |  |

| Stencil opening   | 0.280 mm                                                          |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                     |  |  |

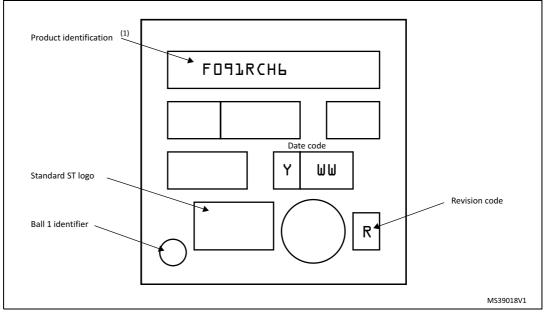

## **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| ccc    | -           | -     | 0.080 | -                     | -      | 0.0031 |

Table 77. LQFP64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

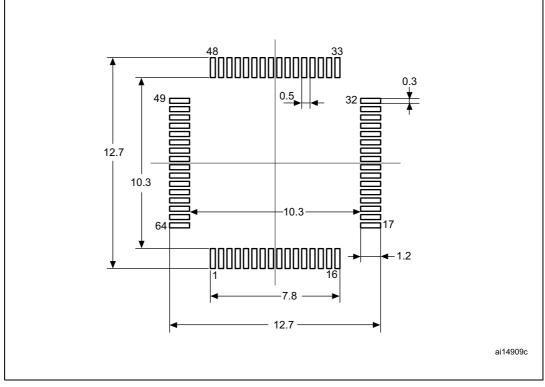

Figure 46. Recommended footprint for LQFP64 package

1. Dimensions are expressed in millimeters.

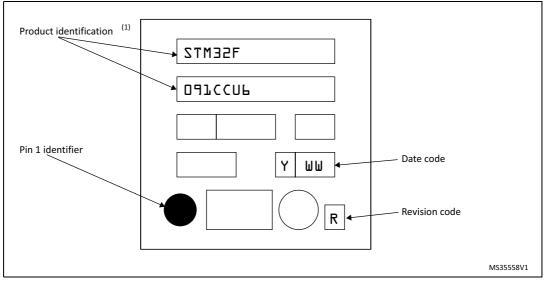

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 53. UFQFPN48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.