Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f091vct6u |  |

|----------------------------|------------------------------------------------------------------------|--|

| Supplier Device Package    | 100-LQFP (14x14)                                                       |  |

| Package / Case             | 100-LQFP                                                               |  |

| Mounting Type              | Surface Mount                                                          |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Oscillator Type            | Internal                                                               |  |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                  |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |  |

| RAM Size                   | 32K x 8                                                                |  |

| EEPROM Size                | -                                                                      |  |

| Program Memory Type        | FLASH                                                                  |  |

| Program Memory Size        | 256KB (256K x 8)                                                       |  |

| Number of I/O              | 88                                                                     |  |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                |  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                |  |

| Speed                      | 48MHz                                                                  |  |

| Core Size                  | 32-Bit Single-Core                                                     |  |

| Core Processor             | ARM® Cortex®-M0                                                        |  |

| Product Status             | Active                                                                 |  |

| Details                    |                                                                        |  |

SWCLK SWDIO as AF POWER Serial Wire Debug VOLT.REG  $V_{DD} = 2 \text{ to } 3.6 \text{ V}$ 3.3 V to 1.8 V Obl Flash Or memory interface Flash GPL up to 256 KB 32-bit CORTEX-M0 CPU OKIN ← SUPPLY SUPERVISION  $f_{MAX} = 48 \text{ MHz}$ V<sub>DDIO2</sub> OKIN ◀ NRST SRAM 32 KB SRAM controller matri Reset ◀  $V_{DDA}$ POR/PDR Int ◀  $V_{SSA}$ NVIC @ V<sub>DDA</sub> V<sub>DD</sub> Bus HSI14 RC 14 MHz PVD HSI RC 8 MHz @ V<sub>DDA</sub> PLLCLK @ V<sub>DD</sub> LSI GP DMA RC 40 kHz XTAL OSC OSC\_IN 12 channels HSI48 4-32 MHz RC 48MHz Ind. Window WDG PA[15:0] GPIO port A RESET & CLOCK ₹. CONTROL V<sub>BAT</sub> = 1.65 to 3.6 V PB[15:0] GPIO port B OSC32\_IN OSC32\_OUT PC[15:0] GPIO port C System and peripheral XTAL32 kHz clocks PD[15:0] GPIO port D 3 TAMPER-RTC RTC AHB reg (ALARM OUT) PE[15:0] GPIO port E RTC interface PF[10:9], PF6 PF[3:0] Щ GPIO port F CRS SYNC 4 channels 3 compl. channels BRK, ETR input as AF PWM TIMER 1 CRC PAD 8 groups of 4 channels 4 ch., ETR as AF TIMER 2 32-bit Sensing Controller switches AHB TIMER 3 4 ch., ETR as AF SYNC APR TIMER 14 1 channel as AF EXT. IT WKUP 88 AF [ 2 channels 1 compl, BRK as AF TIMER 15 SRAM 1 channel 1 compl, BRK as AF 256 B TIMER 16 į į 1 channel 1 compl, BRK as AF IR\_OUT as AF TIMER 17 TX, RX as AF **BxCAN** Window WDG RX, TX,CTS, RTS, CK as AF USART1 MOSI/SD SPI1/I2S1 MISO/MCK SCK/CK NSS/WS as AF RX, TX,CTS, RTS, CK as AF USART2 DBGMCU RX, TX,CTS, RTS, CK as AF USART3 MOSI/SD SPI2/I2S2 RX, TX,CTS, RTS, CK as AF USART4 SCK/CK NSS/WS as AF SYSCFG IF USART5 RX, TX, RTS, CK as AF USART6 RX, TX, RTS, CK as AF INPUT + GP comparator 1 USART7 RX, TX, RTS, CK as AF OUTPUT GP comparator 2 USART8 RX, TX, RTS, CK as AF as AF @ V<sub>DDA</sub> SCL, SDA, SMBA (20 mA FM+) as AF I2C1 Temp. SCL, SDA (20 mA FM+) as AF I2C2 16x AD input IF 12-bit ADC CEC as AF HDMI-CEC TIMER 6 12-bit DAC ►DAC OUT1  $V_{DDA}$   $V_{SSA}$ TIMER 7 @ V<sub>DDA</sub> 12-bit DAC ► DAC\_OUT2 @ V<sub>DDA</sub> Power domain of analog blocks: V<sub>BAT</sub>  $V_{DD}$ V<sub>DDA</sub> MSv34957V2

Figure 1. Block diagram

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

# 3.20 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.21 Clock recovery system (CRS)

The STM32F091xB/xC embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.22 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

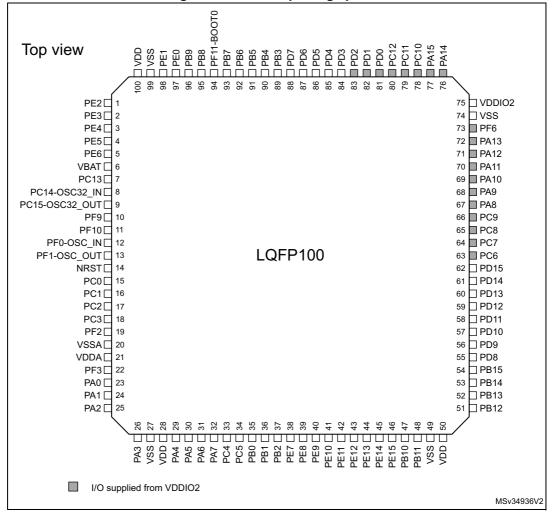

Figure 4. LQFP100 package pinout

Table 13. STM32F091xB/xC pin definitions (continued)

|          | Pi      | n nui   | mber   | s       |                 |                                      |          |               |       | Pin function                                                                     | ns                                                 |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------|----------------------------------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                              | Additional<br>functions                            |

| J1       | 19      | -       | -      | -       | -               | PF2                                  | I/O      | FT            |       | EVENTOUT,<br>USART7_TX,<br>USART7_CK_RTS                                         | WKUP8                                              |

| K1       | 20      | F1      | 12     | G8      | 8               | VSSA                                 | S        | -             |       | Analog grou                                                                      | nd                                                 |

| M1       | 21      | H1      | 13     | Н8      | 9               | VDDA                                 | S        | ı             |       | Analog power s                                                                   | upply                                              |

| L1       | 22      | -       | -      | -       | -               | PF3                                  | I/O      | FT            |       | EVENTOUT,<br>USART7_RX,<br>USART6_CK_RTS                                         |                                                    |

| L2       | 23      | G2      | 14     | F7      | 10              | PA0                                  | I/O      | ТТа           |       | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX<br>COMP1_OUT            | RTC_TAMP2,<br>WKUP1,<br>ADC_IN0,<br>COMP1_INM6     |

| M2       | 24      | H2      | 15     | F6      | 11              | PA1                                  | I/O      | ТТа           |       | USART2_RTS,<br>TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX,<br>EVENTOUT | ADC_IN1,<br>COMP1_INP                              |

| K3       | 25      | F3      | 16     | E5      | 12              | PA2                                  | I/O      | ТТа           |       | USART2_TX, TIM2_CH3,<br>TIM15_CH1,<br>TSC_G1_IO3<br>COMP2_OUT                    | ADC_IN2,<br>WKUP4,<br>COMP2_INM6                   |

| L3       | 26      | G3      | 17     | H7      | 13              | PA3                                  | I/O      | TTa           |       | USART2_RX,TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4                                  | ADC_IN3,<br>COMP2_INP                              |

| D3       | 27      | C2      | 18     | G7      | -               | VSS                                  | S        | -             |       | Ground                                                                           |                                                    |

| Н3       | 28      | D2      | 19     | G6      | -               | VDD                                  | S        | -             |       | Digital power s                                                                  | upply                                              |

| М3       | 29      | Н3      | 20     | H6      | 14              | PA4                                  | I/O      | ТТа           |       | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK,<br>USART6_TX       | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |

| K4       | 30      | F4      | 21     | F5      | 15              | PA5                                  | I/O      | ТТа           |       | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2,<br>USART6_RX          | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |

Table 13. STM32F091xB/xC pin definitions (continued)

|          | Pi      | n nui   | mber   | s       |                 |                                      |          |               |       | Pin function                                                                                                       | ıs                      |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional<br>functions |

| L4       | 31      | G4      | 22     | G5      | 16              | PA6                                  | I/O      | ТТа           |       | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>COMP1_OUT,<br>TSC_G2_IO3,<br>EVENTOUT,<br>USART3_CTS | ADC_IN6                 |

| M4       | 32      | H4      | 23     | E4      | 17              | PA7                                  | I/O      | ТТа           |       | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N, TIM17_CH1,<br>COMP2_OUT,<br>TSC_G2_IO4,<br>EVENTOUT      | ADC_IN7                 |

| K5       | 33      | H5      | 24     | H5      | -               | PC4                                  | I/O      | TTa           |       | EVENTOUT, USART3_TX                                                                                                | ADC_IN14                |

| L5       | 34      | H6      | 25     | F4      | -               | PC5                                  | I/O      | TTa           |       | TSC_G3_IO1,<br>USART3_RX                                                                                           | ADC_IN15,<br>WKUP5      |

| M5       | 35      | F5      | 26     | G4      | 18              | PB0                                  | I/O      | ТТа           |       | TIM3_CH3, TIM1_CH2N,<br>TSC_G3_IO2,<br>EVENTOUT,<br>USART3_CK                                                      | ADC_IN8                 |

| M6       | 36      | G5      | 27     | F3      | 19              | PB1                                  | I/O      | ТТа           |       | TIM3_CH4,<br>USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                                                    | ADC_IN9                 |

| L6       | 37      | G6      | 28     | H4      | 20              | PB2                                  | I/O      | FT            |       | TSC_G3_IO4                                                                                                         | -                       |

| M7       | 38      | -       | -      | -       | -               | PE7                                  | I/O      | FT            |       | TIM1_ETR,<br>USART5_CK_RTS                                                                                         | -                       |

| L7       | 39      | -       | -      | -       | -               | PE8                                  | I/O      | FT            |       | TIM1_CH1N,<br>USART4_TX                                                                                            | -                       |

| M8       | 40      | -       | -      | -       | -               | PE9                                  | I/O      | FT            |       | TIM1_CH1, USART4_RX                                                                                                | <u>-</u>                |

| L8       | 41      | -       | -      | -       | -               | PE10                                 | I/O      | FT            |       | TIM1_CH2N,<br>USART5_TX                                                                                            | -                       |

| M9       | 42      | -       | -      | -       | -               | PE11                                 | I/O      | FT            |       | TIM1_CH2, USART5_RX                                                                                                | -                       |

| L9       | 43      | -       | -      | -       | -               | PE12                                 | I/O      | FT            |       | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                                                                    | -                       |

| M10      | 44      | -       | -      | -       | -               | PE13                                 | I/O      | FT            |       | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                                                                     | -                       |

### 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  =  $V_{DDA}$  = 3.3 V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

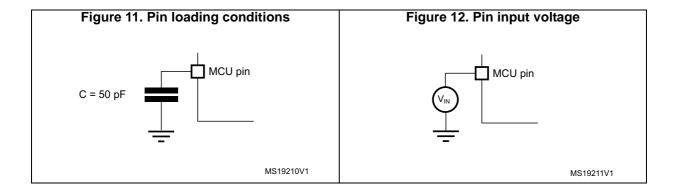

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 12.

Table 25. Operating conditions at power-up / power-down

| Symbol            | Parameter                       | Conditions | Min | Max | Unit  |

|-------------------|---------------------------------|------------|-----|-----|-------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate  |            | 0   | ∞   |       |

|                   | V <sub>DD</sub> fall time rate  | -          | 20  | ∞   | μs/V  |

| +                 | V <sub>DDA</sub> rise time rate |            | 0   | ∞   | μ5/ ν |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -          | 20  | ∞   |       |

## 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

Table 26. Embedded reset and power control block characteristics

| Symbol                               | Parameter           | Conditions                  | Min                 | Тур  | Max                 | Unit |

|--------------------------------------|---------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  |                     | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | ٧    |

| YPOR/PDR                             | reset threshold     | Rising edge                 | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis      | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization | -                           | 1.50                | 2.50 | 4.50                | ms   |

The PDR detector monitors V<sub>DD</sub> and also V<sub>DDA</sub> (if kept enabled in the option bytes). The POR detector monitors only V<sub>DD</sub>.

Table 27. Programmable voltage detector characteristics

| Symbol            | Parameter          | Conditions   | Min  | Тур  | Max                                                                                  | Unit |

|-------------------|--------------------|--------------|------|------|--------------------------------------------------------------------------------------|------|

| V                 | PVD threshold 0    | Rising edge  | 2.1  | 2.18 | 2.26<br>2.16<br>2.37<br>2.27<br>2.48<br>2.38<br>2.58<br>2.48<br>2.69<br>2.59<br>2.79 | V    |

|                   | Falling edge       | 2            | 2.08 | 2.16 | V                                                                                    |      |

| V                 | PVD threshold 1    | Rising edge  | 2.19 | 2.28 | 2.37                                                                                 | V    |

| V <sub>PVD1</sub> | F VD tillesiloid i | Falling edge | 2.09 | 2.18 | 2.27                                                                                 | V    |

| V                 | PVD threshold 2    | Rising edge  | 2.28 | 2.38 | 2.26<br>2.16<br>2.37<br>2.27<br>2.48<br>2.38<br>2.58<br>2.48<br>2.69<br>2.59         | V    |

| V <sub>PVD2</sub> | FVD (IIIeSHold 2   | Falling edge | 2.18 | 2.28 | 2.38                                                                                 | V    |

| V                 | PVD threshold 3    | Rising edge  | 2.38 | 2.48 | 2.58                                                                                 | V    |

| V <sub>PVD3</sub> | F VD tilleshold 3  | Falling edge | 2.28 | 2.38 | 2.48                                                                                 | V    |

| V                 | PVD threshold 4    | Rising edge  | 2.47 | 2.58 | 2.69                                                                                 | V    |

| V <sub>PVD4</sub> | FVD tilleshold 4   | Falling edge | 2.37 | 2.48 | 2.59                                                                                 | V    |

| V                 | PVD threshold 5    | Rising edge  | 2.57 | 2.68 | 2.79                                                                                 | V    |

| V <sub>PVD5</sub> | F AD HIRESHOID 3   | Falling edge | 2.47 | 2.58 | 2.26<br>2.16<br>2.37<br>2.27<br>2.48<br>2.38<br>2.58<br>2.48<br>2.69<br>2.59<br>2.79 | V    |

<sup>2.</sup> The product behavior is guaranteed by design down to the minimum  $V_{POR/PDR}$  value.

<sup>3.</sup> Data based on characterization results, not tested in production.

<sup>4.</sup> Guaranteed by design, not tested in production.

| Symbol                              | Parameter               | Conditions   | Min  | Тур  | Max                 | Unit |

|-------------------------------------|-------------------------|--------------|------|------|---------------------|------|

| V                                   | PVD threshold 6         | Rising edge  | 2.66 | 2.78 | 2.9                 | V    |

| V <sub>PVD6</sub>                   | VD6 PVD threshold 6     |              | 2.56 | 2.68 | 2.8                 | V    |

| V                                   | PVD threshold 7         | Rising edge  | 2.76 | 2.88 | 2.9                 | V    |

| V <sub>PVD7</sub>                   | PVD tillesiloid 7       | Falling edge | 2.66 | 2.78 | 2.9                 | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis          | -            | -    | 100  | -                   | mV   |

| I <sub>DD(PVD)</sub>                | PVD current consumption | -            | -    | 0.15 | 0.26 <sup>(1)</sup> | μA   |

Table 27. Programmable voltage detector characteristics (continued)

#### 6.3.4 Embedded reference voltage

The parameters given in *Table 28* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                 | Parameter                                                     | Conditions                        | Min                  | Тур  | Max                | Unit   |

|------------------------|---------------------------------------------------------------|-----------------------------------|----------------------|------|--------------------|--------|

| $V_{REFINT}$           | Internal reference voltage                                    | -40 °C < T <sub>A</sub> < +105 °C | 1.2                  | 1.23 | 1.25               | V      |

| t <sub>START</sub>     | ADC_IN17 buffer startup time                                  | -                                 | -                    | -    | 10 <sup>(1)</sup>  | μs     |

| t <sub>S_vrefint</sub> | ADC sampling time when reading the internal reference voltage | -                                 | 4 <sup>(1)</sup>     | -    | -                  | μs     |

| $\Delta V_{REFINT}$    | Internal reference voltage spread over the temperature range  | V <sub>DDA</sub> = 3 V            | -                    | -    | 10 <sup>(1)</sup>  | mV     |

| T <sub>Coeff</sub>     | Temperature coefficient                                       | -                                 | - 100 <sup>(1)</sup> | -    | 100 <sup>(1)</sup> | ppm/°C |

Table 28. Embedded internal reference voltage

#### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>1.</sup> Guaranteed by design, not tested in production.

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\text{SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

Table 34. Switching output I/O current consumption

| Symbol          | Parameter               | Conditions <sup>(1)</sup>                                                             | I/O toggling frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|-------------------------|---------------------------------------------------------------------------------------|-------------------------------------------|-------|------|

|                 |                         |                                                                                       | 4 MHz                                     | 0.07  |      |

|                 |                         | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                     | 0.15  |      |

|                 |                         | C =C <sub>INT</sub>                                                                   | 16 MHz                                    | 0.31  |      |

|                 |                         |                                                                                       | 24 MHz                                    | 0.53  |      |

|                 |                         |                                                                                       | 48 MHz                                    | 0.92  |      |

|                 |                         |                                                                                       | 4 MHz                                     | 0.18  |      |

|                 |                         | V <sub>DDIOx</sub> = 3.3 V                                                            | 8 MHz                                     | 0.37  |      |

|                 |                         | $C_{EXT} = 0 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$                              | 16 MHz                                    | 0.76  |      |

|                 |                         |                                                                                       | 24 MHz                                    | 1.39  |      |

|                 |                         |                                                                                       | 48 MHz                                    | 2.188 |      |

|                 |                         |                                                                                       | 4 MHz                                     | 0.32  |      |

|                 | I/O current consumption | $V_{DDIOx} = 3.3 \text{ V}$ $C_{EXT} = 10 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$ | 8 MHz                                     | 0.64  | . mA |

|                 |                         |                                                                                       | 16 MHz                                    | 1.25  |      |

|                 |                         |                                                                                       | 24 MHz                                    | 2.23  |      |

| I <sub>SW</sub> |                         |                                                                                       | 48 MHz                                    | 4.442 |      |

| 'SW             |                         |                                                                                       | 4 MHz                                     | 0.49  |      |

|                 |                         | $V_{DDIOX} = 3.3 V$ $C_{EXT} = 22 pF$ $C = C_{INT} + C_{EXT} + C_{S}$                 | 8 MHz                                     | 0.94  |      |

|                 |                         |                                                                                       | 16 MHz                                    | 2.38  |      |

|                 |                         | INT - EXT - 3                                                                         | 24 MHz                                    | 3.99  |      |

|                 |                         |                                                                                       | 4 MHz                                     | 0.64  |      |

|                 |                         | $V_{DDIOx} = 3.3 \text{ V}$                                                           | 8 MHz                                     | 1.25  |      |

|                 |                         | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$                          | 16 MHz                                    | 3.24  |      |

|                 |                         | INT - EXT - 3                                                                         | 24 MHz                                    | 5.02  |      |

|                 |                         | V <sub>DDIOx</sub> = 3.3 V                                                            | 4 MHz                                     | 0.81  |      |

|                 |                         | C <sub>EXT</sub> = 47 pF                                                              | 8 MHz                                     | 1.7   |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$ $C = C_{int}$                                         | 16 MHz                                    | 3.67  |      |

|                 |                         | V <sub>DDIOx</sub> = 2.4 V                                                            | 4 MHz                                     | 0.66  |      |

|                 |                         | $C_{EXT} = 47 \text{ pF}$                                                             | 8 MHz                                     | 1.43  |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$                                                       | 16 MHz                                    | 2.45  |      |

|                 |                         | C = C <sub>int</sub>                                                                  | 24 MHz                                    | 4.97  |      |

<sup>1.</sup>  $C_S = 7 pF$  (estimated value).

| Symbol           | Parameter      | Conditions                                         | Min <sup>(1)</sup> | Unit   |

|------------------|----------------|----------------------------------------------------|--------------------|--------|

| N <sub>END</sub> | Endurance      | $T_A = -40 \text{ to } +105 ^{\circ}\text{C}$      | 10                 | kcycle |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C  | 30                 |        |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                 | Year   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C | 20                 |        |

Table 47. Flash memory endurance and data retention

- 1. Data based on characterization results, not tested in production.

- 2. Cycling performed over the whole temperature range.

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 48*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                  | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 3.3 V, LQFP100, $T_A$ = +25 °C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, $T_A$ = +25°C, $f_{HCLK}$ = 48 MHz, conforming to IEC 61000-4-4  | 4B              |

**Table 48. EMS characteristics**

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

| Symbol                | Ratings                                            | Conditions                                                  | Packages            | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------|---------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> = +25 °C, conforming to JESD22-A114          | All                 | 2     | 2000                            | V    |

|                       |                                                    | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | WLCSP64,<br>LQFP100 | C3    | 250                             | V    |

| - (0)                 | (charge device model)                              | IU ANSI/ESD STIVIS.S.T                                      | All others          | C4    | 500                             |      |

Table 50. ESD absolute maximum ratings

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 51. Electrical sensitivities

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | II level A |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{\rm SS}$  or above  $V_{\rm DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in *Table 52*.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

<sup>1.</sup> Data based on characterization results, not tested in production.

Table 61. Comparator characteristics (continued)

| Symbol           | Parameter             | Condition                                | Min <sup>(1)</sup>    | Тур | Max <sup>(1)</sup> | Unit |    |

|------------------|-----------------------|------------------------------------------|-----------------------|-----|--------------------|------|----|

|                  | Comparator hysteresis | No hysteresis (COMPxHYST[1:0]=00)        | -                     | -   | 0                  | -    |    |

|                  |                       | Low hysteresis                           | High speed mode       | 3   |                    | 13   | mV |

|                  |                       | (COMPxHYST[1:0]=01)                      | All other power modes | 5   | 8                  | 10   |    |

| V <sub>hys</sub> |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7   | 15                 | 26   |    |

|                  |                       |                                          | All other power modes | 9   |                    | 19   |    |

|                  |                       | Lligh hystorogia                         | High speed mode       | 18  |                    | 49   |    |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | All other power modes | 19  | 31                 | 40   |    |

<sup>1.</sup> Data based on characterization results, not tested in production.

inches<sup>(1)</sup> millimeters Symbol Min. Тур. Max. Min. Тур. Max. 0.240 0.290 0.340 0.0094 0.0114 0.0134 b D 6.850 7.000 7.150 0.2697 0.2756 0.2815 5.500 0.2165 D1 Ε 0.2697 6.850 7.000 7.150 0.2756 0.2815 E1 5.500 0.2165 е 0.500 0.0197 Ζ 0.750 0.0295 ddd 0.080 0.0031 eee 0.150 0.0059 fff 0.050 0.0020

Table 70. UFBGA100 package mechanical data (continued)

000

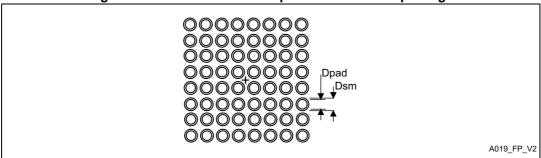

Figure 34. Recommended footprint for UFBGA100 package

Table 71. UFBGA100 recommended PCB design rules

| Dimension         | Recommended values                                                |  |  |

|-------------------|-------------------------------------------------------------------|--|--|

| Pitch             | 0.5                                                               |  |  |

| Dpad              | 0.280 mm                                                          |  |  |

| Dsm               | 0.370 mm typ. (depends on the solder mask registration tolerance) |  |  |

| Stencil opening   | 0.280 mm                                                          |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                     |  |  |

A0C2\_FP\_V1

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

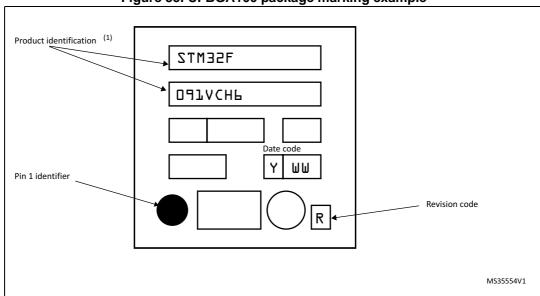

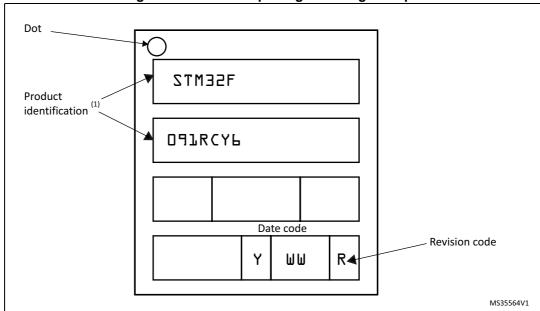

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 35. UFBGA100 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

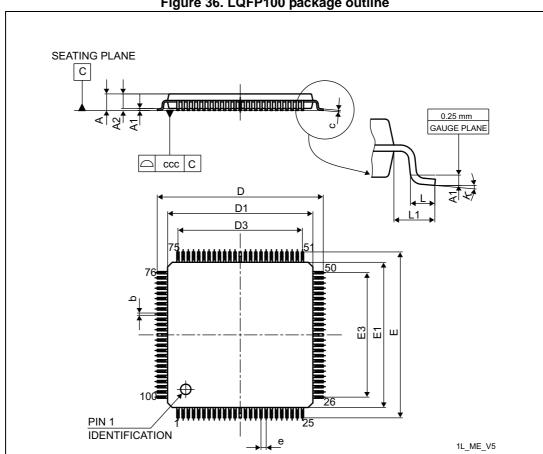

#### 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

Figure 36. LQFP100 package outline

1. Drawing is not to scale.

Table 72. LQPF100 package mechanical data

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Max    | Min                   | Тур    | Max    |

| Α      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

Table 73. UFBGA64 package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 40. Recommended footprint for UFBGA64 package

Table 74. UFBGA64 recommended PCB design rules

| Dimension         | Recommended values                                               |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Pitch             | 0.5                                                              |  |  |

| Dpad              | 0.280 mm                                                         |  |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.280 mm                                                         |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |  |

| Pad trace width   | 0.100 mm                                                         |  |  |

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 44. WLCSP64 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 47. LQFP64 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

Table 78. LQFP48 package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| Α      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| ccc    | -           | -     | 0.080 | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

9.70 5.80 7.30 0.20 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0.30 1.20 0

1. Dimensions are expressed in millimeters.