Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 128                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 40K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3744gj-gae-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1 | 0 | 11 | ١.  |

|---|---|----|-----|

|   | J | /4 | • ) |

| Pin Name | Pin No. | I/O | Function                                      | Alternate Function                                                                                       |                |  |  |

|----------|---------|-----|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|--|--|

| P90      | 61      | I/O | Port 9                                        | A0/KR6/TXDA1/SDA02                                                                                       |                |  |  |

| P91      | 62      |     | 16-bit I/O port                               | A1/KR7/RXDA1/SCL02                                                                                       |                |  |  |

| P92      | 63      |     |                                               | Input/output can be specified in 1-bit units.<br>N-ch open-drain output can be specified in 1-bit units. | A2/TIP41/TOP41 |  |  |

| P93      | 64      |     | 5 V tolerant.                                 | A3/TIP40/TOP40                                                                                           |                |  |  |

| P94      | 65      |     |                                               | A4/TIP31/TOP31                                                                                           |                |  |  |

| P95      | 66      |     |                                               | A5/TIP30/TOP30                                                                                           |                |  |  |

| P96      | 67      |     |                                               | A6/TIP21/TOP21                                                                                           |                |  |  |

| P97      | 68      |     |                                               | A7/SIB1/TIP20/TOP20                                                                                      |                |  |  |

| P98      | 69      |     |                                               | A8/SOB1                                                                                                  |                |  |  |

| P99      | 70      |     |                                               | A9/SCKB1                                                                                                 |                |  |  |

| P910     | 71      |     |                                               | A10/SIB3                                                                                                 |                |  |  |

| P911     | 72      |     |                                               | A11/SOB3                                                                                                 |                |  |  |

| P912     | 73      |     |                                               | A12/SCKB3                                                                                                |                |  |  |

| P913     | 74      |     |                                               | A13/INTP4                                                                                                |                |  |  |

| P914     | 75      |     |                                               | A14/INTP5/TIP51/TOP51                                                                                    |                |  |  |

| P915     | 76      |     |                                               | A15/INTP6/TIP50/TOP50                                                                                    |                |  |  |

| PCD0     | 77      | I/O | Port CD                                       | -                                                                                                        |                |  |  |

| PCD1     | 78      |     | 4-bit I/O port                                | -                                                                                                        |                |  |  |

| PCD2     | 79      |     | Input/output can be specified in 1-bit units. | -                                                                                                        |                |  |  |

| PCD3     | 80      |     |                                               | -                                                                                                        |                |  |  |

| PCM0     | 85      | I/O | Port CM                                       | WAIT                                                                                                     |                |  |  |

| PCM1     | 86      |     | 6-bit I/O port                                | CLKOUT                                                                                                   |                |  |  |

| PCM2     | 87      |     | Input/output can be specified in 1-bit units. | HLDAK                                                                                                    |                |  |  |

| PCM3     | 88      |     |                                               | HLDRQ                                                                                                    |                |  |  |

| PCM4     | 89      |     |                                               | -                                                                                                        |                |  |  |

| PCM5     | 90      |     |                                               | -                                                                                                        |                |  |  |

| PCS0     | 81      | I/O | Port CS                                       | CSO                                                                                                      |                |  |  |

| PCS1     | 82      |     | 8-bit I/O port                                | CS1                                                                                                      |                |  |  |

| PCS2     | 83      |     | Input/output can be specified in 1-bit units. | CS2                                                                                                      |                |  |  |

| PCS3     | 84      |     |                                               | CS3                                                                                                      |                |  |  |

| PCS4     | 91      |     |                                               | _                                                                                                        |                |  |  |

| PCS5     | 92      |     |                                               | -                                                                                                        |                |  |  |

| PCS6     | 93      | ]   |                                               | _                                                                                                        |                |  |  |

| PCS7     | 94      |     |                                               | -                                                                                                        |                |  |  |

| Address   | Function Register Name            | Symbol   | R/W | Manir  | oulatab      | le Bits | (2/12)<br>Default Value |

|-----------|-----------------------------------|----------|-----|--------|--------------|---------|-------------------------|

|           |                                   | 0,       |     | 1      | 8            | 16      |                         |

| FFFFF0C2H | DMA transfer count register 1     | DBC1     | R/W |        | -            | √       | Undefined               |

| FFFFF0C4H | DMA transfer count register 2     | DBC2     | -   |        |              | √       | Undefined               |

| FFFFF0C6H | DMA transfer count register 3     | DBC3     |     |        |              | 1       | Undefined               |

| FFFFF0D0H | DMA addressing control register 0 | DADC0    |     | -      |              | 1       | 0000H                   |

| FFFF0D2H  | DMA addressing control register 1 | DADC1    |     |        |              | V       | 0000H                   |

| FFFFF0D4H | DMA addressing control register 2 | DADC2    |     |        |              |         | 0000H                   |

| FFFF0D6H  | DMA addressing control register 3 | DADC3    |     |        |              |         | 0000H                   |

| FFFF0E0H  | DMA channel control register 0    | DCHC0    |     |        |              |         | 00H                     |

| FFFF0E2H  | DMA channel control register 1    | DCHC1    |     |        | V            |         | 00H                     |

| FFFF0E4H  | DMA channel control register 2    | DCHC2    |     |        |              |         | 00H                     |

| FFFF0E6H  | DMA channel control register 3    | DCHC3    |     |        | V            |         | 00H                     |

| FFFFF100H | Interrupt mask register 0         | IMR0     |     | ,<br>  |              |         | FFFFH                   |

| FFFFF100H | Interrupt mask register 0L        | IMROL    |     |        | V            |         | FFH                     |

| FFFFF101H | Interrupt mask register 0H        | IMROH    | _   | 1      | √<br>        |         | FFH                     |

| FFFFF102H | Interrupt mask register 1         | IMR1     |     | ,<br>  |              |         | FFFFH                   |

| FFFFF102H | Interrupt mask register 1L        | IMR1L    | _   |        |              |         | FFH                     |

| FFFFF103H | Interrupt mask register 1H        | IMR1H    |     |        |              |         | FFH                     |

| FFFFF104H | Interrupt mask register 2         | IMR2     |     | ,<br>  |              |         | FFFFH                   |

| FFFFF104H | Interrupt mask register 2L        | IMR2L    |     |        |              |         | FFH                     |

| FFFFF105H | Interrupt mask register 2H        | IMR2H    |     |        | V            |         | FFH                     |

| FFFFF106H | Interrupt mask register 3         | IMR3     |     | ,<br>  |              |         | FFFFH                   |

| FFFFF106H | Interrupt mask register 3L        | IMR3L    | _   |        |              | ,       | FFH                     |

| FFFFF107H | Interrupt mask register 3H        | IMR3H    | _   | 1      | V            |         | FFH                     |

| FFFFF108H | Interrupt mask register 4         | IMR4     | _   | ,<br>, |              | V       | FFFFH                   |

| FFFFF108H | Interrupt mask register 4L        | IMR4L    |     |        | V            |         | FFH                     |

| FFFFF109H | Interrupt mask register 4H        | IMR4H    |     |        |              |         | FFH                     |

| FFFFF110H | Interrupt control register        | LVIIC    |     |        |              |         | 47H                     |

| FFFFF112H | Interrupt control register        | PIC0     |     |        | 1            |         | 47H                     |

| FFFFF114H | Interrupt control register        | PIC1     |     |        |              |         | 47H                     |

| FFFFF116H | Interrupt control register        | PIC2     |     |        |              |         | 47H                     |

| FFFFF118H | Interrupt control register        | PIC3     |     |        |              |         | 47H                     |

| FFFFF11AH | Interrupt control register        | PIC4     |     |        |              |         | 47H                     |

| FFFFF11CH | Interrupt control register        | PIC5     |     |        |              |         | 47H                     |

| FFFFF11EH | Interrupt control register        | PIC6     | _   |        |              |         | 47H                     |

| FFFFF120H | Interrupt control register        | PIC7     | _   |        |              |         | 47H                     |

| FFFFF122H | Interrupt control register        | TQ0OVIC  | 1   |        |              |         | 47H                     |

| FFFFF124H | Interrupt control register        | TQ0CCIC0 | 1   |        | $\checkmark$ |         | 47H                     |

| FFFFF126H | Interrupt control register        | TQ0CCIC1 | 1   |        | $\checkmark$ |         | 47H                     |

| FFFFF128H | Interrupt control register        | TQ0CCIC2 | 1   |        |              |         | 47H                     |

| FFFFF12AH | Interrupt control register        | TQ0CCIC3 | 1   |        | $\checkmark$ |         | 47H                     |

| FFFFF12CH | Interrupt control register        | TP0OVIC  | 1   |        |              |         | 47H                     |

| FFFFF12EH | Interrupt control register        | TPOCCICO | 1   | √      | √            |         | 47H                     |

| FFFFF130H | Interrupt control register        | TP0CCIC1 | -   | √      | 1            |         | 47H                     |

|           |                                   |         |     |                    |              |              | (8/12)        |

|-----------|-----------------------------------|---------|-----|--------------------|--------------|--------------|---------------|

| Address   | Function Register Name            | Symbol  | R/W | Manipulatable Bits |              |              | Default Value |

|           |                                   |         |     | 1                  | 8            | 16           |               |

| FFFF5C5H  | TMP3 option register 0            | TP3OPT0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5C6H  | TMP3 capture/compare register 0   | TP3CCR0 | 1   |                    |              |              | 0000H         |

| FFFF5C8H  | TMP3 capture/compare register 1   | TP3CCR1 |     |                    |              | $\checkmark$ | 0000H         |

| FFFF5CAH  | TMP3 counter read buffer register | TP3CNT  | R   |                    |              | $\checkmark$ | 0000H         |

| FFFF5D0H  | TMP4 control register 0           | TP4CTL0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF5D1H | TMP4 control register 1           | TP4CTL1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5D2H  | TMP4 I/O control register 0       | TP4IOC0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5D3H  | TMP4 I/O control register 1       | TP4IOC1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5D4H  | TMP4 I/O control register 2       | TP4IOC2 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5D5H  | TMP4 option register 0            | TP4OPT0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5D6H  | TMP4 capture/compare register 0   | TP4CCR0 | 1   |                    |              | $\checkmark$ | 0000H         |

| FFFF5D8H  | TMP4 capture/compare register 1   | TP4CCR1 | 1   |                    |              | $\checkmark$ | 0000H         |

| FFFF5DAH  | TMP4 counter read buffer register | TP4CNT  | R   |                    |              | $\checkmark$ | 0000H         |

| FFFF5E0H  | TMP5 control register 0           | TP5CTL0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E1H  | TMP5 control register 1           | TP5CTL1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E2H  | TMP5 I/O control register 0       | TP5IOC0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E3H  | TMP5 I/O control register 1       | TP5IOC1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E4H  | TMP5 I/O control register 2       | TP5IOC2 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E5H  | TMP5 option register 0            | TP5OPT0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5E6H  | TMP5 capture/compare register 0   | TP5CCR0 | 1   |                    |              |              | 0000H         |

| FFFF5E8H  | TMP5 capture/compare register 1   | TP5CCR1 | 1   |                    |              |              | 0000H         |

| FFFF5EAH  | TMP5 counter read buffer register | TP5CNT  | R   |                    |              | $\checkmark$ | 0000H         |

| FFFF5F0H  | TMP6 control register 0           | TP6CTL0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F1H  | TMP6 control register 1           | TP6CTL1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F2H  | TMP6 I/O control register 0       | TP6IOC0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F3H  | TMP6 I/O control register 1       | TP6IOC1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F4H  | TMP6 I/O control register 2       | TP6IOC2 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F5H  | TMP6 option register 0            | TP6OPT0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF5F6H  | TMP6 capture/compare register 0   | TP6CCR0 | 1   |                    |              | $\checkmark$ | 0000H         |

| FFFF5F8H  | TMP6 capture/compare register 1   | TP6CCR1 | 1   |                    |              | $\checkmark$ | 0000H         |

| FFFF5FAH  | TMP6 counter read buffer register | TP6CNT  | R   |                    |              | $\checkmark$ | 0000H         |

| FFFF600H  | TMP7 control register 0           | TP7CTL0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF601H | TMP7 control register 1           | TP7CTL1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF602H  | TMP7 I/O control register 0       | TP7IOC0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF603H | TMP7 I/O control register 1       | TP7IOC1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFF604H  | TMP7 I/O control register 2       | TP7IOC2 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF605H | TMP7 option register 0            | TP7OPT0 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF606H | TMP7 capture/compare register 0   | TP7CCR0 | 1   |                    |              | $\checkmark$ | 0000H         |

| FFFFF608H | TMP7 capture/compare register 1   | TP7CCR1 | 1   |                    |              |              | 0000H         |

| FFFF60AH  | TMP7 counter read buffer register | TP7CNT  | R   |                    |              | $\checkmark$ | 0000H         |

| FFFFF610H | TMP8 control register 0           | TP8CTL0 | R/W | $\checkmark$       | $\checkmark$ |              | 00H           |

| FFFFF611H | TMP8 control register 1           | TP8CTL1 | 1   | $\checkmark$       | $\checkmark$ |              | 00H           |

## **CHAPTER 4 PORT FUNCTIONS**

## 4.1 Features

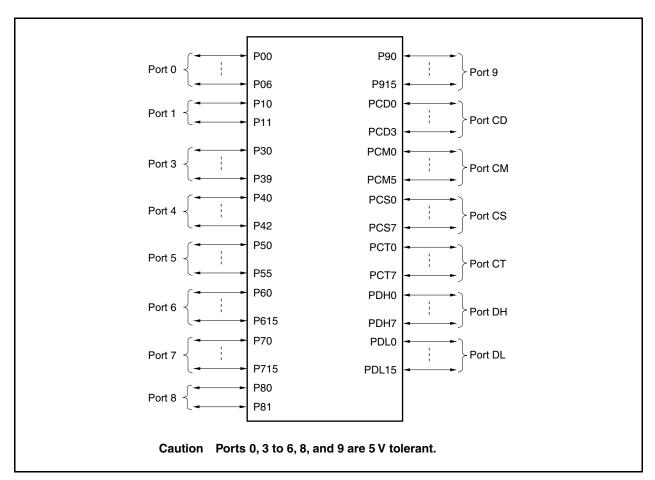

- I/O ports: 128

- 5 V tolerant/N-ch open-drain output switchable: 60 (ports 0, 3 to 6, 8, 9)

- $\bigcirc$  Input/output specifiable in 1-bit units

## 4.2 Basic Port Configuration

The V850ES/JJ3 features a total of 128 I/O ports consisting of ports 0, 1, 3 to 9, CD, CM, CS, CT, DH, and DL. The port configuration is shown below.

## Figure 4-1. Port Configuration Diagram

| Power Supply       | Corresponding Pins                                   |

|--------------------|------------------------------------------------------|

| AV <sub>REF0</sub> | Port 7                                               |

| AV <sub>REF1</sub> | Port 1                                               |

| EVDD               | RESET, ports 0, 3 to 6, 8, 9, CD, CM, CS, CT, DH, DL |

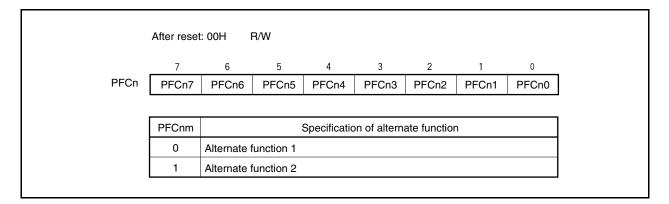

## (4) Port n function control register (PFCn)

The PFCn register specifies the alternate function of a port pin to be used if the pin has two alternate functions. Each bit of this register corresponds to one pin of port n, and the alternate function of a port pin can be specified in 1-bit units.

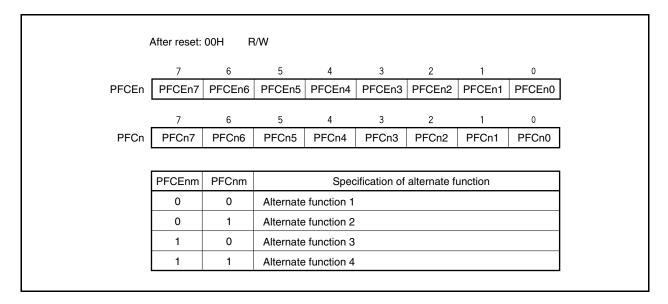

## (5) Port n function control expansion register (PFCEn)

The PFCEn register specifies the alternate function of a port pin to be used if the pin has three or more alternate functions.

Each bit of this register corresponds to one pin of port n, and the alternate function of a port pin can be specified in 1-bit units.

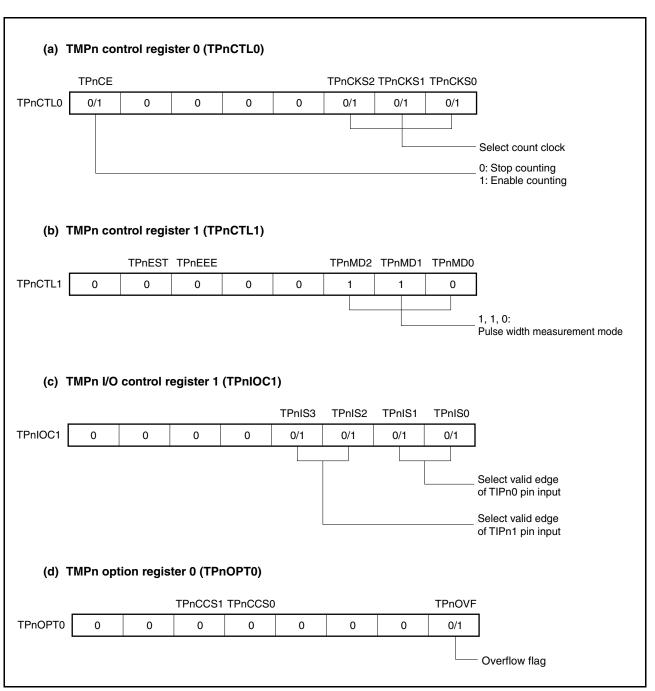

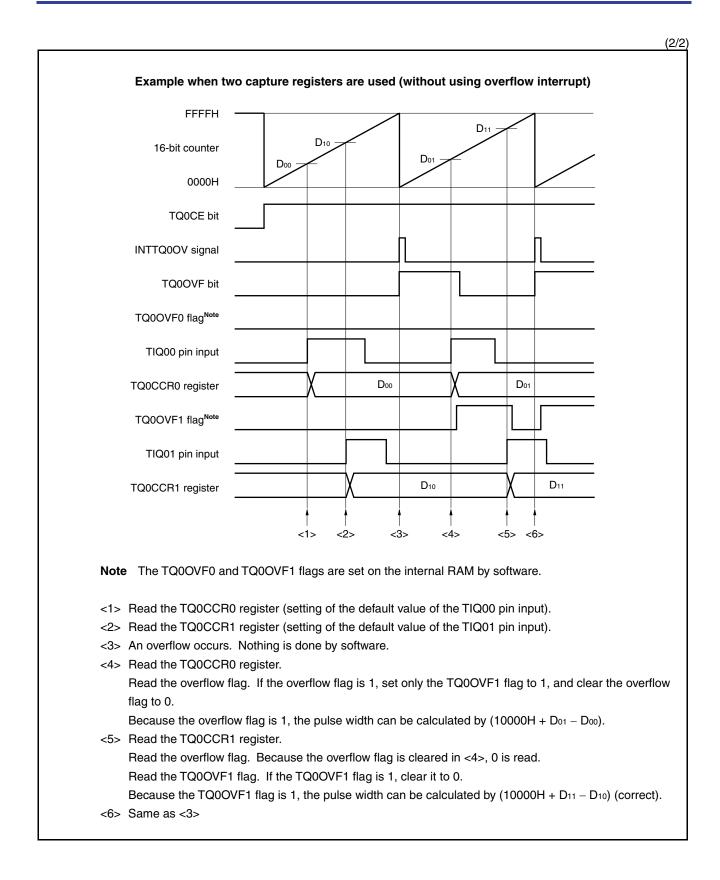

#### Figure 7-36. Register Setting in Pulse Width Measurement Mode (1/2)

#### 7.5.8 Timer output operations

The following table shows the operations and output levels of the TOPn0 and TOPn1 pins.

| Operation Mode                     | TOPn1 Pin                         | TOPn0 Pin               |

|------------------------------------|-----------------------------------|-------------------------|

| Interval timer mode                | Square wave output                |                         |

| External event count mode          | Square wave output                | -                       |

| External trigger pulse output mode | External trigger pulse output     | Square wave output      |

| One-shot pulse output mode         | One-shot pulse output             |                         |

| PWM output mode                    | PWM output                        |                         |

| Free-running timer mode            | Square wave output (only when con | npare function is used) |

| Pulse width measurement mode       |                                   | _                       |

#### **Remark** n = 0 to 8

## Table 7-5. Truth Table of TOPn0 and TOPn1 Pins Under Control of Timer Output Control Bits

| TPnIOC0.TPnOLm Bit | TPnIOC0.TPnOEm Bit | TPnCTL0.TPnCE Bit | Level of TOPnm Pin                                                          |

|--------------------|--------------------|-------------------|-----------------------------------------------------------------------------|

| 0                  | 0                  | ×                 | Low-level output                                                            |

|                    | 1                  | 0                 | Low-level output                                                            |

|                    |                    | 1                 | Low level immediately before counting, high level after counting is started |

| 1                  | 0                  | ×                 | High-level output                                                           |

|                    | 1                  | 0                 | High-level output                                                           |

|                    |                    | 1                 | High level immediately before counting, low level after counting is started |

**Remark** n = 0 to 8 m = 0, 1

## (5) TMQ0 I/O control register 2 (TQ0IOC2)

The TQ0IOC2 register is an 8-bit register that controls the valid edge of the external event count input signal (TIQ00 pin) and external trigger input signal (TIQ00 pin).

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

|         | eset: 00H     |                                                                                                    | Address:                                                                                                                                                     | 4                                                                                                                                                          | 0                                                                                     | 0                                                                                                          | 4                                                                                                             | 0                                                                                                      |

|---------|---------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| TQ0IOC2 | 7             | 6<br>0                                                                                             | 5                                                                                                                                                            | 4                                                                                                                                                          | 3                                                                                     |                                                                                                            | 1<br>FQ0ETS1 T                                                                                                |                                                                                                        |

| 1001002 | 0             | 0                                                                                                  | 0                                                                                                                                                            | 0                                                                                                                                                          | IQUEESI                                                                               | IQUEE50                                                                                                    |                                                                                                               |                                                                                                        |

|         | TOOFFOL       | TOOFFOO                                                                                            | <b>F</b> . <b>1</b>                                                                                                                                          |                                                                                                                                                            |                                                                                       |                                                                                                            | ) l'al                                                                                                        |                                                                                                        |

|         |               |                                                                                                    |                                                                                                                                                              |                                                                                                                                                            | it input signa                                                                        |                                                                                                            |                                                                                                               | e setting                                                                                              |

|         | 0             | 0                                                                                                  |                                                                                                                                                              |                                                                                                                                                            | (external eve                                                                         | ent count in                                                                                               | /alid)                                                                                                        |                                                                                                        |

|         | 0             | 1                                                                                                  |                                                                                                                                                              | of rising e                                                                                                                                                |                                                                                       |                                                                                                            |                                                                                                               |                                                                                                        |

|         | 1             | 0                                                                                                  |                                                                                                                                                              | of falling                                                                                                                                                 | 0                                                                                     |                                                                                                            |                                                                                                               |                                                                                                        |

|         | 1             | 1                                                                                                  | Detection                                                                                                                                                    | of both e                                                                                                                                                  | dges                                                                                  |                                                                                                            |                                                                                                               |                                                                                                        |

|         | TOOFTOI       | TQ0ETS0                                                                                            | Extorno                                                                                                                                                      | l triggor in                                                                                                                                               | nput signal (1                                                                        | 1000 pip) y                                                                                                | valid odgo o                                                                                                  | otting                                                                                                 |

|         | 0             | 0                                                                                                  |                                                                                                                                                              |                                                                                                                                                            | external trig                                                                         | • /                                                                                                        | and edge S                                                                                                    | eung                                                                                                   |

|         | 0             | 1                                                                                                  | -                                                                                                                                                            |                                                                                                                                                            |                                                                                       | ger invaliu)                                                                                               |                                                                                                               |                                                                                                        |

|         | 1             | 0                                                                                                  |                                                                                                                                                              | of rising e                                                                                                                                                | -                                                                                     |                                                                                                            |                                                                                                               |                                                                                                        |

|         | 1 1           | 0                                                                                                  |                                                                                                                                                              |                                                                                                                                                            |                                                                                       |                                                                                                            |                                                                                                               |                                                                                                        |

|         | 1<br>Cautions | 1<br>5 1. Rew                                                                                      | Detection                                                                                                                                                    | of both e                                                                                                                                                  |                                                                                       | D, TQ0ET                                                                                                   | S1, and T                                                                                                     | Q0ETS0                                                                                                 |

|         |               | 5 1. Rew<br>bits<br>can<br>mist<br>set t<br>2. The<br>TQ0                                          | Detection<br>rite the T<br>when the<br>be writte<br>akenly p<br>he bits a<br>TQ0EES<br>CTL1.TQ                                                               | QOEES1<br>e TQOCT<br>en when<br>erformed<br>gain.<br>1 and TO<br>0EEE bi                                                                                   | dges<br>I, TQ0EES<br>FL0.TQ0CE<br>the TQ0CI<br>d, clear the<br>Q0EES0 bi<br>it = 1 or | bit = 0.<br>E bit = 1.)<br>TQOCE<br>ts are val                                                             | (The sam<br>If rewrit<br>bit to 0 a<br>id only w<br>e externa                                                 | ne value<br>ing was<br>nd then<br>then the<br>al event                                                 |

|         |               | 5 1. Rew<br>bits<br>can<br>mist<br>set t<br>2. The<br>TQO<br>cour<br>= 00<br>3. The<br>exte<br>TQO | Detection<br>rite the T<br>when the<br>be writte<br>akenly p<br>the bits a<br>TQ0EES<br>CTL1.TQ<br>nt mode (<br>1) has be<br>TQ0ETS<br>rnal trigg<br>CTL1.TQ | GOUEES1<br>TQUEES1<br>TQUEES1<br>TQUCT<br>To the the<br>erformed<br>gain.<br>1 and TC<br>DEEE bi<br>(TQUCTL<br>the set.<br>1 and TC<br>Jer pulse<br>0MD0 b | dges<br>I, TQ0EES<br>ILO.TQ0CE<br>the TQ0CI<br>d, clear the<br>Q0EES0 bi              | bit = 0.<br>E bit = 1.)<br>TQ0CE<br>ts are val<br>when th<br>to TQ0C<br>ts are val<br>ode (TQ0<br>) or the | (The sam<br>If rewrit<br>bit to 0 a<br>id only w<br>e externa<br>TL1.TQ0M<br>id only w<br>CTL1.TQ0<br>one-sho | ne value<br>ing was<br>ind then<br>when the<br>al event<br>AD0 bits<br>when the<br>OMD2 to<br>ot pulse |

When the TQ0CE bit is set to 1, 16-bit timer/event counter Q waits for a trigger. When the trigger is generated, the 16-bit counter is cleared from FFFFH to 0000H, starts counting, and outputs a one-shot pulse from the TOQ0k pin. After the one-shot pulse is output, the 16-bit counter is set to FFFFH, stops counting, and waits for a trigger. If a trigger is generated again while the one-shot pulse is being output, it is ignored.

The output delay period and active level width of the one-shot pulse can be calculated as follows.

```

Output delay period = (Set value of TQ0CCRk register) × Count clock cycle

Active level width = (Set value of TQ0CCR0 register – Set value of TQ0CCRk register + 1) × Count clock cycle

```

The compare match interrupt request signal INTTQ0CC0 is generated when the 16-bit counter counts after its count value matches the value of the CCR0 buffer register. The compare match interrupt request signal INTTQ0CCk is generated when the count value of the 16-bit counter matches the value of the CCRk buffer register.

The valid edge of an external trigger input or setting the software trigger (TQ0CTL1.TQ0EST bit) to 1 is used as the trigger.

**Remark** k = 1 to 3

| (a) T   | MQ0 cor | trol regis | ster 0 (TQ | OCTLO) |   |         |          |           |                                             |

|---------|---------|------------|------------|--------|---|---------|----------|-----------|---------------------------------------------|

|         | TQ0CE   |            |            |        |   | TQ0CKS2 | 2 TQ0CKS | I TQOCKSO | )                                           |

| TQOCTLO | 0/1     | 0          | 0          | 0      | 0 | 0/1     | 0/1      | 0/1       |                                             |

| •       |         |            |            |        |   |         |          |           |                                             |

|         |         |            |            |        |   |         |          |           | Select count clock                          |

|         |         |            |            |        |   |         |          |           | 0: Stop counting<br>1: Enable counting      |

|         |         |            |            |        |   |         |          |           | č                                           |

| (b) T   | MQ0 cor | trol regis | ster 1 (TQ | 0CTL1) |   |         |          |           |                                             |

|         |         | TQ0EST     | TQ0EEE     |        |   | TQ0MD2  | TQ0MD1   | TQ0MD0    |                                             |

| TQ0CTL1 | 0       | 0/1        | 0          | 0      | 0 | 0       | 1        | 1         |                                             |

| -       |         |            |            |        |   |         |          |           |                                             |

|         |         |            |            |        |   |         |          |           | 0, 1, 1:<br>One-shot pulse output mode      |

|         |         |            |            |        |   |         |          |           | Generate software trigger when 1 is written |

|         |         |            |            |        |   |         |          |           |                                             |

## (2) D/A conversion value setting registers 0, 1 (DA0CS0, DA0CS1)

The DA0CS0 and DA0CS1 registers set the analog voltage value output to the ANO0 and ANO1 pins. These registers can be read or written in 8-bit units. Reset sets these registers to 00H.

|         | After res                             | set: 00H  | R/W     | Address: D | DA0CS0 FF | FFF280H, | DA0CS1 F | FFFF281H | ł       |            |

|---------|---------------------------------------|-----------|---------|------------|-----------|----------|----------|----------|---------|------------|

|         |                                       | 7         | 6       | 5          | 4         | 3        | 2        | 1        | 0       |            |

|         | DA0CSn                                | DA0CSn7   | DA0CSn6 | DA0CSn5    | DA0CSn4   | DA0CSn3  | DA0CSn2  | DA0CSn1  | DA0CSn0 |            |

| Caution | In the real<br>INTTP2CCC<br>INTTP2CCC | )/INTTP3C | CO sig  | nals are   | e genera  |          |          |          | •       | the<br>the |

| Remark  | n = 0, 1                              |           |         |            |           |          |          |          |         |            |

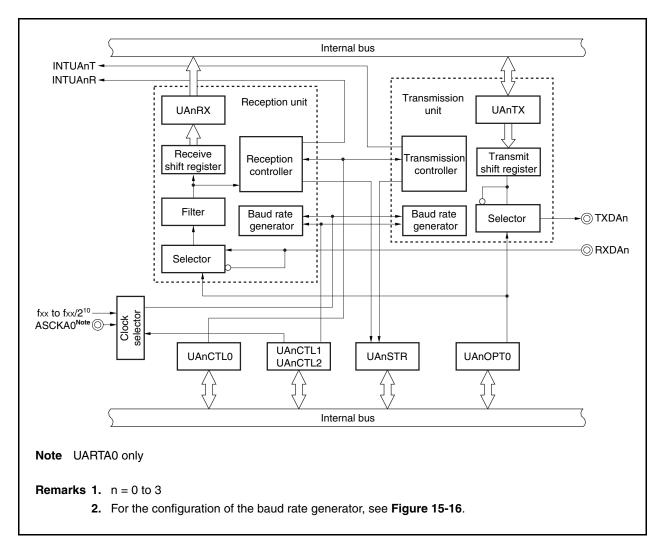

## 15.3 Configuration

The block diagram of the UARTAn is shown below.

UARTAn includes the following hardware.

| Table 15-1. | Configuration of UARTAn |

|-------------|-------------------------|

|-------------|-------------------------|

| Item      | Configuration                              |

|-----------|--------------------------------------------|

| Registers | UARTAn control register 0 (UAnCTL0)        |

|           | UARTAn control register 1 (UAnCTL1)        |

|           | UARTAn control register 2 (UAnCTL2)        |

|           | UARTAn option control register 0 (UAnOPT0) |

|           | UARTAn status register (UAnSTR)            |

|           | UARTAn receive shift register              |

|           | UARTAn receive data register (UAnRX)       |

|           | UARTAn transmit shift register             |

|           | UARTAn transmit data register (UAnTX)      |

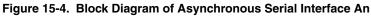

## (2) Operation timing

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (2/2   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|         | (iii) Communication type 2 (CBnCKP and CBnDAP bits = 01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|         | SIBn capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

|         | SOBn pin D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|         | Reg-R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|         | INTCBnT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|         | INTCBnR<br>interrupt <sup>Note 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|         | CBnTSF bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|         | (iv) Communication type 4 (CBnCKP and CBnDAP bits = 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|         | SCKBn pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

|         | SIBn capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

|         | SOBn pin D7 <u>D6</u> <u>D5</u> <u>D4</u> <u>D3</u> <u>D2</u> <u>D1</u> <u>D0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

|         | Reg-R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|         | INTCBnT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|         | INTCBnR<br>interrupt <sup>Note 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|         | CBnTSF bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

|         | The INTCBnT interrupt is set when the data written to the CBnTX register is transferred to the data shift register in the continuous transmission or continuous transmission/reception modes. In the single transmission or single transmission/reception modes, the INTCBnT interrupt request signal is not generated, but the INTCBnR interrupt request signal is generated upon end of communication. The INTCBnR interrupt occurs if reception is correctly ended and receive data is ready in the CBnRX register while reception is enabled. In the single mode, the INTCBnR interrupt request signal is generated even in the transmission mode, upon end of communication. | e<br>t |

| Caution | In single transfer mode, writing to the CBnTX register with the CBnTSF bit set to 1 is ignored.<br>This has no influence on the operation during transfer.<br>For example, if the next data is written to the CBnTX register when DMA is started by generating                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|         | the INTCBnR signal, the written data is not transferred because the CBnTSF bit is set to 1.<br>Use the continuous transfer mode, not the single transfer mode, for such applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

## 17.14.2 When communication reservation function is disabled (IICFn.IICRSVn bit = 1)

When the IICCn.STTn bit is set when the bus is not used in a communication during bus communication, this request is rejected and a start condition is not generated. There are two modes in which the bus is not used.

- When arbitration results in neither master nor slave operation

- When an extension code is received and slave operation is disabled (ACK is not returned and the bus was released when the IICCn.LRELn bit was set to 1) (n = 0 to 2).

To confirm whether the start condition was generated or request was rejected, check the IICFn.STCFn flag. The time shown in Table 17-7 is required until the STCFn flag is set after setting the STTn bit to 1. Therefore, secure the time by software.

| OCKSENm | OCKSm1 | OCKSm0 | CLn1 | CLn0 | Wait Period |

|---------|--------|--------|------|------|-------------|

| 1       | 0      | 0      | 0    | ×    | 10 clocks   |

| 1       | 0      | 1      | 0    | ×    | 15 clocks   |

| 1       | 1      | 0      | 0    | ×    | 20 clocks   |

| 1       | 1      | 1      | 0    | ×    | 25 clocks   |

| 0       | 0      | 0      | 1    | 0    | 5 clocks    |

#### Table 17-7. Wait Periods

**2.** n = 0 to 2 m = 0, 1

Remarks 1. x: don't care

#### 19.4.3 EP flag

The EP flag is a status flag used to indicate that exception processing is in progress. It is set when an exception occurs.

| After rese | et: 00000020H                       |                                                                                                  |    |    |    |     |    |    |   |   |

|------------|-------------------------------------|--------------------------------------------------------------------------------------------------|----|----|----|-----|----|----|---|---|

|            | 31                                  | 8                                                                                                | 7  | 6  | 5  | 4   | 3  | 2  | 1 | 0 |

| PSW        |                                     | 0                                                                                                | NP | EP | ID | SAT | CY | OV | S | Z |

| -          |                                     |                                                                                                  |    |    |    |     |    |    |   |   |

|            | EP                                  | EP         Exception processing status           0         Exception processing not in progress. |    |    |    |     |    |    |   |   |

|            | 0                                   |                                                                                                  |    |    |    |     |    |    |   |   |

|            | 1 Exception processing in progress. |                                                                                                  |    |    |    |     |    |    |   |   |

# 24.4 Operation

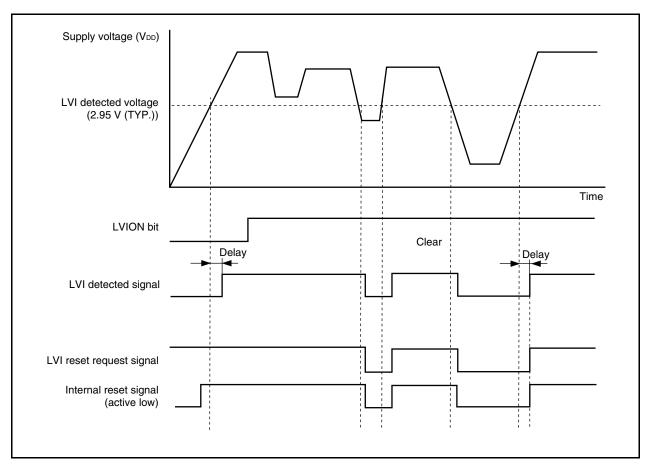

Depending on the setting of the LVIM.VIMD bit, an interrupt signal (INTLVI) or an internal reset signal is generated. How to specify each operation is described below, together with timing charts.

#### 24.4.1 To use for internal reset signal

- <To start operation>

- <1> Mask the interrupt of LVI.

- <2> Select the voltage to be detected by using the LVIS.LVIS0 bit.

- <3> Set the LVIM.LVION bit to 1 (to enable operation).

- <4> Insert a wait cycle of 0.2 ms (max.) or more by software.

- <5> By using the LVIM.LVIF bit, check if the supply voltage > detected voltage.

- <6> Set the LVIMD bit to 1 (to generate an internal reset signal).

# Caution If the LVIMD bit is set to 1, the contents of the LVIM and LVIS registers cannot be changed until a reset request other than LVI is generated.

#### Figure 24-2. Operation Timing of Low-Voltage Detector (LVIMD Bit = 1)

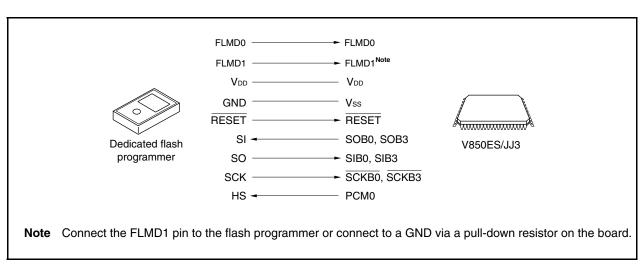

#### (3) CSIB0 + HS, CSIB3 + HS

Serial clock: 2.4 kHz to 2.5 MHz (MSB first)

## Figure 27-5. Communication with Dedicated Flash Programmer (CSIB0 + HS, CSIB3 + HS)

The dedicated flash programmer outputs the transfer clock, and the V850ES/JJ3 operates as a slave.

When the PG-FP4 is used as the dedicated flash programmer, it generates the following signals to the V850ES/JJ3. For details, refer to the **PG-FP4 User's Manual (U15260E)**.

|             |        | PG-FP4                                                       | V850ES/JJ3           | Proce               | ssing for Conr      | nection                   |

|-------------|--------|--------------------------------------------------------------|----------------------|---------------------|---------------------|---------------------------|

| Signal Name | I/O    | Pin Function                                                 | Pin Name             | UARTA0              | CSIB0,<br>CSIB3     | CSIB0 + HS,<br>CSIB3 + HS |

| FLMD0       | Output | Write enable/disable                                         | FLMD0                | O                   | 0                   | O                         |

| FLMD1       | Output | Write enable/disable                                         | FLMD1                | ONote 1             | ONote 1             | ONote 1                   |

| VDD         | -      | VDD voltage generation/voltage monitor                       | V <sub>DD</sub>      | O                   | 0                   | O                         |

| GND         | -      | Ground                                                       | Vss                  | O                   | 0                   | O                         |

| CLK         | Output | Clock output to V850ES/JJ3                                   | X1, X2               | × <sup>Note 2</sup> | × <sup>Note 2</sup> | × <sup>Note 2</sup>       |

| RESET       | Output | Reset signal                                                 | RESET                | O                   | 0                   | O                         |

| SI/RxD      | Input  | Receive signal                                               | SOB0, SOB3/<br>TXDA0 | O                   | 0                   | 0                         |

| SO/TxD      | Output | Transmit signal                                              | SIB0, SIB3/<br>RXDA0 | O                   | 0                   | 0                         |

| SCK         | Output | Transfer clock                                               | SCKB0, SCKB3         | ×                   | 0                   | O                         |

| HS          | Input  | Handshake signal for CSIB0 + HS, CSIB3<br>+ HS communication | PCM0                 | ×                   | ×                   | O                         |

Table 27-5. Signal Connections of Dedicated Flash Programmer (PG-FP4)

Notes 1. Wire these pins as shown in Figure 27-6, or connect then to GND via pull-down resistor on board.

2. Clock cannot be supplied via the CLK pin of the flash programmer. Create an oscillator on board and supply the clock.

**Remark** O: Must be connected.

×: Does not have to be connected.

## • Port registers when UARTA0 is used

When UARTA0 is used, port registers are set to make the TXDA0 and RXDA0 pins valid by the debug monitor program. Do not change the following register settings with the user program during debugging. (The same value can be overwritten.)

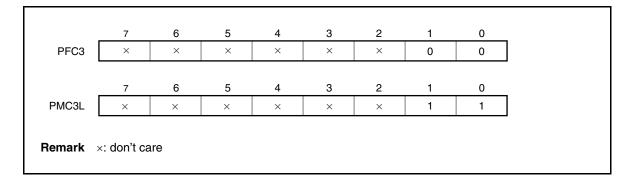

## • Port registers when CSIB0 is used

When CSIB0 is used, port registers are set to make the SIB0, SOB0, SCKB0, and HS (PMC0) pins valid by the debug monitor program. Do not change the following register settings with the user program during debugging. (The same value can be overwritten.)

|                              | 7                                                    | 6                                  | 5                      | 4                      | 3           | 2          | 1            | 0          |           |

|------------------------------|------------------------------------------------------|------------------------------------|------------------------|------------------------|-------------|------------|--------------|------------|-----------|

| PMC4                         | ×                                                    | ×                                  | ×                      | ×                      | ×           | 1          | 1            | 1          |           |

|                              | 7                                                    | 6                                  | 5                      | 4                      | 3           | 2          | 1            | 0          |           |

| PFC4                         | ×                                                    | ×                                  | ×                      | ×                      | ×           | ×          | 0            | 0          |           |

| HS (PMC                      | 0 pin) sett                                          | ings<br>6                          | 5                      | 4                      | 3           | 2          | 1            | 0          |           |

|                              | 7                                                    | 6                                  | 5                      | 4                      | 3           | 2          | 1            | 0          | ,         |

| PMCM                         | ×                                                    | ×                                  | ×                      | ×                      | ×           | ×          | ×            | 0          | I         |

|                              | 7                                                    | 6                                  | 5                      | 4                      | 3           | 2          | 1            | 0          |           |

| PCM                          | ×                                                    | ×                                  | ×                      | ×                      | ×           | ×          | ×            | Note       |           |

| The po<br>the del<br>usually | to this bit<br>rt values o<br>bugger sta<br>use read | correspor<br>atus. To<br>-modify-w | iding to th<br>perform | port regi<br>interrupt | ster settir | igs in 8-b | oit units, t | the user p | orogram o |

| (1 | 4/37) |

|----|-------|

| <u> </u>   |                |                                                |                           |                                                                                                                                                                                                                                                                                                                                                                                                   | (      | 14/37 |  |  |

|------------|----------------|------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--|--|

| Chapter    | Classification | Function                                       | Details of<br>Function    | Cautions                                                                                                                                                                                                                                                                                                                                                                                          | Pag    | e     |  |  |

| Chapter 11 | Soft           | Watchdog WDTM2 register<br>timer 2<br>function |                           | WDTM2 register To stop the operation of watchdog timer 2, set the RCM.RSTOP bit to 1 (to stop the internal oscillator) and write 00H in the WDTM2 register. If the RCM.RSTOP bit cannot be set to 1, set the WDCS23 bit to 1 (2 <sup>n</sup> /fxx is selected and the clock can be stopped in the IDLE1, IDLW2, sub-IDLE, and subclock operation modes).                                          |        |       |  |  |

|            |                |                                                | WDTE register             | When a value other than "ACH" is written to the WDTE register, an overflow signal is forcibly output.                                                                                                                                                                                                                                                                                             | p. 414 |       |  |  |

|            |                |                                                |                           | When a 1-bit memory manipulation instruction is executed for the WDTE register, an overflow signal is forcibly output.                                                                                                                                                                                                                                                                            | p. 414 |       |  |  |

|            |                |                                                |                           | To intentionally generate an overflow signal, write a value other than "ACH" to the WDTE register only once, or write data to the WDTM2 register only twice.<br>However, when the watchdog timer 2 is set to stop operation, an overflow signal is not generated even if data is written to the WDTM2 register only twice, or a value other than "ACH" is written to the WDTE register only once. | p. 414 |       |  |  |