Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 128                                                                                  |

| Program Memory Size        | 768KB (768K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                |                                                                                      |

| RAM Size                   | 60K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3745gj-gae-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

(2/2)

**Note** The result of the operation that has performed saturation processing is determined by the contents of the OV and S flags. The SAT flag is set to 1 only when the OV flag is set to 1 when a saturation operation is performed.

| Status of Operation Result               |                  | Flag Status |   | Result of Operation of  |

|------------------------------------------|------------------|-------------|---|-------------------------|

|                                          | SAT              | OV          | S | Saturation Processing   |

| Maximum positive value is exceeded       | 1                | 1           | 0 | 7FFFFFFH                |

| Maximum negative value is exceeded       | 1                | 1           | 1 | 8000000H                |

| Positive (maximum value is not exceeded) | Holds value      | 0           | 0 | Operation result itself |

| Negative (maximum value is not exceeded) | before operation |             | 1 |                         |

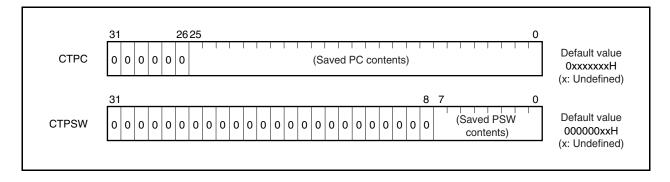

### (5) CALLT execution status saving registers (CTPC and CTPSW)

CTPC and CTPSW are CALLT execution status saving registers.

When the CALLT instruction is executed, the contents of the program counter (PC) are saved to CTPC, and those of the program status word (PSW) are saved to CTPSW.

The contents saved to CTPC are the address of the instruction next to CALLT.

The current contents of the PSW are saved to CTPSW.

Bits 31 to 26 of CTPC and bits 31 to 8 of CTPSW are reserved for future function expansion (fixed to 0).

| Address   | Function Register Name             | Symbol | R/W | Manir        | oulatab      | le Bits      | (6/1)<br>Default Value |

|-----------|------------------------------------|--------|-----|--------------|--------------|--------------|------------------------|

|           |                                    |        |     | 1            | 8            | 16           |                        |

| FFFFF422H | Port 1 mode register               | PM1    | R/W | $\checkmark$ |              |              | FFH                    |

| FFFFF426H | Port 3 mode register               | PM3    | 1   |              |              | $\checkmark$ | FFFFH                  |

| FFFFF426H | Port 3 mode register L             | PM3L   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF427H | Port 3 mode register H             | РМЗН   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF428H | Port 4 mode register               | PM4    | 1   | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF42AH | Port 5 mode register               | PM5    | 1   | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF42CH | Port 6 mode register               | PM6    | 1   |              |              | $\checkmark$ | FFFFH                  |

| FFFFF42CH | Port 6 mode register L             | PM6L   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF42DH | Port 6 mode register H             | PM6H   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF42EH | Port 7 mode register L             | PM7L   | 1   | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF42FH | Port 7 mode register H             | PM7H   | 1   | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF430H | Port 8 mode register               | PM8    | 1   | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF432H | Port 9 mode register               | PM9    | 1   |              |              | $\checkmark$ | FFFFH                  |

| FFFFF432H | Port 9 mode register L             | PM9L   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF433H | Port 9 mode register H             | РМ9Н   |     | $\checkmark$ | $\checkmark$ |              | FFH                    |

| FFFFF440H | Port 0 mode control register       | PMC0   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF446H | Port 3 mode control register       | PMC3   | 1   |              |              | $\checkmark$ | 0000H                  |

| FFFFF446H | Port 3 mode control register L     | PMC3L  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF447H | Port 3 mode control register H     | РМСЗН  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF448H | Port 4 mode control register       | PMC4   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF44AH | Port 5 mode control register       | PMC5   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF44CH | Port 6 mode control register       | PMC6   | 1   |              |              | $\checkmark$ | 0000H                  |

| FFFFF44CH | Port 6 mode control register L     | PMC6L  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF44DH | Port 6 mode control register H     | PMC6H  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF450H | Port 8 mode control register       | PMC8   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF452H | Port 9 mode control register       | PMC9   | 1   |              |              | $\checkmark$ | 0000H                  |

| FFFFF452H | Port 9 mode control register L     | PMC9L  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF453H | Port 9 mode control register H     | PMC9H  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF460H | Port 0 function control register   | PFC0   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF466H | Port 3 function control register   | PFC3   | 1   |              |              |              | 0000H                  |

| FFFFF466H | Port 3 function control register L | PFC3L  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF467H | Port 3 function control register H | PFC3H  |     | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF468H | Port 4 function control register   | PFC4   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF46AH | Port 5 function control register   | PFC5   | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF46DH | Port 6 function control register H | PFC6H  | 1   | $\checkmark$ |              |              | 00H                    |

| FFFFF472H | Port 9 function control register   | PFC9   | 1   |              |              |              | 0000H                  |

| FFFFF472H | Port 9 function control register L | PFC9L  | 1   | $\checkmark$ |              |              | 00H                    |

| FFFFF473H | Port 9 function control register H | PFC9H  | 1   | $\checkmark$ | $\checkmark$ |              | 00H                    |

| FFFFF484H | Data wait control register 0       | DWC0   | 1   |              |              | $\checkmark$ | 7777H                  |

| FFFFF488H | Address wait control register      | AWC    | 1   |              |              | $\checkmark$ | FFFFH                  |

| FFFFF48AH | Bus cycle control register         | BCC    | 1   | <u> </u>     |              |              | ААААН                  |

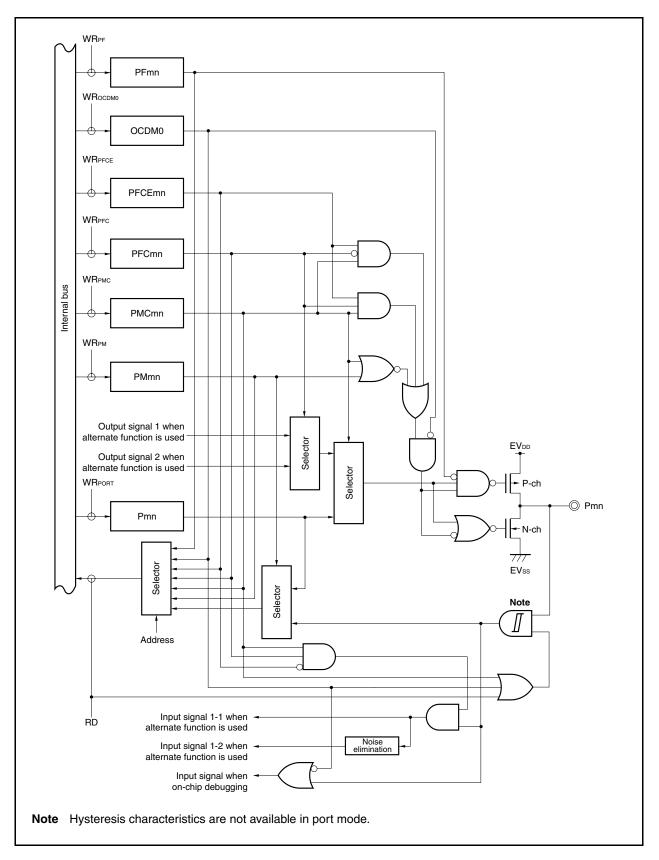

Figure 4-26. Block Diagram of Type U-6

# (5) TMPn I/O control register 2 (TPnIOC2)

The TPnIOC2 register is an 8-bit register that controls the valid edge of the external event count input signal (TIPn0 pin) and external trigger input signal (TIPn0 pin).

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

# (6) TMPn option register 0 (TPnOPT0)

The TPnOPT0 register is an 8-bit register used to set the capture/compare operation and detect an overflow. This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

| After re     | eset: 00H          | R/W                                                              | Address:                           | TP0OPT0                       | FFFFF59                         | 95H, TP10                        | OPTO FFI                         | FFF5A5H,               |  |

|--------------|--------------------|------------------------------------------------------------------|------------------------------------|-------------------------------|---------------------------------|----------------------------------|----------------------------------|------------------------|--|

|              |                    |                                                                  |                                    | TP2OPT0                       | FFFF5E                          | 35H, TP3                         | OPT0 FF                          | FFF5C5H,               |  |

|              |                    |                                                                  |                                    | TP4OPT0                       | FFFFF5                          | 05H, TP5                         | OPT0 FF                          | FFF5E5H,               |  |

|              |                    |                                                                  |                                    | TP6OPT0                       | FFFF5F                          | 5H, TP7                          | OPTO FF                          | FFF605H,               |  |

|              |                    |                                                                  |                                    | TP8OPT0                       | FFFFF61                         | 5H                               |                                  |                        |  |

|              | 7                  | 6                                                                | 5                                  | 4                             | 3                               | 2                                | 1                                | <0>                    |  |

| TPnOPT0      | 0                  | 0                                                                | TPnCCS1                            | TPnCCS0                       | 0                               | 0                                | 0                                | TPnOVF                 |  |

| (n = 0 to 8) |                    |                                                                  |                                    |                               |                                 |                                  |                                  |                        |  |

|              | TPnCCS1            |                                                                  | TPnC                               | CR1 register                  | capture/c                       | ompare s                         | election                         |                        |  |

|              | 0                  | Compare                                                          | register se                        | elected                       |                                 |                                  |                                  |                        |  |

|              | 1                  | Capture r                                                        | register sel                       | ected                         |                                 |                                  |                                  |                        |  |

|              | The TPn            | CCS1 bit s                                                       | etting is va                       | lid only in the               | e free-runr                     | ning timer                       | mode.                            |                        |  |

|              |                    |                                                                  |                                    |                               |                                 |                                  |                                  |                        |  |

|              | TPnCCS0            |                                                                  | TPnC                               | CR0 register                  | capture/c                       | ompare s                         | election                         |                        |  |

|              | 0                  | Compare register selected                                        |                                    |                               |                                 |                                  |                                  |                        |  |

|              | 1                  | Capture r                                                        | register sel                       | ected                         |                                 |                                  |                                  |                        |  |

|              | The TPn            | PnCCS0 bit setting is valid only in the free-running timer mode. |                                    |                               |                                 |                                  |                                  |                        |  |

|              |                    |                                                                  |                                    |                               |                                 |                                  |                                  |                        |  |

|              | TPn                | OVF                                                              |                                    | TMPn ove                      | rflow dete                      | ction flag                       |                                  |                        |  |

|              | Set (1)            |                                                                  | Overflow                           | occurred                      |                                 |                                  |                                  |                        |  |

|              | Reset (0)          |                                                                  |                                    | bit 0 written                 |                                 |                                  |                                  |                        |  |

|              |                    |                                                                  |                                    | the 16-bit co<br>unning timer |                                 |                                  |                                  |                        |  |

|              | mode.              | rupt roquo                                                       | et cignal (II                      | NTTPnOV) is                   | aonorato                        | d at the c                       | ama tima                         | that the               |  |

|              | TPnOV              | F bit is set                                                     | to 1. The l                        | NTTPnOV s                     | ignal is no                     | t generat                        | ed in mod                        | es other               |  |

|              |                    |                                                                  | 0                                  | ode and the                   | •                               |                                  |                                  |                        |  |

|              | register           | are read v                                                       | vhen the TI                        | PnOVF bit =                   | 1.                              |                                  |                                  |                        |  |

|              |                    | nove dit c                                                       | an be both                         | read and wr                   |                                 |                                  |                                  |                        |  |

|              | The TP     to 1 by | software.                                                        | Writing 1 ha                       | as no influen                 |                                 | oporation                        |                                  |                        |  |

|              |                    | software.                                                        | Writing 1 h                        | as no influen                 |                                 | oporation                        |                                  |                        |  |

|              | to 1 by            |                                                                  |                                    |                               |                                 |                                  |                                  | the TPnCE              |  |

|              | to 1 by            | 1. Rew                                                           | rite the T                         | PnCCS1 a                      | nd TPnC                         | CS0 bit                          | s when t                         | the TPnCE<br>the TPnCE |  |

|              | to 1 by            | 1. Rewi<br>bit =                                                 | rite the T<br>0. (The              | PnCCS1 ai<br>same valu        | nd TPnC<br>e can be             | CS0 bit<br>e writter             | s when t<br>n when t             |                        |  |

|              | to 1 by            | 1. Rewi<br>bit =<br>bit =                                        | rite the T<br>0. (The<br>1.) If re | PnCCS1 ai<br>same valu        | nd TPnC<br>e can be<br>s mistal | CS0 bit<br>e writter<br>kenly pe | s when t<br>n when t<br>erformed | the TPnCE              |  |

# 7.6 Selector Function

In the V850ES/JJ3, the capture trigger input for TMP can be selected from the input signal via the port/timer alternate-function pin and the peripheral I/O (TMP/UARTA) input signal.

This function makes the following possible.

- The TIP10 and TIP11 input signals for TMP1 can be selected from the signals via the port/timer alternate-function pins (TIP10 and TIP11) and the signals via the UARTA reception alternate-function pins (RXDA0 and RXDA1). Similarly, the TIP31 input signal for TMP3 can be selected from the signal via the port/timer alternate-function pin (TIP31) and the signal via the UARTA reception alternate-function pin (RXDA3).

- → When the RXDA0, RXDA1, or RXDA3 signal for UARTA0, for UARTA1, or UARTA3 is selected, the baud rate error of the UARTA LIN reception transfer rate can be calculated.

- Cautions 1. When using the selector function, be sure to set the port/timer alternate function pins for TMP to be connected to the capture trigger input.

- 2. Disable the peripheral I/Os to be connected (TMP/UARTA) before setting the selector function.

The capture trigger input can be selected using the following register.

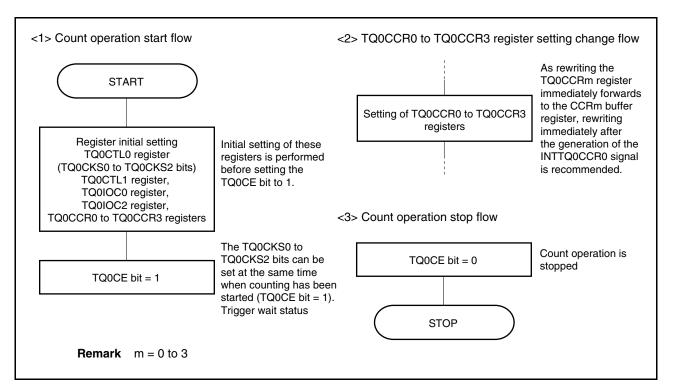

### 8.5 Operation

TMQ0 can perform the following operations.

| Operation                                            | TQ0CTL1.TQ0EST Bit<br>(Software Trigger Bit) | TIQ00 Pin<br>(External Trigger Input) | Capture/Compare<br>Register Setting | Compare Register<br>Write |

|------------------------------------------------------|----------------------------------------------|---------------------------------------|-------------------------------------|---------------------------|

| Interval timer mode                                  | Invalid                                      | Invalid                               | Compare only                        | Anytime write             |

| External event count mode <sup>Note 1</sup>          | Invalid                                      | Invalid                               | Compare only                        | Anytime write             |

| External trigger pulse output mode <sup>Note 2</sup> | Valid                                        | Valid                                 | Compare only                        | Batch write               |

| One-shot pulse output mode <sup>Note 2</sup>         | Valid                                        | Valid                                 | Compare only                        | Anytime write             |

| PWM output mode                                      | Invalid                                      | Invalid                               | Compare only                        | Batch write               |

| Free-running timer mode                              | Invalid                                      | Invalid                               | Switching enabled                   | Anytime write             |

| Pulse width measurement mode <sup>Note 2</sup>       | Invalid                                      | Invalid                               | Capture only                        | Not applicable            |

- **Notes 1.** To use the external event count mode, specify that the valid edge of the TIQ00 pin capture trigger input is not detected (by clearing the TQ0IOC1.TQ0IS1 and TQ0IOC1.TQ0IS0 bits to "00").

- 2. When using the external trigger pulse output mode, one-shot pulse output mode, and pulse width measurement mode, select the internal clock as the count clock (by clearing the TQ0CTL1.TQ0EEE bit to 0).

# 11.4 Operation

Watchdog timer 2 automatically starts in the reset mode following reset release.

The WDTM2 register can be written to only once following reset using byte access. To use watchdog timer 2, write the operation mode and the interval time to the WDTM2 register using an 8-bit memory manipulation instruction. After this, the operation of watchdog timer 2 cannot be stopped.

The WDCS24 to WDCS20 bits of the WDTM2 register are used to select the watchdog timer 2 loop detection time interval.

Writing ACH to the WDTE register clears the counter of watchdog timer 2 and starts the count operation again. After the count operation has started, write ACH to WDTE within the loop detection time interval.

If the time interval expires without ACH being written to the WDTE register, a reset signal (WDT2RES) or a nonmaskable interrupt request signal (INTWDT2) is generated, depending on the set values of the WDM21 and WDTM2.WDM20 bits.

When the WDTM2.WDM21 bit is set to 1 (reset mode), if a WDT overflow occurs during oscillation stabilization after a reset or standby is released, no internal reset will occur and the CPU clock will switch to the internal oscillation clock.

To not use watchdog timer 2, write 00H to the WDTM2 register.

For the non-maskable interrupt servicing while the non-maskable interrupt request mode is set, see **19.2.2 (2)** From **INTWDT2 signal**.

## 13.6 Cautions

### (1) When A/D converter is not used

When the A/D converter is not used, the power consumption can be reduced by clearing the ADA0M0.ADA0CE bit to 0.

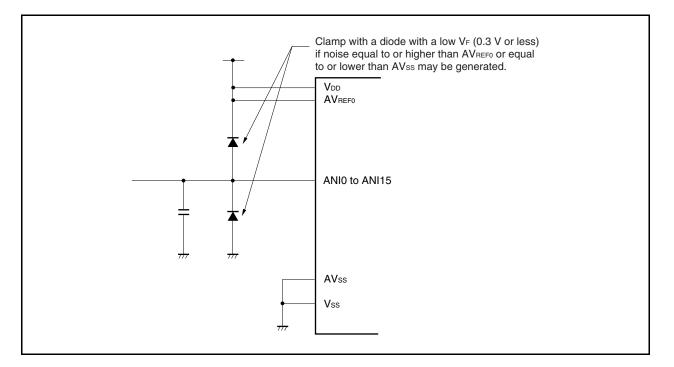

### (2) Input range of ANI0 to ANI15 pins

Input the voltage within the specified range to the ANI0 to ANI15 pins. If a voltage equal to or higher than AV<sub>REF0</sub> or equal to or lower than AV<sub>ss</sub> (even within the range of the absolute maximum ratings) is input to any of these pins, the conversion value of that channel is undefined, and the conversion value of the other channels may also be affected.

### (3) Countermeasures against noise

To maintain the 10-bit resolution, the ANI0 to ANI15 pins must be effectively protected from noise. The influence of noise increases as the output impedance of the analog input source becomes higher. To lower the noise, connecting an external capacitor as shown in Figure 13-12 is recommended.

#### Figure 13-12. Processing of Analog Input Pin

#### (4) Alternate I/O

The analog input pins (ANI0 to ANI15) function alternately as port pins. When selecting one of the ANI0 to ANI15 pins to execute A/D conversion, do not execute an instruction to read an input port or write to an output port during conversion as the conversion resolution may drop.

Also the conversion resolution may drop at the pins set as output port pins during A/D conversion if the output current fluctuates due to the effect of the external circuit connected to the port pins.

If a digital pulse is applied to a pin adjacent to the pin whose input signal is being converted, the A/D conversion value may not be as expected due to the influence of coupling noise. Therefore, do not apply a pulse to a pin adjacent to the pin undergoing A/D conversion.

### 16.6.9 Continuous transfer mode (master mode, transmission/reception mode)

MSB first (CBnCTL0.CBnDIR bit = 0), communication type 1 (CBnCTL1.CBnCKP and CBnCTL1.CBnDAP bits = 00), communication clock ( $f_{CCLK}$ ) =  $f_{XX}/2$  (CBnCTL1.CBnCKS2 to CBnCTL1.CBnCKS0 bits = 000), transfer data length = 8 bits (CBnCTL2.CBnCL3 to CBnCTL2.CBnCL0 bits = 0000)

# (4) When arbitration loss occurs due to restart condition during data transfer

| ST                     | AD6 to AD0                                                                                              | R/W                                                                                                                          | ĀCK                                                                     | D7 to Dn                                                                  | ST       | AD6 to AD0        | R/W       | ACK       | D7 to D0  | ĀCK        | S |

|------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|-------------------|-----------|-----------|-----------|------------|---|

|                        |                                                                                                         |                                                                                                                              |                                                                         | 1                                                                         |          |                   |           |           | 2         |            |   |

| 4                      | ▲1: IICSn regis                                                                                         | ter = 10                                                                                                                     | 00X110                                                                  | 3                                                                         |          |                   |           |           |           |            |   |

| 4                      | ▲2: IICSn regis                                                                                         | ter = 01                                                                                                                     | 000110E                                                                 | 3 (Example: W                                                             | /hen ALI | Dn bit is read di | uring int | errupt se | ervicing) |            |   |

| L                      | ∆ 3: IICSn regist                                                                                       | ter = 00                                                                                                                     | 000001E                                                                 | 3                                                                         |          |                   |           |           |           |            |   |

|                        |                                                                                                         |                                                                                                                              |                                                                         |                                                                           |          |                   |           |           |           |            |   |

|                        | Remarks 1.                                                                                              |                                                                                                                              |                                                                         |                                                                           |          |                   |           |           |           |            |   |

|                        |                                                                                                         |                                                                                                                              |                                                                         | d only when                                                               | SPIEn    | bit = $1$         |           |           |           |            |   |

|                        | 2                                                                                                       |                                                                                                                              | on't care<br>D6 to D0                                                   |                                                                           |          |                   |           |           |           |            |   |

|                        | Ζ.                                                                                                      | n = 01                                                                                                                       |                                                                         | U                                                                         |          |                   |           |           |           |            |   |

|                        |                                                                                                         |                                                                                                                              |                                                                         |                                                                           |          |                   |           |           |           |            |   |

|                        |                                                                                                         | 11 - 01                                                                                                                      | 10 L                                                                    |                                                                           |          |                   |           |           |           |            |   |

| <2> E                  | Extension cod                                                                                           | _                                                                                                                            | .0 2                                                                    |                                                                           |          |                   |           |           |           |            |   |

|                        |                                                                                                         | de                                                                                                                           |                                                                         |                                                                           | 1        |                   |           |           |           | г <u> </u> |   |

| < <b>2&gt; E</b><br>ST | AD6 to AD0                                                                                              | _                                                                                                                            | ĀCK                                                                     | D7 to Dn                                                                  | ST       | AD6 to AD0        | R/W       | ĀCK       | D7 to D0  | ĀCK        | ę |

| ST                     | AD6 to AD0                                                                                              | de<br>R/W                                                                                                                    | ĀĊĸ                                                                     | 1                                                                         | ST       | AD6 to AD0        |           | ACK       | D7 to D0  | ĀCK        |   |

| ST                     | AD6 to AD0<br>▲1: IICSn regis                                                                           | <b>de</b><br>R/₩<br>ter = 10                                                                                                 | ACK<br>00X1108                                                          | <b>1</b><br>3                                                             |          | 1                 |           | 2         |           | ĀĊĶ        |   |

| ST                     | AD6 to AD0<br>▲1: IICSn regis<br>▲2: IICSn regis                                                        | <b>de</b><br>R/W<br>ter = 10<br>ter = 01                                                                                     | ACK<br>00X1108<br>10X0108                                               | 1<br>3<br>3 (Example: W                                                   |          | 1                 |           | 2         |           | ĀCK        | ę |

| ST                     | AD6 to AD0<br>▲1: IICSn regis                                                                           | <b>de</b><br>R/W<br>ter = 10<br>ter = 01                                                                                     | ACK<br>00X1108<br>10X0108                                               | 1<br>3<br>3 (Example: W                                                   |          | 1                 |           | 2         |           | ACK        | Ę |

| ST                     | AD6 to AD0<br>▲1: IICSn regis<br>▲2: IICSn regis                                                        | de<br>$R/\overline{W}$<br>ter = 10<br>ter = 01<br>t is set to                                                                | ACK<br>00X110E<br>10X010E<br>0 1 by so                                  | 1<br>3<br>3 (Example: Wooftware                                           |          | 1                 |           | 2         |           | ĀĊĶ        | ę |

| ST                     | AD6 to AD0<br>▲1: IICSn regis<br>▲2: IICSn regis<br>ICCn.LRELn bit<br>∆ 3: IICSn regist                 | de<br>$R/\overline{W}$<br>ter = 10<br>ter = 01<br>t is set to<br>ter = 000                                                   | ACK<br>00X1108<br>10X0108<br>0 1 by sc<br>000001E                       | 1<br>3<br>3 (Example: Wooftware                                           |          | 1                 |           | 2         |           | ACK        | ( |

| ST                     | AD6 to AD0<br>▲1: IICSn regis<br>▲2: IICSn regis<br>ICCn.LRELn bit                                      | de<br>$R/\overline{W}$<br>ter = 10<br>ter = 01<br>t is set to<br>ter = 000<br>$\blacktriangle$ : Al                          | ACK<br>00X110E<br>10X010E<br>0 1 by sc<br>000001E                       | 1<br>3<br>3 (Example: W<br>oftware<br>3<br>enerated                       | /hen AL  | Dn bit is read d  |           | 2         |           | ĀĊŔ        | ક |

| ST                     | AD6 to AD0<br>▲1: IICSn regis<br>▲2: IICSn regis<br>ICCn.LRELn bit<br>∆ 3: IICSn regist                 | de<br>$R/\overline{W}$<br>ter = 10<br>ter = 01<br>t is set to $ter = 000\Delta: G$                                           | ACK<br>00X110E<br>10X010E<br>0 1 by so<br>000001E<br>Iways g<br>enerate | 1<br>3 (Example: W<br>oftware<br>3<br>enerated<br>ed only when            | /hen AL  | Dn bit is read d  |           | 2         |           | ACK        | 5 |

| ST                     | AD6 to AD0<br>▲ 1: IICSn regis<br>▲ 2: IICSn regis<br>ICCn.LRELn bit<br>Δ 3: IICSn regist<br>Remarks 1. | de<br>$R/\overline{W}$<br>ter = 10<br>ter = 01<br>t is set to<br>ter = 000<br>$\blacktriangle$ : Al<br>$\Delta$ : G<br>X: do | ACK<br>00X110E<br>10X010E<br>0 1 by sc<br>000001E                       | 1<br>3<br>3 (Example: Wo<br>oftware<br>3<br>enerated<br>ed only when<br>a | /hen AL  | Dn bit is read d  |           | 2         |           | ĀĊĸ        |   |

| Status During Arbitration                                                      | Interrupt Request Generation Timing                                                |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Transmitting address transmission                                              | At falling edge of eighth or ninth clock following byte transfer <sup>Note 1</sup> |

| Read/write data after address transmission                                     |                                                                                    |

| Transmitting extension code                                                    |                                                                                    |

| Read/write data after extension code transmission                              |                                                                                    |

| Transmitting data                                                              |                                                                                    |

| ACK transfer period after data reception                                       |                                                                                    |

| When restart condition is detected during data transfer                        |                                                                                    |

| When stop condition is detected during data transfer                           | When stop condition is generated (when IICCn.SPIEn bit = $1$ ) <sup>Note 2</sup>   |

| When SDA0n pin is low level while attempting to generate restart condition     | At falling edge of eighth or ninth clock following byte transfer <sup>Note 1</sup> |

| When stop condition is detected while attempting to generate restart condition | When stop condition is generated (when IICCn.SPIEn bit = $1$ ) <sup>Note 2</sup>   |

| When DSA0n pin is low level while attempting to generate stop condition        | At falling edge of eighth or ninth clock following byte transfer <sup>Note 1</sup> |

| When SCL0n pin is low level while attempting to generate restart condition     |                                                                                    |

Table 17-5. Status During Arbitration and Interrupt Request Signal Generation Timing

- **Notes 1.** When the IICCn.WTIMn bit = 1, an INTIICn signal occurs at the falling edge of the ninth clock. When the WTIMn bit = 0 and the extension code's slave address is received, an INTIICn signal occurs at the falling edge of the eighth clock (n = 0 to 2).

- When there is a possibility that arbitration will occur, set the SPIEn bit to 1 for master device operation (n = 0 to 2).

### 17.13 Wakeup Function

The I<sup>2</sup>C bus slave function is a function that generates an interrupt request signal (INTIICn) when a local address and extension code have been received.

This function makes processing more efficient by preventing unnecessary the INTIICn signal from occurring when addresses do not match.

When a start condition is detected, wakeup standby mode is set. This wakeup standby mode is in effect while addresses are transmitted due to the possibility that an arbitration loss may change the master device (which has generated a start condition) to a slave device.

However, when a stop condition is detected, the IICCn.SPIEn bit is set regardless of the wakeup function, and this determines whether INTIICn signal is enabled or disabled (n = 0 to 2).

# 17.15 Cautions

(1) When IICFn.STCENn bit = 0

Immediately after the  $l^2C0n$  operation is enabled, the bus communication status (IICFn.IICBSYn bit = 1) is recognized regardless of the actual bus status. To execute master communication in the status where a stop condition has not been detected, generate a stop condition and then release the bus before starting the master communication.

Use the following sequence for generating a stop condition.

<1> Set the IICCLn register. <2> Set the IICCn.IICEn bit.

- <3> Set the IICCn.SPTn bit.

- (2) When IICFn.STCENn bit = 1

Immediately after  $I^2COn$  operation is enabled, the bus released status (IICBSYn bit = 0) is recognized regardless of the actual bus status. To generate the first start condition (IICCn.STTn bit = 1), it is necessary to confirm that the bus has been released, so as to not disturb other communications.

- (3) When the IICCn.IICEn bit of the V850ES/JJ3 is set to 1 while communications among other devices are in progress, the start condition may be detected depending on the status of the communication line. Be sure to set the IICCn.IICEn bit to 1 when the SCL0n and SDA0n lines are high level.

- (4) Determine the operation clock frequency by the IICCLn, IICXn, and OCKSm registers before enabling the operation (IICCn.IICEn bit = 1). To change the operation clock frequency, clear the IICCn.IICEn bit to 0 once.

- (5) After the IICCn.STTn and IICCn.SPTn bits have been set to 1, they must not be re-set without being cleared to 0 first.

- (6) If transmission has been reserved, set the IICCN.SPIEn bit to 1 so that an interrupt request is generated by the detection of a stop condition. After an interrupt request has been generated, the wait state will be released by writing communication data to I<sup>2</sup>Cn, then transferring will begin. If an interrupt is not generated by the detection of a stop condition, transmission will halt in the wait state because an interrupt request was not generated. However, it is not necessary to set the SPIEn bit to 1 for the software to detect the IICSn.MSTSn bit.

$\begin{array}{ll} \textbf{Remark} & n=0 \text{ to } 2 \\ & m=0, \ 1 \end{array}$

## 18.10 DMA Abort Factors

DMA transfer is aborted if a bus hold occurs.

The same applies if transfer is executed between the internal memory/on-chip peripheral I/O and internal memory/on-chip peripheral I/O.

When the bus hold is cleared, DMA transfer is resumed.

# 18.11 End of DMA Transfer

When DMA transfer has been completed the number of times set to the DBCn register and when the DCHCn.Enn bit is cleared to 0 and TCn bit is set to 1, a DMA transfer end interrupt request signal (INTDMAn) is generated for the interrupt controller (INTC) (n = 0 to 3).

The V850ES/JJ3 does not output a terminal count signal to an external device. Therefore, confirm completion of DMA transfer by using the DMA transfer end interrupt or polling the TCn bit.

### 18.12 Operation Timing

Figures 18-1 to 18-4 show DMA operation timing.

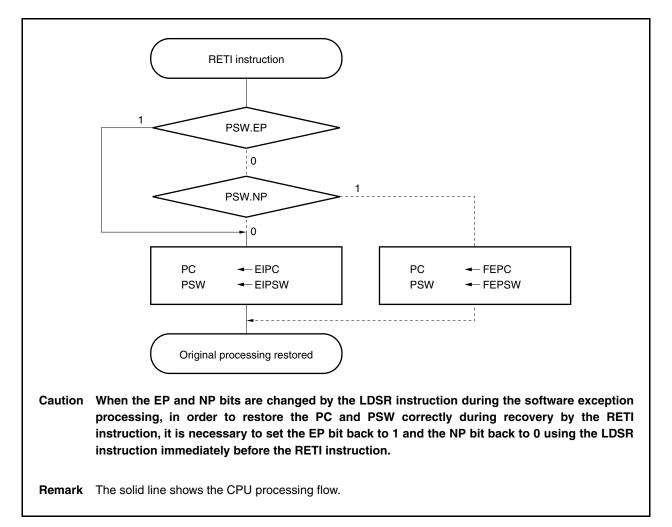

#### 19.4.2 Restore

Restoration from software exception processing is carried out by the RETI instruction.

By executing the RETI instruction, the CPU carries out the following processing and shifts control to the restored PC's address.

- <1> Loads the restored PC and PSW from EIPC and EIPSW because the PSW.EP bit is 1.

- <2> Transfers control to the address of the restored PC and PSW.

The processing of the RETI instruction is shown below.

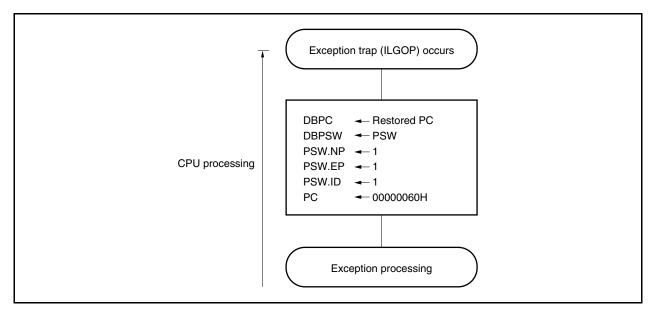

### 19.5 Exception Trap

An exception trap is an interrupt that is requested when the illegal execution of an instruction takes place. In the V850ES/JJ3, an illegal opcode exception (ILGOP: Illegal Opcode Trap) is considered as an exception trap.

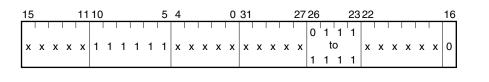

#### 19.5.1 Illegal opcode definition

The illegal instruction has an opcode (bits 10 to 5) of 111111B, a sub-opcode (bits 26 to 23) of 0111B to 1111B, and a sub-opcode (bit 16) of 0B. An exception trap is generated when an instruction applicable to this illegal instruction is executed.

x: Arbitrary

Caution Since it is possible to assign this instruction to an illegal opcode in the future, it is recommended that it not be used.

#### (1) Operation

If an exception trap occurs, the CPU performs the following processing, and transfers control to the handler routine.

- <1> Saves the restored PC to DBPC.

- <2> Saves the current PSW to DBPSW.

- <3> Sets the PSW.NP, PSW.EP, and PSW.ID bits to 1.

- <4> Sets the handler address (00000060H) corresponding to the exception trap to the PC, and transfers control.

The processing of the exception trap is shown below.

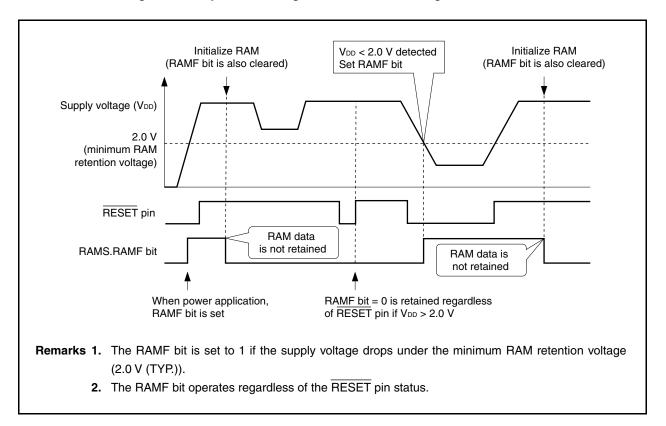

# 24.5 RAM Retention Voltage Detection Operation

The supply voltage and detected voltage are compared. When the supply voltage drops below the detected voltage (including on power application), the RAMS.RAMF bit is set to 1.

| Function         | Functional Outline                                                                                                                                                              | Support (√: Suppor                | ted, ×: Not supported)                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------|

|                  |                                                                                                                                                                                 | On-Board/Off-Board<br>Programming | Self Programming                                                           |

| Blank check      | The erasure status of the entire memory is checked.                                                                                                                             | N                                 | $\checkmark$                                                               |

| Chip erasure     | The contents of the entire memory area are erased all at once.                                                                                                                  | $\checkmark$                      | × <sup>Note</sup>                                                          |

| Block erasure    | The contents of specified memory blocks are erased.                                                                                                                             | N                                 | $\checkmark$                                                               |

| Program          | Writing to specified addresses, and a verify check to see if write level is secured are performed.                                                                              | N                                 | $\checkmark$                                                               |

| Verify/checksum  | Data read from the flash memory is<br>compared with data transferred from the<br>flash memory programmer.                                                                       | N                                 | ×<br>(Can be read by user<br>program)                                      |

| Read             | Data written to the flash memory is read.                                                                                                                                       | $\checkmark$                      | ×                                                                          |

| Security setting | Use of the chip erase command, block<br>erase command, program command, and<br>read command can be prohibited, and<br>rewriting of the boot block cluster can be<br>prohibited. | $\checkmark$                      | ×<br>(Supported only when setting<br>is changed from enable to<br>disable) |

Table 27-2. Basic Functions

Note This is possible by selecting the entire memory area for the block erase function.

The following table lists the security functions. The chip erase command prohibit, block erase command prohibit, program command prohibit, read command prohibit, and rewriting boot block cluster prohibit functions are enabled by default after shipment, and security can be set by rewriting via on-board/off-board programming. Each security function can be used in combination with the others at the same time.

#### Table 27-3. Security Functions

| Function                              | Functional Outline                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip erase command prohibit           | Execution of chip erase and block erase commands on all of the blocks is prohibited. Once prohibition is set, all of the settings of prohibition cannot be initialized because the chip erase command cannot be executed.                                                                                                                                                        |

| Block erase command prohibit          | Execution of a block erase command on all of the blocks is prohibited. Setting of prohibition can be initialized by execution of a chip erase command.                                                                                                                                                                                                                           |

| Program command prohibit              | Execution of program and block erase commands on all of the blocks is prohibited. Setting of prohibition can be initialized by execution of the chip erase command.                                                                                                                                                                                                              |

| Read command prohibit                 | Execution of a read command on all of the blocks is prohibited. Setting of the prohibition can be initialized by execution of the chip erase command.                                                                                                                                                                                                                            |

| Rewriting boot block cluster prohibit | Boot block clusters in block 0 to the specified block can be protected. Rewriting (erasing and writing) the protected boot block clusters is disabled. Even if the chip erase command is executed, setting of prohibition cannot be initialized.<br>The maximum number of specifiable blocks is as follows.<br>384 KB version: 95 blocks<br>512/768/1024 KB versions: 127 blocks |

| After res                                           | set: 01H <sup>Note</sup> | R/W                                                                                                                                  | Address                                                                                                                                            | s: FFFFF9F             | сн                              |                       |             |           |  |

|-----------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|-----------------------|-------------|-----------|--|

|                                                     | 7                        | 6                                                                                                                                    | 5                                                                                                                                                  | 4                      | 3                               | 2                     | 1           | <0>       |  |

| OCDM                                                | 0                        | 0                                                                                                                                    | 0                                                                                                                                                  | 0                      | 0                               | 0                     | 0           | OCDM0     |  |

|                                                     |                          |                                                                                                                                      |                                                                                                                                                    |                        |                                 |                       |             |           |  |

|                                                     | OCDM0                    | Operation mode                                                                                                                       |                                                                                                                                                    |                        |                                 |                       |             |           |  |

|                                                     | 0                        |                                                                                                                                      | ormal oper                                                                                                                                         |                        |                                 |                       |             | -         |  |

|                                                     |                          |                                                                                                                                      | as on-chip debug function pin is used as a port/peripheral function pin) and disconnects the on-chip pull-down resistor of the P05/INTP2/DRST pin. |                        |                                 |                       |             |           |  |

|                                                     | 1                        |                                                                                                                                      | RST pin is I                                                                                                                                       |                        |                                 |                       |             |           |  |

|                                                     |                          |                                                                                                                                      | pperation m                                                                                                                                        |                        | ich a pin th                    | at function           | s alternate | ly as an  |  |

|                                                     |                          |                                                                                                                                      | debug funct                                                                                                                                        |                        | sed as a p                      | ort/periphe           | ral functio | n pin)    |  |

|                                                     |                          |                                                                                                                                      | RST pin is ł<br>debug mod                                                                                                                          | -                      | a nin that                      | functions a           | lternately  | as an     |  |

|                                                     |                          | -                                                                                                                                    | debug funct                                                                                                                                        |                        |                                 |                       | -           |           |  |

| ● Input<br>● Set th<br><1> C<br><2> Fi<br>2. The DR | ST pin ha                | el to the F<br>) bit. In th<br>)CDM0 bi<br>5/INTP2/D<br>as an on                                                                     | P05/INTP2<br>his case,<br>it to 0.<br>PRST pin t<br>-chip pul                                                                                      | 2/DRST p<br>take the t | in.<br>following<br>rel until < | actions.<br>1> is con | npleted.    | isconnect |  |

|                                                     | DRST                     | /INTP2/DRST pin to low level until <1> is completed.<br>s an on-chip pull-down resistor. This resistor is disconnected<br>ared to 0. |                                                                                                                                                    |                        |                                 |                       |             |           |  |