Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 128                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 60K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3746gj-gae-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 22.2    | Regist | ers to Check Reset Source               |     |

|---------|--------|-----------------------------------------|-----|

| 22.3    | Operat | tion                                    |     |

|         | 22.3.1 | Reset operation via RESET pin           |     |

|         | 22.3.2 | Reset operation by watchdog timer 2     |     |

|         | 22.3.3 | Reset operation by low-voltage detector | 717 |

|         | 22.3.4 | Operation after reset release           | 718 |

|         | 22.3.5 | Reset function operation flow           | 719 |

|         |        |                                         |     |

| CHAPTER | 23 CI  | LOCK MONITOR                            |     |

| 23.1    | Functi | ons                                     |     |

| 23.2    | Config | juration                                |     |

| 23.3    | Regist | er                                      |     |

| 23.4    | Operat | tion                                    |     |

|         |        |                                         |     |

|         |        | DW-VOLTAGE DETECTOR (LVI)               |     |

| 24.1    |        | ons                                     |     |

| 24.2    |        | juration                                |     |

| 24.3    | •      | ers                                     |     |

| 24.4    | •      | tion                                    |     |

|         | 24.4.1 | To use for internal reset signal        |     |

|         | 24.4.2 | To use for interrupt                    |     |

| 24.5    |        | Retention Voltage Detection Operation   |     |

| 24.6    | Emula  | tion Function                           |     |

| CHAPTER | 25 CI  | RC FUNCTION                             |     |

| 25.1    |        | ons                                     |     |

| 25.2    |        | juration                                |     |

| 25.3    |        | ers                                     |     |

| 25.4    | -      | tion                                    |     |

| 25.5    | •      | Method                                  |     |

| _0.0    | Cougo  |                                         |     |

| CHAPTER | 26 RI  | EGULATOR                                |     |

| 26.1    | Overvi | ew                                      |     |

| 26.2    | Operat | tion                                    |     |

|         | 07 51  | ASH MEMORY                              | 700 |

| 27.1    |        |                                         |     |

| 27.1    |        | ry Configuration                        |     |

| 27.2    |        | onal Outline                            |     |

| 27.3    |        | ing by Dedicated Flash Programmer       |     |

| 27.4    | 27.4.1 |                                         |     |

|         |        | Programming environment                 |     |

|         | 27.4.2 | Communication mode                      |     |

|         | 27.4.3 | Flash memory control                    |     |

|         | 27.4.4 | Selection of communication mode         |     |

|         | 27.4.5 | Communication commands                  | -   |

| <u></u> | 27.4.6 | Pin connection                          |     |

| 27.5    |        | ing by Self Programming                 |     |

|         | 27.5.1 | Overview                                |     |

|         | 27.5.2 | Features                                |     |

|         | 27.5.3 | Standard self programming flow          |     |

|         | 27.5.4 | Flash functions                         |     |

# (3) Port 8 mode control register (PMC8)

|           | 7         | R/W                                          | Address: F                              | 4                                     | 3       | 2         | 1          | 0         |                                   |  |

|-----------|-----------|----------------------------------------------|-----------------------------------------|---------------------------------------|---------|-----------|------------|-----------|-----------------------------------|--|

| PMC8      | 0         | 0                                            | 0                                       | 0                                     | 0       | 0         | PMC81      | PMC80     |                                   |  |

|           |           |                                              |                                         | · · · · · · · · · · · · · · · · · · · |         |           | •          |           | 1                                 |  |

|           | PMC81     | IC81 Specification of P81 pin operation mode |                                         |                                       |         |           |            |           |                                   |  |

|           | 0         | 0 I/O port                                   |                                         |                                       |         |           |            |           |                                   |  |

|           | 1         | TXDA3 output                                 |                                         |                                       |         |           |            |           |                                   |  |

|           | PMC80     |                                              | Specification of P80 pin operation mode |                                       |         |           |            |           |                                   |  |

|           | 0         | I/O port                                     | /O port                                 |                                       |         |           |            |           |                                   |  |

|           | 1         | RXDA3 ir                                     | nput/INTP8 <sup>N</sup>                 | <sup>lote</sup> input                 |         |           |            |           |                                   |  |

| detection | of the ed | ge of the                                    | INTP8 pi                                |                                       | NTF80 b | it = 0 ar | id INTR8.I | NTR80 bit | 3 pin, disal<br>t = 0). Wh<br>0). |  |

# (4) Port 8 function register (PF8)

|                                                                   | PF80                                                            |      | 1 | 3 | 4 | 5 | 6 | / |     |

|-------------------------------------------------------------------|-----------------------------------------------------------------|------|---|---|---|---|---|---|-----|

|                                                                   | 1100                                                            | PF81 | 0 | 0 | 0 | 0 | 0 | 0 | PF8 |

|                                                                   |                                                                 | •    | • |   |   |   |   |   |     |

| PF8n Control of normal output or N-ch open-drain output (n = 0, 1 | Control of normal output or N-ch open-drain output $(n = 0, 1)$ |      |   |   |   |   |   |   |     |

| 0 Normal output (CMOS output)                                     | Normal output (CMOS output)                                     |      |   |   |   |   |   | 0 |     |

| 1 N-ch open-drain output                                          | 1 N-ch open-drain output                                        |      |   |   |   |   |   | 1 |     |

| I | <                       |

|---|-------------------------|

| I | $\overline{\mathbf{m}}$ |

| I | ы<br>Сп                 |

|   | Š.                      |

| I | Ĭ                       |

|   |                         |

| I | Ś                       |

|   | 2                       |

|   | <u>ب</u>                |

| I | ω                       |

|   |                         |

R01UT0016EJ0400 Rev.4.00 Sep 30, 2010

| Pin Name |                       | Function   | Pnx Bit of<br>Pn Register   | PMnx Bit of<br>PMn Register  | PMCnx Bit of<br>PMCn Register | PFCEnx Bit of<br>PFCEn Register | PFCnx Bit of<br>PFCn Register | Other Bits<br>(Registers)  |

|----------|-----------------------|------------|-----------------------------|------------------------------|-------------------------------|---------------------------------|-------------------------------|----------------------------|

|          | Name                  | I/O        | FILLE                       |                              | FINICIT REGISTER              |                                 |                               | (negisiers)                |

| PCM0     | WAIT                  | Input      | PCM0 = Setting not required | PMCM0 = Setting not required | PMCCM0 = 1                    | -                               | -                             |                            |

| PCM1     | CLKOUT                | Output     | PCM1 = Setting not required | PMCM1 = Setting not required | PMCCM1 = 1                    | _                               | -                             |                            |

| PCM2     | HLDAK                 | Output     | PCM2 = Setting not required | PMCM2 = Setting not required | PMCCM2 = 1                    | _                               | -                             |                            |

| PCM3     | HLDRQ                 | Input      | PCM3 = Setting not required | PMCM3 = Setting not required | PMCCM3 = 1                    | -                               | -                             |                            |

| PCT0     | WR0                   | Output     | PCT0 = Setting not required | PMCT0 = Setting not required | PMCCT0 = 1                    | -                               | -                             |                            |

| PCT1     | WR1                   | Output     | PCT1 = Setting not required | PMCT1 = Setting not required | PMCCT1 = 1                    | -                               | -                             |                            |

| PCT4     | RD                    | Output     | PCT4 = Setting not required | PMCT4 = Setting not required | PMCCT4 = 1                    | -                               | _                             |                            |

| PCT6     | ASTB                  | Output     | PCT6 = Setting not required | PMCT6 = Setting not required | PMCCT6 = 1                    | -                               | -                             |                            |

| PDH0     | A16                   | Output     | PDH0 = Setting not required | PMDH0 = Setting not required | PMCDH0 = 1                    | -                               | _                             |                            |

| PDH1     | A17                   | Output     | PDH1 = Setting not required | PMDH1 = Setting not required | PMCDH1 = 1                    | -                               | -                             |                            |

| PDH2     | A18                   | Output     | PDH2 = Setting not required | PMDH2 = Setting not required | PMCDH2 = 1                    | _                               | -                             |                            |

| PDH3     | A19                   | Output     | PDH3 = Setting not required | PMDH3 = Setting not required | PMCDH3 = 1                    | -                               | -                             |                            |

| PDH4     | A20                   | Output     | PDH4 = Setting not required | PMDH4 = Setting not required | PMCDH4 = 1                    | _                               | -                             |                            |

| PDH5     | A21                   | Output     | PDH5 = Setting not required | PMDH5 = Setting not required | PMCDH5 = 1                    | _                               | -                             |                            |

| PDH6     | A22                   | Output     | PDH6 = Setting not required | PMDH6 = Setting not required | PMCDH6 = 1                    | -                               | -                             |                            |

| PDH7     | A23                   | Output     | PDH7 = Setting not required | PMDH7 = Setting not required | PMCDH7 = 1                    | _                               | -                             |                            |

| PDL0     | AD0                   | I/O        | PDL0 = Setting not required | PMDL0 = Setting not required | PMCDL0 = 1                    | _                               | -                             |                            |

| PDL1     | AD1                   | I/O        | PDL1 = Setting not required | PMDL1 = Setting not required | PMCDL1 = 1                    | _                               | _                             |                            |

| PDL2     | AD2                   | I/O        | PDL2 = Setting not required | PMDL2 = Setting not required | PMCDL2 = 1                    | _                               | -                             |                            |

| PDL3     | AD3                   | I/O        | PDL3 = Setting not required | PMDL3 = Setting not required | PMCDL3 = 1                    | _                               | _                             |                            |

| PDL4     | AD4                   | I/O        | PDL4 = Setting not required | PMDL4 = Setting not required | PMCDL4 = 1                    | _                               | _                             |                            |

| PDL5     | AD5                   | I/O        | PDL5 = Setting not required | PMDL5 = Setting not required | PMCDL5 = 1                    | _                               | _                             |                            |

|          | FLMD1 <sup>Note</sup> | Input      | PDL5 = Setting not required | PMDL5 = Setting not required | PMCDL5 = Setting not required | _                               | _                             |                            |

| PDL6     | AD6                   | I/O        | PDL6 = Setting not required | PMDL6 = Setting not required | PMCDL6 = 1                    | _                               | _                             |                            |

| PDL7     | AD7                   | I/O        | PDL7 = Setting not required | PMDL7 = Setting not required | PMCDL7 = 1                    | _                               | _                             |                            |

| Since t  | his pin is :          | set in the | flash memory progra         | mming mode, it doe           | s not need to be mai          | nipulated with the p            | ort control register. For     | details, see CHAPTER 27 FL |

#### Table 4-19. Using Port Pins as Alternate-Function Pins (7/8)

# 6.3 Registers

# (1) Processor clock control register (PCC)

The PCC register is a special register. Data can be written to this register only in combination of specific sequences (see **3.4.7 Special registers**).

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 03H.

| After re     | set: 00H | R/W                                                  | Address: 7                                                                                                                                                                                                                                                                                     | POCTL1                                                              | FFFFF59                                            | 1H, TP1CTL                                                 | 1 FFFFF                                                           | 5A1H,                                                                                                      |  |  |

|--------------|----------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

|              |          |                                                      | ٦                                                                                                                                                                                                                                                                                              | P2CTL1                                                              | FFFFF5B                                            | 1H, TP3CTL                                                 | 1 FFFFF                                                           | 5C1H,                                                                                                      |  |  |

|              |          |                                                      | ٦                                                                                                                                                                                                                                                                                              | FP4CTL1                                                             | FFFFF5D                                            | 1H, TP5CTI                                                 | _1 FFFFF                                                          | 5E1H,                                                                                                      |  |  |

|              |          |                                                      | ٦                                                                                                                                                                                                                                                                                              | P6CTL1                                                              | FFFFF5F                                            | 1H, TP7CTL                                                 | 1 FFFFF                                                           | 601H,                                                                                                      |  |  |

|              |          |                                                      | ٦                                                                                                                                                                                                                                                                                              | FP8CTL1                                                             | FFFFF61                                            | 1H                                                         |                                                                   |                                                                                                            |  |  |

|              | 7        | <6>                                                  | <5>                                                                                                                                                                                                                                                                                            | 4                                                                   | 3                                                  | 2                                                          | 1                                                                 | 0                                                                                                          |  |  |

| TPnCTL1      | 0        | TPnEST                                               | TPnEEE                                                                                                                                                                                                                                                                                         | 0                                                                   | 0                                                  | TPnMD2                                                     | TPnMD1                                                            | TPnMD0                                                                                                     |  |  |

| (n = 0 to 8) |          |                                                      |                                                                                                                                                                                                                                                                                                |                                                                     |                                                    |                                                            |                                                                   |                                                                                                            |  |  |

|              | TPnEST   |                                                      |                                                                                                                                                                                                                                                                                                | Softw                                                               | are trigge                                         | r control                                                  |                                                                   |                                                                                                            |  |  |

|              | 0        |                                                      |                                                                                                                                                                                                                                                                                                |                                                                     | -                                                  |                                                            |                                                                   |                                                                                                            |  |  |

|              | 1        | <ul> <li>In one-s</li> </ul>                         | Generate a valid signal for external trigger input.<br>In one-shot pulse output mode: A one-shot pulse is output with writing<br>1 to the TPnEST bit as the trigger.<br>In external trigger pulse output mode: A PWM waveform is output with<br>writing 1 to the TPnEST bit as the<br>trigger. |                                                                     |                                                    |                                                            |                                                                   |                                                                                                            |  |  |

|              | TPnEEE   |                                                      |                                                                                                                                                                                                                                                                                                | Cour                                                                | nt clock se                                        |                                                            |                                                                   |                                                                                                            |  |  |

|              | 0        | Disable or                                           | peration wit                                                                                                                                                                                                                                                                                   |                                                                     |                                                    |                                                            |                                                                   |                                                                                                            |  |  |

|              | 0        | (Perform o                                           | Disable operation with external event count input.<br>Perform counting with the count clock selected by the TPnCTL0.TPnCK0<br>D TPnCK2 bits.)                                                                                                                                                  |                                                                     |                                                    |                                                            |                                                                   |                                                                                                            |  |  |

|              | 1        |                                                      | peration with counting at                                                                                                                                                                                                                                                                      |                                                                     |                                                    | int input.<br>e external ev                                | vent count                                                        | input                                                                                                      |  |  |

|              | TPnMD2   | TPnMD1                                               | TPnMD0                                                                                                                                                                                                                                                                                         |                                                                     | Tim                                                | ner mode sel                                               | action                                                            |                                                                                                            |  |  |

|              | 0        | 0                                                    | 0                                                                                                                                                                                                                                                                                              | Interval                                                            | timer moc                                          |                                                            | COLIDIT                                                           |                                                                                                            |  |  |

|              | 0        | 0                                                    | 1                                                                                                                                                                                                                                                                                              |                                                                     | event co                                           | -                                                          |                                                                   |                                                                                                            |  |  |

|              | 0        | 1                                                    | 0                                                                                                                                                                                                                                                                                              |                                                                     |                                                    | ulse output n                                              | node                                                              |                                                                                                            |  |  |

|              | 0        | 1                                                    | 1                                                                                                                                                                                                                                                                                              |                                                                     |                                                    | utput mode                                                 |                                                                   |                                                                                                            |  |  |

|              | 1        | 0                                                    | 0                                                                                                                                                                                                                                                                                              |                                                                     | Itput mod                                          | •                                                          |                                                                   |                                                                                                            |  |  |

|              | 1        | 0                                                    | 1                                                                                                                                                                                                                                                                                              |                                                                     | ning time                                          |                                                            |                                                                   |                                                                                                            |  |  |

|              | 1        | 1                                                    | 0                                                                                                                                                                                                                                                                                              |                                                                     | •                                                  | urement mo                                                 | de                                                                |                                                                                                            |  |  |

|              | 1        | 1                                                    | 1                                                                                                                                                                                                                                                                                              | Setting                                                             | prohibited                                         |                                                            |                                                                   |                                                                                                            |  |  |

|              | Cautions | mode<br>to thi<br>2. Exter<br>mode<br>3. Set<br>TPnC | e or one-s<br>s bit is ig<br>nal event<br>regardle<br>the TPn<br>CTL0.TPn(                                                                                                                                                                                                                     | whot puls<br>nored.<br>t count i<br>ss of the<br>EEE ar<br>CE bit = | e outpu<br>nput is<br>value o<br>nd TPn<br>0. (The | t mode. I<br>selected<br>of the TPnE<br>MD2 to<br>same val | n any ot<br>in the ex<br>EE bit.<br>TPnMD<br>ue can b<br>uarantee | rigger pulse ou<br>her mode, writi<br>xternal event c<br>0 bits when<br>be written wher<br>d when rewritir |  |  |

|              |          |                                                      |                                                                                                                                                                                                                                                                                                | ь. н. —                                                             |                                                    |                                                            | e                                                                 | ng was mistak                                                                                              |  |  |

RENESAS

# 8.3 Configuration

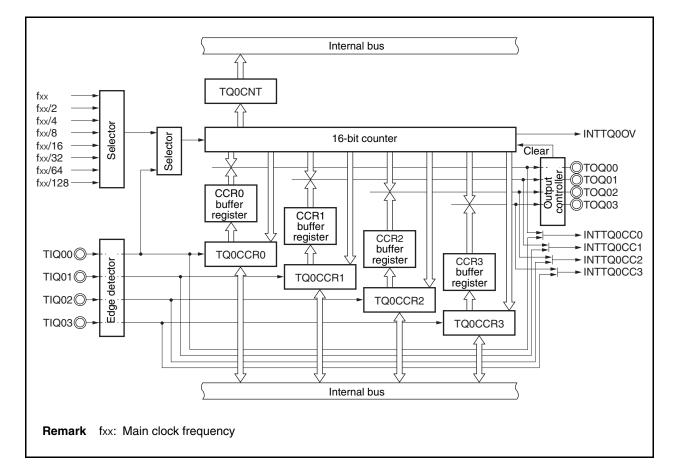

TMQ0 includes the following hardware.

| Item                                | Configuration                                                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Timer register                      | 16-bit counter                                                                                                                               |

| Registers                           | TMQ0 capture/compare registers 0 to 3 (TQ0CCR0 to TQ0CCR3)<br>TMQ0 counter read buffer register (TQ0CNT)<br>CCR0 to CCR3 buffer registers    |

| Timer inputs                        | 4 (TIQ00 <sup>Note 1</sup> to TIQ03 pins)                                                                                                    |

| Timer outputs                       | 4 (TOQ00 to TOQ03 pins)                                                                                                                      |

| Control registers <sup>Note 2</sup> | TMQ0 control registers 0, 1 (TQ0CTL0, TQ0CTL1)<br>TMQ0 I/O control registers 0 to 2 (TQ0IOC0 to TQ0IOC2)<br>TMQ0 option register 0 (TQ0OPT0) |

#### Table 8-1. Configuration of TMQ0

- **Notes 1.** The TIQ00 pin functions alternately as a capture trigger input signal, external event count input signal, and external trigger input signal.

- 2. When using the functions of the TIQ00 to TIQ03 and TOQ00 to TOQ03 pins, see Table 4-19 Using Port Pins as Alternate-Function Pins.

| Figure | 8-1. | Block | Diagram | of TMQ0 |

|--------|------|-------|---------|---------|

|        |      |       |         | ••••••  |

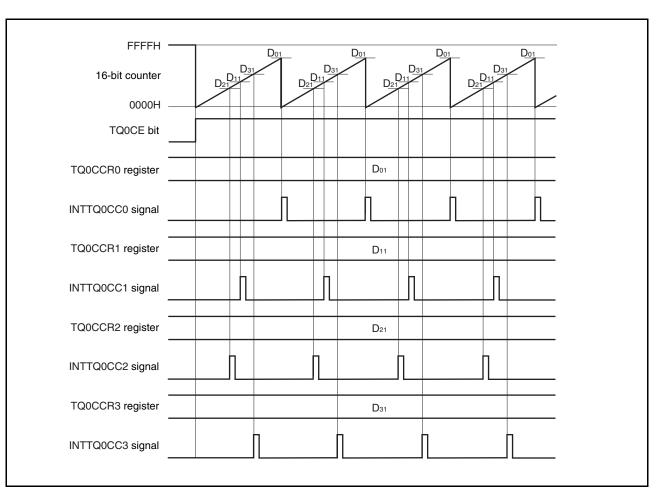

If the set value of the TQ0CCRk register is smaller than the set value of the TQ0CCR0 register, the INTTQ0CCk signal is generated once per cycle.

# **Remark** k = 1 to 3

#### Figure 8-14. Timing Chart When $D_{01} \ge D_{k1}$

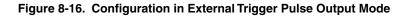

# 8.5.3 External trigger pulse output mode (TQ0MD2 to TQ0MD0 bits = 010)

In the external trigger pulse output mode, 16-bit timer/event counter Q waits for a trigger when the TQ0CTL0.TQ0CE bit is set to 1. When the valid edge of an external trigger input signal is detected, 16-bit timer/event counter Q starts counting, and outputs a PWM waveform from the TOQ01 to TOQ03 pins.

Pulses can also be output by generating a software trigger instead of using the external trigger. When using a software trigger, a square wave that has one cycle of the PWM waveform as half its cycle can also be output from the TOQ00 pin.

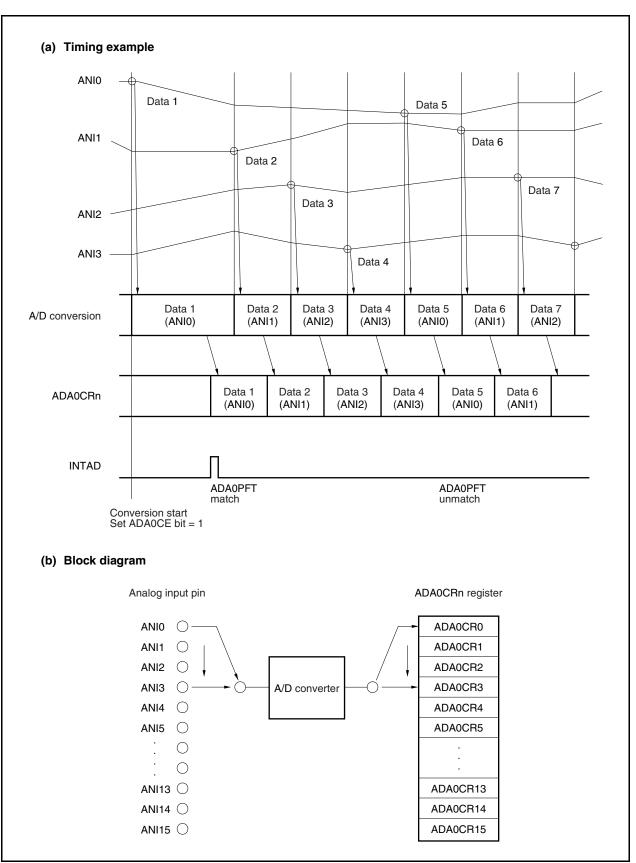

# CHAPTER 13 A/D CONVERTER

#### 13.1 Overview

The A/D converter converts analog input signals into digital values, has a resolution of 10 bits, and can handle 16 analog input signal channels (ANI0 to ANI15).

The A/D converter has the following features.

- 10-bit resolution

- 16 channels

- $\bigcirc$  Successive approximation method

- Operating voltage: AVREF0 = 3.0 to 3.6 V

- Analog input voltage: 0 V to AVREF0

- $\bigcirc$  The following functions are provided as operation modes.

- Continuous select mode

- Continuous scan mode

- One-shot select mode

- One-shot scan mode

- $\bigcirc\,$  The following functions are provided as trigger modes.

- Software trigger mode

- External trigger mode (external, 1)

- Timer trigger mode

- Power-fail monitor function (conversion result compare function)

# 13.2 Functions

#### (1) 10-bit resolution A/D conversion

An analog input channel is selected from ANI0 to ANI15, and an A/D conversion operation is repeated at a resolution of 10 bits. Each time A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

#### (2) Power-fail detection function

This function is used to detect a drop in the battery voltage. The result of A/D conversion (the value of the ADA0CRnH register) is compared with the value of the ADA0PFT register, and the INTAD signal is generated only when a specified comparison condition is satisfied (n = 0 to 15).

## (1) Successive approximation register (SAR)

The SAR register compares the voltage value of the analog input signal with the output voltage (compare voltage) value of the compare voltage generation DAC, and holds the comparison result starting from the most significant bit (MSB).

When the comparison result has been held down to the least significant bit (LSB) (i.e., when A/D conversion is complete), the contents of the SAR register are transferred to the ADA0CRn register.

**Remark** n = 0 to 15

#### (2) A/D conversion result register n (ADA0CRn), A/D conversion result register nH (ADA0CRnH)

The ADA0CRn register is a 16-bit register that stores the A/D conversion result. ADA0ARn consist of 16 registers and the A/D conversion result is stored in the 10 higher bits of the AD0CRn register corresponding to analog input. (The lower 6 bits are fixed to 0.)

#### (3) A/D converter mode register 0 (ADA0M0)

This register specifies the operation mode and controls the conversion operation by the A/D converter.

## (4) A/D converter mode register 1 (ADA0M1)

This register sets the conversion time of the analog input signal to be converted.

- (5) A/D converter mode register 2 (ADA0M2) This register sets the hardware trigger mode.

- (6) A/D converter channel specification register (ADA0S) This register sets the input port that inputs the analog voltage to be converted.

#### (7) Power-fail compare mode register (ADA0PFM)

This register sets the power-fail monitor mode.

#### (8) Power-fail compare threshold value register (ADA0PFT)

The ADA0PFT register sets a threshold value that is compared with the value of A/D conversion result register nH (ADA0CRnH). The 8-bit data set to the ADA0PFT register is compared with the higher 8 bits of the A/D conversion result register (ADA0CRnH).

#### (9) Controller

The controller compares the result of the A/D conversion (the value of the ADA0CRnH register) with the value of the ADA0PFT register when A/D conversion is completed or when the power-fail detection function is used, and generates the INTAD signal only when a specified comparison condition is satisfied.

#### (10) Sample & hold circuit

The sample & hold circuit samples each of the analog input signals selected by the input circuit and sends the sampled data to the voltage comparator. This circuit also holds the sampled analog input signal voltage during A/D conversion.

#### (11) Voltage comparator

The voltage comparator compares a voltage value that has been sampled and held with the output voltage value of the compare voltage generation DAC.

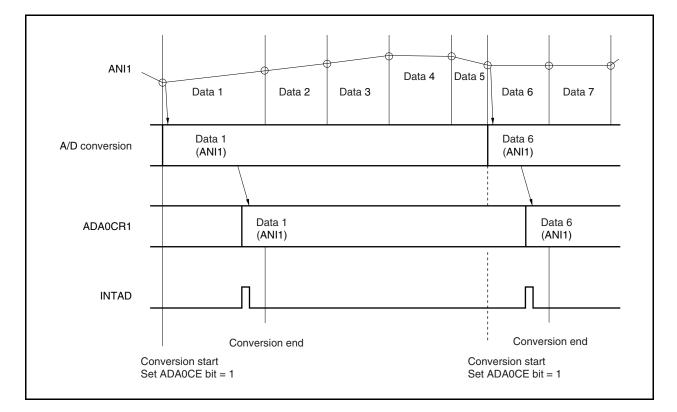

## (3) One-shot select mode

In this mode, the voltage on the analog input pin specified by the ADA0S register is converted into a digital value only once.

The conversion result is stored in the ADA0CRn register corresponding to the analog input pin. In this mode, an analog input pin and an ADA0CRn register correspond on a one-to-one basis. When A/D conversion has been completed once, the INTAD signal is generated. The A/D conversion operation is stopped after it has been completed (n = 0 to 15).

Figure 13-6. Timing Example of One-Shot Select Mode Operation (ADA0S Register = 01H)

#### (4) One-shot scan mode

In this mode, analog input pins are sequentially selected, from the ANIO pin to the pin specified by the ADAOS register, and their values are converted into digital values.

Each conversion result is stored in the ADA0CRn register corresponding to the analog input pin. When conversion of the analog input pin specified by the ADA0S register is complete, the INTAD signal is generated. A/D conversion is stopped after it has been completed (n = 0 to 15).

(4/4)

| 0                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | o condition trigger                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                         | Stop condition is not generated.                                                                                                                                                                                                                                                                                                                                                                                                                                              | Stop condition is not generated.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 1                                                                                                       | Stop condition is generated (termination of master device's transfer).<br>After the SDA0n line goes to low level, either set the SCL0n line to high level or wait until the SCL0n<br>pin goes to high level. Next, after the rated amount of time has elapsed, the SDA0n line is changed<br>from low level to high level and a stop condition is generated.                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| For master<br>For master<br>• Cannot b<br>• The SPT<br>• When the<br>eight cloo<br>The WTII<br>SPTn bit | Can be set to 1 only when the A<br>after the slave has been notified<br>transmission: A stop condition cannot be gen<br>1 during the wait period that fo<br>be set to 1 at the same time as the STTn bit.<br>In bit can be set to 1 only when in master mode<br>e WTIMn bit has been set to 0, if the SPTn bit is<br>cks, note that a stop condition will be generated<br>Mn bit should be changed from 0 to 1 during the<br>should be set to 1 during the wait period that f | ACKEn bit has been set to 0 and during the wait period<br>d of final reception.<br>erated normally during the ACK reception period. Set to<br>llows output of the ninth clock.<br>a <sup>Note</sup> .<br>is set to 1 during the wait period that follows output of<br>d during the high-level period of the ninth clock.<br>ne wait period following output of eight clocks, and the |  |  |  |  |  |

| Condition f                                                                                             | or clearing (SPTn bit = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Condition for setting (SPTn bit = 1)                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| <ul><li>Automation</li><li>When the</li></ul>                                                           | by loss in arbitration<br>cally cleared after stop condition is detected<br>e LRELn bit = 1 (communication save)<br>e IICEn bit = 0 (operation stop)<br>et                                                                                                                                                                                                                                                                                                                    | Set by instruction                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ote Set t                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | wever, when the IICRSVn bit is 0, the SPTn bit mus<br>e first stop condition is detected following the switc                                                                                                                                                                                                                                                                         |  |  |  |  |  |

**Remarks 1.** The SPTn bit is 0 if it is read immediately after data setting. **2.** n = 0 to 2

impedance.

| Address   | Register          |                   |                   |   | E | Bit |                     |                     |                     |

|-----------|-------------------|-------------------|-------------------|---|---|-----|---------------------|---------------------|---------------------|

|           |                   | <7>               | <6>               | 5 | 4 | 3   | 2                   | 1                   | 0                   |

| FFFFF162H | UA0RIC/<br>CB4RIC | UA0RIF/<br>CB4RIF | UA0RMK/<br>CB4RMK | 0 | 0 | 0   | UA0RPR2/<br>CB4RPR2 | UA0RPR1/<br>CB4RPR1 | UA0RPR0/<br>CB4RPR0 |

| FFFFF164H | UA0TIC/<br>CB4TIC | UA0TIF/<br>CB4TIF | UA0TMK/<br>CB4TMK | 0 | 0 | 0   | UA0TPR2/<br>CB4TPR2 | UA0TPR1/<br>CB4TPR1 | UA0TPR0/<br>CB4TPR0 |

| FFFFF166H | UA1RIC/<br>IICIC2 | UA1RIF/<br>IICIF2 | UA1RMK/<br>IICMK2 | 0 | 0 | 0   | UA1RPR2/<br>IICPR22 | UA1RPR1/<br>IICPR21 | UA1RPR0/<br>IICPR20 |

| FFFFF168H | UA1TIC            | UA1TIF            | UA1TMK            | 0 | 0 | 0   | UA1TPR2             | UA1TPR1             | UA1TPR0             |

| FFFFF16AH | UA2RIC/<br>IICIC0 | UA2RIF/<br>IICIF0 | UA2RMK/<br>IICMK0 | 0 | 0 | 0   | UA2RPR2/<br>IICPR02 | UA2RPR1/<br>IICPR01 | UA2RPR0/<br>IICPR00 |

| FFFFF16CH | UA2TIC            | UA2TIF            | UA2TMK            | 0 | 0 | 0   | UA2TPR2             | UA2TPR1             | UA2TPR0             |

| FFFFF16EH | ADIC              | ADIF              | ADMK              | 0 | 0 | 0   | ADPR2               | ADPR1               | ADPR0               |

| FFFFF170H | DMAIC0            | DMAIF0            | DMAMK0            | 0 | 0 | 0   | DMAPR02             | DMAPR01             | DMAPR00             |

| FFFFF172H | DMAIC1            | DMAIF1            | DMAMK1            | 0 | 0 | 0   | DMAPR12             | DMAPR11             | DMAPR10             |

| FFFFF174H | DMAIC2            | DMAIF2            | DMAMK2            | 0 | 0 | 0   | DMAPR22             | DMAPR21             | DMAPR20             |

| FFFFF176H | DMAIC3            | DMAIF3            | DMAMK3            | 0 | 0 | 0   | DMAPR32             | DMAPR31             | DMAPR30             |

| FFFFF178H | KRIC              | KRIF              | KRMK              | 0 | 0 | 0   | KRPR2               | KRPR1               | KRPR0               |

| FFFFF17AH | WTIIC             | WTIIF             | WTIMK             | 0 | 0 | 0   | WTIPR2              | WTIPR1              | WTIPR0              |

| FFFFF17CH | WTIC              | WTIF              | WTMK              | 0 | 0 | 0   | WTPR2               | WTPR1               | WTPR0               |

| FFFFF18EH | PIC8              | PIF8              | PMK8              | 0 | 0 | 0   | PPR82               | PPR81               | PPR80               |

| FFFFF190H | TP6OVIC           | TP6OVIF           | TP6OVMK           | 0 | 0 | 0   | TP6OVPR2            | TP6OVPR1            | TP6OVPR0            |

| FFFFF192H | TP6CCIC0          | TP6CCIF0          | TP6CCMK0          | 0 | 0 | 0   | TP6CCPR02           | TP6CCPR01           | TP6CCPR00           |

| FFFFF194H | TP6CCIC1          | TP6CCIF1          | TP6CCMK1          | 0 | 0 | 0   | TP6CCPR12           | TP6CCPR11           | TP6CCPR10           |

| FFFFF196H | TP7OVIC           | TP70VIF           | TP7OVMK           | 0 | 0 | 0   | TP7OVPR2            | TP70VPR1            | TP7OVPR0            |

| FFFFF198H | TP7CCIC0          | TP7CCIF0          | TP7CCMK0          | 0 | 0 | 0   | TP7CCPR02           | TP7CCPR01           | TP7CCPR00           |

| FFFFF19AH | TP7CCIC1          | TP7CCIF1          | TP7CCMK1          | 0 | 0 | 0   | TP7CCPR12           | TP7CCPR11           | TP7CCPR10           |

| FFFFF19CH | TP8OVIC           | TP8OVIF           | TP8OVMK           | 0 | 0 | 0   | TP8OVPR2            | TP8OVPR1            | TP8OVPR0            |

| FFFFF19EH | TP8CCIC0          | TP8CCIF0          | TP8CCMK0          | 0 | 0 | 0   | TP8CCPR02           | TP8CCPR01           | TP8CCPR00           |

| FFFFF1A0H | TP8CCIC1          | TP8CCIF1          | TP8CCMK1          | 0 | 0 | 0   | TP8CCPR12           | TP8CCPR11           | TP8CCPR10           |

| FFFFF1A2H | CB5RIC            | CB5RIF            | CB5RMK            | 0 | 0 | 0   | CB5RPR2             | CB5RPR1             | CB5RPR0             |

| FFFFF1A4H | CB5TIC            | CB5TIF            | CB5TMK            | 0 | 0 | 0   | CB5TPR2             | CB5TPR1             | CB5TPR0             |

| FFFFF1A6H | UA3RIC            | UA3RIF            | <b>UA3RMK</b>     | 0 | 0 | 0   | UA3RPR2             | UA3RPR1             | UA3RPR0             |

| FFFFF1A8H | UA3TIC            | UA3TIF            | UA3TMK            | 0 | 0 | 0   | UA3TPR2             | UA3TPR1             | UA3TPR0             |

| Table 19-2. | Interrupt Cor | ntrol Register | (xxICn) (2/2) |

|-------------|---------------|----------------|---------------|

|-------------|---------------|----------------|---------------|

# 19.3.5 Interrupt mask registers 0 to 4 (IMR0 to IMR4)

The IMR0 to IMR4 registers set the interrupt mask state for the maskable interrupts. The xxMKn bit of the IMR0 to IMR4 registers is equivalent to the xxICn.xxMKn bit.

The IMRm register can be read or written in 16-bit units (m = 0 to 4).

If the higher 8 bits of the IMRm register are used as an IMRmH register and the lower 8 bits as an IMRmL register, these registers can be read or written in 8-bit or 1-bit units (m = 0 to 4).

Reset sets these registers to FFFFH.

Caution The device file defines the xxICn.xxMKn bit as a reserved word. If a bit is manipulated using the name of xxMKn, the contents of the xxICn register, instead of the IMRm register, are rewritten (as a result, the contents of the IMRm register are also rewritten).

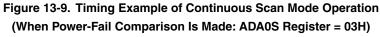

#### (3) Oscillation stabilization time select register (OSTS)

The wait time until the oscillation stabilizes after the STOP mode is released or the wait time until the on-chip flash memory stabilizes after the IDLE2 mode is released is controlled by the OSTS register. The OSTS register can be read or written 8-bit units.

Reset sets this register to 06H.

# 23.4 Operation

This section explains the functions of the clock monitor. The start and stop conditions are as follows.

<Start condition>

Enabling operation by setting the CLM.CLME bit to 1

<Stop conditions>

- While oscillation stabilization time is being counted after STOP mode is released

- When the main clock is stopped (from when PCC.MCK bit = 1 during subclock operation to when PCC.CLS bit = 0 during main clock operation)

- When the sampling clock (internal oscillation clock) is stopped

- When the CPU operates using the internal oscillation clock

# Table 23-2. Operation Status of Clock Monitor(When CLM.CLME Bit = 1, During Internal Oscillation Clock Operation)

| CPU Operating Clock                    | Operation Mode     | Status of Main Clock | Status of Internal<br>Oscillation Clock | Status of Clock Monitor    |

|----------------------------------------|--------------------|----------------------|-----------------------------------------|----------------------------|

| Main clock                             | HALT mode          | Oscillates           | Oscillates <sup>Note 1</sup>            | Operates <sup>Note 2</sup> |

|                                        | IDLE1, IDLE2 modes | Oscillates           | Oscillates <sup>Note 1</sup>            | Operates <sup>Note 2</sup> |

|                                        | STOP mode          | Stops                | Oscillates <sup>Note 1</sup>            | Stops                      |

| Subclock (MCK bit of PCC register = 0) | Sub-IDLE mode      | Oscillates           | Oscillates <sup>Note 1</sup>            | Operates <sup>Note 2</sup> |

| Subclock (MCK bit of PCC register = 1) | Sub-IDLE mode      | Stops                | Oscillates <sup>Note 1</sup>            | Stops                      |

| Internal oscillation clock             | -                  | Stops                | Oscillates <sup>Note 3</sup>            | Stops                      |

| During reset                           | _                  | Stops                | Stops                                   | Stops                      |

**Notes 1.** The internal oscillator can be stopped by setting the RCM.RSTOP bit to 1.

- 2. The clock monitor is stopped while the internal oscillator is stopped.

- **3.** The internal oscillator cannot be stopped by software.

|         |                        |                        |                        | Block 255 (4 KB)        | 000FFFF<br>000FF00 |

|---------|------------------------|------------------------|------------------------|-------------------------|--------------------|

|         |                        |                        |                        | :                       | 000FEFF<br>000C100 |

|         |                        |                        |                        | Block 192 (4 KB)        | 000C0FF<br>000C000 |

|         |                        |                        | Block 191 (4 KB)       | Block 191 (4 KB)        | 000BFFI<br>000BF0  |

|         |                        |                        | :                      | :                       | 000BEF             |

|         |                        |                        | Block 160 (4 KB)       | Block 160 (4 KB)        | 000A0F             |

|         |                        |                        | Block 159 (4 KB)       | Block 159 (4 KB)        | 0009FF             |

|         |                        |                        | :                      | :                       | 0009EFI            |

|         |                        |                        | Block 128 (4 KB)       | Block 128 (4 KB)        | 00080FI            |

|         |                        | Block 127 (4 KB)       | Block 127 (4 KB)       | Block 127 (4 KB)        | 0007FF             |

|         |                        | :                      | :                      | :                       | 0007EF             |

|         |                        | Block 96 (4 KB)        | Block 96 (4 KB)        | Block 96 (4 KB)         | 00060F             |

|         | Block 95 (4 KB)         | 0005FF             |

|         | :                      | :                      | :                      |                         | 0005EFI            |

|         | Block 64 (4 KB)         | 00040FI            |

|         | Block 63 (4 KB)         | 0003FF             |

|         | :                      |                        | :                      |                         | 0003EF             |

| c       | Block 32 (4 KB)         | 00020F             |

|         | Block 31 (4 KB)         | 0001FFI            |

| ote 1 { | :                      |                        | :                      | :                       | 0001EF             |

|         | Block 17 (4 KB)         | 00011FI            |

| ļ       | Block 16 (4 KB)         | 00010FI            |

|         | Block 15 (4 KB)         | 0000FFI            |

| Note 2  | :                      |                        |                        |                         | 0000EFF            |

|         | Block 1 (4 KB)          | 00001FF            |

|         | Block 0 (4 KB)          | 00000FF            |

|         | μPD70F3743<br>(384 KB) | μPD70F3744<br>(512 KB) | μPD70F3745<br>(768 KB) | μPD70F3746<br>(1024 KB) |                    |

Figure 27-1. Flash Memory Mapping

2. Boot area

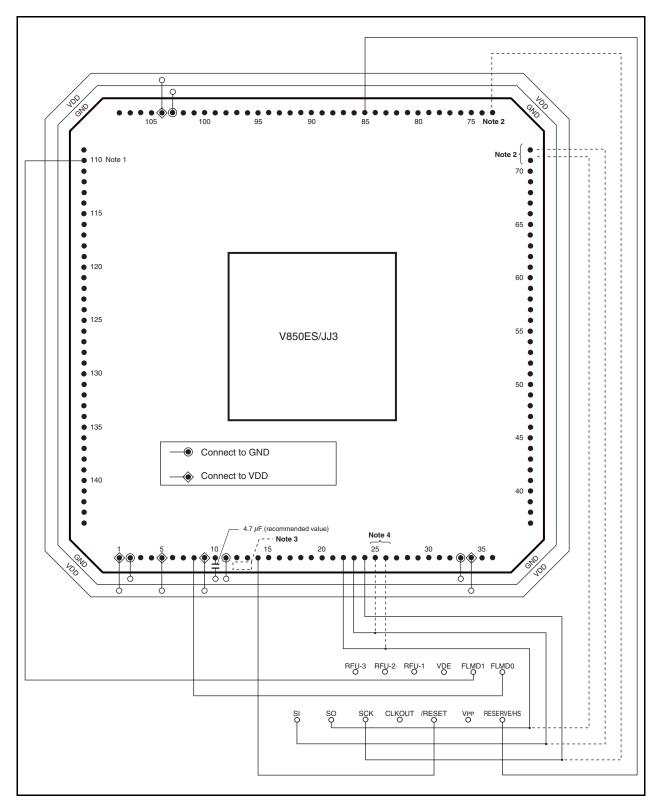

Figure 27-6. Example of Wiring of V850ES/JJ3 Flash Writing Adapter (FA-144GJ-UEN-A) (in CSIB0 + HS Mode) (1/2)

RENESAS

Chapter

Chapter 4

Chapter 5 Soft

| ы                  | Function                    | Details of                                                                    | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page   | (6/3<br>e |

|--------------------|-----------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|

| <br>Classification |                             | Function                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | -         |

| Soft               | Port<br>functions           | PFn.PFnm bit<br>in port mode                                                  | In port mode, the PFn.PFnm bit is valid only in the output mode (PMn.PMnm bit = $0$ ). In the input mode (PMnm bit = 1), the value of the PFnm bit is not reflected in the buffer.                                                                                                                                                                                                                                                                          | p. 163 |           |

|                    |                             | Cautions on bit<br>manipulation<br>instruction for<br>port n register<br>(Pn) | When a 1-bit manipulation instruction is executed on a port that provides both<br>input and output functions, the value of the output latch of an input port that is not<br>subject to manipulation may be written in addition to the targeted bit.<br>Therefore, it is recommended to rewrite the output latch when switching a port<br>from input mode to output mode.                                                                                    | p. 164 |           |

| Hard, soft         |                             | Cautions on on-<br>chip debug pins                                            | The following action must be taken if on-chip debugging is not used.<br>• Clear the OCDM0 bit of the OCDM register (special register) (0)<br>At this time, fix the P05/INTP2/DRST pin to low level from when reset by the<br>RESET pin is released until the above action is taken.<br>If a high level is input to the DRST pin before the above action is taken, it may<br>cause a malfunction (CPU deadlock).<br>Handle the P05 pin with the utmost care. | p. 165 |           |

| Hard               |                             |                                                                               | After reset by the WDT2RES signal, clock monitor (CLM), or low-voltage detector (LVI), the P05/INTP2/DRST pin is not initialized to function as an on-chip debug pin (DRST). The OCDM register holds the current value.                                                                                                                                                                                                                                     | p. 165 |           |

|                    |                             | Cautions on<br>P05/INTP2/<br>DRST pin                                         | The P05/INTP2/ $\overline{DRST}$ pin has an internal pull-down resistor (30 k $\Omega$ TYP.). After a reset by the $\overline{RESET}$ pin, a pulldown resistor is connected. The pull-down resistor is disconnected when the OCDM0 bit is cleared (0).                                                                                                                                                                                                      | p. 165 |           |

|                    |                             | Cautions on<br>P53 pin when<br>power is turned<br>on                          | <ul> <li>When the power is turned on, the following pin may output an undefined level temporarily, even during reset.</li> <li>P53/SIB2/KR3/TIQ00/TOQ00/RTP03/DDO pin</li> </ul>                                                                                                                                                                                                                                                                            | p. 165 |           |

|                    |                             | Hysteresis<br>characteristics                                                 | In port mode, the following port pins do not have hysteresis characteristics.<br>P00 to P06<br>P31 to P35, P38, P39<br>P40 to P42<br>P50 to P55<br>P66, P68 to P610, P612, P613<br>P80<br>P90 to P97, P99, P910, P912 to P915                                                                                                                                                                                                                               | p. 165 |           |

| Soft               | Bus<br>control<br>functions | Pin status when internal ROM                                                  | When a write access is performed to the internal ROM area, address, data, and control signals are activated in the same way as access to the external memory area.                                                                                                                                                                                                                                                                                          | p. 167 |           |

|                    |                             | EXIMC register                                                                | Set the EXIMC register from the internal ROM or internal RAM area before<br>making an external access.<br>After setting the EXIMC register, be sure to insert a NOP instruction.                                                                                                                                                                                                                                                                            | p. 169 |           |

|                    |                             | BSC register                                                                  | Write to the BSC register after reset, and then do not change the set values. Also, do not access an external memory area until the initial settings of the BSC register are complete.                                                                                                                                                                                                                                                                      | p. 170 |           |

|                    |                             |                                                                               | Be sure to set bits 14, 12, 10, and 8 to "1", and clear bits 15, 13, 11, 9, 7, 5, 3, and 1 to "0".                                                                                                                                                                                                                                                                                                                                                          | p. 170 |           |

|                    |                             | DWC0 register                                                                 | The internal ROM and internal RAM areas are not subject to programmable wait,<br>and are always accessed without a wait state. The on-chip peripheral I/O area is<br>also not subject to programmable wait, and only wait control from each peripheral<br>function is performed.                                                                                                                                                                            | p. 178 |           |

function is performed.

| (36/37) |

|---------|

| ( )     |

|            |                | r                                 | 1                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (      | 36/37 |

|------------|----------------|-----------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| Chapter    | Classification | Function                          | Details of<br>Function                      | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pag    | Э     |

| Chapter 29 | Hard           | Electrical<br>specifica-<br>tions | Absolute<br>maximum<br>ratings              | Product quality may suffer if the absolute maximum rating is exceeded even<br>momentarily for any parameter. That is, the absolute maximum ratings are rated<br>values at which the product is on the verge of suffering physical damage, and<br>therefore the product must be used under conditions that ensure that the absolute<br>maximum ratings are not exceeded. The ratings and conditions indicated for DC<br>characteristics and AC characteristics represent the quality assurance range<br>during normal operation.                                                                                                                                | p. 784 |       |