# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08aw16cfde |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

### Title

### Page

|      | 10.4.3    | Timer x Counter Modulo Registers (TPMxMODH:TPMxMODL)     | 172 |

|------|-----------|----------------------------------------------------------|-----|

|      | 10.4.4    | Timer x Channel n Status and Control Register (TPMxCnSC) | 173 |

|      | 10.4.5    | Timer x Channel Value Registers (TPMxCnVH:TPMxCnVL)      | 174 |

| 10.5 | Functiona | al Description                                           | 175 |

|      | 10.5.1    | Counter                                                  | 175 |

|      | 10.5.2    | Channel Mode Selection                                   | 176 |

|      | 10.5.3    | Center-Aligned PWM Mode                                  | 178 |

| 10.6 | TPM Inte  | errupts                                                  | 179 |

|      | 10.6.1    | Clearing Timer Interrupt Flags                           | 179 |

|      | 10.6.2    | Timer Overflow Interrupt Description                     | 179 |

|      | 10.6.3    | Channel Event Interrupt Description                      | 180 |

|      | 10.6.4    | PWM End-of-Duty-Cycle Events                             | 180 |

### Chapter 11 Serial Communications Interface (S08SCIV2)

| 11.1 | Introduct  | ion                                        |     |

|------|------------|--------------------------------------------|-----|

|      | 11.1.1     | Features                                   |     |

|      | 11.1.2     | Modes of Operation                         |     |

|      | 11.1.3     | Block Diagram                              |     |

| 11.2 | Register 1 | Definition                                 |     |

|      | 11.2.1     | SCI Baud Rate Registers (SCIxBDH, SCIxBHL) |     |

|      | 11.2.2     | SCI Control Register 1 (SCIxC1)            | 187 |

|      | 11.2.3     | SCI Control Register 2 (SCIxC2)            |     |

|      | 11.2.4     | SCI Status Register 1 (SCIxS1)             | 189 |

|      | 11.2.5     | SCI Status Register 2 (SCIxS2)             | 191 |

|      | 11.2.6     | SCI Control Register 3 (SCIxC3)            | 191 |

|      | 11.2.7     |                                            |     |

| 11.3 | Function   | al Description                             | 192 |

|      | 11.3.1     | Baud Rate Generation                       |     |

|      | 11.3.2     | Transmitter Functional Description         | 193 |

|      | 11.3.3     | Receiver Functional Description            | 194 |

|      | 11.3.4     | Interrupts and Status Flags                |     |

|      | 11.3.5     | Additional SCI Functions                   | 197 |

### Chapter 12 Serial Peripheral Interface (S08SPIV3)

| 12.0.1   | Features                               | 201                                                                                                                                                                  |

|----------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.0.2   | Block Diagrams                         | 201                                                                                                                                                                  |

| 12.0.3   | SPI Baud Rate Generation               | 203                                                                                                                                                                  |

| External | Signal Description                     | 204                                                                                                                                                                  |

|          |                                        |                                                                                                                                                                      |

| 12.1.2   | MOSI — Master Data Out, Slave Data In  | 204                                                                                                                                                                  |

|          | 12.0.2<br>12.0.3<br>External<br>12.1.1 | 12.0.1Features12.0.2Block Diagrams12.0.3SPI Baud Rate GenerationExternal Signal Description12.1.1SPSCK — SPI Serial Clock12.1.2MOSI — Master Data Out, Slave Data In |

the CPU executes a STOP instruction, the MCU will not enter either of the stop modes and an illegal opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

HCS08 devices that are designed for low voltage operation (1.8V to 3.6V) also include stop1 mode. The MC9S08AW60 Series family of devices does not include stop1 mode.

| Mode  | PPDC | CPU, Digital<br>Peripherals,<br>FLASH | RAM     | ICG              | ADC1          | Regulator | I/O Pins       | RTI           |

|-------|------|---------------------------------------|---------|------------------|---------------|-----------|----------------|---------------|

| Stop2 | 1    | Off                                   | Standby | Off              | Disabled      | Standby   | States<br>held | Optionally on |

| Stop3 | 0    | Standby                               | Standby | Off <sup>1</sup> | Optionally on | Standby   | States<br>held | Optionally on |

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

|            |      |      | -        |

|------------|------|------|----------|

| Table 3-1. | Stop | Mode | Behavior |

<sup>1</sup> Crystal oscillator can be configured to run in stop3. Please see the ICG registers.

### 3.6.1 Stop2 Mode

The stop2 mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. To enter stop2, the user must execute a STOP instruction with stop2 selected (PPDC = 1) and stop mode enabled (STOPE = 1). In addition, the LVD must not be enabled to operate in stop (LVDSE = 0 or LVDE = 0). If the LVD is enabled in stop, then the MCU enters stop3 upon the execution of the STOP instruction regardless of the state of PPDC.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers which they want to restore after exit of stop2, to locations in RAM. Upon exit of stop2, these values can be restored by user software before pin latches are opened.

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ADC. Upon entry into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and after exiting stop2 mode until a logic 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting either of the wake-up pins:  $\overline{\text{RESET}}$  or IRQ, or by an RTI interrupt. IRQ is always an active low input when the MCU is in stop2, regardless of how it was configured before entering stop2.

#### NOTE

Although this IRQ pin is automatically configured as active low input, the pullup associated with the IRQ pin is not automatically enabled. Therefore, if an external pullup is not used, the internal pullup must be enabled by setting IRQPE in IRQSC.

Upon wake-up from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

# Chapter 4 Memory

### 4.1 MC9S08AW60 Series Memory Map

Figure 4-1 shows the memory map for the MC9S08AW60 and MC9S08AW48 MCUs. Figure 4-2 shows the memory map for the MC9S08AW32 and MC9S08AW16 MCUs. On-chip memory in the MC9S08AW60 Series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (\$0000 through \$006F)

- High-page registers (\$1800 through \$185F)

- Nonvolatile registers (\$FFB0 through \$FFBF)

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at \$1800.

| Address            | Register Name | Bit 7  | 6      | 5       | 4       | 3      | 2      | 1              | Bit 0  |

|--------------------|---------------|--------|--------|---------|---------|--------|--------|----------------|--------|

| \$1800             | SRS           | POR    | PIN    | COP     | ILOP    | 0      | ICG    | LVD            | 0      |

| \$1801             | SBDFR         | 0      | 0      | 0       | 0       | 0      | 0      | 0              | BDFR   |

| \$1802             | SOPT          | COPE   | COPT   | STOPE   | _       | 0      | 0      | —              | _      |

| \$1803             | SMCLK         | 0      | 0      | 0       | MPE     | 0      |        | MCSEL          |        |

| \$1804 —<br>\$1805 | Reserved      | _      | _      | _       | _       |        | _      | _              | _      |

| \$1806             | SDIDH         | REV3   | REV2   | REV1    | REV0    | ID11   | ID10   | ID9            | ID8    |

| \$1807             | SDIDL         | ID7    | ID6    | ID5     | ID4     | ID3    | ID2    | ID1            | ID0    |

| \$1808             | SRTISC        | RTIF   | RTIACK | RTICLKS | RTIE    | 0      | RTIS2  | RTIS1          | RTIS0  |

| \$1809             | SPMSC1        | LVDF   | LVDACK | LVDIE   | LVDRE   | LVDSE  | LVDE   | 0 <sup>1</sup> | BGBE   |

| \$180A             | SPMSC2        | LVWF   | LVWACK | LVDV    | LVWV    | PPDF   | PPDACK | —              | PPDC   |

| \$180B–<br>\$180F  | Reserved      | _      | _      | _       | _       | _      | _      | _              | _      |

| \$1810             | DBGCAH        | Bit 15 | 14     | 13      | 12      | 11     | 10     | 9              | Bit 8  |

| \$1811             | DBGCAL        | Bit 7  | 6      | 5       | 4       | 3      | 2      | 1              | Bit 0  |

| \$1812             | DBGCBH        | Bit 15 | 14     | 13      | 12      | 11     | 10     | 9              | Bit 8  |

| \$1813             | DBGCBL        | Bit 7  | 6      | 5       | 4       | 3      | 2      | 1              | Bit 0  |

| \$1814             | DBGFH         | Bit 15 | 14     | 13      | 12      | 11     | 10     | 9              | Bit 8  |

| \$1815             | DBGFL         | Bit 7  | 6      | 5       | 4       | 3      | 2      | 1              | Bit 0  |

| \$1816             | DBGC          | DBGEN  | ARM    | TAG     | BRKEN   | RWA    | RWAEN  | RWB            | RWBEN  |

| \$1817             | DBGT          | TRGSEL | BEGIN  | 0       | 0       | TRG3   | TRG2   | TRG1           | TRG0   |

| \$1818             | DBGS          | AF     | BF     | ARMF    | 0       | CNT3   | CNT2   | CNT1           | CNT0   |

| \$1819–<br>\$181F  | Reserved      | _      | _      | _       | _       | _      | _      | _              | _      |

| \$1820             | FCDIV         | DIVLD  | PRDIV8 | DIV5    | DIV4    | DIV3   | DIV2   | DIV1           | DIV0   |

| \$1821             | FOPT          | KEYEN  | FNORED | 0       | 0       | 0      | 0      | SEC01          | SEC00  |

| \$1822             | Reserved      | —      | _      | _       | _       | _      |        |                | _      |

| \$1823             | FCNFG         | 0      | 0      | KEYACC  | 0       | 0      | 0      | 0              | 0      |

| \$1824             | FPROT         | FPS7   | FPS6   | FPS5    | FPS4    | FPS3   | FPS2   | FPS1           | FPDIS  |

| \$1825             | FSTAT         | FCBEF  | FCCF   | FPVIOL  | FACCERR | 0      | FBLANK | 0              | 0      |

| \$1826             | FCMD          | FCMD7  | FCMD6  | FCMD5   | FCMD4   | FCMD3  | FCMD2  | FCMD1          | FCMD0  |

| \$1827–<br>\$183F  | Reserved      | _      | _      | _       | _       | _      | _      | _              | _      |

| \$1840             | PTAPE         | PTAPE7 | PTAPE6 | PTAPE5  | PTAPE4  | PTAPE3 | PTAPE2 | PTAPE1         | PTAPE0 |

| \$1841             | PTASE         | PTASE7 | PTASE6 | PTASE5  | PTASE4  | PTASE3 | PTASE2 | PTASE1         | PTASE0 |

| \$1842             | PTADS         | PTADS7 | PTADS6 | PTADS5  | PTADS4  | PTADS3 | PTADS2 | PTADS1         | PTADS0 |

| \$1843             | Reserved      | —      |        |         | —       |        | _      |                |        |

| \$1844             | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5  | PTBPE4  | PTBPE3 | PTBPE2 | PTBPE1         | PTBPE0 |

| \$1845             | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5  | PTBSE4  | PTBSE3 | PTBSE2 | PTBSE1         | PTBSE0 |

#### Table 4-3. High-Page Register Summary (Sheet 1 of 2)

MC9S08AW60 Data Sheet, Rev 2

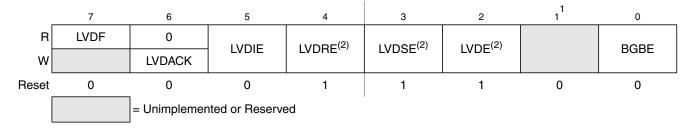

### 5.9.8 System Power Management Status and Control 1 Register (SPMSC1)

<sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                           |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This read/write bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                               |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This read/write bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This read/write bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

| 0<br>BGBE   | <ul> <li>Bandgap Buffer Enable — The BGBE bit is used to enable an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>                                      |

#### Table 5-11. SPMSC1 Register Field Descriptions

| Source                                                                                                           |                                             |                                                                                                                                                                                                                                                                                                                                                 |   | Effect<br>on CCR |   |    |    |    | ess                                                                                          | and                                      | cles <sup>1</sup>                                                             |                                                          |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|---|----|----|----|----------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|

| Form                                                                                                             | Operation                                   | Description<br>V                                                                                                                                                                                                                                                                                                                                |   |                  | I | N  | z  | с  | Address<br>Mode                                                                              | Opcode                                   | Operand                                                                       | Bus Cycles <sup>1</sup>                                  |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Clear   | Branch if (Mn) = 0                                                                                                                                                                                                                                                                                                                              | _ | _                | _ | _  | _  | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 03<br>05<br>07<br>09<br>0B<br>0D         | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BRN rel                                                                                                          | Branch Never                                | Uses 3 Bus Cycles                                                                                                                                                                                                                                                                                                                               | - | -                | - | -  | -  | -  | REL                                                                                          | 21                                       | rr                                                                            | 3                                                        |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Set     | Branch if (Mn) = 1                                                                                                                                                                                                                                                                                                                              | _ | _                | _ | _  | _  | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 02<br>04<br>06<br>08<br>0A<br>0C         | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSET n,opr8a                                                                                                     | Set Bit <i>n</i> in Memory                  | Mn ← 1                                                                                                                                                                                                                                                                                                                                          | _ | _                | _ | _  | _  | _  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 14                                       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                                        | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5           |

| BSR rel                                                                                                          | Branch to Subroutine                        | $\begin{array}{l} PC \leftarrow (PC) + 0x0002\\ push\ (PCL); SP \leftarrow (SP) - 0x0001\\ push\ (PCH); SP \leftarrow (SP) - 0x0001\\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                            | _ | _                | _ | _  | _  | _  | REL                                                                                          | AD                                       | rr                                                                            | 5                                                        |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if<br>Equal              | Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                                                                                                              | _ | _                | _ | _  | _  | _  | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61       | ii rr<br>ff rr<br>rr                                                          | 5<br>4<br>4<br>5<br>5<br>6                               |

| CLC                                                                                                              | Clear Carry Bit                             | $C \leftarrow 0$                                                                                                                                                                                                                                                                                                                                | - | -                | - | -  | -  | 0  | INH                                                                                          | 98                                       |                                                                               | 1                                                        |

| CLI                                                                                                              | Clear Interrupt Mask Bit                    | I ← 0                                                                                                                                                                                                                                                                                                                                           | - | -                | 0 | -  | -  | -  | INH                                                                                          | 9A                                       |                                                                               | 1                                                        |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear                                       | $\begin{array}{c} M \leftarrow 0x00 \\ A \leftarrow 0x00 \\ X \leftarrow 0x00 \\ H \leftarrow 0x00 \\ M \leftarrow 0x00 \\ M \leftarrow 0x00 \\ M \leftarrow 0x00 \\ M \leftarrow 0x00 \end{array}$                                                                                                                                             | 0 | _                | _ | 0  | 1  | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                 | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F | ff                                                                            | 5<br>1<br>1<br>5<br>4<br>6                               |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP  | Compare Accumulator<br>with Memory          | (A) – (M)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                                                                          | ¢ | _                | _ | \$ | \$ | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                          |                                          | dd<br>hh II<br>ee ff<br>ff<br>ee ff                                           | 2<br>3<br>4<br>3<br>3<br>5<br>4                          |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                               | Complement<br>(One's Complement)            | $\begin{array}{l} M \leftarrow (\overline{M}) = OxFF - (M) \\ A \leftarrow (\overline{A}) = OxFF - (A) \\ X \leftarrow (\overline{X}) = OxFF - (X) \\ M \leftarrow (\overline{M}) = OxFF - (M) \end{array}$ | 0 | _                | _ | \$ | \$ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 33<br>43<br>53<br>63<br>73<br>9E63       | ff                                                                            | 5<br>1<br>5<br>4<br>6                                    |

| CPHX opr16a<br>CPHX #opr16i<br>CPHX opr8a<br>CPHX oprx8,SP                                                       | Compare Index Register<br>(H:X) with Memory | (H:X) – (M:M + 0x0001)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                                                             | € | _                | _ | €  | \$ | €  | EXT<br>IMM<br>DIR<br>SP1                                                                     | 65                                       | dd                                                                            | 6<br>3<br>5<br>6                                         |

Table 7-2. HCS08 Instruction Set Summary (Sheet 3 of 7)

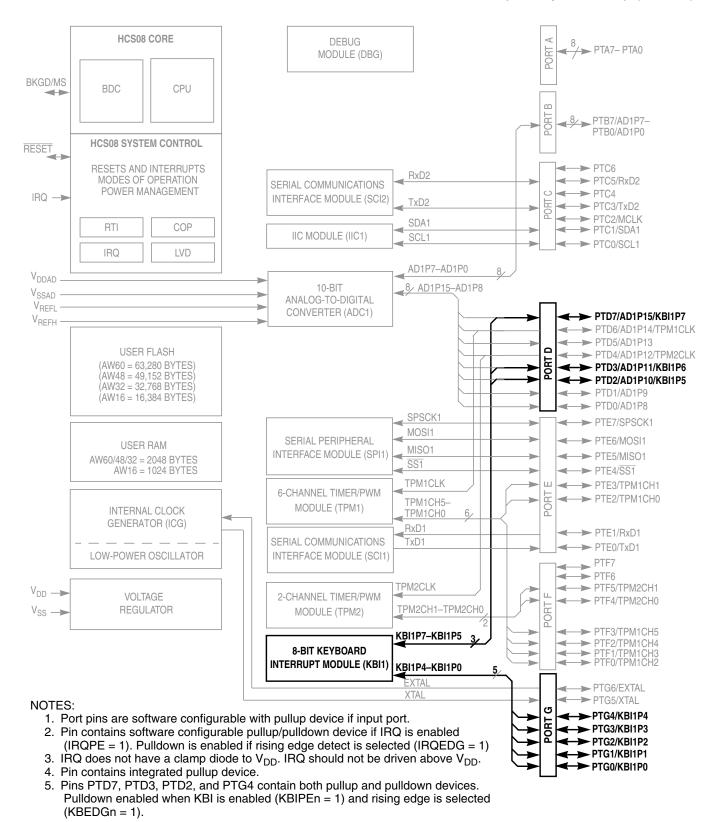

Chapter 9 Keyboard Interrupt (S08KBIV1)

### 9.3 Features

The keyboard interrupt (KBI) module features include:

- Four falling edge/low level sensitive

- Four falling edge/low level or rising edge/high level sensitive

- Choice of edge-only or edge-and-level sensitivity

- Common interrupt flag and interrupt enable control

- Capable of waking up the MCU from stop3 or wait mode

Chapter 9 Keyboard Interrupt (S08KBIV1)

Figure 9-1. Block Diagram Highlighting KBI Module

MC9S08AW60 Data Sheet, Rev 2

### 11.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character

- Selectable transmitter output polarity

### 11.1.2 Modes of Operation

See Section 11.3, "Functional Description," for a detailed description of SCI operation in the different modes.

- 8- and 9-bit data modes

- Stop modes SCI is halted during all stop modes

- Loop mode

- Single-wire mode

### 11.1.3 Block Diagram

Figure 11-2 shows the transmitter portion of the SCI.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RDRF | Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). In 8-bit mode, to clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD). In 9-bit mode, to clear RDRF, read SCIxS1 with RDRF = 1 and then read SCIxD and the SCI control 3 register (SCIxC3). SCIxD and SCIxC3 can be read in any order, but the flag is cleared only after both data registers are read.         0       Receive data register full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1<br>FE   | Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop<br>bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read<br>SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).0 No framing error detected. This does not guarantee the framing is correct.1 Framing error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>PF   | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Chapter 11 Serial Communications Interface (S08SCIV2)

9-bit data mode typically is used in conjunction with parity to allow eight bits of data plus the parity in the ninth bit. Or it is used with address-mark wakeup so the ninth data bit can serve as the wakeup bit. In custom protocols, the ninth bit can also serve as a software-controlled marker.

### 11.3.5.2 Stop Mode Operation

During all stop modes, clocks to the SCI module are halted.

In stop1 and stop2 modes, all SCI register data is lost and must be re-initialized upon recovery from these two stop modes.

No SCI module registers are affected in stop3 mode.

Note, because the clocks are halted, the SCI module will resume operation upon exit from stop (only in stop3 mode). Software should ensure stop mode is not entered while there is a character being transmitted out of or received into the SCI module.

#### 11.3.5.3 Loop Mode

When LOOPS = 1, the RSRC bit in the same register chooses between loop mode (RSRC = 0) or single-wire mode (RSRC = 1). Loop mode is sometimes used to check software, independent of connections in the external system, to help isolate system problems. In this mode, the transmitter output is internally connected to the receiver input and the RxD pin is not used by the SCI, so it reverts to a general-purpose port I/O pin.

#### 11.3.5.4 Single-Wire Mode

When LOOPS = 1, the RSRC bit in the same register chooses between loop mode (RSRC = 0) or single-wire mode (RSRC = 1). Single-wire mode is used to implement a half-duplex serial connection. The receiver is internally connected to the transmitter output and to the TxD pin. The RxD pin is not used and reverts to a general-purpose port I/O pin.

In single-wire mode, the TXDIR bit in SCIxC3 controls the direction of serial data on the TxD pin. When TXDIR = 0, the TxD pin is an input to the SCI receiver and the transmitter is temporarily disconnected from the TxD pin so an external device can send serial data to the receiver. When TXDIR = 1, the TxD pin is an output driven by the transmitter.

#### Table 12-1. SPI1C1 Field Descriptions (continued)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSTR  | Master/Slave Mode Select         0       SPI module configured as a slave SPI device         1       SPI module configured as a master SPI device                                                                                                                                                                                                                                                             |

| 3<br>CPOL  | <ul> <li>Clock Polarity — This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 12.4.1, "SPI Clock Formats" for more details.</li> <li>0 Active-high SPI clock (idles low)</li> <li>1 Active-low SPI clock (idles high)</li> </ul>                                                                                             |

| 2<br>CPHA  | <ul> <li>Clock Phase — This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 12.4.1, "SPI Clock Formats" for more details.</li> <li>0 First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer</li> <li>1 First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer</li> </ul> |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the SS pin as shown in Table 12-2.                                                                                                                                                                                  |

| 0<br>LSBFE | <ul> <li>LSB First (Shifter Direction)</li> <li>0 SPI serial data transfers start with most significant bit</li> <li>1 SPI serial data transfers start with least significant bit</li> </ul>                                                                                                                                                                                                                  |

Table 12-2. SS Pin Function

| MODFEN | SSOE | Master Mode                   | Slave Mode         |

|--------|------|-------------------------------|--------------------|

| 0      | 0    | General-purpose I/O (not SPI) | Slave select input |

| 0      | 1    | General-purpose I/O (not SPI) | Slave select input |

| 1      | 0    | SS input for mode fault       | Slave select input |

| 1      | 1    | Automatic SS output           | Slave select input |

#### NOTE

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

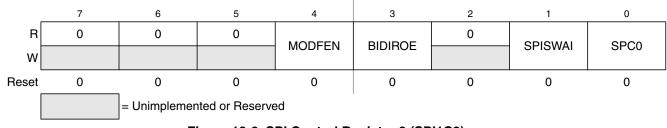

### 12.3.2 SPI Control Register 2 (SPI1C2)

This read/write register is used to control optional features of the SPI system. Bits 7, 6, 5, and 2 are not implemented and always read 0.

MC9S08AW60 Data Sheet, Rev 2

Chapter 13 Inter-Integrated Circuit (S08IICV1)

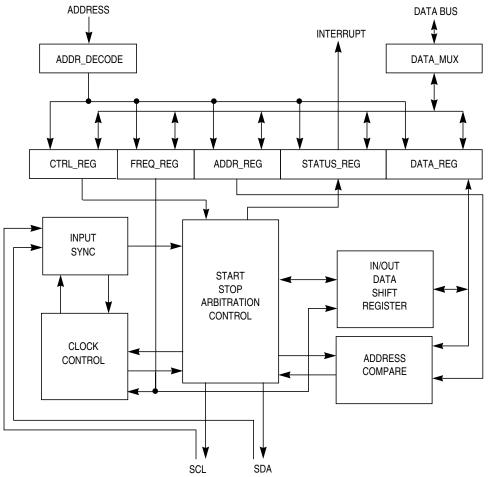

### 13.1.3 Block Diagram

Figure 13-2 is a block diagram of the IIC.

Figure 13-2. IIC Functional Block Diagram

### 13.2 External Signal Description

This section describes each user-accessible pin signal.

### 13.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

### 13.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

### **13.3 Register Definition**

This section consists of the IIC register descriptions in address order.

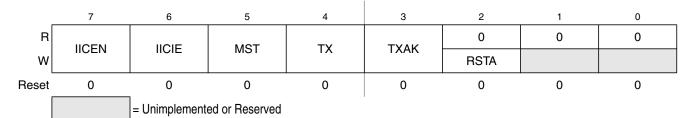

## 13.3.3 IIC Control Register (IIC1C)

Figure 13-5. IIC Control Register (IIC1C)

| Table 13-4. IIC1C Register Field Descriptions |

|-----------------------------------------------|

|-----------------------------------------------|

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | <ul> <li>IIC Enable — The IICEN bit determines whether the IIC module is enabled.</li> <li>0 IIC is not enabled.</li> <li>1 IIC is enabled.</li> </ul>                                                                                                                                                                                                                            |

| 6<br>IICIE | <ul> <li>IIC Interrupt Enable — The IICIE bit determines whether an IIC interrupt is requested.</li> <li>0 IIC interrupt request not enabled.</li> <li>1 IIC interrupt request enabled.</li> </ul>                                                                                                                                                                                |

| 5<br>MST   | <ul> <li>Master Mode Select — The MST bit is changed from a 0 to a 1 when a START signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a STOP signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave Mode.</li> <li>1 Master Mode.</li> </ul>                                                  |

| 4<br>TX    | Transmit Mode Select — The TX bit selects the direction of master and slave transfers. In master mode this bit<br>should be set according to the type of transfer required. Therefore, for address cycles, this bit will always be high.<br>When addressed as a slave this bit should be set by software according to the SRW bit in the status register.0Receive.<br>11Transmit. |

| 3<br>TXAK  | Transmit Acknowledge Enable — This bit specifies the value driven onto the SDA during data acknowledge<br>cycles for both master and slave receivers.0An acknowledge signal will be sent out to the bus after receiving one data byte.1No acknowledge signal response is sent.                                                                                                    |

| 2<br>RSTA  | <b>Repeat START</b> — Writing a one to this bit will generate a repeated START condition provided it is the current master. This bit will always be read as a low. Attempting a repeat at the wrong time will result in loss of arbitration.                                                                                                                                      |

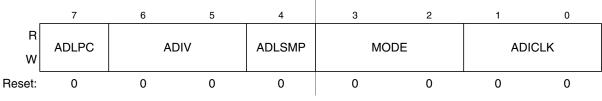

#### Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

Figure 14-10. Configuration Register (ADC1CFG)

Table 14-5. ADC1CFG Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC    | <ul> <li>Low Power Configuration — ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.</li> <li>0 High speed configuration</li> <li>1 Low power configuration: {FC31}The power is reduced at the expense of maximum clock speed.</li> </ul>                                                                                                    |

| 6:5<br>ADIV   | <b>Clock Divide Select</b> — ADIV select the divide ratio used by the ADC to generate the internal clock ADCK.<br>Table 14-6 shows the available clock configurations.                                                                                                                                                                                                                                                                                                       |

| 4<br>ADLSMP   | <ul> <li>Long Sample Time Configuration — ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.</li> <li>Short sample time</li> <li>Long sample time</li> </ul> |

| 3:2<br>MODE   | <b>Conversion Mode Selection</b> — MODE bits are used to select between 10- or 8-bit operation. See Table 14-7.                                                                                                                                                                                                                                                                                                                                                              |

| 1:0<br>ADICLK | Input Clock Select — ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 14-8.                                                                                                                                                                                                                                                                                                                                                          |

#### Table 14-6. Clock Divide Select

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

#### Table 14-7. Conversion Modes

| MODE | Mode Description         |  |  |

|------|--------------------------|--|--|

| 00   | 8-bit conversion (N=8)   |  |  |

| 01   | Reserved                 |  |  |

| 10   | 10-bit conversion (N=10) |  |  |

| 11   | Reserved                 |  |  |

#### **Chapter 15 Development Support**

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

### 15.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

| Rating                                                                                                                  | Symbol           | Value                          | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|------|

| Supply voltage                                                                                                          | V <sub>DD</sub>  | -0.3 to + 5.8                  | V    |

| Input voltage                                                                                                           | V <sub>In</sub>  | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | ۱ <sub>D</sub>   | ± 25                           | mA   |

| Maximum current into V <sub>DD</sub>                                                                                    | I <sub>DD</sub>  | 120                            | mA   |

| Storage temperature                                                                                                     | T <sub>stg</sub> | -55 to +150                    | °C   |

| Maximum junction temperature                                                                                            | TJ               | 150                            | °C   |

#### Table A-2. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

#### Appendix A Electrical Characteristics and Timing Specifications

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2 \qquad \qquad Eqn. A-3$$

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

### A.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model               | Description                 | Symbol | Value | Unit |

|---------------------|-----------------------------|--------|-------|------|

|                     | Series Resistance           | R1     | 1500  | Ω    |

| Human Body<br>Model | Storage Capacitance         | С      | 100   | pF   |

|                     | Number of Pulse per pin     | _      | 3     |      |

|                     | Series Resistance           | R1     | 0     | Ω    |

| Machine Model       | Storage Capacitance         | С      | 200   | pF   |

|                     | Number of Pulse per pin     | —      | 3     |      |

| Latch-Up            | Minimum input voltage limit |        | -2.5  | V    |

| Laten-op            | Maximum input voltage limit |        | 7.5   | V    |

Table A-4. ESD and Latch-up Test Conditions

| Table A-5. | ESD and | Latch-Up | Protection | Characteristics |

|------------|---------|----------|------------|-----------------|

|------------|---------|----------|------------|-----------------|

| Num | С | Rating                                     | Symbol           | Min    | Мах | Unit |

|-----|---|--------------------------------------------|------------------|--------|-----|------|

| 1   | С | Human Body Model (HBM)                     | V <sub>HBM</sub> | ± 2000 | _   | V    |

| 2   | С | Machine Model (MM)                         | V <sub>MM</sub>  | ± 200  | _   | V    |

| 3   | С | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ± 500  | _   | V    |

| 4   | С | Latch-up Current at T <sub>A</sub> = 125°C | I <sub>LAT</sub> | ± 100  | _   | mA   |

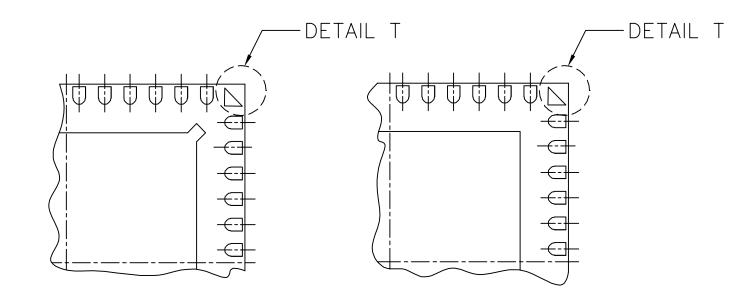

# Appendix B Ordering Information and Mechanical Drawings

### **B.1** Ordering Information

This section contains ordering numbers for MC9S08AW60 Series devices. See below for an example of the device numbering system.

| Device Number <sup>1</sup>             | Memory                     |      | Available Packages <sup>2</sup>         |  |

|----------------------------------------|----------------------------|------|-----------------------------------------|--|

| Device Number                          | FLASH                      | RAM  | Туре                                    |  |

| MC9S08AW60<br>MC9S08AW48<br>MC9S08AW32 | 63,280<br>49,152<br>32,768 | 2048 | 64-pin LQFP<br>64-pin QFP<br>48-pin QFN |  |

| MC9S08AW16                             | 16,384                     | 1024 | 44-pin LQFP                             |  |

#### Table B-1. Consumer and Industrial Device Numbering System

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-3 for package information.

#### Table B-2. Automotive Device Numbering System

| Device Number <sup>1</sup>          | Memory                     |      | Available Packages <sup>2</sup>          |

|-------------------------------------|----------------------------|------|------------------------------------------|

| Device Nulliber                     | FLASH                      | RAM  | Туре                                     |

| S9S08AW60<br>S9S08AW48<br>S9S08AW32 | 63,280<br>49,152<br>32,768 | 2048 | 64-pin LQFP<br>48-pin QFN<br>44-pin LQFP |

| S9S08AW16                           | 16,384                     | 1024 | 48-pin QFN<br>44-pin LQFP                |

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-3 for package information.

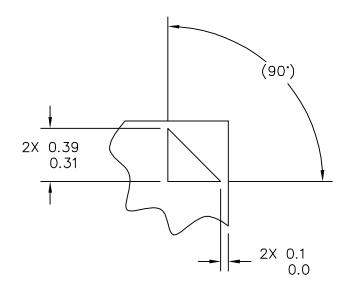

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL T

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE |                               | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|-------------------------------|----------------------------|-------------|

|                                                         |                    | DOCUMENT NO: 98ARH99048A      |                            | REV: F      |

|                                                         |                    | CASE NUMBER                   | 2: 1314–05                 | 05 DEC 2005 |

|                                                         |                    | STANDARD: JEDEC-MO-220 VKKD-2 |                            |             |