Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 508                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LQFP                                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08aw16cfge |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08AW60 Features

### 8-Bit HCS08 Central Processor Unit (CPU)

- 40-MHz HCS08 CPU (central processor unit)

- 20-MHz internal bus frequency

- HC08 instruction set with added BGND instruction

- Single-wire background debug mode interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- On-chip real-time in-circuit emulation (ICE) with two comparators (plus one in BDM), nine trigger modes, and on-chip bus capture buffer. Typically shows approximately 50 instructions before or after the trigger point.

- Support for up to 32 interrupt/reset sources

### **Memory Options**

- Up to 60 KB of on-chip in-circuit programmable FLASH memory with block protection and security options

- Up to 2 KB of on-chip RAM

### **Clock Source Options**

Clock source options include crystal, resonator, external clock, or internally generated clock with precision NVM trimming

### System Protection

- Optional computer operating properly (COP) reset

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset (some devices don't have illegal addresses)

### **Power-Saving Modes**

Wait plus two stops

### Peripherals

- ADC Up to 16-channel, 10-bit analog-to-digital converter with automatic compare function

- SCI Two serial communications interface modules with optional 13-bit break

- SPI Serial peripheral interface module

- IIC Inter-integrated circuit bus module to operate at up to 100 kbps with maximum bus loading; capable of higher baud rates with reduced loading

- Timers One 2-channel and one 6-channel 16-bit timer/pulse-width modulator (TPM) module: Selectable input capture, output compare, and edge-aligned PWM capability on each channel. Each timer module may be configured for buffered, centered PWM (CPWM) on all channels

- **KBI** Up to 8-pin keyboard interrupt module

### Input/Output

- Up to 54 general-purpose input/output (I/O) pins

- Software-selectable pullups on ports when used as inputs

- Software-selectable slew rate control on ports when used as outputs

- Software-selectable drive strength on ports when used as outputs

- Master reset pin and power-on reset (POR)

- Internal pullup on RESET, IRQ, and BKGD/MS pins to reduce customer system cost

### Package Options

### MC9S08AW60/48/32

- 64-pin quad flat package (QFP)

- 64-pin low-profile quad flat package (LQFP)

- 48-pin low-profile quad flat package (QFN)

- 44-pin low-profile quad flat package (LQFP)

### MC9S08AW16

- 48-pin low-profile quad flat package (QFN)

- 44-pin low-profile quad flat package (LQFP)

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                  | 1/2006           | Initial external release.                                                                                                                                                                                                                                                                                                  |  |  |  |

| 2                  | 12/2006          | Includes KBI block changes; new V <sub>OL</sub> / I <sub>OL</sub> figures; RI <sub>DD</sub> spec changes; SC part numbers with ICG trim modifications; addition of Temp Sensor to ADC. Resolved the stop IDD issues, added RTI figure, bandgap information, and incorporated electricals edits and any ProjectSync issues. |  |  |  |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006. All rights reserved.

### **Section Number**

Title

### Page

|     | 7.2.1     | Accumulator (A)                 | 110 |

|-----|-----------|---------------------------------|-----|

|     | 7.2.2     | Index Register (H:X)            |     |

|     | 7.2.3     | Stack Pointer (SP)              |     |

|     | 7.2.4     | Program Counter (PC)            |     |

|     | 7.2.5     | Condition Code Register (CCR)   |     |

| 7.3 | Addressi  | ng Modes                        | 113 |

|     | 7.3.1     | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2     | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3     | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4     | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5     | Extended Addressing Mode (EXT)  | 114 |

|     | 7.3.6     | Indexed Addressing Mode         | 114 |

| 7.4 | Special ( | Operations                      | 115 |

|     | 7.4.1     | Reset Sequence                  | 115 |

|     | 7.4.2     | Interrupt Sequence              |     |

|     | 7.4.3     | Wait Mode Operation             | 116 |

|     | 7.4.4     | Stop Mode Operation             | 116 |

|     | 7.4.5     | BGND Instruction                | 117 |

| 7.5 | HCS08 I   | nstruction Set Summary          |     |

## Chapter 8 Internal Clock Generator (S08ICGV4)

| Introduc |                                                                                                                                                                         |                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 8.1.1    | Features                                                                                                                                                                | 131                                         |

| 8.1.2    | Modes of Operation                                                                                                                                                      | 132                                         |

| 8.1.3    | Block Diagram                                                                                                                                                           | 133                                         |

| External | Signal Description                                                                                                                                                      | 133                                         |

| 8.2.1    | EXTAL — External Reference Clock / Oscillator Input                                                                                                                     | 133                                         |

| 8.2.2    | XTAL — Oscillator Output                                                                                                                                                | 133                                         |

| 8.2.3    | External Clock Connections                                                                                                                                              | 134                                         |

| 8.2.4    | External Crystal/Resonator Connections                                                                                                                                  | 134                                         |

| Register | Definition                                                                                                                                                              | 135                                         |

| 8.3.1    | ICG Control Register 1 (ICGC1)                                                                                                                                          | 135                                         |

| 8.3.2    | ICG Control Register 2 (ICGC2)                                                                                                                                          | 137                                         |

| 8.3.3    | ICG Status Register 1 (ICGS1)                                                                                                                                           | 138                                         |

| 8.3.4    | ICG Status Register 2 (ICGS2)                                                                                                                                           | 139                                         |

| 8.3.5    | ICG Filter Registers (ICGFLTU, ICGFLTL)                                                                                                                                 | 139                                         |

| 8.3.6    | ICG Trim Register (ICGTRM)                                                                                                                                              | 140                                         |

| Function |                                                                                                                                                                         |                                             |

| 8.4.1    | Off Mode (Off)                                                                                                                                                          | 141                                         |

| 8.4.2    |                                                                                                                                                                         |                                             |

| 8.4.3    | FLL Engaged, Internal Clock (FEI) Mode                                                                                                                                  | 142                                         |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>External<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Register<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Function<br>8.4.1<br>8.4.2 | <ul> <li>8.1.2 Modes of Operation</li></ul> |

### MC9S08AW60 Data Sheet, Rev 2

**Chapter 3 Modes of Operation**

| Devinheral        | Mode                       |                            |  |  |  |

|-------------------|----------------------------|----------------------------|--|--|--|

| Peripheral        | Stop2                      | Stop3                      |  |  |  |

| КВІ               | Off                        | Optionally On <sup>3</sup> |  |  |  |

| RTI               | Optionally On <sup>4</sup> | Optionally On <sup>4</sup> |  |  |  |

| SCI               | Off                        | Standby                    |  |  |  |

| SPI               | Off                        | Standby                    |  |  |  |

| ТРМ               | Off                        | Standby                    |  |  |  |

| Voltage Regulator | Standby                    | Standby                    |  |  |  |

| I/O Pins          | States Held                | States Held                |  |  |  |

#### Table 3-4. Stop Mode Behavior (continued)

<sup>1</sup> Requires the asynchronous ADC clock and LVD to be enabled, else in standby.

<sup>2</sup> OSCSTEN set in ICSC1, else in standby. For high frequency range (RANGE in ICSC2 set) requires the LVD to also be enabled in stop3.

<sup>3</sup> During stop3, KBI pins that are enabled continue to function as interrupt sources that are capable of waking the MCU from stop3.

<sup>4</sup> This RTI can be enabled to run in stop2 or stop3 with the internal RTI clock source (RTICLKS = 0, in SRTISC). The RTI also can be enabled to run in stop3 with the external clock source (RTICLKS = 1 and OSCSTEN = 1).

Chapter 6 Parallel Input/Output

## 6.7.9 Port E I/O Registers (PTED and PTEDD)

Port E parallel I/O function is controlled by the registers listed below.

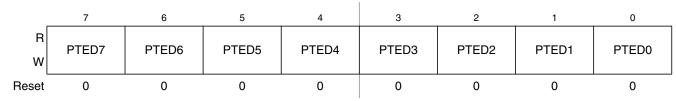

### Figure 6-29. Port E Data Register (PTED)

### Table 6-22. PTED Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTED[7:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-30. Data Direction for Port E (PTEDD)

### Table 6-23. PTEDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 7:0        | Data Direction for Port E Bits — These read/write bits control the direction of port E pins and what is read for |

| PTEDD[7:0] | PTED reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.                            |

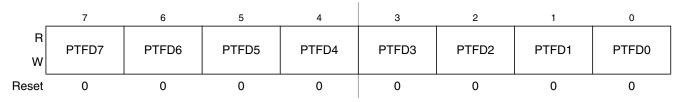

### 6.7.11 Port F I/O Registers (PTFD and PTFDD)

Port F parallel I/O function is controlled by the registers listed below.

#### Figure 6-34. Port F Data Register (PTFD)

| Table 6-27. | PTFD | Register | Field | Descriptions |

|-------------|------|----------|-------|--------------|

|-------------|------|----------|-------|--------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFD[7:0] | Port F Data Register Bits— For port F pins that are inputs, reads return the logic level on the pin. For port F pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTFD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDD7 | PTFDD6 | PTFDD5 | PTFDD4 | PTFDD3 | PTFDD2 | PTFDD1 | PTFDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-35. Data Direction for Port F (PTFDD)

#### Table 6-28. PTFDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 7:0        | Data Direction for Port F Bits — These read/write bits control the direction of port F pins and what is read for |

| PTFDD[7:0] | PTFD reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port F bit n and PTFD reads return the contents of PTFDn.                            |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

### MC9S08AW60 Data Sheet, Rev 2

- 0 = Bit forced to 0

- 1 = Bit forced to 1

- = Bit set or cleared according to results of operation

- U = Undefined after the operation

### Machine coding notation

- dd = Low-order 8 bits of a direct address 0x0000-0x00FF (high byte assumed to be 0x00)

- ee = Upper 8 bits of 16-bit offset

- ff = Lower 8 bits of 16-bit offset or 8-bit offset

- ii = One byte of immediate data

- jj = High-order byte of a 16-bit immediate data value

- kk = Low-order byte of a 16-bit immediate data value

- hh = High-order byte of 16-bit extended address

- II = Low-order byte of 16-bit extended address

- rr = Relative offset

### Source form

Everything in the source forms columns, *except expressions in italic characters*, is literal information that must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic is always a literal expression. All commas, pound signs (#), parentheses, and plus signs (+) are literal characters.

- n Any label or expression that evaluates to a single integer in the range 0–7

- opr8i Any label or expression that evaluates to an 8-bit immediate value

- opr16i Any label or expression that evaluates to a 16-bit immediate value

- *opr8a* Any label or expression that evaluates to an 8-bit value. The instruction treats this 8-bit value as the low order 8 bits of an address in the direct page of the 64-Kbyte address space (0x00xx).

- *opr16a* Any label or expression that evaluates to a 16-bit value. The instruction treats this value as an address in the 64-Kbyte address space.

- *oprx8* Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing

- *oprx16* Any label or expression that evaluates to a 16-bit value. Because the HCS08 has a 16-bit address bus, this can be either a signed or an unsigned value.

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the next address after the last byte of object code for the current instruction. The assembler will calculate the 8-bit signed offset and include it in the object code for this instruction.

### Address modes

- INH = Inherent (no operands)

- IMM = 8-bit or 16-bit immediate

- DIR = 8-bit direct

- EXT = 16-bit extended

MC9S08AW60 Data Sheet, Rev 2

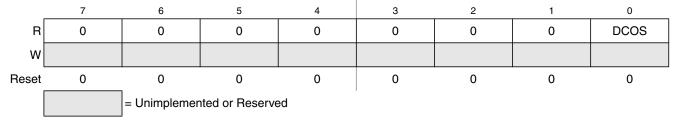

### 8.3.4 ICG Status Register 2 (ICGS2)

### Figure 8-9. ICG Status Register 2 (ICGS2)

#### Table 8-4. ICGS2 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | <ul> <li>DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n<sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.</li> <li>0 DCO clock is unstable.</li> <li>1 DCO clock is stable.</li> </ul> |

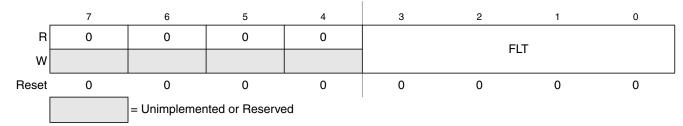

### 8.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

### Figure 8-10. ICG Upper Filter Register (ICGFLTU)

### Table 8-5. ICGFLTU Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

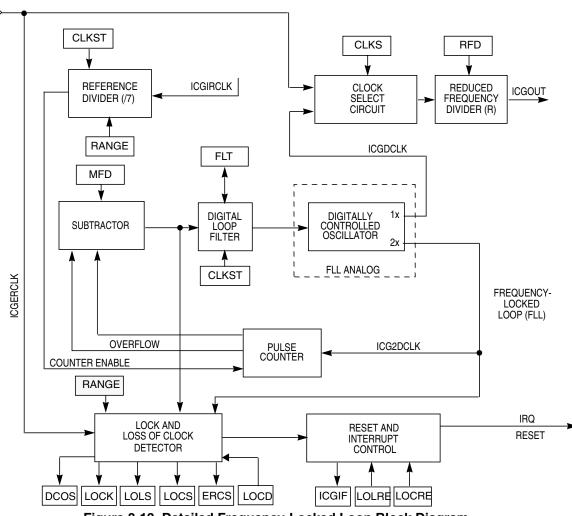

Chapter 8 Internal Clock Generator (S08ICGV4)

entering off mode. If CLKS bits are set to 01 or 11 coming out of the Off state, the ICG enters this mode until ICGDCLK is stable as determined by the DCOS bit. After ICGDCLK is considered stable, the ICG automatically closes the loop by switching to FLL engaged (internal or external) as selected by the CLKS bits.

Figure 8-13. Detailed Frequency-Locked Loop Block Diagram

## 8.4.3 FLL Engaged, Internal Clock (FEI) Mode

FLL engaged internal (FEI) is entered when any of the following conditions occur:

- CLKS bits are written to 01

- The DCO clock stabilizes (DCOS = 1) while in SCM upon exiting the off state with CLKS = 01

In FLL engaged internal mode, the reference clock is derived from the internal reference clock ICGIRCLK, and the FLL loop will attempt to lock the ICGDCLK frequency to the desired value, as selected by the MFD bits.

### 8.5.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz

In this example, the FLL will be used (in FEE mode) to multiply the external 4 MHz oscillator up to 40-MHz to achieve 20 MHz bus frequency.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

During reset initialization software, the clock scheme will be set to FLL engaged, external (FEE). So

Solving for N / R gives:

```

N / R = 40 MHz /(4 MHz * 1) = 10 ; We can choose N = 10 and R = 1 Eqn. 8-4

```

The values needed in each register to set up the desired operation are:

ICGC1 = \$78 (%01111000)

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                      |

|----------|---------|----|--------------------------------------------------------------------------|

| Bit 6    | RANGE   | 1  | Configures oscillator for high-frequency range; FLL prescale factor is 1 |

| Bit 5    | REFS    | 1  | Requests an oscillator                                                   |

| Bits 4:3 | CLKS    | 11 | FLL engaged, external reference clock mode                               |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator                                                  |

| Bit 1    | LOCD    | 0  | Loss-of-clock detection enabled                                          |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                             |

### ICGC2 = \$30 (%00110000)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 000 | Sets the RFD division factor to ÷1              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 =\$xx

This is read only. Should read DCOS before performing any time critical tasks

### ICGFLTLU/L =\$xx

Not used in this example

### ICGTRM

Not used in this example

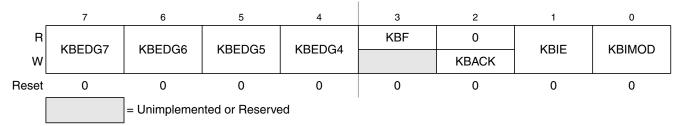

## 9.4.1 KBI Status and Control Register (KBI1SC)

### Figure 9-3. KBI Status and Control Register (KBI1SC)

#### Table 9-2. KBI1SC Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4<br>KBEDG[7:4] | <ul> <li>Keyboard Edge Select for KBI Port Bits — Each of these read/write bits selects the polarity of the edges and/or levels that are recognized as trigger events on the corresponding KBI port pin when it is configured as a keyboard interrupt input (KBIPEn = 1). Also see the KBIMOD control bit, which determines whether the pin is sensitive to edges-only or edges and levels.</li> <li>Falling edges/low levels</li> <li>Rising edges/high levels</li> </ul>                                                                                                              |

| 3<br>KBF          | <ul> <li>Keyboard Interrupt Flag — This read-only status flag is set whenever the selected edge event has been detected on any of the enabled KBI port pins. This flag is cleared by writing a 1 to the KBACK control bit. The flag will remain set if KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level.</li> <li>KBF can be used as a software pollable flag (KBIE = 0) or it can generate a hardware interrupt request to the CPU (KBIE = 1).</li> <li>0 No KBI interrupt pending</li> <li>1 KBI interrupt pending</li> </ul> |

| 2<br>KBACK        | <b>Keyboard Interrupt Acknowledge</b> — This write-only bit (reads always return 0) is used to clear the KBF status flag by writing a 1 to KBACK. When KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level, KBF is being continuously set so writing 1 to KBACK does not clear the KBF flag.                                                                                                                                                                                                                                       |

| 1<br>KBIE         | <ul> <li>Keyboard Interrupt Enable — This read/write control bit determines whether hardware interrupts are generated when the KBF status flag equals 1. When KBIE = 0, no hardware interrupts are generated, but KBF can still be used for software polling.</li> <li>0 KBF does not generate hardware interrupts (use polling)</li> <li>1 KBI hardware interrupt requested when KBF = 1</li> </ul>                                                                                                                                                                                    |

| KBIMOD            | <ul> <li>Keyboard Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. KBI port bits 3 through 0 can detect falling edges-only or falling edges and low levels. KBI port bits 7 through 4 can be configured to detect either: <ul> <li>Rising edges-only or rising edges and high levels (KBEDGn = 1)</li> <li>Falling edges-only or falling edges and low levels (KBEDGn = 0)</li> </ul> </li> <li>0 Edge-only detection <ul> <li>1 Edge-and-level detection</li> </ul> </li> </ul>                                            |

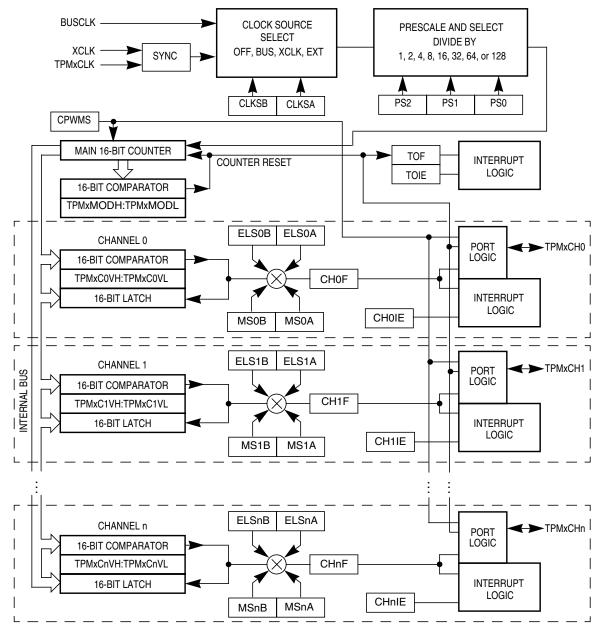

Chapter 10 Timer/Pulse-Width Modulator (S08TPMV2)

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF effectively make the counter free running.) Software can read the counter value at any time without affecting the counting sequence. Any write to either byte of the TPMxCNT counter resets the counter regardless of the data value written.

# Chapter 12 Serial Peripheral Interface (S08SPIV3)

The MC9S08AW60 Series has one serial peripheral interface (SPI) module. The four pins associated with SPI functionality are shared with port E pins 4–7. See Appendix A, "Electrical Characteristics and Timing Specifications," for SPI electrical parametric information.

Chapter 12 Serial Peripheral Interface (S08SPIV3)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>ACFE  | <ul> <li>Compare Function Enable — ACFE is used to enable the compare function.</li> <li>0 Compare function disabled</li> <li>1 Compare function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>ACFGT | <ul> <li>Compare Function Greater Than Enable — ACFGT is used to configure the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.</li> <li>0 Compare triggers when input is less than compare level</li> <li>1 Compare triggers when input is greater than or equal to compare level</li> </ul> |

Table 14-4. ADC1SC2 Register Field Descriptions (continued)

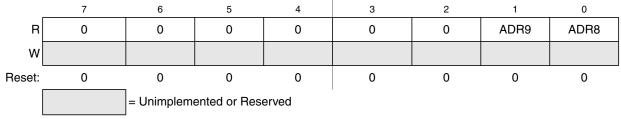

### 14.4.3 Data Result High Register (ADC1RH)

ADC1RH contains the upper two bits of the result of a 10-bit conversion. When configured for 8-bit conversions both ADR8 and ADR9 are equal to zero. ADC1RH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit MODE, reading ADC1RH prevents the ADC from transferring subsequent conversion results into the result registers until ADC1RL is read. If ADC1RL is not read until after the next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode there is no interlocking with ADC1RL. In the case that the MODE bits are changed, any data in ADC1RH becomes invalid.

Figure 14-6. Data Result High Register (ADC1RH)

### 14.4.4 Data Result Low Register (ADC1RL)

ADC1RL contains the lower eight bits of the result of a 10-bit conversion, and all eight bits of an 8-bit conversion. This register is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit mode, reading ADC1RH prevents the ADC from transferring subsequent conversion results into the result registers until ADC1RL is read. If ADC1RL is not read until the after next conversion is completed, then the intermediate conversion results will be lost. In 8-bit mode, there is no interlocking with ADC1RH. In the case that the MODE bits are changed, any data in ADC1RL becomes invalid.

#### Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

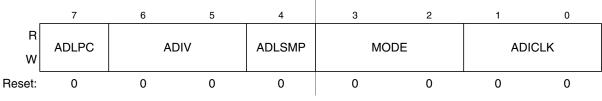

Figure 14-10. Configuration Register (ADC1CFG)

Table 14-5. ADC1CFG Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC    | <ul> <li>Low Power Configuration — ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.</li> <li>0 High speed configuration</li> <li>1 Low power configuration: {FC31}The power is reduced at the expense of maximum clock speed.</li> </ul>                                                                                                    |

| 6:5<br>ADIV   | <b>Clock Divide Select</b> — ADIV select the divide ratio used by the ADC to generate the internal clock ADCK.<br>Table 14-6 shows the available clock configurations.                                                                                                                                                                                                                                                                                                       |

| 4<br>ADLSMP   | <ul> <li>Long Sample Time Configuration — ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.</li> <li>Short sample time</li> <li>Long sample time</li> </ul> |

| 3:2<br>MODE   | <b>Conversion Mode Selection</b> — MODE bits are used to select between 10- or 8-bit operation. See Table 14-7.                                                                                                                                                                                                                                                                                                                                                              |

| 1:0<br>ADICLK | Input Clock Select — ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 14-8.                                                                                                                                                                                                                                                                                                                                                          |

#### Table 14-6. Clock Divide Select

| ADIV | Divide Ratio | Clock Rate      |  |  |

|------|--------------|-----------------|--|--|

| 00   | 1            | Input clock     |  |  |

| 01   | 2            | Input clock ÷ 2 |  |  |

| 10   | 4            | Input clock ÷ 4 |  |  |

| 11   | 8            | Input clock ÷ 8 |  |  |

### Table 14-7. Conversion Modes

| MODE | Mode Description         |  |  |  |

|------|--------------------------|--|--|--|

| 00   | 8-bit conversion (N=8)   |  |  |  |

| 01   | Reserved                 |  |  |  |

| 10   | 10-bit conversion (N=10) |  |  |  |

| 11   | Reserved                 |  |  |  |

Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

### 14.5.4.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADC1RH and ADC1RL. This is indicated by the setting of COCO. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADC1RH and ADC1RL if the previous data is in the process of being read while in 10-bit MODE (the ADC1RH register has been read but the ADC1RL register has not). When blocking is active, the data transfer is blocked, COCO is not set, and the new result is lost. In the case of single conversions with the compare function enabled and the compare condition false, blocking has no effect and ADC operation is terminated. In all other cases of operation, when a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled).

If single conversions are enabled, the blocking mechanism could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

### 14.5.4.3 Aborting Conversions

Any conversion in progress will be aborted when:

- A write to ADC1SC1 occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADC1SC2, ADC1CFG, ADC1CVH, or ADC1CVL occurs. This indicates a mode of operation change has occurred and the current conversion is therefore invalid.

- The MCU is reset.

- The MCU enters stop mode with ADACK not enabled.

When a conversion is aborted, the contents of the data registers, ADC1RH and ADC1RL, are not altered but continue to be the values transferred after the completion of the last successful conversion. In the case that the conversion was aborted by a reset, ADC1RH and ADC1RL return to their reset states.

### 14.5.4.4 Power Control

The ADC module remains in its idle state until a conversion is initiated. If ADACK is selected as the conversion clock source, the ADACK clock generator is also enabled.

Power consumption when active can be reduced by setting ADLPC. This results in a lower maximum value for  $f_{ADCK}$  (see the electrical specifications).

### 14.5.4.5 Total Conversion Time

The total conversion time depends on the sample time (as determined by ADLSMP), the MCU bus frequency, the conversion mode (8-bit or 10-bit), and the frequency of the conversion clock ( $f_{ADCK}$ ). After the module becomes active, sampling of the input begins. ADLSMP is used to select between short and long sample times. When sampling is complete, the converter is isolated from the input channel and a successive approximation algorithm is performed to determine the digital value of the analog signal. The

### 15.4.3.5 Debug FIFO High Register (DBGFH)

This register provides read-only access to the high-order eight bits of the FIFO. Writes to this register have no meaning or effect. In the event-only trigger modes, the FIFO only stores data into the low-order byte of each FIFO word, so this register is not used and will read 0x00.

Reading DBGFH does not cause the FIFO to shift to the next word. When reading 16-bit words out of the FIFO, read DBGFH before reading DBGFL because reading DBGFL causes the FIFO to advance to the next word of information.

### 15.4.3.6 Debug FIFO Low Register (DBGFL)

This register provides read-only access to the low-order eight bits of the FIFO. Writes to this register have no meaning or effect.

Reading DBGFL causes the FIFO to shift to the next available word of information. When the debug module is operating in event-only modes, only 8-bit data is stored into the FIFO (high-order half of each FIFO word is unused). When reading 8-bit words out of the FIFO, simply read DBGFL repeatedly to get successive bytes of data from the FIFO. It isn't necessary to read DBGFH in this case.

Do not attempt to read data from the FIFO while it is still armed (after arming but before the FIFO is filled or ARMF is cleared) because the FIFO is prevented from advancing during reads of DBGFL. This can interfere with normal sequencing of reads from the FIFO.

Reading DBGFL while the debugger is not armed causes the address of the most-recently fetched opcode to be stored to the last location in the FIFO. By reading DBGFH then DBGFL periodically, external host software can develop a profile of program execution. After eight reads from the FIFO, the ninth read will return the information that was stored as a result of the first read. To use the profiling feature, read the FIFO eight times without using the data to prime the sequence and then begin using the data to get a delayed picture of what addresses were being executed. The information stored into the FIFO on reads of DBGFL (while the FIFO is not armed) is the address of the most-recently fetched opcode.

Appendix A Electrical Characteristics and Timing Specifications

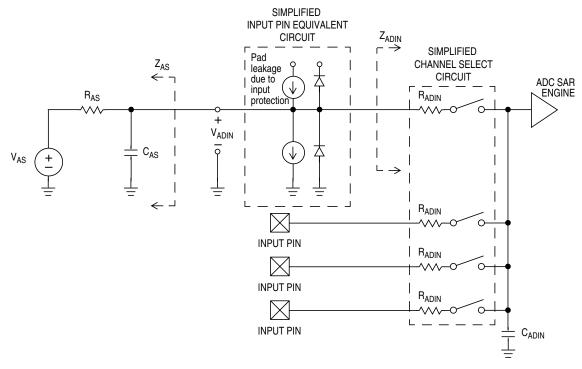

Figure A-8. ADC Input Impedance Equivalency Diagram

| Characteristic                                        | Conditions                 | С | Symb              | Min | Typ <sup>1</sup> | Мах | Unit |

|-------------------------------------------------------|----------------------------|---|-------------------|-----|------------------|-----|------|

| Supply current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 |                            | Т | I <sub>DDAD</sub> |     | 133              |     | μA   |

| Supply current<br>ADLPC = 1<br>ADLSMP = 0<br>ADCO = 1 |                            | Т | I <sub>DDAD</sub> | _   | 218              |     | μΑ   |

| Supply current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 |                            | Т | I <sub>DDAD</sub> | _   | 327              |     | μA   |

| Supply current<br>ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1 | V <sub>DDAD</sub> ≤ 5.5 V  | Р | I <sub>DDAD</sub> |     | 582              | 990 | μΑ   |

| Supply current                                        | Stop, reset,<br>module off |   | I <sub>DDAD</sub> | _   | 0.011            | 1   | μA   |