Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 508                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LQFP                                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08aw32cfge |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 4 Memory

## 4.4.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased. In the 60K version, there are two instances where the size of a block that is accessible to the user is less than 512 bytes: the first page following RAM, and the first page following the high page registers. These pages are overlapped by the RAM and high page registers respectively.

### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (\$05), byte program (\$20), burst program (\$25), page erase (\$40), and mass erase (\$41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-3 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized before using any FLASH commands. This only must be done once following a reset.

## 4.4.5 Access Errors

An access error occurs whenever the command execution protocol is violated.

Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

- Writing to a FLASH address before the internal FLASH clock frequency has been set by writing to the FCDIV register

- Writing to a FLASH address while FCBEF is not set (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a FLASH address before launching the previous command (There is only one write to FLASH for every command.)

- Writing a second time to FCMD before launching the previous command (There is only one write to FCMD for every command.)

- Writing to any FLASH control register other than FCMD after writing to a FLASH address

- Writing any command code other than the five allowed codes (\$05, \$20, \$25, \$40, or \$41) to FCMD

- Accessing (read or write) any FLASH control register other than the write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD.

- The MCU enters stop mode while a program or erase command is in progress (The command is aborted.)

- Writing the byte program, burst program, or page erase command code (\$20, \$25, or \$40) with a background debug command while the MCU is secured (The background debug controller can only do blank check and mass erase commands when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command

# 4.4.6 FLASH Block Protection

The block protection feature prevents the protected region of FLASH from program or erase changes. Block protection is controlled through the FLASH Protection Register (FPROT). When enabled, block protection begins at any 512 byte boundary below the last address of FLASH, \$FFFF. (see Section 4.6.4, "FLASH Protection Register (FPROT and NVPROT)").

After exit from reset, FPROT is loaded with the contents of the NVPROT location which is in the nonvolatile register block of the FLASH memory. FPROT cannot be changed directly from application software so a runaway program cannot alter the block protection settings. Since NVPROT is within the last 512 bytes of FLASH, if any amount of memory is protected, NVPROT is itself protected and cannot be altered (intentionally or unintentionally) by the application software. FPROT can be written through background debug commands which allows a way to erase and reprogram a protected FLASH memory.

The block protection mechanism is illustrated below. The FPS bits are used as the upper bits of the last address of unprotected memory. This address is formed by concatenating FPS7:FPS1 with logic 1 bits as shown. For example, in order to protect the last 8192 bytes of memory (addresses \$E000 through \$FFFF), the FPS bits must be set to 1101 111 which results in the value \$DFFF as the last address of unprotected memory. In addition to programming the FPS bits to the appropriate value, FPDIS (bit 0 of NVPROT) must

Chapter 4 Memory

# 4.6 FLASH Registers and Control Bits

The FLASH module has nine 8-bit registers in the high-page register space, three locations in the nonvolatile register space in FLASH memory which are copied into three corresponding high-page control registers at reset. There is also an 8-byte comparison key in FLASH memory. Refer to Table 4-3 and Table 4-4 for the absolute address assignments for all FLASH registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

# 4.6.1 FLASH Clock Divider Register (FCDIV)

Bit 7 of this register is a read-only status flag. Bits 6 through 0 may be read at any time but can be written only one time. Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

|       | 7     | 6                           | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------|-----------------------------|------|------|------|------|------|------|

| R     | DIVLD |                             |      |      |      |      |      |      |

| w     |       | PRDIV8                      | DIV5 | DIV4 | DIV3 | DIV2 | DIV1 | DIV0 |

| Reset | 0     | 0                           | 0    | 0    | 0    | 0    | 0    | 0    |

|       |       | = Unimplemented or Reserved |      |      |      |      |      |      |

Figure 4-6. FLASH Clock Divider Register (FCDIV)

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD      | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH.</li> </ul>                                                                                                                                                      |

| 6<br>PRDIV8     | <ul> <li>Prescale (Divide) FLASH Clock by 8</li> <li>O Clock input to the FLASH clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5:0<br>DIV[5:0] | <b>Divisor for FLASH Clock Divider</b> — The FLASH clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV5:DIV0 field plus one. The resulting frequency of the internal FLASH clock must fall within the range of 200 kHz to 150 kHz for proper FLASH operations. Program/Erase timing pulses are one cycle of this internal FLASH clock which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1, Equation 4-2, and Table 4-6. |

### Table 4-6. FCDIV Register Field Descriptions

### if PRDIV8 = 0 — $f_{FCLK} = f_{Bus} \div ([DIV5:DIV0] + 1)$ Eqn. 4-1

if PRDIV8 = 1 —

$$f_{FCLK} = f_{Bus} \div (8 \times ([DIV5:DIV0] + 1))$$

Eqn. 4-2

Table 4-7 shows the appropriate values for PRDIV8 and DIV5:DIV0 for selected bus frequencies.

MC9S08AW60 Data Sheet, Rev 2

Chapter 5 Resets, Interrupts, and System Configuration

- Illegal opcode detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self\_reset}$  selected. The reset pin is driven low for 34 bus cycles where the internal bus frequency is half the ICG frequency. After the 34 bus cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 bus cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.9.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods  $(2^{18} \text{ or } 2^{13} \text{ cycles of the bus rate clock})$ . Even if the application will use the reset default settings in COPE and COPT, the user should write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

## 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is a logic 1 to enable the interrupt. The

Chapter 5 Resets, Interrupts, and System Configuration

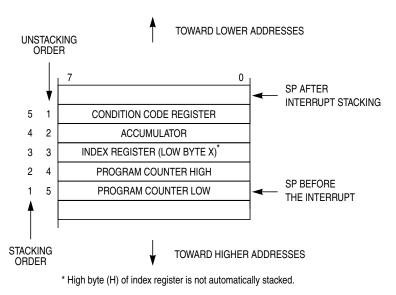

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

The status flag causing the interrupt must be acknowledged (cleared) before returning from the ISR. Typically, the flag should be cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

# 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQSC status and control register. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

### 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in the IRQSC register must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

When the IRQ pin is configured to detect rising edges, an optional pulldown resistor is available rather than a pullup resistor. BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

Chapter 6 Parallel Input/Output

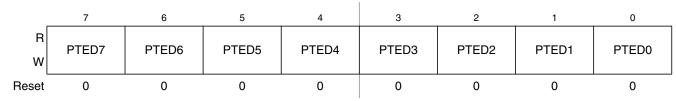

# 6.7.9 Port E I/O Registers (PTED and PTEDD)

Port E parallel I/O function is controlled by the registers listed below.

#### Figure 6-29. Port E Data Register (PTED)

#### Table 6-22. PTED Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTED[7:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-30. Data Direction for Port E (PTEDD)

#### Table 6-23. PTEDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 7:0        | Data Direction for Port E Bits — These read/write bits control the direction of port E pins and what is read for |

| PTEDD[7:0] | PTED reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.                            |

Chapter 7 Central Processor Unit (S08CPUV2)

# 7.3.5 Extended Addressing Mode (EXT)

In extended addressing mode, the full 16-bit address of the operand is located in the next two bytes of program memory after the opcode (high byte first).

## 7.3.6 Indexed Addressing Mode

Indexed addressing mode has seven variations including five that use the 16-bit H:X index register pair and two that use the stack pointer as the base reference.

### 7.3.6.1 Indexed, No Offset (IX)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction.

### 7.3.6.2 Indexed, No Offset with Post Increment (IX+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is only used for MOV and CBEQ instructions.

### 7.3.6.3 Indexed, 8-Bit Offset (IX1)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

### 7.3.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is used only for the CBEQ instruction.

### 7.3.6.5 Indexed, 16-Bit Offset (IX2)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

### 7.3.6.6 SP-Relative, 8-Bit Offset (SP1)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

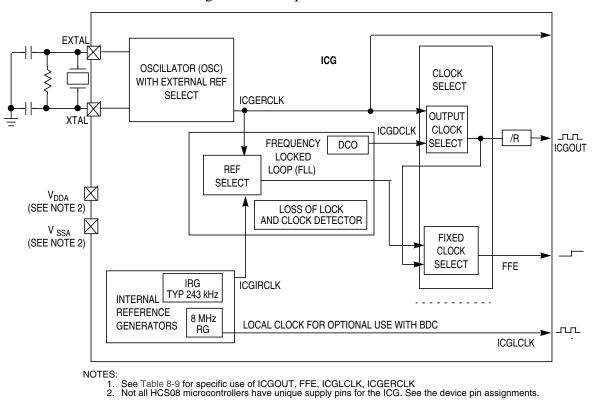

## 8.1.3 Block Diagram

Figure 8-3 is a top-level diagram that shows the functional organization of the internal clock generation (ICG) module. This section includes a general description and a feature list.

Figure 8-3. ICG Block Diagram

# 8.2 External Signal Description

The oscillator pins are used to provide an external clock source for the MCU. The oscillator pins are gain controlled in low-power mode (default). Oscillator amplitudes in low-power mode are limited to approximately 1 V, peak-to-peak.

## 8.2.1 EXTAL — External Reference Clock / Oscillator Input

If upon the first write to ICGC1, either the FEE mode or FBE mode is selected, this pin functions as either the external clock input or the input of the oscillator circuit as determined by REFS. If upon the first write to ICGC1, either the FEI mode or SCM mode is selected, this pin is not used by the ICG.

## 8.2.2 XTAL — Oscillator Output

If upon the first write to ICGC1, either the FEE mode or FBE mode is selected, this pin functions as the output of the oscillator circuit. If upon the first write to ICGC1, either the FEI mode or SCM mode is

## 8.5.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz

In this example, the FLL will be used (in FEE mode) to multiply the external 4 MHz oscillator up to 40-MHz to achieve 20 MHz bus frequency.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

During reset initialization software, the clock scheme will be set to FLL engaged, external (FEE). So

Solving for N / R gives:

```

N / R = 40 MHz /(4 MHz * 1) = 10 ; We can choose N = 10 and R = 1 Eqn. 8-4

```

The values needed in each register to set up the desired operation are:

ICGC1 = \$78 (%01111000)

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                      |

|----------|---------|----|--------------------------------------------------------------------------|

| Bit 6    | RANGE   | 1  | Configures oscillator for high-frequency range; FLL prescale factor is 1 |

| Bit 5    | REFS    | 1  | Requests an oscillator                                                   |

| Bits 4:3 | CLKS    | 11 | FLL engaged, external reference clock mode                               |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator                                                  |

| Bit 1    | LOCD    | 0  | Loss-of-clock detection enabled                                          |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                             |

### ICGC2 = \$30 (%00110000)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 000 | Sets the RFD division factor to ÷1              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 =\$xx

This is read only. Should read DCOS before performing any time critical tasks

### ICGFLTLU/L =\$xx

Not used in this example

### ICGTRM

Not used in this example

# 9.4.1 KBI Status and Control Register (KBI1SC)

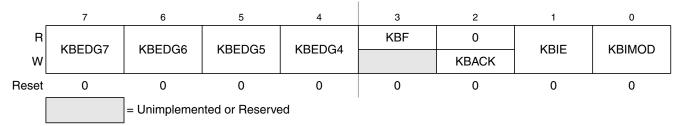

#### Figure 9-3. KBI Status and Control Register (KBI1SC)

#### Table 9-2. KBI1SC Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4<br>KBEDG[7:4] | <ul> <li>Keyboard Edge Select for KBI Port Bits — Each of these read/write bits selects the polarity of the edges and/or levels that are recognized as trigger events on the corresponding KBI port pin when it is configured as a keyboard interrupt input (KBIPEn = 1). Also see the KBIMOD control bit, which determines whether the pin is sensitive to edges-only or edges and levels.</li> <li>Falling edges/low levels</li> <li>Rising edges/high levels</li> </ul>                                                                                                              |

| 3<br>KBF          | <ul> <li>Keyboard Interrupt Flag — This read-only status flag is set whenever the selected edge event has been detected on any of the enabled KBI port pins. This flag is cleared by writing a 1 to the KBACK control bit. The flag will remain set if KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level.</li> <li>KBF can be used as a software pollable flag (KBIE = 0) or it can generate a hardware interrupt request to the CPU (KBIE = 1).</li> <li>0 No KBI interrupt pending</li> <li>1 KBI interrupt pending</li> </ul> |

| 2<br>KBACK        | <b>Keyboard Interrupt Acknowledge</b> — This write-only bit (reads always return 0) is used to clear the KBF status flag by writing a 1 to KBACK. When KBIMOD = 1 to select edge-and-level operation and any enabled KBI port pin remains at the asserted level, KBF is being continuously set so writing 1 to KBACK does not clear the KBF flag.                                                                                                                                                                                                                                       |

| 1<br>KBIE         | <ul> <li>Keyboard Interrupt Enable — This read/write control bit determines whether hardware interrupts are generated when the KBF status flag equals 1. When KBIE = 0, no hardware interrupts are generated, but KBF can still be used for software polling.</li> <li>0 KBF does not generate hardware interrupts (use polling)</li> <li>1 KBI hardware interrupt requested when KBF = 1</li> </ul>                                                                                                                                                                                    |

| KBIMOD            | <ul> <li>Keyboard Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. KBI port bits 3 through 0 can detect falling edges-only or falling edges and low levels. KBI port bits 7 through 4 can be configured to detect either: <ul> <li>Rising edges-only or rising edges and high levels (KBEDGn = 1)</li> <li>Falling edges-only or falling edges and low levels (KBEDGn = 0)</li> </ul> </li> <li>0 Edge-only detection <ul> <li>1 Edge-and-level detection</li> </ul> </li> </ul>                                            |

# 10.4.4 Timer x Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

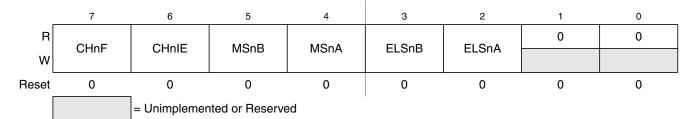

#### Figure 10-8. Timer x Channel n Status and Control Register (TPMxCnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs<br>on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when<br>the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is<br>seldom used with center-aligned PWMs because it is set every time the counter matches the channel value<br>register, which correspond to both edges of the active duty cycle period.<br>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF<br>by reading TPMxCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before<br>the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence<br>was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a<br>previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.<br>0 No input capture or output compare event occurred on channel n<br>1 Input capture or output compare event occurred on channel n |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>O Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 10-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 10-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 10-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 10-4. TPMxCnSC Register Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWU | <ul> <li>Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character (WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware condition automatically clears RWU. Refer to Section 11.3.3.2, "Receiver Wakeup Operation" for more details.</li> <li>0 Normal SCI receiver operation.</li> <li>1 SCI receiver in standby waiting for wakeup condition.</li> </ul> |

| 0<br>SBK | <ul> <li>Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the set and clear of SBK relative to the information currently being transmitted, a second break character may be queued before software clears SBK. Refer to Section 11.3.2.1, "Send Break and Queued Idle" for more details.</li> <li>0 Normal transmitter operation.</li> <li>1 Queue break character(s) to be sent.</li> </ul>                                                                                                                     |

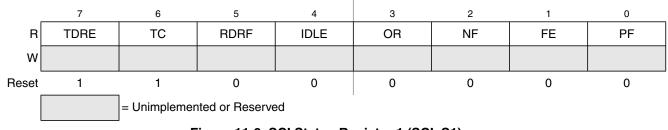

# 11.2.4 SCI Status Register 1 (SCIxS1)

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do not involve writing to this register) are used to clear these status flags.

Figure 11-8. SCI Status Register 1 (SCIxS1)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                         |  |  |  |  |

| 6<br>TC   | <ul> <li>Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.</li> <li>0 Transmitter active (sending data, a preamble, or a break).</li> <li>1 Transmitter idle (transmission activity complete).</li> <li>TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:</li> <li>Write to the SCI data register (SCIxD) to transmit new data</li> <li>Queue a preamble by changing TE from 0 to 1</li> <li>Queue a break character by writing 1 to SBK in SCIxC2</li> </ul> |  |  |  |  |

Chapter 12 Serial Peripheral Interface (S08SPIV3)

### 12.0.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

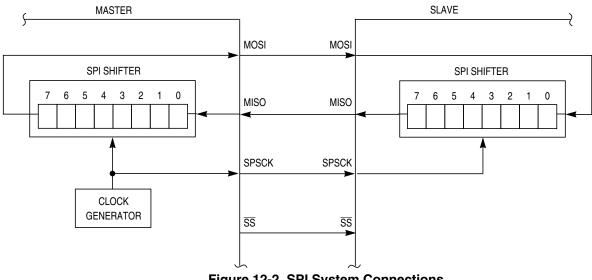

### 12.0.2 Block Diagrams

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 12.0.2.1 SPI System Block Diagram

Figure 12-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 12-2. SPI System Connections

MC9S08AW60 Data Sheet, Rev 2

Chapter 12 Serial Peripheral Interface (S08SPIV3)

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 12-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

### 12.0.2.2 SPI Module Block Diagram

Figure 12-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPI1D) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPI1D). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

### 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

### 13.1.2 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop2 will reset the register contents.

# 14.3.1 Analog Power (V<sub>DDAD</sub>)

The ADC analog portion uses  $V_{DDAD}$  as its power connection. In some packages,  $V_{DDAD}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDAD}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDAD}$  for good results.

## 14.3.2 Analog Ground (V<sub>SSAD</sub>)

The ADC analog portion uses  $V_{SSAD}$  as its ground connection. In some packages,  $V_{SSAD}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSAD}$  pin to the same voltage potential as  $V_{SS}$ .

## 14.3.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDAD}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ).

### 14.3.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSAD}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSAD}$ .

### 14.3.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

# 14.4 Register Definition

These memory mapped registers control and monitor operation of the ADC:

- Status and control register, ADC1SC1

- Status and control register, ADC1SC2

- Data result registers, ADC1RH and ADC1RL

- Compare value registers, ADC1CVH and ADC1CVL

- Configuration register, ADC1CFG

- Pin enable registers, APCTL1, APCTL2, APCTL3

## 14.4.1 Status and Control Register 1 (ADC1SC1)

This section describes the function of the ADC status and control register (ADC1SC1). Writing ADC1SC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

#### **Chapter 15 Development Support**

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a debug pod is connected to BKGD it is possible to force the MCU into active background mode after reset. The specific conditions for forcing active background depend upon the HCS08 derivative (refer to the introduction to this Development Support section). It is not necessary to reset the target MCU to communicate with it through the background debug interface.

### 15.2.2 Communication Details

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Appendix A Electrical Characteristics and Timing Specifications

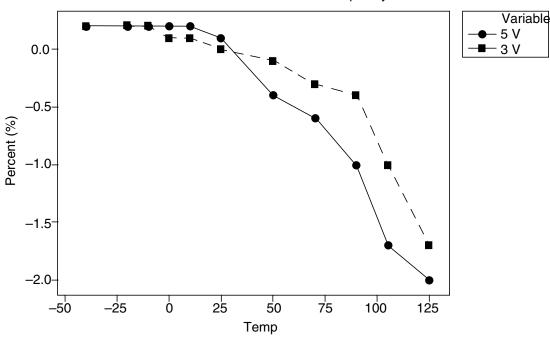

Internal Oscillator Deviation from Trimmed Frequency

Device trimmed at 25°C at 3.0 V.

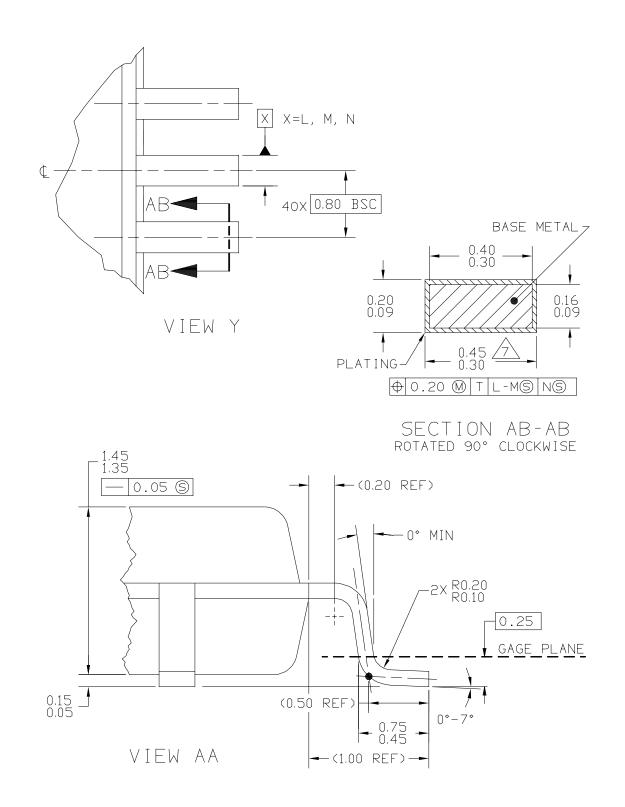

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. |             | L OUTLINE     | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|-------------|---------------|----------------------------|-------------|

| TITLE:<br>44 LD LQFP.                                   | DOCUMENT NE | : 98ASS23225W | RE∨: D                     |             |

| 10 X 10 PKG, 0.8 PITCH,                                 | 1.4 THICK   | CASE NUMBER   | 2:824D-02                  | 26 FEB 2007 |

|                                                         |             | STANDARD: JE  | DEC MS-026 BCB             |             |

DETAIL "A"

SECTION B-B

DETAIL "C"

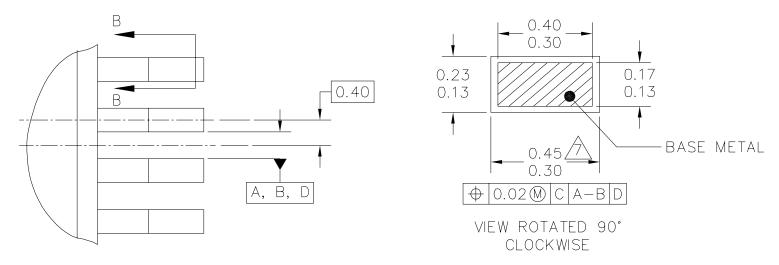

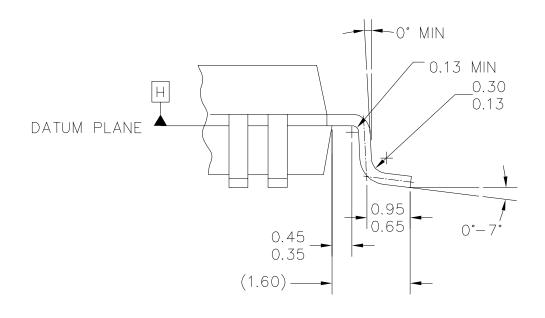

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                | PRINT VERSION NOT TO SCALE |  |

|---------------------------------------------------------|--------------------|----------------|----------------------------|--|

| TITLE:                                                  | DOCUMENT NE        | ]: 98ASB42844B | RE∨: B                     |  |

| 64LD QFP (14 X                                          | CASE NUMBER        | 2: 840B-01     | 20 MAY 2005                |  |

|                                                         |                    | STANDARD: NE   | IN-JEDEC                   |  |