Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 54                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 16x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-QFP                                                      |

| Supplier Device Package    | 64-QFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08aw32vfue |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

| Chapter    | Title                                                | Page |

|------------|------------------------------------------------------|------|

| Chapter 1  | Introduction                                         | 19   |

| Chapter 2  | Pins and Connections                                 | 23   |

| Chapter 3  | Modes of Operation                                   | 33   |

| Chapter 4  | Memory                                               | 39   |

| Chapter 5  | Resets, Interrupts, and System Configuration         | 65   |

| Chapter 6  | Parallel Input/Output                                | 81   |

| Chapter 7  | Central Processor Unit (S08CPUV2)                    | 109  |

| Chapter 8  | Internal Clock Generator (S08ICGV4)                  | 129  |

| Chapter 9  | Keyboard Interrupt (S08KBIV1)                        | 157  |

| Chapter 10 | Timer/PWM (S08TPMV2)                                 | 165  |

| Chapter 11 | Serial Communications Interface (S08SCIV2)           | 181  |

| Chapter 12 | Serial Peripheral Interface (S08SPIV3)               | 199  |

| Chapter 13 | Inter-Integrated Circuit (S08IICV1)                  | 215  |

| Chapter 14 | Analog-to-Digital Converter (S08ADC10V1)             | 233  |

| Chapter 15 | Development Support                                  | 261  |

| Appendix A | Electrical Characteristics and Timing Specifications | 283  |

| Appendix B | Ordering Information and Mechanical Drawings         | 309  |

# **Section Number**

Title

# Page

|     | 7.2.1     | Accumulator (A)                 | 110 |

|-----|-----------|---------------------------------|-----|

|     | 7.2.2     | Index Register (H:X)            |     |

|     | 7.2.3     | Stack Pointer (SP)              |     |

|     | 7.2.4     | Program Counter (PC)            |     |

|     | 7.2.5     | Condition Code Register (CCR)   |     |

| 7.3 | Addressi  | ng Modes                        | 113 |

|     | 7.3.1     | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2     | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3     | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4     | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5     | Extended Addressing Mode (EXT)  | 114 |

|     | 7.3.6     | Indexed Addressing Mode         | 114 |

| 7.4 | Special ( | Operations                      | 115 |

|     | 7.4.1     | Reset Sequence                  | 115 |

|     | 7.4.2     | Interrupt Sequence              |     |

|     | 7.4.3     | Wait Mode Operation             | 116 |

|     | 7.4.4     | Stop Mode Operation             | 116 |

|     | 7.4.5     | BGND Instruction                | 117 |

| 7.5 | HCS08 I   | nstruction Set Summary          |     |

# Chapter 8 Internal Clock Generator (S08ICGV4)

| Introduc |                                                                                                                                                                         |                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 8.1.1    | Features                                                                                                                                                                | 131                                         |

| 8.1.2    | Modes of Operation                                                                                                                                                      | 132                                         |

| 8.1.3    | Block Diagram                                                                                                                                                           | 133                                         |

| External | Signal Description                                                                                                                                                      | 133                                         |

| 8.2.1    | EXTAL — External Reference Clock / Oscillator Input                                                                                                                     | 133                                         |

| 8.2.2    | XTAL — Oscillator Output                                                                                                                                                | 133                                         |

| 8.2.3    | External Clock Connections                                                                                                                                              | 134                                         |

| 8.2.4    | External Crystal/Resonator Connections                                                                                                                                  | 134                                         |

| Register | Definition                                                                                                                                                              | 135                                         |

| 8.3.1    | ICG Control Register 1 (ICGC1)                                                                                                                                          | 135                                         |

| 8.3.2    | ICG Control Register 2 (ICGC2)                                                                                                                                          | 137                                         |

| 8.3.3    | ICG Status Register 1 (ICGS1)                                                                                                                                           | 138                                         |

| 8.3.4    | ICG Status Register 2 (ICGS2)                                                                                                                                           | 139                                         |

| 8.3.5    | ICG Filter Registers (ICGFLTU, ICGFLTL)                                                                                                                                 | 139                                         |

| 8.3.6    | ICG Trim Register (ICGTRM)                                                                                                                                              | 140                                         |

| Function |                                                                                                                                                                         |                                             |

| 8.4.1    | Off Mode (Off)                                                                                                                                                          | 141                                         |

| 8.4.2    |                                                                                                                                                                         |                                             |

| 8.4.3    | FLL Engaged, Internal Clock (FEI) Mode                                                                                                                                  | 142                                         |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>External<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Register<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Function<br>8.4.1<br>8.4.2 | <ul> <li>8.1.2 Modes of Operation</li></ul> |

#### MC9S08AW60 Data Sheet, Rev 2

**Section Number**

## Title

Page

# Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

| 14.1 | Overview    | /                                           | 233 |

|------|-------------|---------------------------------------------|-----|

| 14.2 | Channel .   | Assignments                                 | 233 |

|      | 14.2.1      | Alternate Clock                             |     |

|      | 14.2.2      | Hardware Trigger                            | 234 |

|      | 14.2.3      | Temperature Sensor                          | 235 |

|      | 14.2.4      | Features                                    | 237 |

|      | 14.2.5      | Block Diagram                               | 237 |

| 14.3 | External    | Signal Description                          | 238 |

|      | 14.3.1      | Analog Power (V <sub>DDAD</sub> )           | 239 |

|      | 14.3.2      | Analog Ground (V <sub>SSAD</sub> )          |     |

|      | 14.3.3      | Voltage Reference High (V <sub>REFH</sub> ) | 239 |

|      | 14.3.4      | Voltage Reference Low (V <sub>REFL</sub> )  |     |

|      | 14.3.5      | Analog Channel Inputs (ADx)                 |     |

| 14.4 | Register 1  | Definition                                  | 239 |

|      | 14.4.1      | Status and Control Register 1 (ADC1SC1)     | 239 |

|      | 14.4.2      | Status and Control Register 2 (ADC1SC2)     | 241 |

|      | 14.4.3      | Data Result High Register (ADC1RH)          | 242 |

|      | 14.4.4      | Data Result Low Register (ADC1RL)           | 242 |

|      | 14.4.5      | Compare Value High Register (ADC1CVH)       | 243 |

|      | 14.4.6      | Compare Value Low Register (ADC1CVL)        | 243 |

|      | 14.4.7      | Configuration Register (ADC1CFG)            |     |

|      | 14.4.8      | Pin Control 1 Register (APCTL1)             | 245 |

|      | 14.4.9      | Pin Control 2 Register (APCTL2)             | 246 |

|      | 14.4.10     | Pin Control 3 Register (APCTL3)             | 247 |

| 14.5 | Functiona   | al Description                              | 248 |

|      | 14.5.1      | Clock Select and Divide Control             | 248 |

|      | 14.5.2      | Input Select and Pin Control                | 249 |

|      | 14.5.3      | Hardware Trigger                            | 249 |

|      | 14.5.4      | Conversion Control                          | 249 |

|      | 14.5.5      | Automatic Compare Function                  | 252 |

|      | 14.5.6      | MCU Wait Mode Operation                     | 252 |

|      | 14.5.7      | MCU Stop3 Mode Operation                    | 252 |

|      | 14.5.8      | MCU Stop1 and Stop2 Mode Operation          | 253 |

| 14.6 | Initializat | tion Information                            |     |

|      | 14.6.1      | ADC Module Initialization Example           | 253 |

| 14.7 | Applicati   | on Information                              |     |

|      | 14.7.1      | External Pins and Routing                   | 255 |

|      | 14.7.2      | Sources of Error                            |     |

# 2.3.3 RESET Pin

**RESET** is a dedicated pin with a pullup device built in. It has input hysteresis, a high current output driver, and no output slew rate control. Internal power-on reset and low-voltage reset circuitry typically make external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background debug connector so a development system can directly reset the MCU system. If desired, a manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

Whenever any reset is initiated (whether from an external signal or from an internal system), the reset pin is driven low for approximately 34 bus cycles, released, and sampled again approximately 38 bus cycles later. If reset was caused by an internal source such as low-voltage reset or watchdog timeout, the circuitry expects the reset pin sample to return a logic 1. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system control reset status register (SRS).

In EMC-sensitive applications, an external RC filter is recommended on the reset pin. See Figure 2-4 for an example.

# 2.3.4 Background/Mode Select (BKGD/MS)

While in reset, the BKGD/MS pin functions as a mode select pin. Immediately after reset rises the pin functions as the background pin and can be used for background debug communication. While functioning as a background/mode select pin, the pin includes an internal pullup device, input hysteresis, a standard output driver, and no output slew rate control.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during the rising edge of reset which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

# 2.3.5 ADC Reference Pins (V<sub>REFH</sub>, V<sub>REFL</sub>)

The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs respectively for the ADC module.

# 2.3.6 External Interrupt Pin (IRQ)

The IRQ pin is the input source for the IRQ interrupt and is also the input for the BIH and BIL instructions. If the IRQ function is not enabled, this pin does not perform any function.

Chapter 5 Resets, Interrupts, and System Configuration

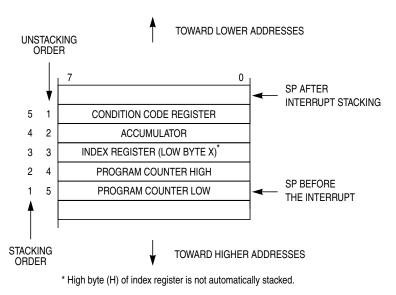

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

The status flag causing the interrupt must be acknowledged (cleared) before returning from the ISR. Typically, the flag should be cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

# 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQSC status and control register. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

# 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in the IRQSC register must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

When the IRQ pin is configured to detect rising edges, an optional pulldown resistor is available rather than a pullup resistor. BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

**Chapter 6 Parallel Input/Output**

- Software-controlled slew rate output buffers

- Eight port A pins

- Eight port B pins shared with ADC1

- Seven port C pins shared with SCI2, IIC1, and MCLK

- Eight port D pins shared with ADC1, KBI1, and TPM1 and TPM2 external clock inputs

- Eight port E pins shared with SCI1, TPM1, and SPI1

- Eight port F pins shared with TPM1 and TPM2

- Seven port G pins shared with XTAL, EXTAL, and KBI1

# 6.3 Pin Descriptions

The MC9S08AW60 Series has a total of 54 parallel I/O pins in seven ports (PTA–PTG). Not all pins are bonded out in all packages. Consult the pin assignment in Chapter 2, "Pins and Connections," for available parallel I/O pins. All of these pins are available for general-purpose I/O when they are not used by other on-chip peripheral systems.

After reset, the shared peripheral functions are disabled so that the pins are controlled by the parallel I/O. All of the parallel I/O are configured as inputs (PTxDDn = 0). The pin control functions for each pin are configured as follows: slew rate control enabled (PTxSEn = 1), low drive strength selected (PTxDSn = 0), and internal pullups disabled (PTxPEn = 0).

The following paragraphs discuss each port and the software controls that determine each pin's use.

## 6.3.1 Port A

| Port A |          | Bit 7 | 6      | 5           | 4        | 3    | 2    | 1    | Bit 0 |

|--------|----------|-------|--------|-------------|----------|------|------|------|-------|

|        | MCU Pin: | PTA7  | PTA6   | PTA5        | PTA4     | PTA3 | PTA2 | PTA1 | PTA0  |

|        |          |       | Figure | e 6-1. Port | A Pin Na | imes |      |      |       |

Port A pins are general-purpose I/O pins. Parallel I/O function is controlled by the port A data (PTAD) and data direction (PTADD) registers which are located in page zero register space. The pin control registers, pullup enable (PTAPE), slew rate control (PTASE), and drive strength select (PTADS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

## 6.3.2 Port B

| Port B |          | Bit 7          | 6              | 5              | 4              | 3              | 2              | 1              | Bit 0          |

|--------|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|        | MCU Pin: | PTB7/<br>AD1P7 | PTB6/<br>AD1P6 | PTB5/<br>AD1P5 | PTB4/<br>AD1P4 | PTB3/<br>AD1P3 | PTB2/<br>AD1P2 | PTB1/<br>AD1P1 | PTB0/<br>AD1P0 |

|        |          |                | <b>F</b> :     |                |                |                |                |                |                |

Figure 6-2. Port B Pin Names

MC9S08AW60 Data Sheet, Rev 2

#### Chapter 6 Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _ |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|

| R<br>W | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |   |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |   |

## Figure 6-18. Output Drive Strength Selection for Port B (PTBDS)

### Table 6-11. PTBDS Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin.</li> <li>0 Low output drive enabled for port B bit n.</li> <li>1 High output drive enabled for port B bit n.</li> </ul> |

#### Chapter 6 Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTDDS7 | PTDDS6 | PTDDS5 | PTDDS4 | PTDDS3 | PTDDS2 | PTDDS1 | PTDDS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

## Figure 6-28. Output Drive Strength Selection for Port D (PTDDS)

## Table 6-21. PTDDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTDDS[7:0] | <ul> <li>Output Drive Strength Selection for Port D Bits — Each of these control bits selects between low and high output drive for the associated PTD pin.</li> <li>0 Low output drive enabled for port D bit n.</li> <li>1 High output drive enabled for port D bit n.</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

# 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08AW60 Data Sheet, Rev 2

Chapter 7 Central Processor Unit (S08CPUV2)

# 7.5 HCS08 Instruction Set Summary

### **Instruction Set Summary Nomenclature**

The nomenclature listed here is used in the instruction descriptions in Table 7-2.

## Operators

- () = Contents of register or memory location shown inside parentheses

- $\leftarrow$  = Is loaded with (read: "gets")

- **&** = Boolean AND

- $\mid$  = Boolean OR

- $\oplus$  = Boolean exclusive-OR

- $\times$  = Multiply

- $\div$  = Divide

- : = Concatenate

- + = Add

- = Negate (two's complement)

### **CPU registers**

- A = Accumulator

- CCR = Condition code register

- H = Index register, higher order (most significant) 8 bits

- X = Index register, lower order (least significant) 8 bits

- PC = Program counter

- PCH = Program counter, higher order (most significant) 8 bits

- PCL = Program counter, lower order (least significant) 8 bits

- SP = Stack pointer

### Memory and addressing

- M = A memory location or absolute data, depending on addressing mode

- M:M + 0x0001= A 16-bit value in two consecutive memory locations. The higher-order (most significant) 8 bits are located at the address of M, and the lower-order (least significant) 8 bits are located at the next higher sequential address.

### Condition code register (CCR) bits

- V = Two's complement overflow indicator, bit 7

- H = Half carry, bit 4

- I = Interrupt mask, bit 3

- N = Negative indicator, bit 2

- Z = Zero indicator, bit 1

- **C** = Carry/borrow, bit 0 (carry out of bit 7)

### CCR activity notation

- = Bit not affected

\_\_\_\_\_

| Source                                                                                                         |                                                            | <b></b>                                                               |   |   |   | eci<br>CC |    |   | ess                                                                                                      | ode                                          | and                                 | Cycles <sup>1</sup>             |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|---|---|---|-----------|----|---|----------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                           | Operation                                                  | Description                                                           | v | н | I | N         | z  | с | Address<br>Mode                                                                                          | Opcode                                       | Operand                             | Bus Cy                          |

| BCLR n,opr8a                                                                                                   | Clear Bit n in Memory                                      | Mn ← 0                                                                | _ | _ | _ | _         | _  | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F | dd<br>dd<br>dd<br>dd<br>dd          | 55555555                        |

| BCS rel                                                                                                        | Branch if Carry Bit Set<br>(Same as BLO)                   | Branch if $(C) = 1$                                                   | - | - | - | -         | -  | - | REL                                                                                                      | 25                                           | rr                                  | 3                               |

| BEQ rel                                                                                                        | Branch if Equal                                            | Branch if $(Z) = 1$                                                   | - | - | - | -         | -  | - | REL                                                                                                      | 27                                           | rr                                  | 3                               |

| BGE <i>rel</i>                                                                                                 | Branch if Greater Than or<br>Equal To<br>(Signed Operands) | Branch if $(N \oplus V) = 0$                                          | - | - | - | -         | _  | - | REL                                                                                                      | 90                                           | rr                                  | 3                               |

| BGND                                                                                                           | Enter Active Background<br>if ENBDM = 1                    | Waits For and Processes BDM<br>Commands Until GO, TRACE1, or<br>TAGGO | _ | _ | _ | _         | _  | - | INH                                                                                                      | 82                                           |                                     | 5+                              |

| BGT rel                                                                                                        | Branch if Greater Than (Signed Operands)                   | Branch if (Z)   (N $\oplus$ V) = 0                                    | - | - | - | -         | -  | - | REL                                                                                                      | 92                                           | rr                                  | 3                               |

| BHCC rel                                                                                                       | Branch if Half Carry Bit<br>Clear                          | Branch if (H) = 0                                                     | - | - | - | -         | _  | - | REL                                                                                                      | 28                                           | rr                                  | 3                               |

| BHCS rel                                                                                                       | Branch if Half Carry Bit Set                               | Branch if (H) = 1                                                     | - | - | - | -         | _  | - | REL                                                                                                      | 29                                           | rr                                  | 3                               |

| BHI <i>rel</i>                                                                                                 | Branch if Higher                                           | Branch if $(C) \mid (Z) = 0$                                          | - | - | - | -         | -  | - | REL                                                                                                      | 22                                           | rr                                  | 3                               |

| BHS rel                                                                                                        | Branch if Higher or Same (Same as BCC)                     | Branch if $(C) = 0$                                                   | - | - | - | -         | _  | - | REL                                                                                                      | 24                                           | rr                                  | 3                               |

| BIH rel                                                                                                        | Branch if IRQ Pin High                                     | Branch if IRQ pin = 1                                                 | - | - | - | -         | -  | - | REL                                                                                                      | 2F                                           | rr                                  | 3                               |

| BIL rel                                                                                                        | Branch if IRQ Pin Low                                      | Branch if IRQ pin = $0$                                               | - | - | - | -         | -  | - | REL                                                                                                      | 2E                                           | rr                                  | 3                               |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT opr16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test                                                   | (A) & (M)<br>(CCR Updated but Operands<br>Not Changed)                | 0 | _ | _ | \$        | \$ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      |                                              | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| BLE rel                                                                                                        | Branch if Less Than<br>or Equal To<br>(Signed Operands)    | Branch if (Z)   (N $\oplus$ V) = 1                                    | _ | - | _ | _         | _  | - | REL                                                                                                      | 93                                           | rr                                  | 3                               |

| BLO rel                                                                                                        | Branch if Lower<br>(Same as BCS)                           | Branch if (C) = $1$                                                   | - | - | - | -         | -  | - | REL                                                                                                      | 25                                           | rr                                  | 3                               |

| BLS rel                                                                                                        | Branch if Lower or Same                                    | Branch if $(C) \mid (Z) = 1$                                          | - | - | - | -         | -  | - | REL                                                                                                      | 23                                           | rr                                  | 3                               |

| BLT <i>rel</i>                                                                                                 | Branch if Less Than<br>(Signed Operands)                   | Branch if (N $\oplus$ V ) = 1                                         | - | - | - | -         | -  | - | REL                                                                                                      | 91                                           | rr                                  | 3                               |

| BMC rel                                                                                                        | Branch if Interrupt Mask<br>Clear                          | Branch if (I) = 0                                                     | - | - | - | -         | _  | - | REL                                                                                                      | 2C                                           | rr                                  | 3                               |

| BMI <i>rel</i>                                                                                                 | Branch if Minus                                            | Branch if (N) = 1                                                     | - | - | _ | -         | -  | - | REL                                                                                                      | 2B                                           | rr                                  | 3                               |

| BMS rel                                                                                                        | Branch if Interrupt Mask<br>Set                            | Branch if (I) = 1                                                     | - | - | - | -         | -  | - | REL                                                                                                      | 2D                                           | rr                                  | 3                               |

| BNE rel                                                                                                        | Branch if Not Equal                                        | Branch if (Z) = 0                                                     | - | - | _ | -         | -  | - | REL                                                                                                      | 26                                           | rr                                  | 3                               |

| BPL <i>rel</i>                                                                                                 | Branch if Plus                                             | Branch if (N) = 0                                                     | - | - | - | -         | -  | - | REL                                                                                                      | 2A                                           | rr                                  | 3                               |

| BRA <i>rel</i>                                                                                                 | Branch Always                                              | No Test                                                               | - | - | _ | _         | _  | _ | REL                                                                                                      | 20                                           | rr                                  | 3                               |

| Table 7-2. HCS08 Instruction Set Summar | 'y | (Sheet 2 of 7) |

|-----------------------------------------|----|----------------|

|-----------------------------------------|----|----------------|

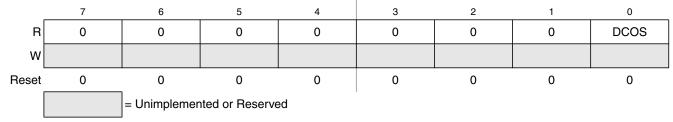

# 8.3.4 ICG Status Register 2 (ICGS2)

#### Figure 8-9. ICG Status Register 2 (ICGS2)

#### Table 8-4. ICGS2 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | <ul> <li>DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n<sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.</li> <li>0 DCO clock is unstable.</li> <li>1 DCO clock is stable.</li> </ul> |

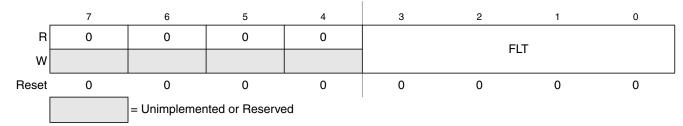

# 8.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

#### Figure 8-10. ICG Upper Filter Register (ICGFLTU)

#### Table 8-5. ICGFLTU Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPMxCnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

# **10.5** Functional Description

All TPM functions are associated with a main 16-bit counter that allows flexible selection of the clock source and prescale divisor. A 16-bit modulo register also is associated with the main 16-bit counter in the TPM. Each TPM channel is optionally associated with an MCU pin and a maskable interrupt function.

The TPM has center-aligned PWM capabilities controlled by the CPWMS control bit in TPMxSC. When CPWMS is set to 1, timer counter TPMxCNT changes to an up-/down-counter and all channels in the associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

# 10.5.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for each of the TPM can be independently selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 10.4.1, "Timer x Status and Control Register (TPMxSC)" and Table 10-2 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

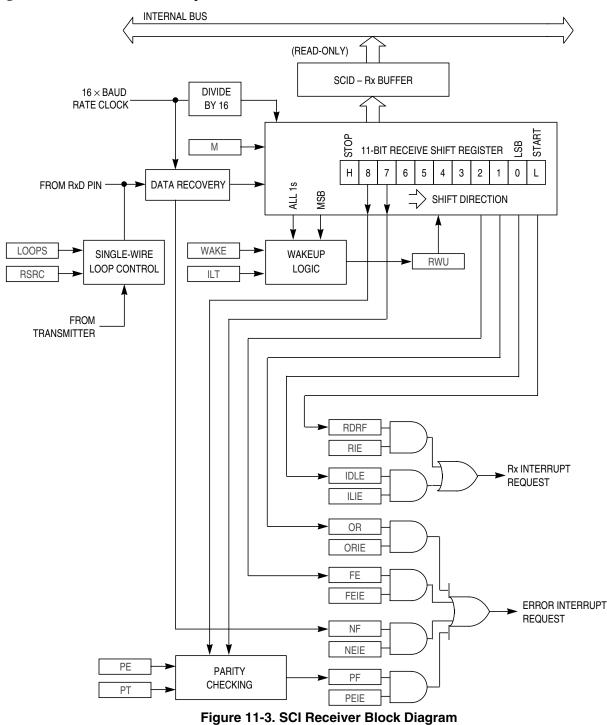

Figure 11-3 shows the receiver portion of the SCI.

# 11.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

# Chapter 12 Serial Peripheral Interface (S08SPIV3)

The MC9S08AW60 Series has one serial peripheral interface (SPI) module. The four pins associated with SPI functionality are shared with port E pins 4–7. See Appendix A, "Electrical Characteristics and Timing Specifications," for SPI electrical parametric information.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPRF  | <ul> <li>SPI Read Buffer Full Flag — SPRF is set at the completion of an SPI transfer to indicate that received data may be read from the SPI data register (SPI1D). SPRF is cleared by reading SPRF while it is set, then reading the SPI data register.</li> <li>0 No data available in the receive data buffer</li> <li>1 Data available in the receive data buffer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5<br>SPTEF | SPI Transmit Buffer Empty Flag — This bit is set when there is room in the transmit data buffer. It is cleared by reading SPI1S with SPTEF set, followed by writing a data value to the transmit buffer at SPI1D. SPI1S must be read with SPTEF = 1 before writing data to SPI1D or the SPI1D write will be ignored. SPTEF generates an SPTEF CPU interrupt request if the SPTIE bit in the SPI1C1 is also set. SPTEF is automatically set when a data byte transfers from the transmit buffer into the transmit shift register. For an idle SPI (no data in the transmit buffer or the shift register and no transfer in progress), data written to SPI1D is transferred to the shifter almost immediately so SPTEF is set within two bus cycles allowing a second 8-bit data value to be queued into the transmit buffer. After completion of the transfer of the value in the shift register, the queued value from the transmit buffer. If no new data is waiting in the transmit buffer, SPTEF simply remains set and no data moves from the buffer to the shifter. |

| 4<br>MODF  | <ul> <li>Master Mode Fault Flag — MODF is set if the SPI is configured as a master and the slave select input goes low, indicating some other SPI device is also configured as a master. The SS pin acts as a mode fault error input only when MSTR = 1, MODFEN = 1, and SSOE = 0; otherwise, MODF will never be set. MODF is cleared by reading MODF while it is 1, then writing to SPI control register 1 (SPI1C1).</li> <li>0 No mode fault error</li> <li>1 Mode fault error detected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 12.3.5 SPI Data Register (SPI1D)

|        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |  |

|--------|-------|---|---|---|---|---|---|-------|--|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |  |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |  |

Figure 12-9. SPI Data Register (SPI1D)

Reads of this register return the data read from the receive data buffer. Writes to this register write data to the transmit data buffer. When the SPI is configured as a master, writing data to the transmit data buffer initiates an SPI transfer.

Data should not be written to the transmit data buffer unless the SPI transmit buffer empty flag (SPTEF) is set, indicating there is room in the transmit buffer to queue a new transmit byte.

Data may be read from SPI1D any time after SPRF is set and before another transfer is finished. Failure to read the data out of the receive data buffer before a new transfer ends causes a receive overrun condition and the data from the new transfer is lost.

MC9S08AW60 Data Sheet, Rev 2

# 15.4.3.5 Debug FIFO High Register (DBGFH)

This register provides read-only access to the high-order eight bits of the FIFO. Writes to this register have no meaning or effect. In the event-only trigger modes, the FIFO only stores data into the low-order byte of each FIFO word, so this register is not used and will read 0x00.

Reading DBGFH does not cause the FIFO to shift to the next word. When reading 16-bit words out of the FIFO, read DBGFH before reading DBGFL because reading DBGFL causes the FIFO to advance to the next word of information.

# 15.4.3.6 Debug FIFO Low Register (DBGFL)

This register provides read-only access to the low-order eight bits of the FIFO. Writes to this register have no meaning or effect.

Reading DBGFL causes the FIFO to shift to the next available word of information. When the debug module is operating in event-only modes, only 8-bit data is stored into the FIFO (high-order half of each FIFO word is unused). When reading 8-bit words out of the FIFO, simply read DBGFL repeatedly to get successive bytes of data from the FIFO. It isn't necessary to read DBGFH in this case.

Do not attempt to read data from the FIFO while it is still armed (after arming but before the FIFO is filled or ARMF is cleared) because the FIFO is prevented from advancing during reads of DBGFL. This can interfere with normal sequencing of reads from the FIFO.

Reading DBGFL while the debugger is not armed causes the address of the most-recently fetched opcode to be stored to the last location in the FIFO. By reading DBGFH then DBGFL periodically, external host software can develop a profile of program execution. After eight reads from the FIFO, the ninth read will return the information that was stored as a result of the first read. To use the profiling feature, read the FIFO eight times without using the data to prime the sequence and then begin using the data to get a delayed picture of what addresses were being executed. The information stored into the FIFO on reads of DBGFL (while the FIFO is not armed) is the address of the most-recently fetched opcode.

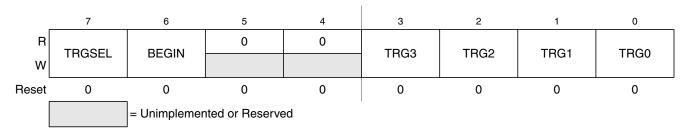

## 15.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

#### Figure 15-8. Debug Trigger Register (DBGT)

#### Table 15-5. DBGT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TRGSEL     | <ul> <li>Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.</li> <li>0 Trigger on access to compare address (force)</li> <li>1 Trigger if opcode at compare address is executed (tag)</li> </ul> |

| 6<br>BEGIN      | <ul> <li>Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.</li> <li>Data stored in FIFO until trigger (end trace)</li> <li>Trigger initiates data storage (begin trace)</li> </ul>                                                                                                                 |

| 3:0<br>TRG[3:0] | Select Trigger Mode — Selects one of nine triggering modes, as described below.0000 A-only0001 A OR B0010 A Then B0011 Event-only B (store data)0100 A then event-only B (store data)0101 A AND B data (full mode)0110 A AND NOT B data (full mode)0111 Inside range: $A \leq address \leq B$ 1000 Outside range: address < A or address > B1001 - 1111 (No trigger)                                                                                                                                                 |

# A.13 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

# A.13.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter                             | Symbol              | Conditions                                                         | fosc/f <sub>BUS</sub>       | Frequency      | Level <sup>1</sup><br>(Max) | Unit |

|---------------------------------------|---------------------|--------------------------------------------------------------------|-----------------------------|----------------|-----------------------------|------|

| Radiated emissions,<br>electric field |                     | $V_{DD} = 5.5V$<br>$T_A = +25^{\circ}C$<br>package type<br>64  QFP | 4 MHz crystal<br>20 MHz Bus | 0.15 – 50 MHz  | 16                          | dBµV |

|                                       |                     |                                                                    |                             | 50 – 150 MHz   | 3                           |      |

|                                       |                     |                                                                    |                             | 150 – 500 MHz  | 1                           |      |

|                                       |                     |                                                                    |                             | 500 – 1000 MHz | 0                           |      |

|                                       |                     |                                                                    |                             | IEC Level      | L                           |      |

|                                       |                     |                                                                    |                             | SAE Level      | 2                           |      |

|                                       | V <sub>RE_TEM</sub> |                                                                    | 32 kHz crystal<br>8 MHz Bus | 0.15 – 50 MHz  | -1                          | dBμV |

|                                       |                     |                                                                    |                             | 50 – 150 MHz   | -6                          |      |

|                                       |                     |                                                                    |                             | 150 – 500 MHz  | -10                         |      |

|                                       |                     |                                                                    |                             | 500 – 1000 MHz | -10                         |      |

|                                       |                     |                                                                    |                             | IEC Level      | Ν                           | _    |

|                                       |                     |                                                                    |                             | SAE Level      | 1                           | —    |

#### Table A-17. Radiated Emissions

<sup>1</sup> Data based on qualification test results.

# A.13.2 Conducted Transient Susceptibility

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method.

#### How to Reach Us:

#### USA/Europe/Locations not listed:

Freescale Semiconductor Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor H.K. Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong 852-26668334

#### Learn More: For more information about Freescale Semiconductor products, please visit http://www.freescale.com

MC9S08AW60, Rev 2 12/2006

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.