# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-QFP                                                                 |

| Supplier Device Package    | 64-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08aw48cfue |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                     |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 1/2006           | Initial external release.                                                                                                                                                                                                                                                                                                  |

| 2                  | 12/2006          | Includes KBI block changes; new V <sub>OL</sub> / I <sub>OL</sub> figures; RI <sub>DD</sub> spec changes; SC part numbers with ICG trim modifications; addition of Temp Sensor to ADC. Resolved the stop IDD issues, added RTI figure, bandgap information, and incorporated electricals edits and any ProjectSync issues. |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006. All rights reserved.

### **Section Number**

Title

#### Page

|     | 7.2.1     | Accumulator (A)                 | 110 |

|-----|-----------|---------------------------------|-----|

|     | 7.2.2     | Index Register (H:X)            |     |

|     | 7.2.3     | Stack Pointer (SP)              |     |

|     | 7.2.4     | Program Counter (PC)            |     |

|     | 7.2.5     | Condition Code Register (CCR)   |     |

| 7.3 | Addressi  | ng Modes                        | 113 |

|     | 7.3.1     | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2     | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3     | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4     | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5     | Extended Addressing Mode (EXT)  | 114 |

|     | 7.3.6     | Indexed Addressing Mode         | 114 |

| 7.4 | Special C | Operations                      | 115 |

|     | 7.4.1     | Reset Sequence                  | 115 |

|     | 7.4.2     | Interrupt Sequence              |     |

|     | 7.4.3     | Wait Mode Operation             |     |

|     | 7.4.4     | Stop Mode Operation             |     |

|     | 7.4.5     | BGND Instruction                | 117 |

| 7.5 | HCS08 I   | nstruction Set Summary          | 118 |

# Chapter 8 Internal Clock Generator (S08ICGV4)

| Introduc | tion                                                                                                                                                                    | 131                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 8.1.1    | Features                                                                                                                                                                | 131                                         |

| 8.1.2    | Modes of Operation                                                                                                                                                      | 132                                         |

| 8.1.3    | Block Diagram                                                                                                                                                           | 133                                         |

| External | Signal Description                                                                                                                                                      | 133                                         |

| 8.2.1    | EXTAL — External Reference Clock / Oscillator Input                                                                                                                     | 133                                         |

| 8.2.2    | XTAL — Oscillator Output                                                                                                                                                | 133                                         |

| 8.2.3    |                                                                                                                                                                         |                                             |

| 8.2.4    | External Crystal/Resonator Connections                                                                                                                                  | 134                                         |

| Register | Definition                                                                                                                                                              | 135                                         |

| 8.3.1    | ICG Control Register 1 (ICGC1)                                                                                                                                          | 135                                         |

| 8.3.2    | ICG Control Register 2 (ICGC2)                                                                                                                                          | 137                                         |

| 8.3.3    | ICG Status Register 1 (ICGS1)                                                                                                                                           | 138                                         |

| 8.3.4    | ICG Status Register 2 (ICGS2)                                                                                                                                           | 139                                         |

| 8.3.5    | ICG Filter Registers (ICGFLTU, ICGFLTL)                                                                                                                                 | 139                                         |

| 8.3.6    | ICG Trim Register (ICGTRM)                                                                                                                                              | 140                                         |

| Function | al Description                                                                                                                                                          | 140                                         |

| 8.4.1    | Off Mode (Off)                                                                                                                                                          | 141                                         |

| 8.4.2    | Self-Clocked Mode (SCM)                                                                                                                                                 | 141                                         |

| 8.4.3    | FLL Engaged, Internal Clock (FEI) Mode                                                                                                                                  | 142                                         |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>External<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Register<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Function<br>8.4.1<br>8.4.2 | <ul> <li>8.1.2 Modes of Operation</li></ul> |

**Chapter 6 Parallel Input/Output**

# 6.6 Pin Behavior in Stop Modes

Depending on the stop mode, I/O functions differently as the result of executing a STOP instruction. An explanation of I/O behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, peripherals may require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user's application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.7 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports and pin control functions. These parallel I/O registers are located in page zero of the memory map and the pin control registers are located in the high page register section of memory.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and pin control registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

# 6.7.1 Port A I/O Registers (PTAD and PTADD)

Port A parallel I/O function is controlled by the registers listed below.

| _     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R     | PTAD7 | PTAD6 | PTAD5 | PTAD4 | PTAD3 | PTAD2 | PTAD1 | PTAD0 |

| w     |       |       |       |       |       |       |       |       |

| Reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 6-9. Port A Data Register (PTAD)

| Table 6-2. PTAD Register Field Desci | riptions |

|--------------------------------------|----------|

|--------------------------------------|----------|

| F | Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | AD[7:0] | Port A Data Register Bits — For port A pins that are inputs, reads return the logic level on the pin. For port A pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port A pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTAD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

#### MC9S08AW60 Data Sheet, Rev 2

#### Chapter 6 Parallel Input/Output

| _     | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     |   | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| w     |   | FIGD30 | FIGD00 | FTGD34 | FIGD33 | FIGD32 | FIGDST | FIGDSU |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-43. Output Drive Strength Selection for Port G (PTGDS)

#### Table 6-36. PTGDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGDS[6:0] | <ul> <li>Output Drive Strength Selection for Port G Bits — Each of these control bits selects between low and high output drive for the associated PTG pin.</li> <li>0 Low output drive enabled for port G bit n.</li> <li>1 High output drive enabled for port G bit n.</li> </ul> |

### 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

### 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

### 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

| Source                                                                                                          |                                                                 | <b>_</b>                                                                                                                                                                                                                         | Effec<br>on CC |   |   |    |    |    | ess                                                 | ode                                | and                                 | rcles <sup>1</sup>              |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|---|----|----|----|-----------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                            | Operation                                                       | Description                                                                                                                                                                                                                      | v              | н | I | N  | z  | с  | Address<br>Mode                                     | Opcode                             | Operand                             | Bus Cycles <sup>1</sup>         |

| CPX #opr8i<br>CPX opr8a<br>CPX opr16a<br>CPX oprx16,X<br>CPX oprx8,X<br>CPX ,X<br>CPX oprx16,SP<br>CPX oprx8,SP | Compare X (Index<br>Register Low) with<br>Memory                | (X) – (M)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                           | \$             | _ | _ | \$ | \$ | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| DAA                                                                                                             | Decimal Adjust<br>Accumulator After ADD or<br>ADC of BCD Values | (A) <sub>10</sub>                                                                                                                                                                                                                | υ              | - | - | ¢  | ¢  | ¢  | INH                                                 | 72                                 |                                     | 1                               |

| DBNZ opr8a,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ oprx8,X,rel<br>DBNZ ,X,rel<br>DBNZ oprx8,SP,rel                | Decrement and Branch if<br>Not Zero                             | Decrement A, X, or M<br>Branch if (result) ≠ 0<br>DBNZX Affects X Not H                                                                                                                                                          | _              | _ | _ | _  | _  | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B | rr<br>ff rr<br>rr                   | 7<br>4<br>7<br>6<br>8           |

| DEC opr8a<br>DECA<br>DECX<br>DEC oprx8,X<br>DEC ,X<br>DEC oprx8,SP                                              | Decrement                                                       | $\begin{array}{l} M \leftarrow (M) - 0x01 \\ A \leftarrow (A) - 0x01 \\ X \leftarrow (X) - 0x01 \\ M \leftarrow (M) - 0x01 \end{array}$         | ¢              | _ | _ | \$ | \$ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A | ff                                  | 511546                          |

| DIV                                                                                                             | Divide                                                          | $A \leftarrow (H:A) \div (X)$<br>H $\leftarrow$ Remainder                                                                                                                                                                        | -              | - | - | -  | \$ | \$ | INH                                                 | 52                                 |                                     | 6                               |

| EOR #opr8i<br>EOR opr8a<br>EOR opr16a<br>EOR oprx16,X<br>EOR oprx8,X<br>EOR ,X<br>EOR oprx16,SP<br>EOR oprx8,SP | Exclusive OR<br>Memory with<br>Accumulator                      | $A \gets (A \oplus M)$                                                                                                                                                                                                           | 0              | _ | _ | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| INC opr8a<br>INCA<br>INCX<br>INC oprx8,X<br>INC ,X<br>INC oprx8,SP                                              | Increment                                                       | $\begin{array}{l} M \leftarrow (M) + 0x01 \\ A \leftarrow (A) + 0x01 \\ X \leftarrow (X) + 0x01 \\ M \leftarrow (M) + 0x01 \end{array}$         | \$             | _ | _ | \$ | \$ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C | ff                                  | 5<br>1<br>5<br>4<br>6           |

| JMP opr8a<br>JMP opr16a<br>JMP oprx16,X<br>JMP oprx8,X<br>JMP ,X                                                | Jump                                                            | $PC \gets Jump \; Address$                                                                                                                                                                                                       | _              | _ | _ | _  | _  | _  | DIR<br>EXT<br>IX2<br>IX1<br>IX                      |                                    | hh II<br>ee ff                      | 3<br>4<br>3<br>3                |

| JSR opr8a<br>JSR opr16a<br>JSR oprx16,X<br>JSR oprx8,X<br>JSR ,X                                                | Jump to Subroutine                                              | $\begin{array}{l} PC \leftarrow (PC) + n \ (n = 1, 2, \text{ or } 3) \\ Push \ (PCL); \ SP \leftarrow (SP) - 0 \\ x0001 \\ Push \ (PCH); \ SP \leftarrow (SP) - 0 \\ x0001 \\ PC \leftarrow Unconditional \ Address \end{array}$ | _              | _ | _ | _  | _  | _  | DIR<br>EXT<br>IX2<br>IX1<br>IX                      |                                    | hh II<br>ee ff                      | 56655                           |

| LDA #opr8i<br>LDA opr8a<br>LDA opr16a<br>LDA oprx16,X<br>LDA oprx8,X<br>LDA ,X<br>LDA oprx16,SP<br>LDA oprx8,SP | Load Accumulator from<br>Memory                                 | A ← (M)                                                                                                                                                                                                                          | 0              | _ | _ | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 |                                    | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| LDHX #opr16i<br>LDHX opr8a<br>LDHX opr16a<br>LDHX ,X<br>LDHX oprx16,X<br>LDHX oprx8,X<br>LDHX oprx8,SP          | Load Index Register (H:X)<br>from Memory                        | H:X ← (M:M + 0x0001)                                                                                                                                                                                                             | 0              | _ | _ | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX<br>IX2<br>IX1<br>SP1        |                                    | dd<br>hh ll<br>ee ff<br>ff          | 3455655                         |

| Table 7-2. HCS08 Instruction Set Summary | (Sheet 4 of 7) |

|------------------------------------------|----------------|

|                                          | (0             |

| Table 7-3. Opcode map (Sheet 1 of 2)      |                        |                      |                       |                     |                       |                         |                       |                        |              |                      |                      |                      |                      |                      |                     |

|-------------------------------------------|------------------------|----------------------|-----------------------|---------------------|-----------------------|-------------------------|-----------------------|------------------------|--------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| Bit-Manipulation Branch Read-Modify-Write |                        |                      |                       |                     |                       | Control Register/Memory |                       |                        |              |                      |                      |                      |                      |                      |                     |

| 00 5                                      | 10 5                   | 20 3                 | 30 5                  | 40 1                | 50 1                  | 60 5                    | 70 4                  | 80 9                   | 90 3         | A0 2                 | B0 3                 | C0 4                 | D0 4                 | E0 3                 | F0 3                |

| BRSET0                                    | BSET0                  | BRA                  | NEG                   | NEGA                | NEGX                  | NEG                     | NEG                   | RTI                    | BGE          | SUB                  | SUB                  | SUB                  | SUB                  | SUB                  | SUB                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 01 5                                      | 11 5                   | 21 3                 | 31 5                  | 41 4                | 51 4                  | 61 5                    | 71 5                  | 81 6                   | 91 3         | A1 2                 | B1 3                 | C1 4                 | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                                    | BCLR0                  | BRN                  | CBEQ                  | CBEQA               | CBEQX                 | CBEQ                    | CBEQ                  | RTS                    | BLT          | CMP                  | CMP                  | CMP                  | CMP                  | CMP                  | CMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 3 DIR                 | 3 IMM               | 3 IMM                 | 3 IX1+                  | 2 IX+                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                                      | 12 5                   | 22 3                 | 32 5                  | 42 5                | 52 6                  | 62 1                    | 72 1                  | 82 5+                  | 92 3         | A2 2                 | B2 3                 | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                                    | BSET1                  | BHI                  | LDHX                  | MUL                 | DIV                   | NSA                     | DAA                   | BGND                   | BGT          | SBC                  | SBC                  | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 3 EXT                 | 1 INH               | 1 INH                 | 1 INH                   | 1 INH                 | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                                      | 13 5                   | 23 3                 | 33 5                  | 43 1                | 53 1                  | 63 5                    | 73 4                  | 83 11                  | 93 3         | A3 2                 | B3 3                 | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                                    | BCLR1                  | BLS                  | COM                   | COMA                | COMX                  | COM                     | COM                   | SWI                    | BLE          | CPX                  | CPX                  | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 2 REL        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5                                      | 14 5                   | 24 3                 | 34 5                  | 44 1                | 54 1                  | 64 5                    | 74 4                  | 84 1                   | 94 2         | A4 2                 | B4 3                 | C4 4                 | D4 4                 | E4 3                 | F4 3                |

| BRSET2                                    | BSET2                  | BCC                  | LSR                   | LSRA                | LSRX                  | LSR                     | LSR                   | TAP                    | TXS          | AND                  | AND                  | AND                  | AND                  | AND                  | AND                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 05 5                                      | 15 5                   | 25 3                 | 35 4                  | 45 3                | 55 4                  | 65 3                    | 75 5                  | 85 1                   | 95 2         | A5 2                 | B5 3                 | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                                    | BCLR2                  | BCS                  | STHX                  | LDHX                | LDHX                  | CPHX                    | CPHX                  | TPA                    | TSX          | BIT                  | BIT                  | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 3 IMM               | 2 DIR                 | 3 IMM                   | 2 DIR                 | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                                      | 16 5                   | 26 3                 | 36 5                  | 46 1                | 56 1                  | 66 5                    | 76 4                  | 86 3                   | 96 5         | A6 2                 | B6 3                 | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                                    | BSET3                  | BNE                  | ROR                   | RORA                | RORX                  | ROR                     | ROR                   | PULA                   | STHX         | LDA                  | LDA                  | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 3 EXT        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                                      | 17 5                   | 27 3                 | 37 5                  | 47 1                | 57 1                  | 67 5                    | 77 4                  | 87 2                   | 97 1         | AIS                  | B7 3                 | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                                    | BCLR3                  | BEQ                  | ASR                   | ASRA                | ASRX                  | ASR                     | ASR                   | PSHA                   | TAX          |                      | STA                  | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                                      | 18 5                   | 28 3                 | 38 5                  | 48 1                | 58 1                  | 68 5                    | 78 4                  | 88 3                   | 98 1         | A8 2                 | B8 3                 | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                                    | BSET4                  | BHCC                 | LSL                   | LSLA                | LSLX                  | LSL                     | LSL                   | PULX                   | CLC          | EOR                  | EOR                  | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5                                      | 19 5                   | 29 3                 | 39 5                  | 49 1                | 59 1                  | 69 5                    | 79 4                  | 89 2                   | 99 1         | A9 2                 | B9 3                 | C9 4                 | D9 4                 | E9 3                 | F9 3                |

| BRCLR4                                    | BCLR4                  | BHCS                 | ROL                   | ROLA                | ROLX                  | ROL                     | ROL                   | PSHX                   | SEC          | ADC                  | ADC                  | ADC                  | ADC                  | ADC                  | ADC                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0A 5                                      | 1A 5                   | 2A 3                 | 3A 5                  | 4A 1                | 5A 1                  | 6A 5                    | 7A 4                  | 8A 3                   | 9A 1         | AA 2                 | BA 3                 | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                                    | BSET5                  | BPL                  | DEC                   | DECA                | DECX                  | DEC                     | DEC                   | PULH                   | CLI          | ORA                  | ORA                  | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                                      | 1B 5                   | 2B 3                 | 3B 7                  | 4B 4                | 5B 4                  | 6B 7                    | 7B 6                  | 8B 2                   | 9B 1         | ADD                  | BB 3                 | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                                    | BCLR5                  | BMI                  | DBNZ                  | DBNZA               | DBNZX                 | DBNZ                    | DBNZ                  | PSHH                   | SEI          |                      | ADD                  | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 3 DIR                 | 2 INH               | 2 INH                 | 3 IX1                   | 2 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                                      | 1C 5                   | 2C 3                 | 3C 5                  | 4C 1                | 5C 1                  | 6C 5                    | 7C 4                  | 8C 1                   | 9C 1         |                      | BC 3                 | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                                    | BSET6                  | BMC                  | INC                   | INCA                | INCX                  | INC                     | INC                   | CLRH                   | RSP          |                      | JMP                  | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        |                      | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                                      | 1D 5                   | 2D 3                 | 3D 4                  | 4D 1                | 5D 1                  | 6D 4                    | 7D 3                  |                        | 9D 1         | AD 5                 | BD 5                 | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                                    | BCLR6                  | BMS                  | TST                   | TSTA                | TSTX                  | TST                     | TST                   |                        | NOP          | BSR                  | JSR                  | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  |                        | 1 INH        | 2 REL                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR                   | 1E 5<br>BSET7<br>2 DIR | 2E 3<br>BIL<br>2 REL | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD    | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2 | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                                      | 1F 5                   | 2F 3                 | 3F 5                  | 4F 1                | 5F 1                  | 6F 5                    | 7F 4                  | 8F 2+                  | 9F 1         | AF 2                 | BF 3                 | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                                    | BCLR7                  | BIH                  | CLR                   | CLRA                | CLRX                  | CLR                     | CLR                   | WAIT                   | TXA          | AIX                  | STX                  | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                                     | 2 DIR                  | 2 REL                | 2 DIR                 | 1 INH               | 1 INH                 | 2 IX1                   | 1 IX                  | 1 INH                  | 1 INH        | 2 IMM                | 2 DIR                | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

#### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

REL IX IX1 IX2 IMD DIX+

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

Opcode in Hexadecimal SUB 1 IX Addressing Mode

# Chapter 9 Keyboard Interrupt (S08KBIV1)

# 9.1 Introduction

The MC9S08AW60 Series has one KBI module with eight keyboard interrupt inputs that are shared with port D and port G pins. See Chapter 2, "Pins and Connections," for more information about the logic and hardware aspects of these pins.

# 9.2 Keyboard Pin Sharing

The KBI input KBIP7 shares a common pin with PTD7 and AD15. When KBIP7 is enabled the pin is forced to its input state regardless of the value of the associated port D data direction bit. The port D pullup enable is still used to control the pullup resistor and the pin state can be sensed through a read of the port D data register (this requires that bit 7 of the port D DDR is 0). In the case that the pin is enabled as an ADC input, both the PTD7 and KBIP7 functions are disabled, including the pullup resistor.

The KBI input KBIP6 shares a common pin with PTD3 and AD11, and KBI input KBIP5 shares a common pin with PTD2 and AD10. The sharing of each of these inputs with port and ADC functions operates in the same way as described above for KBIP7.

The KBI inputs KBIP4 – KBIP0 are shared on common pins with PTG4 – PTG0. These pins all operate in the same way as described above for KBIP7 except that none are shared with an ADC input.

KBIP3 – KBIP0 are always falling-edge/low-level sensitive. KBIP7 – KBIP4 can be configured for rising-edge/high-level or for falling-edge/low-level sensitivity. When any of the inputs KBIP7 – KBIP0 are enabled and configured to detect rising edges/high levels, and the pin pullup is enabled through the corresponding port pullup enable bit for that pin, a pulldown resistor rather than a pullup resistor is enabled on the pin.

| PTxPEn<br>(Pull Enable) | PTxDDn<br>(Data Direction) | KBIPEn<br>(KBI Pin Enable) | KBEDGn<br>(KBI Edge Select) | Pullup   | Pulldown |

|-------------------------|----------------------------|----------------------------|-----------------------------|----------|----------|

| 0                       | 0                          | 0                          | x <sup>1</sup>              | disabled | disabled |

| 1                       | 0                          | 0                          | х                           | enabled  | disabled |

| x                       | 1                          | 0                          | х                           | disabled | disabled |

| 1                       | x                          | 1                          | 0                           | enabled  | disabled |

| 1                       | x                          | 1                          | 1                           | disabled | enabled  |

| 0                       | x                          | 1                          | х                           | disabled | disabled |

<sup>1</sup> x = Don't care

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input      |

|-------------|------------------------------------------|

| 0:0         | No clock selected (TPMx disabled)        |

| 0:1         | Bus rate clock (BUSCLK)                  |

| 1:0         | Fixed system clock (XCLK)                |

| 1:1         | External source (TPMxCLK) <sup>1,2</sup> |

#### Table 10-2. TPM Clock Source Selection

<sup>1</sup> The maximum frequency that is allowed as an external clock is one-fourth of the bus frequency.

<sup>2</sup> If the external clock input is shared with channel n and is selected as the TPM clock source, the corresponding ELSnB:ELSnA control bits should be set to 0:0 so channel n does not try to use the same pin for a conflicting function.

| PS2:PS1:PS0 | TPM Clock Source Divided-By |

|-------------|-----------------------------|

| 0:0:0       | 1                           |

| 0:0:1       | 2                           |

| 0:1:0       | 4                           |

| 0:1:1       | 8                           |

| 1:0:0       | 16                          |

| 1:0:1       | 32                          |

| 1:1:0       | 64                          |

| 1:1:1       | 128                         |

Table 10-3. Prescale Divisor Selection

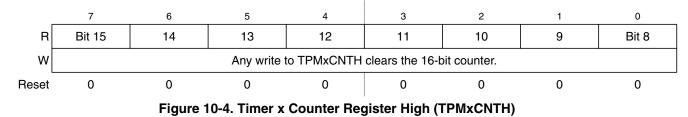

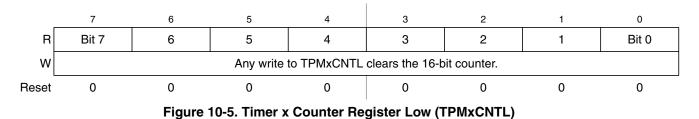

#### **10.4.2** Timer x Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This allows coherent 16-bit reads in either order. The coherency mechanism is automatically restarted by an MCU reset, a write of any value to TPMxCNTH or TPMxCNTL, or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers.

Chapter 10 Timer/Pulse-Width Modulator (S08TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

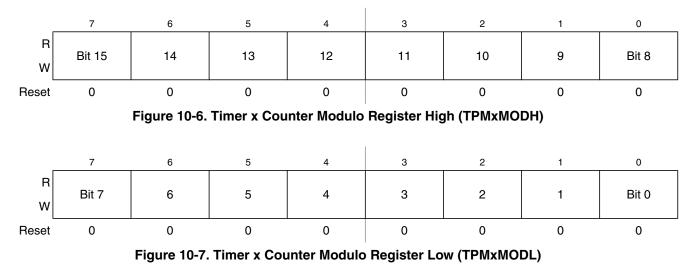

### 10.4.3 Timer x Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

Chapter 11 Serial Communications Interface (S08SCIV2)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

### 11.2.1 SCI Baud Rate Registers (SCIxBDH, SCIxBHL)

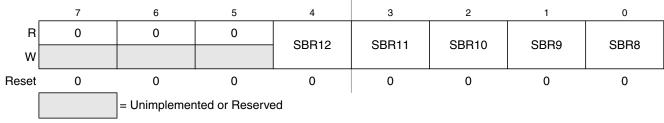

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCIxBDH to buffer the high half of the new value and then write to SCIxBDL. The working value in SCIxBDH does not change until SCIxBDL is written.

SCIxBDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCIxC2 are written to 1).

#### Figure 11-4. SCI Baud Rate Register (SCIxBDH)

| Field            | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — These 13 bits are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/( $16 \times BR$ ). See also BR bits in Table 11-2. |

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| R<br>W | SBR7 | SBR6 | SBR5 | SBR4 | SBR3 | SBR2 | SBR1 | SBR0 |

| Reset  | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

Figure 11-5. SCI Baud Rate Register (SCIxBDL)

| Table 11-2. | SCIxBDL | Register | Field | Descriptions |

|-------------|---------|----------|-------|--------------|

|-------------|---------|----------|-------|--------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — These 13 bits are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 11-1. |

systems with modems to determine when it is safe to turn off the modem. If the transmit complete interrupt enable (TCIE) bit is set, a hardware interrupt will be requested whenever TC = 1. Instead of hardware interrupts, software polling may be used to monitor the TDRE and TC status flags if the corresponding TIE or TCIE local interrupt masks are 0s.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared by reading SCIxS1 while RDRF = 1 and then reading SCIxD. If the SCI is configured to operate in 9-bit mode, an additional read to the SCIxC3 register is required to clear RDRF

When polling is used, this sequence is naturally satisfied in the normal course of the user program. If hardware interrupts are used, SCIxS1 must be read in the interrupt service routine (ISR). Normally, this is done in the ISR anyway to check for receive errors, so the sequence is automatically satisfied.

The IDLE status flag includes logic that prevents it from getting set repeatedly when the RxD line remains idle for an extended period of time. IDLE is cleared by reading SCIxS1 while IDLE = 1 and then reading SCIxD. After IDLE has been cleared, it cannot become set again until the receiver has received at least one new character and has set RDRF.

If the associated error was detected in the received character that caused RDRF to be set, the error flags — noise flag (NF), framing error (FE), and parity error flag (PF) — get set at the same time as RDRF. These flags are not set in overrun cases.

If RDRF was already set when a new character is ready to be transferred from the receive shifter to the receive data buffer, the overrun (OR) flag gets set instead and the data and any associated NF, FE, or PF condition is lost.

#### 11.3.5 Additional SCI Functions

The following sections describe additional SCI functions.

#### 11.3.5.1 8- and 9-Bit Data Modes

The SCI system (transmitter and receiver) can be configured to operate in 9-bit data mode by setting the M control bit in SCIxC1. In 9-bit mode, there is a ninth data bit to the left of the MSB of the SCI data register. For the transmit data buffer, this bit is stored in T8 in SCIxC3. For the receiver, the ninth bit is held in R8 in SCIxC3.

When transmitting 9-bit data, write to the T8 bit before writing to SCIxD for coherent writes to the transmit data buffer. If the bit value to be transmitted as the ninth bit of a new character is the same as for the previous character, it is not necessary to write to T8 again. When data is transferred from the transmit data buffer to the transmit shifter, the value in T8 is copied at the same time data is transferred from SCIxD to the shifter.

When receiving 9-bit data, clear the RDRF bit by reading both R8 and SCIxD. R8 and SCIxD can be read in either order.

Chapter 12 Serial Peripheral Interface (S08SPIV3)

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 12-5. SPI Baud Rate Prescaler Divisor

#### Table 12-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |

|----------------|--------------|

| 0:0:0          | 2            |

| 0:0:1          | 4            |

| 0:1:0          | 8            |

| 0:1:1          | 16           |

| 1:0:0          | 32           |

| 1:0:1          | 64           |

| 1:1:0          | 128          |

| 1:1:1          | 256          |

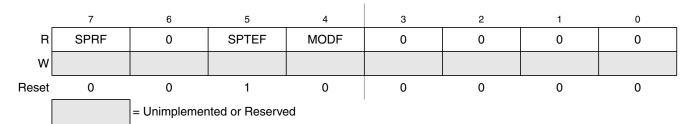

### 12.3.4 SPI Status Register (SPI1S)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 12-8. SPI Status Register (SPI1S)

Chapter 13 Inter-Integrated Circuit (S08IICV1)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all IIC registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

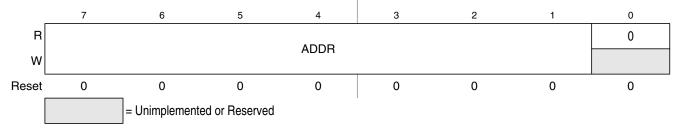

# 13.3.1 IIC Address Register (IIC1A)

Figure 13-3. IIC Address Register (IIC1A)

#### Table 13-1. IIC1A Register Field Descriptions

| Field            | Description                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>ADDR[7:1] | <b>IIC Address Register</b> — The ADDR contains the specific slave address to be used by the IIC module. This is the address the module will respond to when addressed as a slave. |

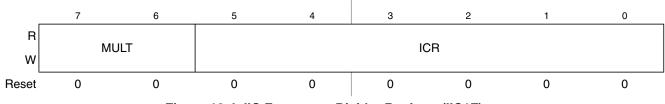

### 13.3.2 IIC Frequency Divider Register (IIC1F)

Figure 13-4. IIC Frequency Divider Register (IIC1F)

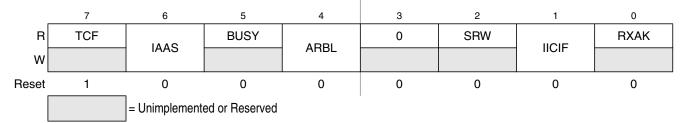

# 13.3.4 IIC Status Register (IIC1S)

Figure 13-6. IIC Status Register (IIC1S)

| Table 13-5. IIC1S R | Register Field Descriptions |

|---------------------|-----------------------------|

|---------------------|-----------------------------|

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>TCF   | Transfer Complete Flag — This bit is set on the completion of a byte transfer. Note that this bit is only val during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared reading the IIC1D register in receive mode or writing to the IIC1D in transmit mode.         0       Transfer in progress.         1       Transfer complete.                                            |  |  |  |  |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave — The IAAS bit is set when the calling address matches the programmed slave address.</li> <li>Writing the IIC1C register clears this bit.</li> <li>0 Not addressed.</li> <li>1 Addressed as a slave.</li> </ul>                                                                                                                                                                                      |  |  |  |  |

| 5<br>BUSY  | <ul> <li>Bus Busy — The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a START signal is detected and cleared when a STOP signal is detected.</li> <li>0 Bus is idle.</li> <li>1 Bus is busy.</li> </ul>                                                                                                                                                                    |  |  |  |  |

| 4<br>ARBL  | <ul> <li>Arbitration Lost — This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software, by writing a one to it.</li> <li>0 Standard bus operation.</li> <li>1 Loss of arbitration.</li> </ul>                                                                                                                                                                                    |  |  |  |  |

| 2<br>SRW   | <ul> <li>Slave Read/Write — When addressed as a slave the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>0 Slave receive, master writing to slave.</li> <li>1 Slave transmit, master reading from slave.</li> </ul>                                                                                                                                                        |  |  |  |  |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag — The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a one to it in the interrupt routine. One of the following events can set the IICIF bit: <ul> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> </ul> </li> <li>0 No interrupt pending.</li> <li>1 Interrupt pending.</li> </ul> |  |  |  |  |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge — When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received.</li> <li>1 No acknowledge received.</li> </ul>                                                                                           |  |  |  |  |

#### 14.2.4 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 10 bits resolution.

- Up to 28 analog inputs.

- Output formatted in 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop3 modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Selectable asynchronous hardware conversion trigger.

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

#### 14.2.5 Block Diagram

Figure 14-2 provides a block diagram of the ADC module

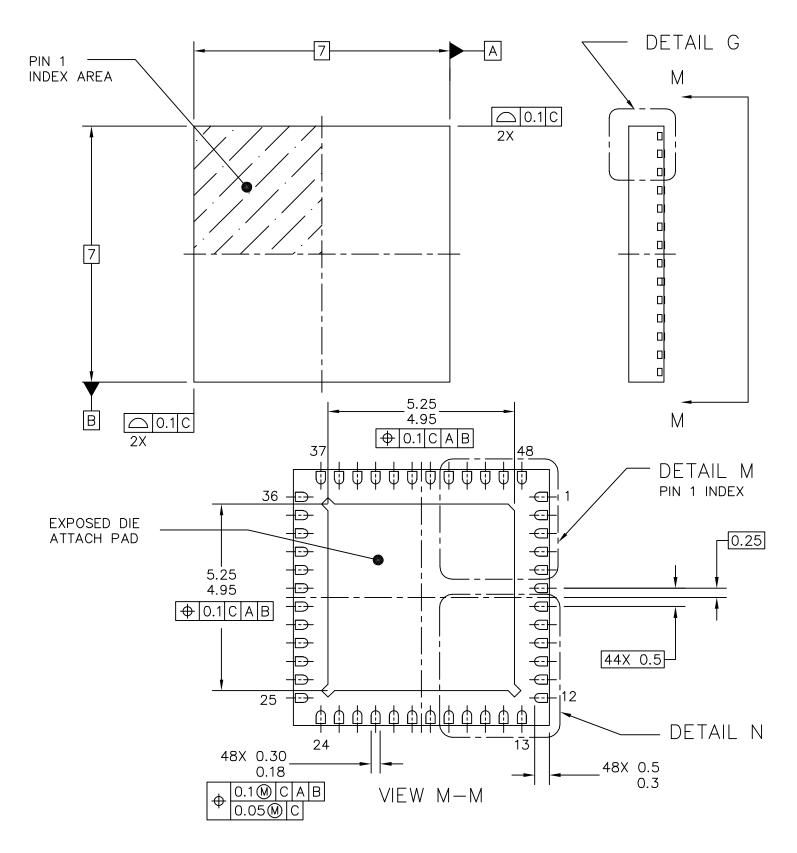

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA   | L OUTLINE      | PRINT VERSION NO  | T TO SCALE |

|---------------------------------------------------------|-------------|----------------|-------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO | ): 98ARH99048A | REV: F            |            |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER | : 1314–05      | 05 DEC 2005       |            |

| 48 TERMINAL, 0.5 PITCH (7 X 7 X 1)                      |             | STANDARD: JE   | DEC-MO-220 VKKD-2 | 2          |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4. COPLANARITY APPLIES TO LEADS, CORNER LEADS, AND DIE ATTACH PAD.

5. MIN METAL GAP SHOULD BE 0.2MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |              | L OUTLINE         | PRINT VERSION NO | T TO SCALE |

|---------------------------------------------------------|--------------|-------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO  | ): 98ARH99048A    | REV: F           |            |

| FLAT NON-LEADED PACK                                    | CASE NUMBER  |                   | 05 DEC 2005      |            |

| 48 TERMINAL, 0.5 PITCH (                                | STANDARD: JE | DEC-MO-220 VKKD-2 | 2                |            |

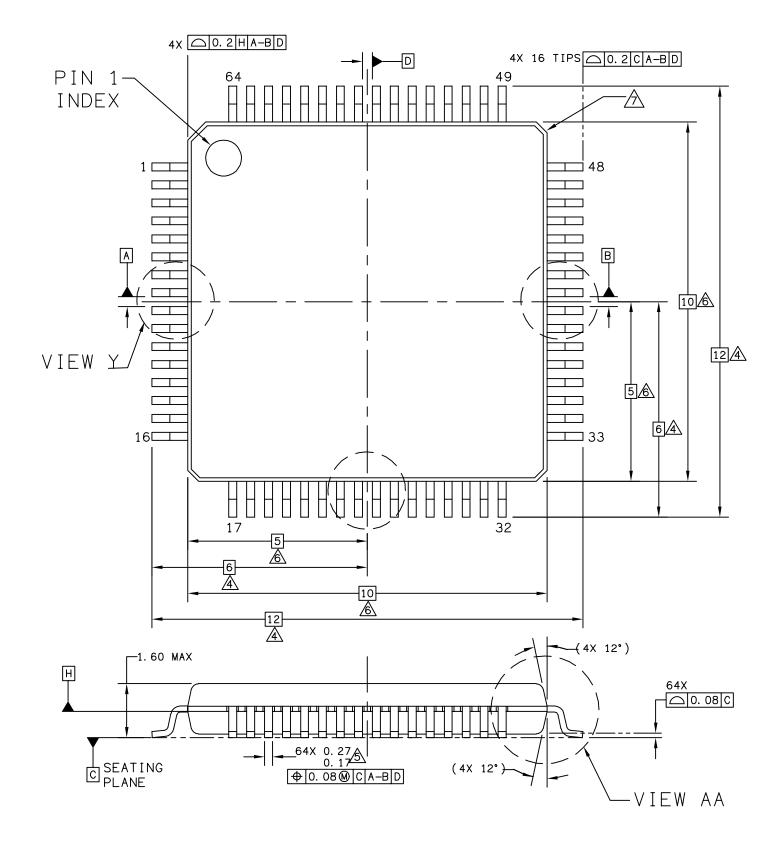

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |             | LOUTLINE       | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-------------|----------------|------------------|-------------|

| TITLE: 64LD LQFP,                                       | DOCUMENT NO | ): 98ASS23234W | REV: E           |             |

| 10 X 10 X 1.4 PKG,<br>0.5 PITCH, CASE OUTLINE           |             | CASE NUMBER    | 2: 840F-02       | 11 AUG 2006 |

|                                                         |             | STANDARD: JE   | DEC MS-026 BCD   |             |