Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                          |

| Program Memory Size        | 60KB (60K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 48-QFN-EP (7x7)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08aw60mfde |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |

| MC9S08AC16    |                     |                                                 |                                                  |

| MC9S908AC60   |                     |                                                 |                                                  |

| MC9S08AC128   |                     |                                                 |                                                  |

| MC9S08AW60    |                     |                                                 |                                                  |

| MC9S08GB60A   |                     |                                                 |                                                  |

| MC9S08GT16A   |                     |                                                 |                                                  |

| MC9S08JM16    |                     |                                                 |                                                  |

| MC9S08JM60    |                     |                                                 |                                                  |

| MC9S08LL16    |                     |                                                 |                                                  |

| MC9S08QE128   |                     |                                                 |                                                  |

| MC9S08QE32    |                     |                                                 |                                                  |

| MC9S08RG60    |                     |                                                 |                                                  |

| MCF51CN128    |                     |                                                 |                                                  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |

| MC9S08QB8     |                     |                                                 |                                                  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |

| MC9S08QG8     |                     |                                                 |                                                  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                  | 1/2006           | Initial external release.                                                                                                                                                                                                                                                                                                  |  |  |  |

| 2                  | 12/2006          | Includes KBI block changes; new V <sub>OL</sub> / I <sub>OL</sub> figures; RI <sub>DD</sub> spec changes; SC part numbers with ICG trim modifications; addition of Temp Sensor to ADC. Resolved the stop IDD issues, added RTI figure, bandgap information, and incorporated electricals edits and any ProjectSync issues. |  |  |  |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006. All rights reserved.

# Contents

| Section Number | Title                     | Page |

|----------------|---------------------------|------|

|                | Chapter 1<br>Introduction |      |

|                | Introduction              | 10   |

| 1.1 | Overview                  | 19 |

|-----|---------------------------|----|

| 1.2 | MCU Block Diagrams        | 19 |

|     | System Clock Distribution |    |

### Chapter 2 Pins and Connections

| 2.1 | Introduc | tion                                                                                   | 23 |

|-----|----------|----------------------------------------------------------------------------------------|----|

| 2.2 | Device F | Pin Assignment                                                                         |    |

|     |          | nended System Connections                                                              |    |

|     | 2.3.1    | Power (V <sub>DD</sub> , 2 x V <sub>SS</sub> , V <sub>DDAD</sub> , V <sub>SSAD</sub> ) |    |

|     |          | Oscillator (XTAL, EXTAL)                                                               |    |

|     | 2.3.3    | RESET Pin                                                                              |    |

|     | 2.3.4    | Background/Mode Select (BKGD/MS)                                                       | 29 |

|     | 2.3.5    | ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFL</sub> )                            |    |

|     | 2.3.6    | External Interrupt Pin (IRQ)                                                           |    |

|     | 2.3.7    | General-Purpose I/O and Peripheral Ports                                               |    |

### Chapter 3 Modes of Operation

| 3.1 | Introduc | tion                                     | 33 |

|-----|----------|------------------------------------------|----|

| 3.2 | Features |                                          |    |

| 3.3 | Run Mo   | de                                       |    |

| 3.4 | Active B | Background Mode                          |    |

|     |          | ode                                      |    |

| 3.6 | Stop Mo  | odes                                     | 34 |

|     | 3.6.1    | Stop2 Mode                               | 35 |

|     | 3.6.2    | *                                        |    |

|     | 3.6.3    | Active BDM Enabled in Stop Mode          |    |

|     | 3.6.4    | LVD Enabled in Stop Mode                 |    |

|     | 3.6.5    | On-Chip Peripheral Modules in Stop Modes |    |

|     |          |                                          |    |

### Chapter 4 Memory

| 4.1 | MC9S08AW60 Series Memory Map                 |  |

|-----|----------------------------------------------|--|

|     | 4.1.1 Reset and Interrupt Vector Assignments |  |

| 4.2 | Register Addresses and Bit Assignments       |  |

|     | RĂM                                          |  |

|     |                                              |  |

# NP

Chapter 1 Introduction

- The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop sub-module

- Control bits inside the ICG determine which source is connected.

- FFE is a control signal generated inside the ICG. If the frequency of ICGOUT > 4 × the frequency of ICGERCLK, this signal is a logic 1 and the fixed-frequency clock will be ICGERCLK/2. Otherwise the fixed-frequency clock will be BUSCLK.

- ICGLCLK Development tools can select this internal self-clocked source (~ 8 MHz) to speed up BDC communications in systems where the bus clock is slow.

- ICGERCLK External reference clock can be selected as the real-time interrupt clock source. Can also be used as the ALTCLK input to the ADC module.

Chapter 5 Resets, Interrupts, and System Configuration

- Illegal opcode detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self\_reset}$  selected. The reset pin is driven low for 34 bus cycles where the internal bus frequency is half the ICG frequency. After the 34 bus cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 bus cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.9.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>13</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user should write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is a logic 1 to enable the interrupt. The

#### Chapter 6 Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-38. Output Drive Strength Selection for Port F (PTFDS)

### Table 6-31. PTFDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFDS[7:0] | <ul> <li>Output Drive Strength Selection for Port F Bits — Each of these control bits selects between low and high output drive for the associated PTF pin.</li> <li>0 Low output drive enabled for port F bit n.</li> <li>1 High output drive enabled for port F bit n.</li> </ul> |

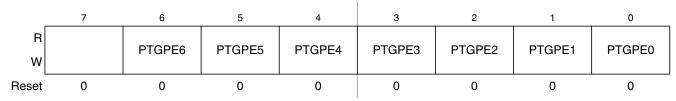

# 6.7.14 Port G Pin Control Registers (PTGPE, PTGSE, PTGDS)

In addition to the I/O control, port G pins are controlled by the registers listed below.

Figure 6-41. Internal Pullup Enable for Port G Bits (PTGPE)

#### Table 6-34. PTGPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGPE[6:0] | <ul> <li>Internal Pullup Enable for Port G Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTG pin. For port G pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port G bit n.</li> <li>1 Internal pullup device enabled for port G bit n.</li> </ul> |

|        | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|---|--------|--------|--------|--------|--------|--------|--------|

| R<br>W |   | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| Reset  | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-42. Output Slew Rate Control Enable for Port G Bits (PTGSE)

#### Table 6-35. PTGSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGSE[6:0] | <ul> <li>Output Slew Rate Control Enable for Port G Bits— Each of these control bits determine whether output slew rate control is enabled for the associated PTG pin. For port G pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port G bit n.</li> <li>1 Output slew rate control enabled for port G bit n.</li> </ul> |

- 0 = Bit forced to 0

- 1 = Bit forced to 1

- = Bit set or cleared according to results of operation

- U = Undefined after the operation

### Machine coding notation

- dd = Low-order 8 bits of a direct address 0x0000-0x00FF (high byte assumed to be 0x00)

- ee = Upper 8 bits of 16-bit offset

- ff = Lower 8 bits of 16-bit offset or 8-bit offset

- ii = One byte of immediate data

- jj = High-order byte of a 16-bit immediate data value

- kk = Low-order byte of a 16-bit immediate data value

- hh = High-order byte of 16-bit extended address

- II = Low-order byte of 16-bit extended address

- rr = Relative offset

### Source form

Everything in the source forms columns, *except expressions in italic characters*, is literal information that must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic is always a literal expression. All commas, pound signs (#), parentheses, and plus signs (+) are literal characters.

- n Any label or expression that evaluates to a single integer in the range 0–7

- opr8i Any label or expression that evaluates to an 8-bit immediate value

- opr16i Any label or expression that evaluates to a 16-bit immediate value

- *opr8a* Any label or expression that evaluates to an 8-bit value. The instruction treats this 8-bit value as the low order 8 bits of an address in the direct page of the 64-Kbyte address space (0x00xx).

- *opr16a* Any label or expression that evaluates to a 16-bit value. The instruction treats this value as an address in the 64-Kbyte address space.

- *oprx8* Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing

- *oprx16* Any label or expression that evaluates to a 16-bit value. Because the HCS08 has a 16-bit address bus, this can be either a signed or an unsigned value.

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the next address after the last byte of object code for the current instruction. The assembler will calculate the 8-bit signed offset and include it in the object code for this instruction.

### Address modes

- INH = Inherent (no operands)

- IMM = 8-bit or 16-bit immediate

- DIR = 8-bit direct

- EXT = 16-bit extended

Chapter 10 Timer/Pulse-Width Modulator (S08TPMV2)

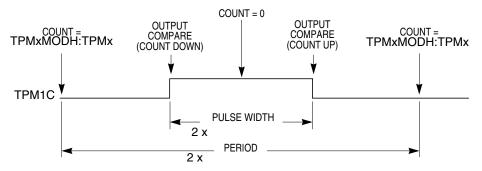

### 10.5.3 Center-Aligned PWM Mode

This type of PWM output uses the up-/down-counting mode of the timer counter (CPWMS = 1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal and the period is determined by the value in TPMxMODH:TPMxMODL.

TPMxMODH:TPMxMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

#### period = 2 x (TPMxMODH:TPMxMODL); for TPMxMODH:TPMxMODL = 0x0001–0x7FFF Eqn. 10-2

If the channel value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (nonzero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if generation of 100% duty cycle is not necessary). This is not a significant limitation because the resulting period is much longer than required for normal applications.

TPMxMODH:TPMxMODL = 0x0000 is a special case that should not be used with center-aligned PWM mode. When CPWMS = 0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS = 1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

Figure 10-12 shows the output compare value in the TPM channel registers (multiplied by 2), which determines the pulse width (duty cycle) of the CPWM signal. If ELSnA = 0, the compare match while counting up forces the CPWM output signal low and a compare match while counting down forces the output high. The counter counts up until it reaches the modulo setting in TPMxMODH:TPMxMODL, then counts down until it reaches zero. This sets the period equal to two times TPMxMODH:TPMxMODL.

Figure 10-12. CPWM Period and Pulse Width (ELSnA = 0)

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin transitions are lined up at the same system clock edge. This type of PWM is also required for some types of motor drives.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are

| Table 11-5. SCIxS1 | Register Field | Descriptions | (continued) |

|--------------------|----------------|--------------|-------------|

|--------------------|----------------|--------------|-------------|

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RDRF | Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). In 8-bit mode, to clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD). In 9-bit mode, to clear RDRF, read SCIxS1 with RDRF = 1 and then read SCIxD and the SCI control 3 register (SCIxC3). SCIxD and SCIxC3 can be read in any order, but the flag is cleared only after both data registers are read.         0       Receive data register full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1<br>FE   | Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).         0 No framing error detected. This does not guarantee the framing is correct.         1 Framing error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0<br>PF   | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Chapter 13 Inter-Integrated Circuit (S08IICV1)

# **13.7** Initialization/Application Information

| Module Initialization (Slave)                                    |                                                                                                                                                                            |                                                                                                                              |                          |  |  |  |  |  |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|

| 1.                                                               | Write: IICA<br>— to set the slave address                                                                                                                                  |                                                                                                                              |                          |  |  |  |  |  |  |

| 2.                                                               | Write: IICC                                                                                                                                                                |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  | <ul> <li>to enable IIC and interrupts</li> </ul>                                                                                                                           |                                                                                                                              |                          |  |  |  |  |  |  |

| 3.                                                               |                                                                                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                                                    |                          |  |  |  |  |  |  |

| 4.                                                               | Initialize                                                                                                                                                                 | RAM variables used to achieve the routine shown in Figure 13-11                                                              |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            |                                                                                                                              |                          |  |  |  |  |  |  |

| 1.                                                               | Write: IIC                                                                                                                                                                 | Module Initialization (Master)                                                                                               |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | t the IIC baud rate (example provided in this chapter)                                                                       |                          |  |  |  |  |  |  |

| 2.                                                               | Write: IIC                                                                                                                                                                 | C                                                                                                                            |                          |  |  |  |  |  |  |

| ~                                                                |                                                                                                                                                                            | able IIC and interrupts                                                                                                      |                          |  |  |  |  |  |  |

| 3.<br>4.                                                         |                                                                                                                                                                            | RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>RAM variables used to achieve the routine shown in Figure 13-11 |                          |  |  |  |  |  |  |

| 4.<br>5.                                                         | Write: IIC                                                                                                                                                                 |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  | — to er                                                                                                                                                                    |                                                                                                                              |                          |  |  |  |  |  |  |

| 6.                                                               | Write: IIC                                                                                                                                                                 |                                                                                                                              |                          |  |  |  |  |  |  |

| 7                                                                | — to er<br>Write: IIC                                                                                                                                                      | able MST (master mode)                                                                                                       |                          |  |  |  |  |  |  |

| 7.                                                               |                                                                                                                                                                            | b<br>he address of the target slave. (The LSB of this byte will determine wheth                                              | her the communication is |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | er receive or transmit.)                                                                                                     |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | Module Use                                                                                                                   |                          |  |  |  |  |  |  |

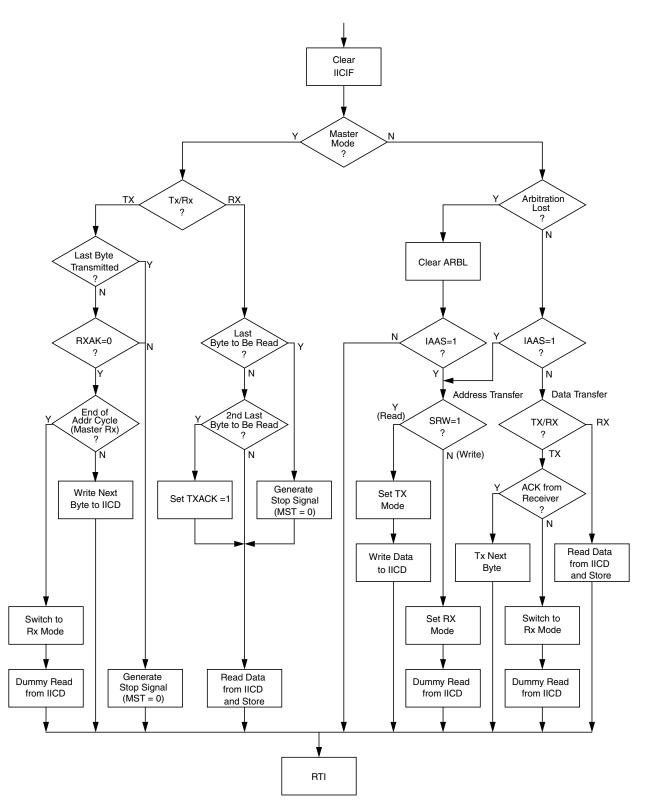

|                                                                  |                                                                                                                                                                            | he shown in Figure 13-11 can handle both master and slave IIC operations                                                     |                          |  |  |  |  |  |  |

|                                                                  | incoming IIC message that contains the proper address will begin IIC communication. For master operation, communication must be initiated by writing to the IICD register. |                                                                                                                              |                          |  |  |  |  |  |  |

| communication must be initiated by writing to the IICD register. |                                                                                                                                                                            |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | Register Model                                                                                                               |                          |  |  |  |  |  |  |

|                                                                  | IICA                                                                                                                                                                       | ADDR                                                                                                                         | 0                        |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | Address to which the module will respond when addressed as a slave (ir                                                       | slave mode)              |  |  |  |  |  |  |

|                                                                  | IICF MULT ICR                                                                                                                                                              |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                                                                                                                            |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  | IICC                                                                                                                                                                       | IICEN IICIE MST TX TXAK RSTA 0                                                                                               | 0                        |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | Module configuration                                                                                                         |                          |  |  |  |  |  |  |

|                                                                  | IICS                                                                                                                                                                       | TCF IAAS BUSY ARBL 0 SRW IICIF                                                                                               | RXAK                     |  |  |  |  |  |  |

|                                                                  | Module status flags                                                                                                                                                        |                                                                                                                              |                          |  |  |  |  |  |  |

|                                                                  | IICD                                                                                                                                                                       | DATA                                                                                                                         |                          |  |  |  |  |  |  |

|                                                                  |                                                                                                                                                                            | Data register; Write to transmit IIC data read to read IIC data                                                              |                          |  |  |  |  |  |  |

|                                                                  | Data register, write to transmit no data read to read no data                                                                                                              |                                                                                                                              |                          |  |  |  |  |  |  |

### Figure 13-10. IIC Module Quick Start

Figure 13-11. Typical IIC Interrupt Routine

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>ACFE  | <ul> <li>Compare Function Enable — ACFE is used to enable the compare function.</li> <li>0 Compare function disabled</li> <li>1 Compare function enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>ACFGT | <ul> <li>Compare Function Greater Than Enable — ACFGT is used to configure the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.</li> <li>0 Compare triggers when input is less than compare level</li> <li>1 Compare triggers when input is greater than or equal to compare level</li> </ul> |

Table 14-4. ADC1SC2 Register Field Descriptions (continued)

### 14.4.3 Data Result High Register (ADC1RH)

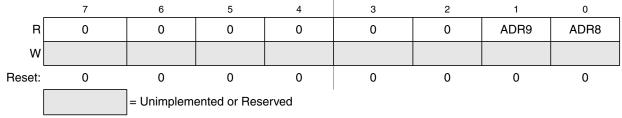

ADC1RH contains the upper two bits of the result of a 10-bit conversion. When configured for 8-bit conversions both ADR8 and ADR9 are equal to zero. ADC1RH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit MODE, reading ADC1RH prevents the ADC from transferring subsequent conversion results into the result registers until ADC1RL is read. If ADC1RL is not read until after the next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode there is no interlocking with ADC1RL. In the case that the MODE bits are changed, any data in ADC1RH becomes invalid.

Figure 14-6. Data Result High Register (ADC1RH)

### 14.4.4 Data Result Low Register (ADC1RL)

ADC1RL contains the lower eight bits of the result of a 10-bit conversion, and all eight bits of an 8-bit conversion. This register is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. In 10-bit mode, reading ADC1RH prevents the ADC from transferring subsequent conversion results into the result registers until ADC1RL is read. If ADC1RL is not read until the after next conversion is completed, then the intermediate conversion results will be lost. In 8-bit mode, there is no interlocking with ADC1RH. In the case that the MODE bits are changed, any data in ADC1RL becomes invalid.

| ADICLK | Selected Clock Source      |  |  |

|--------|----------------------------|--|--|

| 00     | Bus clock                  |  |  |

| 01     | Bus clock divided by 2     |  |  |

| 10     | Alternate clock (ALTCLK)   |  |  |

| 11     | Asynchronous clock (ADACK) |  |  |

#### Table 14-8. Input Clock Select

### 14.4.8 Pin Control 1 Register (APCTL1)

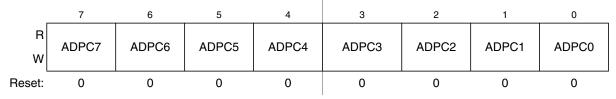

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 14-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |

#### Table 14-9. APCTL1 Register Field Descriptions

#### Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

- 2. Update status and control register 2 (ADCSC2) to select the conversion trigger (hardware or software) and compare function options, if enabled.

- 3. Update status and control register 1 (ADCSC1) to select whether conversions will be continuous or completed only once, and to enable or disable conversion complete interrupts. The input channel on which conversions will be performed is also selected here.

### 14.6.1.2 Pseudo — Code Example

In this example, the ADC module will be set up with interrupts enabled to perform a single 10-bit conversion at low power with a long sample time on input channel 1, where the internal ADCK clock will be derived from the bus clock divided by 1.

### ADCCFG = 0x98 (%10011000)

| Bit 7   | ADLPC  | 1  | Configures for low power (lowers maximum clock speed) |

|---------|--------|----|-------------------------------------------------------|

| Bit 6:5 | ADIV   | 00 | Sets the ADCK to the input clock $\div$ 1             |

| Bit 4   | ADLSMP | 1  | Configures for long sample time                       |

| Bit 3:2 | MODE   | 10 | Sets mode at 10-bit conversions                       |

| Bit 1:0 | ADICLK | 00 | Selects bus clock as input clock source               |

|         |        |    |                                                       |

### ADCSC2 = 0x00 (% 00000000)

| Bit 7   | ADACT | 0  | Flag indicates if a conversion is in progress            |

|---------|-------|----|----------------------------------------------------------|

| Bit 6   | ADTRG | 0  | Software trigger selected                                |

| Bit 5   | ACFE  | 0  | Compare function disabled                                |

| Bit 4   | ACFGT | 0  | Not used in this example                                 |

| Bit 3:2 |       | 00 | Unimplemented or reserved, always reads zero             |

| Bit 1:0 |       | 00 | Reserved for Freescale's internal use; always write zero |

|         |       |    |                                                          |

### ADCSC1 = 0x41 (%01000001)

| Bit 7   | COCO | 0     | Read-only flag which is set when a conversion completes |

|---------|------|-------|---------------------------------------------------------|

| Bit 6   | AIEN | 1     | Conversion complete interrupt enabled                   |

| Bit 5   | ADCO | 0     | One conversion only (continuous conversions disabled)   |

| Bit 4:0 | ADCH | 00001 | Input channel 1 selected as ADC input channel           |

### ADCRH/L = 0xxx

Holds results of conversion. Read high byte (ADCRH) before low byte (ADCRL) so that conversion data cannot be overwritten with data from the next conversion.

### ADCCVH/L = 0xxx

Holds compare value when compare function enabled

### APCTL1=0x02

AD1 pin I/O control disabled. All other AD pins remain general purpose I/O pins

### APCTL2=0x00

All other AD pins remain general purpose I/O pins

Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

- Average the result by converting the analog input many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and averaging. Noise that is synchronous to ADCK cannot be averaged out.

### 14.7.2.4 Code Width and Quantization Error

The ADC quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

### $1LSB = (V_{REFH} - V_{REFL}) / 2^{N}$ Eqn. 14-2

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm 1/2$ LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

### 14.7.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error ( $E_{ZS}$ ) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is used.

- Full-scale error  $(E_{FS})$  This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

### 14.7.2.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the

Figure 15-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 15-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

Appendix A Electrical Characteristics and Timing Specifications

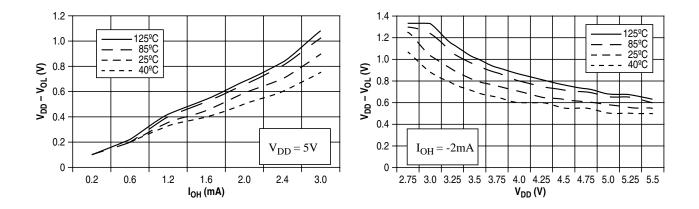

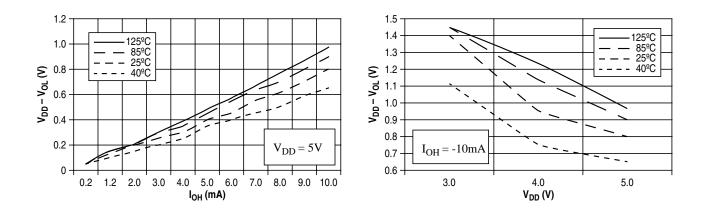

Figure A-3. Typical High-Side (Source) Characteristics — Low Drive (PTxDS<sub>n</sub> = 0)

Figure A-4. Typical High-Side (Source) Characteristics — High Drive (PTxDSn = 1)

Appendix A Electrical Characteristics and Timing Specifications

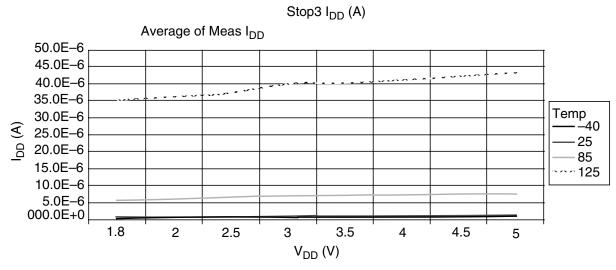

Figure A-7. Typical Stop3 I<sub>DD</sub>

# A.8 ADC Characteristics

| Characteristic                              | Conditions                                                                  | Symb               | Min               | Typ <sup>1</sup>  | Max               | Unit |

|---------------------------------------------|-----------------------------------------------------------------------------|--------------------|-------------------|-------------------|-------------------|------|

| Supply voltage                              | Absolute                                                                    | V <sub>DDAD</sub>  | 2.7               | _                 | 5.5               | V    |

|                                             | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | ΔV <sub>DDAD</sub> | -100              | 0                 | +100              | mV   |

| Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | ΔV <sub>SSAD</sub> | -100              | 0                 | +100              | mV   |

| Ref voltage high                            |                                                                             | V <sub>REFH</sub>  | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V    |

| Ref voltage low                             |                                                                             | V <sub>REFL</sub>  | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V    |

| Input voltage                               |                                                                             | V <sub>ADIN</sub>  | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |

| Input capacitance                           |                                                                             | C <sub>ADIN</sub>  | _                 | 4.5               | 5.5               | pF   |

| Input resistance                            |                                                                             | R <sub>ADIN</sub>  | _                 | 3                 | 5                 | kΩ   |

| Analog source resistance<br>External to MCU | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>    |                   |                   | 5<br>10           | kΩ   |

|                                             | 8-bit mode (all valid f <sub>ADCK</sub> )                                   |                    | _                 | _                 | 10                |      |

| ADC conversion clock frequency              | High speed (ADLPC = 0)                                                      | f <sub>ADCK</sub>  | 0.4               | _                 | 8.0               | MHz  |

|                                             | Low power (ADLPC = 1)                                                       |                    | 0.4               | _                 | 4.0               |      |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> dc potential difference.

# Appendix B Ordering Information and Mechanical Drawings

# **B.1** Ordering Information

This section contains ordering numbers for MC9S08AW60 Series devices. See below for an example of the device numbering system.

| Device Number <sup>1</sup> | Memory |      | Available Packages <sup>2</sup> |

|----------------------------|--------|------|---------------------------------|

|                            | FLASH  | RAM  | Туре                            |

| MC9S08AW60                 | 63,280 |      | 64-pin LQFP                     |

| MC9S08AW48                 | 49,152 | 2048 | 64-pin QFP                      |

| MC9S08AW32                 | 32,768 |      | 48-pin QFN                      |

| MC9S08AW16                 | 16,384 | 1024 | 44-pin LQFP                     |

### Table B-1. Consumer and Industrial Device Numbering System

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-3 for package information.

#### Table B-2. Automotive Device Numbering System

| Device Number <sup>1</sup>          | Memory                     |      | Available Packages <sup>2</sup>          |

|-------------------------------------|----------------------------|------|------------------------------------------|

|                                     | FLASH                      | RAM  | Туре                                     |

| S9S08AW60<br>S9S08AW48<br>S9S08AW32 | 63,280<br>49,152<br>32,768 | 2048 | 64-pin LQFP<br>48-pin QFN<br>44-pin LQFP |

| S9S08AW16                           | 16,384                     | 1024 | 48-pin QFN<br>44-pin LQFP                |

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-3 for package information.