# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-QFP                                                                 |

| Supplier Device Package    | 64-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08aw60mfue |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08AW60 Data Sheet

Covers: MC9S08AW60 MC9S08AW48 MC9S08AW32 MC9S08AW16

> MC9S08AW60 Rev 2 12/2006

## **Section Number**

Title

## Page

|     | 7.2.1     | Accumulator (A)                 | 110 |

|-----|-----------|---------------------------------|-----|

|     | 7.2.2     | Index Register (H:X)            |     |

|     | 7.2.3     | Stack Pointer (SP)              |     |

|     | 7.2.4     | Program Counter (PC)            |     |

|     | 7.2.5     | Condition Code Register (CCR)   |     |

| 7.3 | Addressi  | ng Modes                        | 113 |

|     | 7.3.1     | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2     | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3     | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4     | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5     | Extended Addressing Mode (EXT)  | 114 |

|     | 7.3.6     | Indexed Addressing Mode         | 114 |

| 7.4 | Special C | Operations                      | 115 |

|     | 7.4.1     | Reset Sequence                  | 115 |

|     | 7.4.2     | Interrupt Sequence              |     |

|     | 7.4.3     | Wait Mode Operation             |     |

|     | 7.4.4     | Stop Mode Operation             |     |

|     | 7.4.5     | BGND Instruction                | 117 |

| 7.5 | HCS08 I   | nstruction Set Summary          | 118 |

# Chapter 8 Internal Clock Generator (S08ICGV4)

| Introduc | tion                                                                                                                                                                    | 131                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 8.1.1    | Features                                                                                                                                                                | 131                                         |

| 8.1.2    | Modes of Operation                                                                                                                                                      | 132                                         |

| 8.1.3    | Block Diagram                                                                                                                                                           | 133                                         |

| External | Signal Description                                                                                                                                                      | 133                                         |

| 8.2.1    | EXTAL — External Reference Clock / Oscillator Input                                                                                                                     | 133                                         |

| 8.2.2    | XTAL — Oscillator Output                                                                                                                                                | 133                                         |

| 8.2.3    |                                                                                                                                                                         |                                             |

| 8.2.4    | External Crystal/Resonator Connections                                                                                                                                  | 134                                         |

| Register | Definition                                                                                                                                                              | 135                                         |

| 8.3.1    | ICG Control Register 1 (ICGC1)                                                                                                                                          | 135                                         |

| 8.3.2    | ICG Control Register 2 (ICGC2)                                                                                                                                          | 137                                         |

| 8.3.3    | ICG Status Register 1 (ICGS1)                                                                                                                                           | 138                                         |

| 8.3.4    | ICG Status Register 2 (ICGS2)                                                                                                                                           | 139                                         |

| 8.3.5    | ICG Filter Registers (ICGFLTU, ICGFLTL)                                                                                                                                 | 139                                         |

| 8.3.6    | ICG Trim Register (ICGTRM)                                                                                                                                              | 140                                         |

| Function | al Description                                                                                                                                                          | 140                                         |

| 8.4.1    | Off Mode (Off)                                                                                                                                                          | 141                                         |

| 8.4.2    | Self-Clocked Mode (SCM)                                                                                                                                                 | 141                                         |

| 8.4.3    | FLL Engaged, Internal Clock (FEI) Mode                                                                                                                                  | 142                                         |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>External<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Register<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Function<br>8.4.1<br>8.4.2 | <ul> <li>8.1.2 Modes of Operation</li></ul> |

**Chapter 2 Pins and Connections**

# 2.3.1 Power ( $V_{DD}$ , 2 x $V_{SS}$ , $V_{DDAD}$ , $V_{SSAD}$ )

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the paired V<sub>DD</sub> and V<sub>SS</sub> power pins as practical to suppress high-frequency noise. The MC9S08AW60 has a second V<sub>SS</sub> pin. This pin should be connected to the system ground plane or to the primary V<sub>SS</sub> pin through a low-impedance connection.

$V_{DDAD}$  and  $V_{SSAD}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the analog power pins as practical to suppress high-frequency noise.

# 2.3.2 Oscillator (XTAL, EXTAL)

Out of reset, the MCU uses an internally generated clock (self-clocked mode —  $f_{Self\_reset}$ ) equivalent to about 8-MHz crystal rate. This frequency source is used during reset startup and can be enabled as the clock source for stop recovery to avoid the need for a long crystal startup delay. This MCU also contains a trimmable internal clock generator (ICG) module that can be used to run the MCU. For more information on the ICG, see the Chapter 8, "Internal Clock Generator (S08ICGV4)."

The oscillator amplitude on XTAL and EXTAL is gain limited for low-power oscillation. Typically, these pins have a 1-V peak-to-peak signal. For noisy environments, the high gain output (HGO) bit can be set to enable rail-to-rail oscillation.

The oscillator in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator in either of two frequency ranges selected by the RANGE bit in the ICGC1 register. Rather than a crystal or ceramic resonator, an external oscillator can be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion.  $R_S$  (when used) and  $R_F$  should be low-inductance resistors such as carbon composition resistors. Wire-wound resistors, and some metal film resistors, have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup and its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2 which are usually the same size. As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

Chapter 5 Resets, Interrupts, and System Configuration

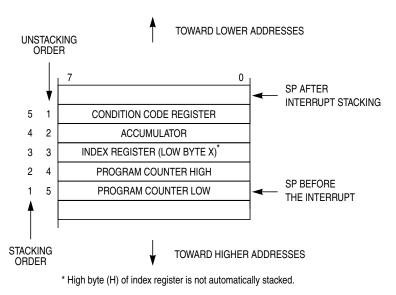

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

The status flag causing the interrupt must be acknowledged (cleared) before returning from the ISR. Typically, the flag should be cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

# 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQSC status and control register. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

## 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in the IRQSC register must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

When the IRQ pin is configured to detect rising edges, an optional pulldown resistor is available rather than a pullup resistor. BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

## 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

## 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

# 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

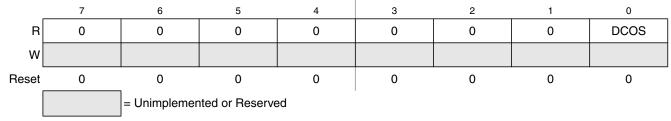

## 8.3.4 ICG Status Register 2 (ICGS2)

#### Figure 8-9. ICG Status Register 2 (ICGS2)

#### Table 8-4. ICGS2 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | <ul> <li>DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n<sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.</li> <li>0 DCO clock is unstable.</li> <li>1 DCO clock is stable.</li> </ul> |

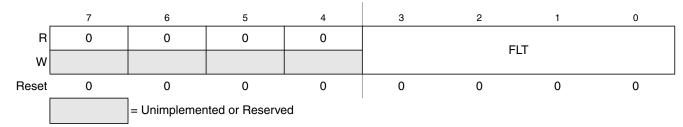

## 8.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

#### Figure 8-10. ICG Upper Filter Register (ICGFLTU)

#### Table 8-5. ICGFLTU Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

## 8.4.9 FLL Loss-of-Clock Detection

The reference clock and the DCO clock are monitored under different conditions (see Table 8-8). Provided the reference frequency is being monitored, ERCS = 1 indicates that the reference clock meets minimum frequency requirements. When the reference and/or DCO clock(s) are being monitored, if either one falls below a certain frequency,  $f_{LOR}$  and  $f_{LOD}$ , respectively, the LOCS status bit will be set to indicate the error. LOCS will remain set until it is acknowledged or until the MCU is reset. LOCS is cleared by reading ICGS1 then writing 1 to ICGIF (LOCRE = 0), or by a loss-of-clock induced reset (LOCRE = 1), or by any MCU reset.

If the ICG is in FEE, a loss of reference clock causes the ICG to enter SCM, and a loss of DCO clock causes the ICG to enter FBE mode. If the ICG is in FBE mode, a loss of reference clock will cause the ICG to enter SCM. In each case, the CLKST and CLKS bits will be automatically changed to reflect the new state.

If the ICG is in FEE mode when a loss of clock occurs and the ERCS is still set to 1, then the CLKST bits are set to 10 and the ICG reverts to FBE mode.

A loss of clock will also cause a loss of lock when in FEE or FEI modes. Because the method of clearing the LOCS and LOLS bits is the same, this would only be an issue in the unlikely case that LOLRE = 1 and LOCRE = 0. In this case, the interrupt would be overridden by the reset for the loss of lock.

| Mode                | CLKS     | REFST | ERCS                   | External Reference<br>Clock<br>Monitored? | DCO Clock<br>Monitored? |

|---------------------|----------|-------|------------------------|-------------------------------------------|-------------------------|

| Off                 | 0X or 11 | Х     | Forced Low             | No                                        | No                      |

|                     | 10       | 0     | Forced Low             | No                                        | No                      |

|                     | 10       | 1     | Real-Time <sup>1</sup> | Yes <sup>(1)</sup>                        | No                      |

| SCM                 | 0X       | Х     | Forced Low             | No                                        | Yes <sup>2</sup>        |

| (CLKST = 00)        | 10       | 0     | Forced High            | No                                        | Yes <sup>(2)</sup>      |

|                     | 10       | 1     | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

|                     | 11       | Х     | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

| FEI                 | 0X       | Х     | Forced Low             | No                                        | Yes                     |

| (CLKST = 01)        | 11       | Х     | Real-Time              | Yes                                       | Yes                     |

| FBE                 | 10       | 0     | Forced High            | No                                        | No                      |

| (CLKST = 10)        | 10       | 1     | Real-Time              | Yes                                       | No                      |

| FEE<br>(CLKST = 11) | 11       | Х     | Real-Time              | Yes                                       | Yes                     |

Table 8-8. Clock Monitoring (When LOCD = 0)

<sup>1</sup> If ENABLE is high (waiting for external crystal start-up after exiting stop).

<sup>2</sup> DCO clock will not be monitored until DCOS = 1 upon entering SCM from off or FLL bypassed external mode.

Chapter 9 Keyboard Interrupt (S08KBIV1)

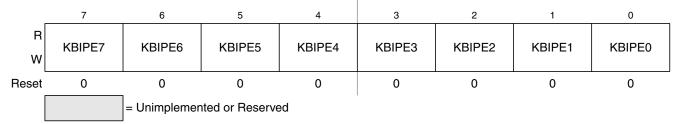

# 9.4.2 KBI Pin Enable Register (KBI1PE)

#### Figure 9-4. KBI Pin Enable Register (KBI1PE)

| Table 9-3. KBI1PE Register Field Descriptio | ns |

|---------------------------------------------|----|

|---------------------------------------------|----|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>KBIPE[7:0] | <ul> <li>Keyboard Pin Enable for KBI Port Bits — Each of these read/write bits selects whether the associated KBI port pin is enabled as a keyboard interrupt input or functions as a general-purpose I/O pin.</li> <li>0 Bit n of KBI port is a general-purpose I/O pin not associated with the KBI</li> <li>1 Bit n of KBI port enabled as a keyboard interrupt input</li> </ul> |

# 9.5 Functional Description

## 9.5.1 Pin Enables

The KBIPEn control bits in the KBI1PE register allow a user to enable (KBIPEn = 1) any combination of KBI-related port pins to be connected to the KBI module. Pins corresponding to 0s in KBI1PE are general-purpose I/O pins that are not associated with the KBI module.

## 9.5.2 Edge and Level Sensitivity

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled keyboard inputs in a KBI module must be at the deasserted logic level.

A falling edge is detected when an enabled keyboard input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle.

A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

The KBIMOD control bit can be set to reconfigure the detection logic so that it detects edges and levels. In KBIMOD = 1 mode, the KBF status flag becomes set when an edge is detected (when one or more enabled pins change from the deasserted to the asserted level while all other enabled pins remain at their deasserted levels), but the flag is continuously set (and cannot be cleared) as long as any enabled keyboard input pin remains at the asserted level. When the MCU enters stop3 mode, the synchronous edge-detection logic is bypassed (because clocks are stopped). In stop3 mode, KBI inputs act as asynchronous level-sensitive inputs so they can wake the MCU from stop3 mode.

#### 10.2.1 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

#### 10.2.2 Block Diagram

Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

Chapter 11 Serial Communications Interface (S08SCIV2)

character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU = 1, it inhibits setting of the status flags associated with the receiver, thus eliminating the software overhead for handling the unimportant message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

#### 11.3.3.2.1 Idle-Line Wakeup

When WAKE = 0, the receiver is configured for idle-line wakeup. In this mode, RWU is cleared automatically when the receiver detects a full character time of the idle-line level. The M control bit selects 8-bit or 9-bit data mode that determines how many bit times of idle are needed to constitute a full character time (10 or 11 bit times because of the start and stop bits).

When the RWU bit is set, the idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF. It therefore will not generate an interrupt when this idle character occurs. The receiver will wake up and wait for the next data transmission which will set RDRF and generate an interrupt if enabled.

The idle-line type (ILT) control bit selects one of two ways to detect an idle line. When ILT = 0, the idle bit counter starts after the start bit so the stop bit and any logic 1s at the end of a character count toward the full character time of idle. When ILT = 1, the idle bit counter does not start until after a stop bit time, so the idle detection is not affected by the data in the last character of the previous message.

#### 11.3.3.2.2 Address-Mark Wakeup

When WAKE = 1, the receiver is configured for address-mark wakeup. In this mode, RWU is cleared automatically when the receiver detects a logic 1 in the most significant bit of a received character (eighth bit in M = 0 mode and ninth bit in M = 1 mode).

Address-mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames. The logic 1 MSB of an address frame clears the receivers RWU bit before the stop bit is received and sets the RDRF flag.

## 11.3.4 Interrupts and Status Flags

The SCI system has three separate interrupt vectors to reduce the amount of software needed to isolate the cause of the interrupt. One interrupt vector is associated with the transmitter for TDRE and TC events. Another interrupt vector is associated with the receiver for RDRF and IDLE events, and a third vector is used for OR, NF, FE, and PF error conditions. Each of these eight interrupt sources can be separately masked by local interrupt enable masks. The flags can still be polled by software when the local masks are cleared to disable generation of hardware interrupt requests.

The SCI transmitter has two status flags that optionally can generate hardware interrupt requests. Transmit data register empty (TDRE) indicates when there is room in the transmit data buffer to write another transmit character to SCIxD. If the transmit interrupt enable (TIE) bit is set, a hardware interrupt will be requested whenever TDRE = 1. Transmit complete (TC) indicates that the transmitter is finished transmitting all data, preamble, and break characters and is idle with TxD high. This flag is often used in

## **13.4 Functional Description**

This section provides a complete functional description of the IIC module.

#### 13.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- START signal

- Slave address transmission

- Data transfer

- STOP signal

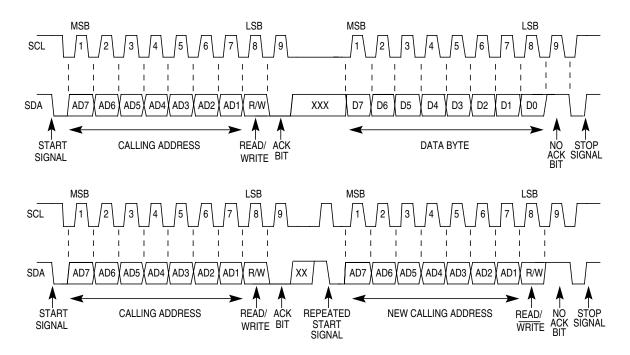

The STOP signal should not be confused with the CPU STOP instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 13-8.

Figure 13-8. IIC Bus Transmission Signals

Chapter 13 Inter-Integrated Circuit (S08IICV1)

#### 13.4.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 13-8, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

#### 13.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 13-8).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

#### 13.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 13-8. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

#### 14.2.2.1 Analog Pin Enables

The ADC on MC9S08AW60 Series contains only two analog pin enable registers, APCTL1 and APCTL2.

#### 14.2.2.2 Low-Power Mode Operation

The ADC is capable of running in stop3 mode but requires LVDSE and LVDE in SPMSC1 to be set.

#### 14.2.3 Temperature Sensor

The ADC1 module includes a temperature sensor whose output is connected to one of the ADC analog channel inputs. Equation 14-1 provides an approximate transfer function of the temperature sensor.

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- $V_{\text{TEMP25}}$  is the voltage of the temperature sensor channel at 25°C.

- m is the hot or cold voltage versus temperature slope in  $V/^{\circ}C$ .

For temperature calculations, use the V<sub>TEMP25</sub> and m values from the ADC Electricals table.

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$  the cold slope value is applied in Equation 14-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 14-1.

#### Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

5. Pins PTD7, PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

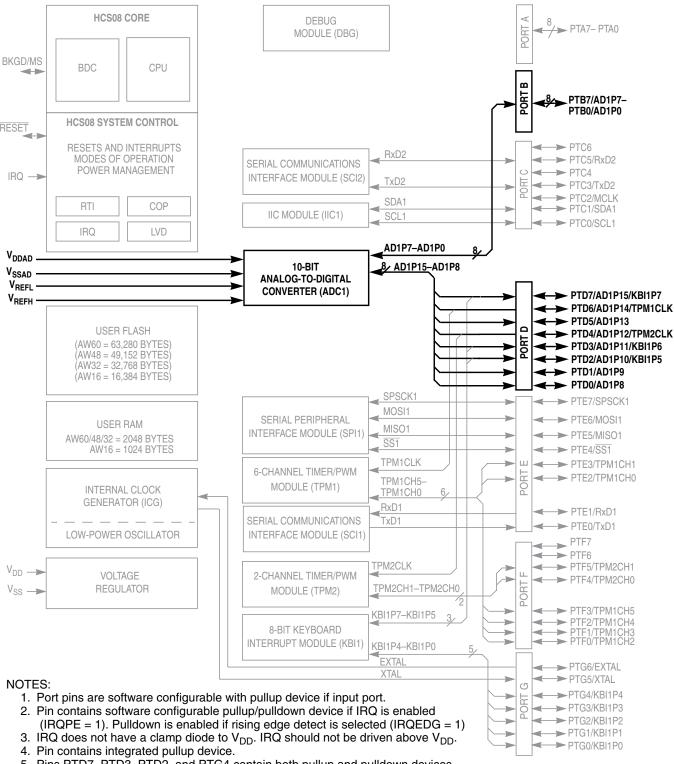

#### Figure 14-1. MC9S08AW60 Block Diagram Highlighting ADC Block and Pins

MC9S08AW60 Data Sheet, Rev 2

#### 14.5.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

#### NOTE

It is possible for the ADC module to wake the system from low power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software should ensure that the data transfer blocking mechanism (discussed in Section 14.5.4.2, "Completing Conversions) is cleared when entering stop3 and continuing ADC conversions.

## 14.5.8 MCU Stop1 and Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters either stop1 or stop2 mode. All module registers contain their reset values following exit from stop1 or stop2. Therefore the module must be re-enabled and re-configured following exit from stop1 or stop2.

## 14.6 Initialization Information

This section gives an example which provides some basic direction on how a user would initialize and configure the ADC module. The user has the flexibility of choosing between configuring the module for 8-bit or 10-bit resolution, single or continuous conversion, and a polled or interrupt approach, among many other options. Refer to Table 14-6, Table 14-7, and Table 14-8 for information used in this example.

#### NOTE

Hexadecimal values designated by a preceding 0x, binary values designated by a preceding %, and decimal values have no preceding character.

### 14.6.1 ADC Module Initialization Example

#### 14.6.1.1 Initialization Sequence

Before the ADC module can be used to complete conversions, an initialization procedure must be performed. A typical sequence is as follows:

1. Update the configuration register (ADCCFG) to select the input clock source and the divide ratio used to generate the internal clock, ADCK. This register is also used for selecting sample time and low-power configuration.

**Chapter 15 Development Support**

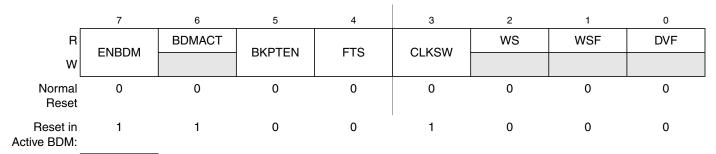

## 15.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

#### Figure 15-5. BDC Status and Control Register (BDCSCR)

#### Table 15-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.</li> <li>0 BDM cannot be made active (non-intrusive commands still allowed)</li> <li>1 BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.0 BDM not active (user application program running)1 BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.         0 Alternate BDC clock source         1 MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Appendix A Electrical Characteristics and Timing Specifications

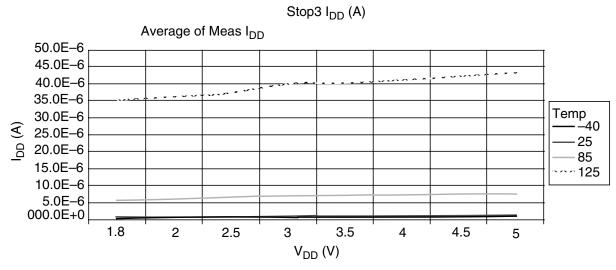

Figure A-7. Typical Stop3 I<sub>DD</sub>

# A.8 ADC Characteristics

| Characteristic                              | Conditions                                                                  | Symb               | Min               | Typ <sup>1</sup>  | Max               | Unit |

|---------------------------------------------|-----------------------------------------------------------------------------|--------------------|-------------------|-------------------|-------------------|------|

| Supply voltage                              | Absolute                                                                    | V <sub>DDAD</sub>  | 2.7               | _                 | 5.5               | V    |

|                                             | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | ΔV <sub>DDAD</sub> | -100              | 0                 | +100              | mV   |

| Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | ΔV <sub>SSAD</sub> | -100              | 0                 | +100              | mV   |

| Ref voltage high                            |                                                                             | V <sub>REFH</sub>  | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V    |

| Ref voltage low                             |                                                                             | V <sub>REFL</sub>  | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V    |

| Input voltage                               |                                                                             | V <sub>ADIN</sub>  | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |

| Input capacitance                           |                                                                             | C <sub>ADIN</sub>  | _                 | 4.5               | 5.5               | pF   |

| Input resistance                            |                                                                             | R <sub>ADIN</sub>  | _                 | 3                 | 5                 | kΩ   |

| Analog source resistance<br>External to MCU | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>    |                   |                   | 5<br>10           | kΩ   |

|                                             | 8-bit mode (all valid f <sub>ADCK</sub> )                                   |                    | _                 | _                 | 10                |      |

| ADC conversion clock frequency              | High speed (ADLPC = 0)                                                      | f <sub>ADCK</sub>  | 0.4               | _                 | 8.0               | MHz  |

|                                             | Low power (ADLPC = 1)                                                       |                    | 0.4               | _                 | 4.0               |      |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> dc potential difference.

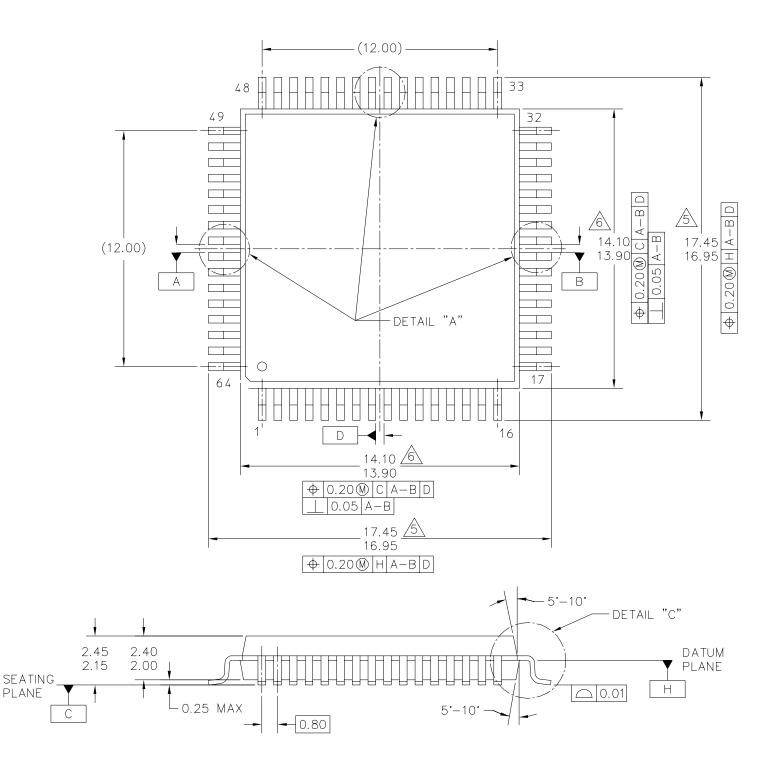

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA    | L OUTLINE                       | PRINT VERSION NO | IT TO SCALE |

|---------------------------------------------------------|--------------|---------------------------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NE  | ]: 98ASB42844B                  | RE∨: B           |             |

| 64LD QFP (14 X 14)                                      |              | CASE NUMBER: 840B-01 20 MAY 200 |                  |             |

|                                                         | STANDARD: NE | IN-JEDEC                        |                  |             |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS A-B AND -D- TO BE DETERMINED AT DATUM PLANE -H-.

5 dimensions to be determined at seating plane -C-.

- DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- Z DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDICTION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

| © FREESCALE SEMICONDUCTOR, INC. MECHANICA |  | L OUTLINE                | PRINT VERSION NO | DT TO SCALE |

|-------------------------------------------|--|--------------------------|------------------|-------------|

| TITLE:<br>64LD QFP (14 X 14)              |  | DOCUMENT NO: 98ASB42844B |                  | REV: B      |

|                                           |  | CASE NUMBER              | R: 840B-01       | 20 MAY 2005 |

|                                           |  | STANDARD: NON-JEDEC      |                  |             |