Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 508                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 40MHz                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                           |

| Program Memory Size        | 16KB (16K × 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-LQFP                                                      |

| Supplier Device Package    | 44-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08aw16ae0cld |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 2 Pins and Connections**

# 2.3.1 Power ( $V_{DD}$ , 2 x $V_{SS}$ , $V_{DDAD}$ , $V_{SSAD}$ )

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the paired V<sub>DD</sub> and V<sub>SS</sub> power pins as practical to suppress high-frequency noise. The MC9S08AW60 has a second V<sub>SS</sub> pin. This pin should be connected to the system ground plane or to the primary V<sub>SS</sub> pin through a low-impedance connection.

$V_{DDAD}$  and  $V_{SSAD}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the analog power pins as practical to suppress high-frequency noise.

# 2.3.2 Oscillator (XTAL, EXTAL)

Out of reset, the MCU uses an internally generated clock (self-clocked mode —  $f_{Self\_reset}$ ) equivalent to about 8-MHz crystal rate. This frequency source is used during reset startup and can be enabled as the clock source for stop recovery to avoid the need for a long crystal startup delay. This MCU also contains a trimmable internal clock generator (ICG) module that can be used to run the MCU. For more information on the ICG, see the Chapter 8, "Internal Clock Generator (S08ICGV4)."

The oscillator amplitude on XTAL and EXTAL is gain limited for low-power oscillation. Typically, these pins have a 1-V peak-to-peak signal. For noisy environments, the high gain output (HGO) bit can be set to enable rail-to-rail oscillation.

The oscillator in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator in either of two frequency ranges selected by the RANGE bit in the ICGC1 register. Rather than a crystal or ceramic resonator, an external oscillator can be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion.  $R_S$  (when used) and  $R_F$  should be low-inductance resistors such as carbon composition resistors. Wire-wound resistors, and some metal film resistors, have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup and its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2 which are usually the same size. As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

| Lowest <- Pin Function Priority -> Highest |                     |                    | Reference <sup>1</sup>                           |  |

|--------------------------------------------|---------------------|--------------------|--------------------------------------------------|--|

| Port Pins                                  | Alternate Function  | Alternate Function | - Reference                                      |  |

| PTF3-PTF0                                  | TPM1CH5–<br>TPM1CH2 |                    | Chapter 10, "Timer/PWM (S08TPMV2)"               |  |

| PTG4–PTG0                                  | KBI1P4–KBI1P0       |                    | Chapter 9, "Keyboard Interrupt (S08KBIV1)"       |  |

| PTG6–PTG5                                  | EXTAL-XTAL          |                    | Chapter 8, "Internal Clock Generator (S08ICGV4)" |  |

#### Table 2-1. Pin Sharing Priority

See the listed chapter for information about modules that share these pins.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. See the Chapter 6, "Parallel Input/Output" chapter for more details.

Pullup enable bits for each input pin control whether on-chip pullup devices are enabled whenever the pin is acting as an input even if it is being controlled by an on-chip peripheral module. When the PTD7, PTD3, PTD2, and PTG4 pins are controlled by the KBI module and are configured for rising-edge/high-level sensitivity, the pullup enable control bits enable pulldown devices rather than pullup devices.

#### NOTE

When an alternative function is first enabled it is possible to get a spurious edge to the module, user software should clear out any associated flags before interrupts are enabled. Table 2-1 illustrates the priority if multiple modules are enabled. The highest priority module will have control over the pin. Selecting a higher priority pin function with a lower priority function already enabled can cause spurious edges to the lower priority module. It is recommended that all modules that share a pin be disabled before enabling another module.

# NP

#### **Chapter 3 Modes of Operation**

After entering active background mode, the CPU is held in a suspended state waiting for serial background commands rather than executing instructions from the user's application program.

Background commands are of two types:

- Non-intrusive commands, defined as commands that can be issued while the user program is running. Non-intrusive commands can be issued through the BKGD pin while the MCU is in run mode; non-intrusive commands can also be executed when the MCU is in the active background mode. Non-intrusive commands include:

- Memory access commands

- Memory-access-with-status commands

- BDC register access commands

- The BACKGROUND command

- Active background commands, which can only be executed while the MCU is in active background mode. Active background commands include commands to:

- Read or write CPU registers

- Trace one user program instruction at a time

- Leave active background mode to return to the user's application program (GO)

The active background mode is used to program a bootloader or user application program into the FLASH program memory before the MCU is operated in run mode for the first time. When the MC9S08AW60 Series is shipped from the Freescale Semiconductor factory, the FLASH program memory is erased by default unless specifically noted so there is no program that could be executed in run mode until the FLASH memory is initially programmed. The active background mode can also be used to erase and reprogram the FLASH memory after it has been previously programmed.

For additional information about the active background mode, refer to Chapter 15, "Development Support."

### 3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and resumes processing, beginning with the stacking operations leading to the interrupt service routine.

While the MCU is in wait mode, there are some restrictions on which background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode.

# 3.6 Stop Modes

One of two stop modes is entered upon execution of a STOP instruction when the STOPE bit in the system option register is set. In both stop modes, all internal clocks are halted. If the STOPE bit is not set when

### 4.2 Register Addresses and Bit Assignments

The registers in the MC9S08AW60 Series are divided into these three groups:

- Direct-page registers are located in the first 112 locations in the memory map, so they are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located above \$1800 in the memory map. This leaves more room in the direct page for more frequently used registers and variables.

- The nonvolatile register area consists of a block of 16 locations in FLASH memory at \$FFB0-\$FFBF.

Nonvolatile register locations include:

- Three values which are loaded into working registers at reset

- An 8-byte backdoor comparison key which optionally allows a user to gain controlled access to secure memory

- Because the nonvolatile register locations are FLASH memory, they must be erased and programmed like other FLASH memory locations.

Direct-page registers can be accessed with efficient direct addressing mode instructions. Bit manipulation instructions can be used to access any bit in any direct-page register. Table 4-2 is a summary of all user-accessible direct-page registers and control bits.

The direct page registers in Table 4-2 can use the more efficient direct addressing mode which only requires the lower byte of the address. Because of this, the lower byte of the address in column one is shown in bold text. In Table 4-3 and Table 4-4 the whole address in column one is shown in bold. In Table 4-2, Table 4-3, and Table 4-4, the register names in column two are shown in bold to set them apart from the bit names to the right. Cells that are not associated with named bits are shaded. A shaded cell with a 0 indicates this unused bit always reads as a 0. Shaded cells with dashes indicate unused or reserved bit locations that could read as 1s or 0s.

#### **Chapter 4 Memory**

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security" for a detailed description of the security feature.

# 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

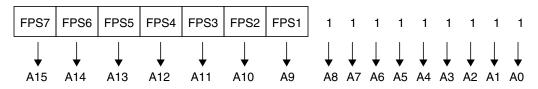

be programmed to logic 0 to enable block protection. Therefore the value \$DE must be programmed into NVPROT to protect addresses \$E000 through \$FFFF.

#### Figure 4-5. Block Protection Mechanism

One use for block protection is to block protect an area of FLASH memory for a bootloader program. This bootloader program then can be used to erase the rest of the FLASH memory and reprogram it. Because the bootloader is protected, it remains intact even if MCU power is lost in the middle of an erase and reprogram operation.

# 4.4.7 Vector Redirection

Whenever any block protection is enabled, the reset and interrupt vectors will be protected. Vector redirection allows users to modify interrupt vector information without unprotecting bootloader and reset vector space. Vector redirection is enabled by programming the FNORED bit in the NVOPT register located at address \$FFBF to zero. For redirection to occur, at least some portion but not all of the FLASH memory must be block protected by programming the NVPROT register located at address \$FFBD. All of the interrupt vectors (memory locations \$FFC0-\$FFFD) are redirected, though the reset vector (\$FFFE:FFFF) is not.

For example, if 512 bytes of FLASH are protected, the protected address region is from \$FE00 through \$FFFF. The interrupt vectors (\$FFC0-\$FFFD) are redirected to the locations \$FDC0-\$FDFD. Now, if an SPI interrupt is taken for instance, the values in the locations \$FDE0:FDE1 are used for the vector instead of the values in the locations \$FFE0:FFE1. This allows the user to reprogram the unprotected portion of the FLASH with new program code including new interrupt vector values while leaving the protected area, which includes the default vector locations, unchanged.

# 4.5 Security

The MC9S08AW60 Series includes circuitry to prevent unauthorized access to the contents of FLASH and RAM memory. When security is engaged, FLASH and RAM are considered secure resources. Direct-page registers, high-page registers, and the background debug controller are considered unsecured resources. Programs executing within secure memory have normal access to any MCU memory locations and resources. Attempts to access a secure memory location with a program executing from an unsecured memory space or through the background debug interface are blocked (writes are ignored and reads return all 0s).

Security is engaged or disengaged based on the state of two nonvolatile register bits (SEC01:SEC00) in the FOPT register. During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into the working FOPT register in high-page register space. A user engages security by programming the NVOPT location which can be done at the same time the FLASH memory is programmed. The 1:0 state disengages security and the other three combinations engage security. Notice the erased state (1:1) makes

### NOTE

The voltage measured on the pulled up IRQ pin may be as low as  $V_{DD} - 0.7$  V. The internal gates connected to this pin are pulled all the way to  $V_{DD}$ . All other pins with enabled pullup resistors will have an unloaded measurement of  $V_{DD}$ .

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In this edge detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

### 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-1 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction, stack the PCL, PCH, X, A, and CCR CPU registers, set the I bit, and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

# 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

# 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

# 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

- 0 = Bit forced to 0

- 1 = Bit forced to 1

- = Bit set or cleared according to results of operation

- U = Undefined after the operation

#### Machine coding notation

- dd = Low-order 8 bits of a direct address 0x0000-0x00FF (high byte assumed to be 0x00)

- ee = Upper 8 bits of 16-bit offset

- ff = Lower 8 bits of 16-bit offset or 8-bit offset

- ii = One byte of immediate data

- jj = High-order byte of a 16-bit immediate data value

- kk = Low-order byte of a 16-bit immediate data value

- hh = High-order byte of 16-bit extended address

- II = Low-order byte of 16-bit extended address

- rr = Relative offset

#### Source form

Everything in the source forms columns, *except expressions in italic characters*, is literal information that must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic is always a literal expression. All commas, pound signs (#), parentheses, and plus signs (+) are literal characters.

- n Any label or expression that evaluates to a single integer in the range 0–7

- opr8i Any label or expression that evaluates to an 8-bit immediate value

- opr16i Any label or expression that evaluates to a 16-bit immediate value

- *opr8a* Any label or expression that evaluates to an 8-bit value. The instruction treats this 8-bit value as the low order 8 bits of an address in the direct page of the 64-Kbyte address space (0x00xx).

- *opr16a* Any label or expression that evaluates to a 16-bit value. The instruction treats this value as an address in the 64-Kbyte address space.

- *oprx8* Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing

- *oprx16* Any label or expression that evaluates to a 16-bit value. Because the HCS08 has a 16-bit address bus, this can be either a signed or an unsigned value.

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the next address after the last byte of object code for the current instruction. The assembler will calculate the 8-bit signed offset and include it in the object code for this instruction.

#### Address modes

- INH = Inherent (no operands)

- IMM = 8-bit or 16-bit immediate

- DIR = 8-bit direct

- EXT = 16-bit extended

MC9S08AW60 Data Sheet, Rev 2

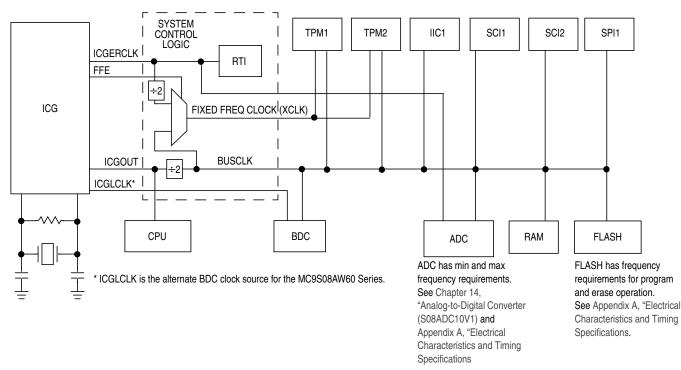

# Chapter 8 Internal Clock Generator (S08ICGV4)

The internal clock generation (ICG) module is used to generate the system clocks for the MC9S08AW60 Series MCU. The analog supply lines  $V_{DDA}$  and  $V_{SSA}$  are internally derived from the MCU's  $V_{DD}$  and  $V_{SS}$  pins. Electrical parametric data for the ICG may be found in Appendix A, "Electrical Characteristics and Timing Specifications."

#### Figure 8-1. System Clock Distribution Diagram

#### NOTE

Freescale Semiconductor recommends that FLASH location \$FFBE be reserved to store a nonvolatile version of ICGTRM. This will allow debugger and programmer vendors to perform a manual trim operation and store the resultant ICGTRM value for users to access at a later time.

Chapter 8 Internal Clock Generator (S08ICGV4)

# 8.4.10 Clock Mode Requirements

A clock mode is requested by writing to CLKS1:CLKS0 and the actual clock mode is indicated by CLKST1:CLKST0. Provided minimum conditions are met, the status shown in CLKST1:CLKST0 should be the same as the requested mode in CLKS1:CLKS0. Table 8-9 shows the relationship between CLKS, CLKST, and ICGOUT. It also shows the conditions for CLKS = CLKST or the reason CLKS  $\neq$  CLKST.

#### NOTE

If a crystal will be used before the next reset, then be sure to set REFS = 1 and CLKS = 1x on the first write to the ICGC1 register. Failure to do so will result in "locking" REFS = 0 which will prevent the oscillator amplifier from being enabled until the next reset occurs.

| Actual<br>Mode<br>(CLKST) | Desired<br>Mode<br>(CLKS) | Range | Reference<br>Frequency<br>(f <sub>REFERENCE</sub> ) | Comparison<br>Cycle Time  | ICGOUT                   | Conditions <sup>1</sup> for<br>CLKS = CLKST | Reason<br>CLKS1 ≠<br>CLKST |

|---------------------------|---------------------------|-------|-----------------------------------------------------|---------------------------|--------------------------|---------------------------------------------|----------------------------|

| Off                       | Off<br>(XX)               | х     | 0                                                   | _                         | 0                        | _                                           | _                          |

| (XX)                      | FBE<br>(10)               | х     | 0                                                   |                           | 0                        | _                                           | ERCS = 0                   |

|                           | SCM<br>(00)               | х     | ficgirclk/7 <sup>2</sup>                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | Not switching<br>from FBE to<br>SCM         | _                          |

| SCM<br>(00)               | FEI<br>(01)               | 0     | f <sub>ICGIRCLK</sub> /7 <sup>(1)</sup>             | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0                   |

| (00)                      | FBE<br>(10)               | х     | ficgirclk/7 <sup>(1)</sup>                          | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | ERCS = 0                   |

|                           | FEE<br>(11)               | х     | f <sub>ICGIRCLK</sub> /7 <sup>(1)</sup>             | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0 or<br>ERCS = 0    |

| FEI                       | FEI<br>(01)               | 0     | f <sub>ICGIRCLK</sub> /7                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | DCOS = 1                                    | —                          |

| (01)                      | FEE<br>(11)               | х     | f <sub>ICGIRCLK</sub> /7                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | ERCS = 0                   |

| FBE<br>(10)               | FBE<br>(10)               | х     | 0                                                   | _                         | ICGERCLK/R               | ERCS = 1                                    | —                          |

|                           | FEE<br>(11)               | х     | 0                                                   | _                         | ICGERCLK/R               | _                                           | LOCS = 1 &<br>ERCS = 1     |

| FEE<br>(11)               | FEE<br>(11)               | 0     | f <sub>ICGERCLK</sub>                               | 2/f <sub>ICGERCLK</sub>   | ICGDCLK/R <sup>3</sup>   | ERCS = 1 and<br>DCOS = 1                    | _                          |

|                           |                           | 1     | ficgerclk                                           | 128/f <sub>ICGERCLK</sub> | ICGDCLK/R <sup>(2)</sup> | ERCS = 1 and<br>DCOS = 1                    | _                          |

#### Table 8-9. ICG State Table

<sup>1</sup> CLKST will not update immediately after a write to CLKS. Several bus cycles are required before CLKST updates to the new value.

<sup>2</sup> The reference frequency has no effect on ICGOUT in SCM, but the reference frequency is still used in making the comparisons that determine the DCOS bit

<sup>3</sup> After initial LOCK; will be ICGDCLK/2R during initial locking process and while FLL is re-locking after the MFD bits are changed.

# Chapter 9 Keyboard Interrupt (S08KBIV1)

# 9.1 Introduction

The MC9S08AW60 Series has one KBI module with eight keyboard interrupt inputs that are shared with port D and port G pins. See Chapter 2, "Pins and Connections," for more information about the logic and hardware aspects of these pins.

# 9.2 Keyboard Pin Sharing

The KBI input KBIP7 shares a common pin with PTD7 and AD15. When KBIP7 is enabled the pin is forced to its input state regardless of the value of the associated port D data direction bit. The port D pullup enable is still used to control the pullup resistor and the pin state can be sensed through a read of the port D data register (this requires that bit 7 of the port D DDR is 0). In the case that the pin is enabled as an ADC input, both the PTD7 and KBIP7 functions are disabled, including the pullup resistor.

The KBI input KBIP6 shares a common pin with PTD3 and AD11, and KBI input KBIP5 shares a common pin with PTD2 and AD10. The sharing of each of these inputs with port and ADC functions operates in the same way as described above for KBIP7.

The KBI inputs KBIP4 – KBIP0 are shared on common pins with PTG4 – PTG0. These pins all operate in the same way as described above for KBIP7 except that none are shared with an ADC input.

KBIP3 – KBIP0 are always falling-edge/low-level sensitive. KBIP7 – KBIP4 can be configured for rising-edge/high-level or for falling-edge/low-level sensitivity. When any of the inputs KBIP7 – KBIP0 are enabled and configured to detect rising edges/high levels, and the pin pullup is enabled through the corresponding port pullup enable bit for that pin, a pulldown resistor rather than a pullup resistor is enabled on the pin.

| PTxPEn<br>(Pull Enable) | PTxDDn<br>(Data Direction) | KBIPEn<br>(KBI Pin Enable) | KBEDGn<br>(KBI Edge Select) | Pullup   | Pulldown |

|-------------------------|----------------------------|----------------------------|-----------------------------|----------|----------|

| 0                       | 0                          | 0                          | x <sup>1</sup>              | disabled | disabled |

| 1                       | 0                          | 0                          | х                           | enabled  | disabled |

| x                       | 1                          | 0                          | х                           | disabled | disabled |

| 1                       | x                          | 1                          | 0                           | enabled  | disabled |

| 1                       | x                          | 1                          | 1                           | disabled | enabled  |

| 0                       | x                          | 1                          | х                           | disabled | disabled |

1 x = Don't care

# Chapter 10 Timer/PWM (S08TPMV2)

# 10.1 Introduction

The MC9S08AW60 Series includes two independent timer/PWM (TPM) modules which support traditional input capture, output compare, or buffered edge-aligned pulse-width modulation (PWM) on each channel. A control bit in each TPM configures all channels in that timer to operate as center-aligned PWM functions. In each of these two TPMs, timing functions are based on a separate 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications, and the center-aligned PWM capability on the 3-channel TPM extends the field of applications to motor control in small appliances.

The use of the fixed system clock, XCLK, as the clock source for either of the TPM modules allows the TPM prescaler to run using the oscillator rate divided by two (ICGERCLK/2). This option is only available if the ICG is configured in FEE mode and the proper conditions are met (see Section 8.4.11, "Fixed Frequency Clock"). In all other ICG modes this selection is redundant because XCLK is the same as BUSCLK.

# 10.2 Features

The timer system in the MC9S08AW60 Series includes a 6-channel TPM1 and a separate 2-channel TPM2. Timer system features include:

- A total of eight channels:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock source to prescaler for each TPM is independently selectable as bus clock, fixed system clock, or an external pin:

- Prescale taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- External clock inputs TPM1CLK for TPM1 and TPM2CLK for TPM2 (only available in 64-pin package)

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module

#### MC9S08AW60 Data Sheet, Rev 2

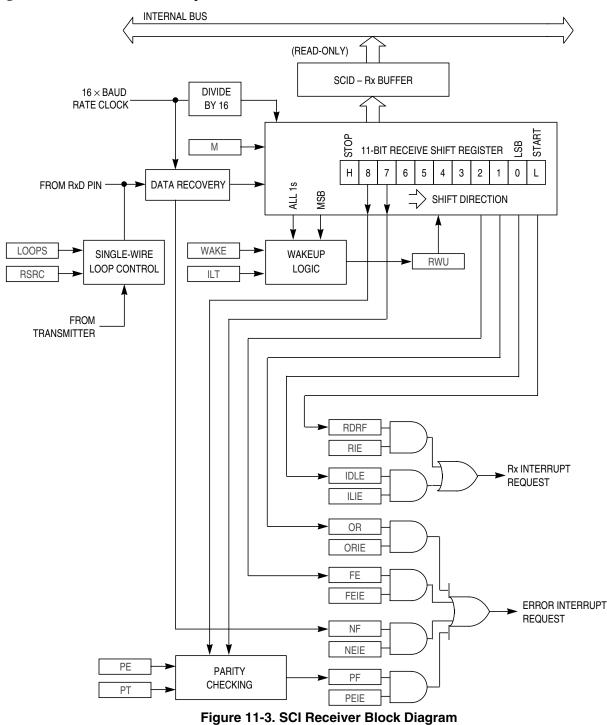

Figure 11-3 shows the receiver portion of the SCI.

### 11.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Chapter 13 Inter-Integrated Circuit (S08IICV1)

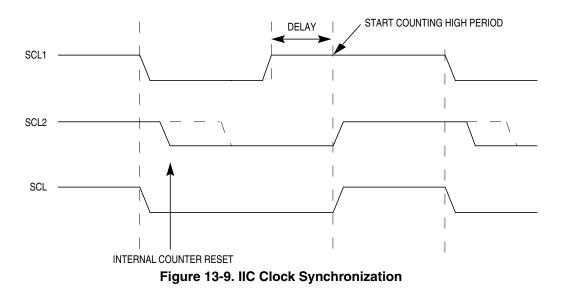

#### 13.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 13.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

# 13.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

# 13.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 13-7 occur provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a one to it in the interrupt routine. The user can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

| Table 13-7. Interrupt Summary |

|-------------------------------|

|-------------------------------|

### 14.5.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

#### NOTE

It is possible for the ADC module to wake the system from low power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software should ensure that the data transfer blocking mechanism (discussed in Section 14.5.4.2, "Completing Conversions) is cleared when entering stop3 and continuing ADC conversions.

### 14.5.8 MCU Stop1 and Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters either stop1 or stop2 mode. All module registers contain their reset values following exit from stop1 or stop2. Therefore the module must be re-enabled and re-configured following exit from stop1 or stop2.

# 14.6 Initialization Information

This section gives an example which provides some basic direction on how a user would initialize and configure the ADC module. The user has the flexibility of choosing between configuring the module for 8-bit or 10-bit resolution, single or continuous conversion, and a polled or interrupt approach, among many other options. Refer to Table 14-6, Table 14-7, and Table 14-8 for information used in this example.

#### NOTE

Hexadecimal values designated by a preceding 0x, binary values designated by a preceding %, and decimal values have no preceding character.

### 14.6.1 ADC Module Initialization Example

#### 14.6.1.1 Initialization Sequence

Before the ADC module can be used to complete conversions, an initialization procedure must be performed. A typical sequence is as follows:

1. Update the configuration register (ADCCFG) to select the input clock source and the divide ratio used to generate the internal clock, ADCK. This register is also used for selecting sample time and low-power configuration.

**Chapter 15 Development Support**

# 15.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 15-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 15-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

#### **Chapter 15 Development Support**

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 15.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

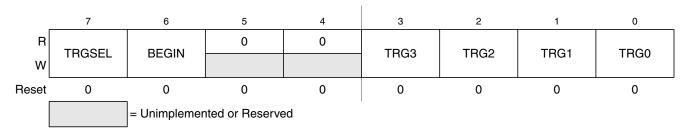

### 15.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

#### Figure 15-8. Debug Trigger Register (DBGT)

#### Table 15-5. DBGT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TRGSEL     | <ul> <li>Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.</li> <li>0 Trigger on access to compare address (force)</li> <li>1 Trigger if opcode at compare address is executed (tag)</li> </ul> |

| 6<br>BEGIN      | <ul> <li>Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.</li> <li>Data stored in FIFO until trigger (end trace)</li> <li>Trigger initiates data storage (begin trace)</li> </ul>                                                                                                                 |

| 3:0<br>TRG[3:0] | Select Trigger Mode — Selects one of nine triggering modes, as described below.0000 A-only0001 A OR B0010 A Then B0011 Event-only B (store data)0100 A then event-only B (store data)0101 A AND B data (full mode)0110 A AND NOT B data (full mode)0111 Inside range: $A \leq address \leq B$ 1000 Outside range: address < A or address > B1001 - 1111 (No trigger)                                                                                                                                                 |

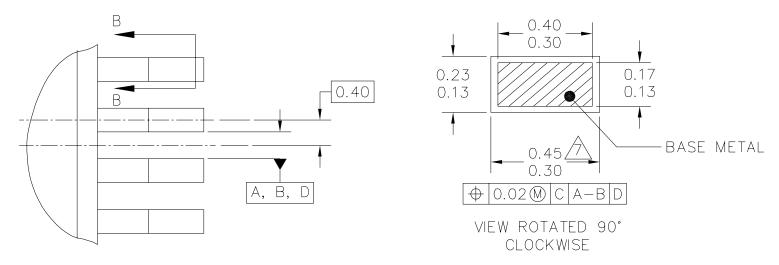

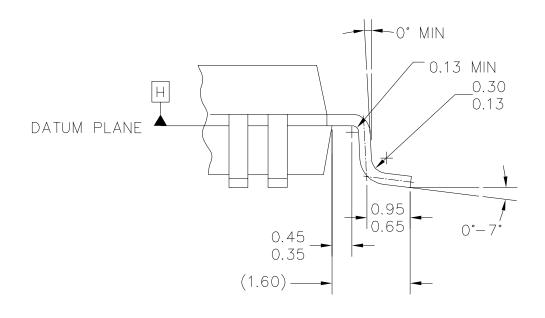

DETAIL "A"

SECTION B-B

DETAIL "C"

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |     | L OUTLINE    | OUTLINE PRINT VERSION NOT TO SCA |             |

|---------------------------------------------------------|-----|--------------|----------------------------------|-------------|

| TITLE:                                                  |     | DOCUMENT NE  | ]: 98ASB42844B                   | RE∨: B      |

| 64LD QFP (14 X                                          | 14) | CASE NUMBER  | 2: 840B-01                       | 20 MAY 2005 |

|                                                         |     | STANDARD: NE | IN-JEDEC                         |             |