#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | S08                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 40MHz                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-LQFP                                                      |

| Supplier Device Package    | 44-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08aw16ae0mld |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| Part Number   | Package Description | Original (gold wire)<br>package document number | Current (copper wire)<br>package document number |

|---------------|---------------------|-------------------------------------------------|--------------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                     | 98ASA00466D                                      |

| MC9S08AC16    |                     |                                                 |                                                  |

| MC9S908AC60   |                     |                                                 |                                                  |

| MC9S08AC128   |                     |                                                 |                                                  |

| MC9S08AW60    |                     |                                                 |                                                  |

| MC9S08GB60A   |                     |                                                 |                                                  |

| MC9S08GT16A   |                     |                                                 |                                                  |

| MC9S08JM16    |                     |                                                 |                                                  |

| MC9S08JM60    |                     |                                                 |                                                  |

| MC9S08LL16    |                     |                                                 |                                                  |

| MC9S08QE128   |                     |                                                 |                                                  |

| MC9S08QE32    |                     |                                                 |                                                  |

| MC9S08RG60    |                     |                                                 |                                                  |

| MCF51CN128    |                     |                                                 |                                                  |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                     | 98ASA00466D                                      |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                     | 98ASA00473D                                      |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                     | 98ASA00473D                                      |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                     | 98ASA00736D                                      |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                     | 98ASA00734D                                      |

| MC9S08QB8     |                     |                                                 |                                                  |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                     | 98ASA00474D                                      |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                     | 98ASA00474D                                      |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                     | 98ASA00602D                                      |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                     | 98ASA00671D                                      |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                     | 98ASA00672D                                      |

| MC9S08QG8     |                     |                                                 |                                                  |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                     | 98ASA00735D                                      |

# **Section Number**

Title

### Page

| 4.4 | FLASH    |                                              | 50 |

|-----|----------|----------------------------------------------|----|

|     | 4.4.1    | Features                                     | 51 |

|     | 4.4.2    | Program and Erase Times                      |    |

|     | 4.4.3    | Program and Erase Command Execution          | 52 |

|     | 4.4.4    | Burst Program Execution                      |    |

|     | 4.4.5    | Access Errors                                | 55 |

|     | 4.4.6    | FLASH Block Protection                       | 55 |

|     | 4.4.7    | Vector Redirection                           | 56 |

| 4.5 | Security |                                              | 56 |

| 4.6 | FLASH    | Registers and Control Bits                   | 58 |

|     | 4.6.1    | FLASH Clock Divider Register (FCDIV)         |    |

|     | 4.6.2    | FLASH Options Register (FOPT and NVOPT)      | 59 |

|     | 4.6.3    | FLASH Configuration Register (FCNFG)         | 60 |

|     | 4.6.4    | FLASH Protection Register (FPROT and NVPROT) |    |

|     | 4.6.5    | FLASH Status Register (FSTAT)                | 61 |

|     | 4.6.6    | FLASH Command Register (FCMD)                | 63 |

|     |          |                                              |    |

# Chapter 5 Resets, Interrupts, and System Configuration

| 5.1 | Introduc  | tion                                                            | 65 |

|-----|-----------|-----------------------------------------------------------------|----|

| 5.2 | Features  |                                                                 | 65 |

| 5.3 | MCU Re    | eset                                                            | 65 |

| 5.4 | Compute   | er Operating Properly (COP) Watchdog                            | 66 |

| 5.5 | Interrupt | ts                                                              | 66 |

|     | 5.5.1     | Interrupt Stack Frame                                           | 67 |

|     | 5.5.2     | External Interrupt Request (IRQ) Pin                            | 68 |

|     | 5.5.3     | Interrupt Vectors, Sources, and Local Masks                     | 69 |

| 5.6 | Low-Vol   | ltage Detect (LVD) System                                       |    |

|     | 5.6.1     | Power-On Reset Operation                                        | 71 |

|     | 5.6.2     | LVD Reset Operation                                             | 71 |

|     | 5.6.3     | LVD Interrupt Operation                                         |    |

|     | 5.6.4     | Low-Voltage Warning (LVW)                                       |    |

| 5.7 |           | ne Interrupt (RTI)                                              |    |

| 5.8 |           | Output                                                          |    |

| 5.9 | Reset, In | terrupt, and System Control Registers and Control Bits          | 72 |

|     | 5.9.1     | Interrupt Pin Request Status and Control Register (IRQSC)       |    |

|     | 5.9.2     | System Reset Status Register (SRS)                              | 74 |

|     | 5.9.3     | System Background Debug Force Reset Register (SBDFR)            | 75 |

|     | 5.9.4     | System Options Register (SOPT)                                  |    |

|     | 5.9.5     | System MCLK Control Register (SMCLK)                            | 76 |

|     | 5.9.6     | System Device Identification Register (SDIDH, SDIDL)            |    |

|     | 5.9.7     | System Real-Time Interrupt Status and Control Register (SRTISC) | 78 |

|     |           |                                                                 |    |

# **Section Number**

### Title

### Page

|     | 8.4.4      | FLL Engaged Internal Unlocked                                     | 143 |

|-----|------------|-------------------------------------------------------------------|-----|

|     | 8.4.5      | FLL Engaged Internal Locked                                       | 143 |

|     | 8.4.6      | FLL Bypassed, External Clock (FBE) Mode                           | 143 |

|     | 8.4.7      | FLL Engaged, External Clock (FEE) Mode                            | 143 |

|     | 8.4.8      | FLL Lock and Loss-of-Lock Detection                               |     |

|     | 8.4.9      | FLL Loss-of-Clock Detection                                       | 145 |

|     | 8.4.10     | Clock Mode Requirements                                           |     |

|     | 8.4.11     | Fixed Frequency Clock                                             |     |

|     | 8.4.12     | High Gain Oscillator                                              |     |

| 8.5 | Initializa | tion/Application Information                                      |     |

|     | 8.5.1      | Introduction                                                      | 147 |

|     | 8.5.2      | Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz   |     |

|     | 8.5.3      | Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz      |     |

|     | 8.5.4      | Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency |     |

|     | 8.5.5      | Example #4: Internal Clock Generator Trim                         |     |

|     |            | 1                                                                 |     |

# Chapter 9 Keyboard Interrupt (S08KBIV1)

| 9.1 | Introduct  | ion                                      | 157 |

|-----|------------|------------------------------------------|-----|

| 9.2 | Keyboard   | l Pin Sharing                            | 157 |

|     |            | ~                                        |     |

|     | 9.3.1      | KBI Block Diagram                        | 160 |

| 9.4 | Register 1 | Definition                               | 160 |

|     | 9.4.1      | KBI Status and Control Register (KBI1SC) | 161 |

|     | 9.4.2      | KBI Pin Enable Register (KBI1PE)         | 162 |

| 9.5 | Function   | al Description                           | 162 |

|     | 9.5.1      | Pin Enables                              | 162 |

|     | 9.5.2      | Edge and Level Sensitivity               | 162 |

|     | 9.5.3      | KBI Interrupt Controls                   | 163 |

|     |            |                                          |     |

# Chapter 10 Timer/PWM (S08TPMV2)

| 10.1 | Introduct | tion                                          | 165 |

|------|-----------|-----------------------------------------------|-----|

| 10.2 | Features  |                                               | 165 |

|      | 10.2.1    | Features                                      | 167 |

|      | 10.2.2    | Block Diagram                                 | 167 |

| 10.3 | External  | Signal Description                            | 169 |

|      | 10.3.1    | External TPM Clock Sources                    | 169 |

|      | 10.3.2    | TPMxCHn — TPMx Channel n I/O Pins             | 169 |

| 10.4 | Register  | Definition                                    | 169 |

|      | 10.4.1    | Timer x Status and Control Register (TPMxSC)  | 170 |

|      | 10.4.2    | Timer x Counter Registers (TPMxCNTH:TPMxCNTL) | 171 |

|      |           |                                               |     |

MC9S08AW60 Data Sheet, Rev 2

# NP

Chapter 1 Introduction

- The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop sub-module

- Control bits inside the ICG determine which source is connected.

- FFE is a control signal generated inside the ICG. If the frequency of ICGOUT > 4 × the frequency of ICGERCLK, this signal is a logic 1 and the fixed-frequency clock will be ICGERCLK/2. Otherwise the fixed-frequency clock will be BUSCLK.

- ICGLCLK Development tools can select this internal self-clocked source (~ 8 MHz) to speed up BDC communications in systems where the bus clock is slow.

- ICGERCLK External reference clock can be selected as the real-time interrupt clock source. Can also be used as the ALTCLK input to the ADC module.

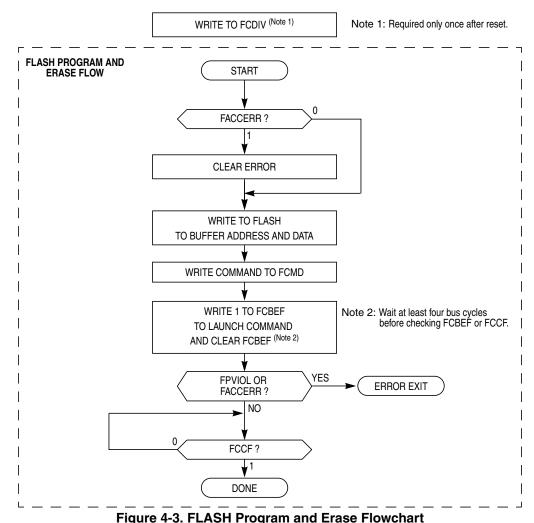

### 4.4.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

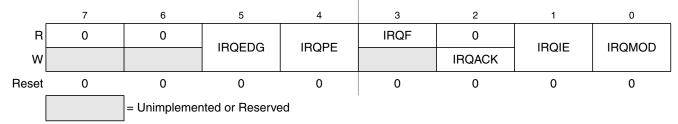

### 5.9.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes two unimplemented bits which always read 0, four read/write bits, one read-only status bit, and one write-only bit. These bits are used to configure the IRQ function, report status, and acknowledge IRQ events.

#### Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

#### Table 5-2. IRQSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>IRQEDG | <ul> <li>Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured to detect rising edges, the optional pullup resistor is re-configured as an optional pulldown resistor.</li> <li>IRQ is falling edge or falling edge/low-level sensitive.</li> </ul> |

| 4<br>IRQPE  | <ul> <li>IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set the IRQ pin can be used as an interrupt request. Also, when this bit is set, either an internal pull-up or an internal pull-down resistor is enabled depending on the state of the IRQEDG bit.</li> <li>IRQ pin function is disabled.</li> <li>IRQ pin function is enabled.</li> </ul>                                                                                                                                       |

| 3<br>IRQF   | <ul> <li>IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.</li> <li>0 No IRQ request.</li> <li>1 IRQ event detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 2<br>IRQACK | <b>IRQ Acknowledge</b> — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF). Writing 0 has no meaning or effect. Reads always return logic 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF cannot be cleared while the IRQ pin remains at its asserted level.                                                                                                                                                                                                                  |

| 1<br>IRQIE  | <ul> <li>IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate a hardware interrupt request.</li> <li>0 Hardware interrupt requests from IRQF disabled (use polling).</li> <li>1 Hardware interrupt requested whenever IRQF = 1.</li> </ul>                                                                                                                                                                                                                                                       |

| 0<br>IRQMOD | <ul> <li>IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt request events. See Section 5.5.2.2, "Edge and Level Sensitivity" for more details.</li> <li>IRQ event on falling edges or rising edges only.</li> <li>IRQ event on falling edges and low levels or on rising edges and high levels.</li> </ul>                                                           |

Chapter 5 Resets, Interrupts, and System Configuration

# 5.9.2 System Reset Status Register (SRS)

This register includes seven read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

|           | 7   | 6   | 5               | 4            | 3              | 2              | 1    | 0 |

|-----------|-----|-----|-----------------|--------------|----------------|----------------|------|---|

| R         | POR | PIN | COP             | ILOP         | 0              | ICG            | LVD  | 0 |

| w         |     | Wr  | iting any value | to SIMRS add | ress clears CO | P watchdog tin | ner. |   |

| POR       | 1   | 0   | 0               | 0            | 0              | 0              | 1    | 0 |

| LVR:      | U   | 0   | 0               | 0            | 0              | 0              | 1    | 0 |

| Any other | 0   | (1) | (1)             | (1)          | 0              | (1)            | 0    | 0 |

reset:

U = Unaffected by reset

<sup>1</sup> Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                     |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                             |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source may be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                                 |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

#### Chapter 5 Resets, Interrupts, and System Configuration

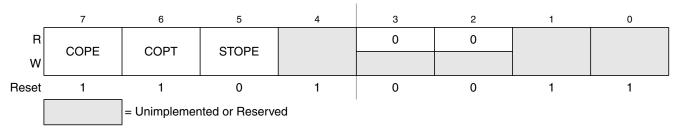

#### Figure 5-5. System Options Register (SOPT)

#### Table 5-5. SOPT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPE  | <ul> <li>COP Watchdog Enable — This write-once bit defaults to 1 after reset.</li> <li>0 COP watchdog timer disabled.</li> <li>1 COP watchdog timer enabled (force reset on timeout).</li> </ul>                                                                                                    |

| 6<br>COPT  | <ul> <li>COP Watchdog Timeout — This write-once bit defaults to 1 after reset.</li> <li>0 Short timeout period selected (2<sup>13</sup> cycles of BUSCLK).</li> <li>1 Long timeout period selected (2<sup>18</sup> cycles of BUSCLK).</li> </ul>                                                    |

| 5<br>STOPE | <ul> <li>Stop Mode Enable — This write-once bit defaults to 0 after reset, which disables stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul> |

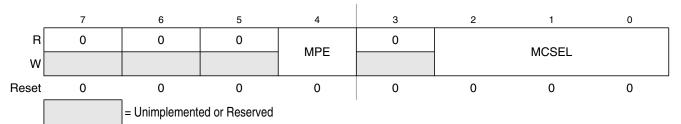

### 5.9.5 System MCLK Control Register (SMCLK)

This register is used to control the MCLK clock output.

#### Figure 5-6. System MCLK Control Register (SMCLK)

#### Table 5-6. SMCLK Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MPE     | <ul> <li>MCLK Pin Enable — This bit is used to enable the MCLK function.</li> <li>0 MCLK output disabled.</li> <li>1 MCLK output enabled on PTC2 pin.</li> </ul>                                                                                                                     |

| 2:0<br>MCSEL | <b>MCLK Divide Select</b> — These bits are used to select the divide ratio for the MCLK output according to the formula below when the MCSEL bits are not equal to all zeroes. In the case that the MCSEL bits are all zero and MPE is set, the pin is driven low. See Equation 5-1. |

#### MCLK frequency = Bus Clock frequency ÷ (2 \* MCSEL)

Eqn. 5-1

MC9S08AW60 Data Sheet, Rev 2

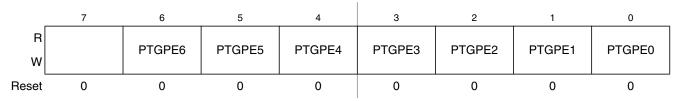

# 6.7.14 Port G Pin Control Registers (PTGPE, PTGSE, PTGDS)

In addition to the I/O control, port G pins are controlled by the registers listed below.

Figure 6-41. Internal Pullup Enable for Port G Bits (PTGPE)

| Table 6-34. PTGPE Register Fiel | Id Descriptions |

|---------------------------------|-----------------|

|---------------------------------|-----------------|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGPE[6:0] | <ul> <li>Internal Pullup Enable for Port G Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTG pin. For port G pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port G bit n.</li> <li>1 Internal pullup device enabled for port G bit n.</li> </ul> |

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     |   | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| w     |   | TTUSED | TTUSES | 110324 | TIGSES | TTUSEZ | TIUSET | TIGGEO |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-42. Output Slew Rate Control Enable for Port G Bits (PTGSE)

#### Table 6-35. PTGSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGSE[6:0] | <ul> <li>Output Slew Rate Control Enable for Port G Bits— Each of these control bits determine whether output slew rate control is enabled for the associated PTG pin. For port G pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port G bit n.</li> <li>1 Output slew rate control enabled for port G bit n.</li> </ul> |

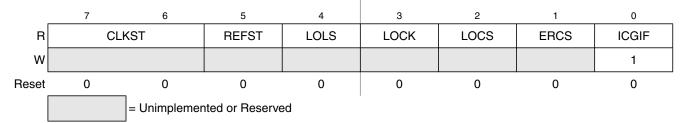

# 8.3.3 ICG Status Register 1 (ICGS1)

#### Figure 8-8. ICG Status Register 1 (ICGS1)

| Table 8-3. ICGS1 | <b>Register Field</b> | I Descriptions |

|------------------|-----------------------|----------------|

|------------------|-----------------------|----------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKST | Clock Mode Status — The CLKST bits indicate the current clock mode. The CLKST bits don't update<br>immediately after a write to the CLKS bits due to internal synchronization between clock domains.<br>00 Self-clocked<br>01 FLL engaged, internal reference<br>10 FLL bypassed, external reference<br>11 FLL engaged, external reference                                                                                                                                                                                                                                      |

| 5<br>REFST   | Reference Clock Status — The REFST bit indicates which clock reference is currently selected by the Reference Select circuit.         0       External Clock selected.         1       Crystal/Resonator selected.                                                                                                                                                                                                                                                                                                                                                              |

| 4<br>LOLS    | <ul> <li>FLL Loss of Lock Status — The LOLS bit is an indication of FLL lock status.</li> <li>FLL has not unexpectedly lost lock since LOLS was last cleared.</li> <li>FLL has unexpectedly lost lock since LOLS was last cleared, LOLRE determines action taken.</li> </ul>                                                                                                                                                                                                                                                                                                    |

| 3<br>LOCK    | FLL Lock Status — The LOCK bit indicates whether the FLL has acquired lock. The LOCK bit is cleared in off, self-clocked, and FLL bypassed modes.         0       FLL is currently unlocked.         1       FLL is currently locked.                                                                                                                                                                                                                                                                                                                                           |

| 2<br>LOCS    | <ul> <li>Loss Of Clock Status — The LOCS bit is an indication of ICG loss of clock status.</li> <li>ICG has not lost clock since LOCS was last cleared.</li> <li>ICG has lost clock since LOCS was last cleared, LOCRE determines action taken.</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| 1<br>ERCS    | External Reference Clock Status — The ERCS bit is an indication of whether or not the external referenceclock (ICGERCLK) meets the minimum frequency requirement.0External reference clock is not stable, frequency requirement is not met.1External reference clock is stable, frequency requirement is met.                                                                                                                                                                                                                                                                   |

| 0<br>ICGIF   | <ul> <li>ICG Interrupt Flag — The ICGIF read/write flag is set when an ICG interrupt request is pending. It is cleared by a reset or by reading the ICG status register when ICGIF is set and then writing a logic 1 to ICGIF. If another ICG interrupt occurs before the clearing sequence is complete, the sequence is reset so ICGIF would remain set after the clear sequence was completed for the earlier interrupt. Writing a logic 0 to ICGIF has no effect.</li> <li>0 No ICG interrupt request is pending.</li> <li>1 An ICG interrupt request is pending.</li> </ul> |

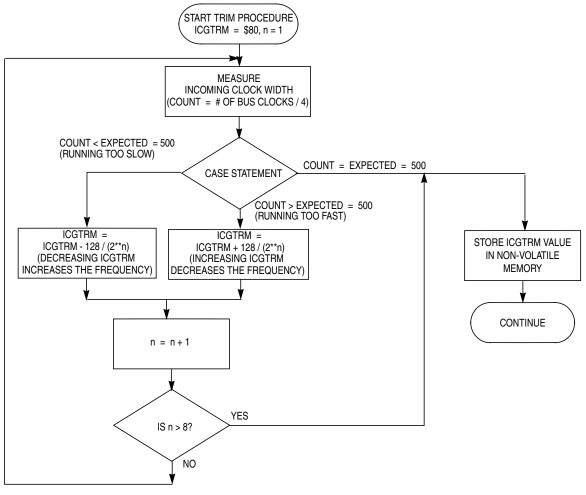

### 8.5.5 Example #4: Internal Clock Generator Trim

The internally generated clock source is guaranteed to have a period  $\pm 25\%$  of the nominal value. In some cases, this may be sufficient accuracy. For other applications that require a tight frequency tolerance, a trimming procedure is provided that will allow a very accurate source. This section outlines one example of trimming the internal oscillator. Many other possible trimming procedures are valid and can be used.

Initial conditions:

- 1) Clock supplied from ATE has 500  $\mu sec$  duty period

- 2) ICG configured for internal reference with 4 MHz bus

Figure 8-17. Trim Procedure

In this particular case, the MCU has been attached to a PCB and the entire assembly is undergoing final test with automated test equipment. A separate signal or message is provided to the MCU operating under user provided software control. The MCU initiates a trim procedure as outlined in Figure 8-17 while the tester supplies a precision reference signal.

If the intended bus frequency is near the maximum allowed for the device, it is recommended to trim using a reduction divisor (R) twice the final value. After the trim procedure is complete, the reduction divisor can be restored. This will prevent accidental overshoot of the maximum clock frequency.

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input      |

|-------------|------------------------------------------|

| 0:0         | No clock selected (TPMx disabled)        |

| 0:1         | Bus rate clock (BUSCLK)                  |

| 1:0         | Fixed system clock (XCLK)                |

| 1:1         | External source (TPMxCLK) <sup>1,2</sup> |

#### Table 10-2. TPM Clock Source Selection

<sup>1</sup> The maximum frequency that is allowed as an external clock is one-fourth of the bus frequency.

<sup>2</sup> If the external clock input is shared with channel n and is selected as the TPM clock source, the corresponding ELSnB:ELSnA control bits should be set to 0:0 so channel n does not try to use the same pin for a conflicting function.

| PS2:PS1:PS0 | TPM Clock Source Divided-By |

|-------------|-----------------------------|

| 0:0:0       | 1                           |

| 0:0:1       | 2                           |

| 0:1:0       | 4                           |

| 0:1:1       | 8                           |

| 1:0:0       | 16                          |

| 1:0:1       | 32                          |

| 1:1:0       | 64                          |

| 1:1:1       | 128                         |

Table 10-3. Prescale Divisor Selection

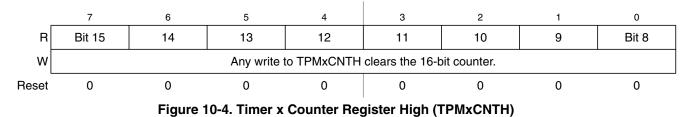

### **10.4.2** Timer x Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This allows coherent 16-bit reads in either order. The coherency mechanism is automatically restarted by an MCU reset, a write of any value to TPMxCNTH or TPMxCNTL, or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers.

Chapter 12 Serial Peripheral Interface (S08SPIV3)

# 12.1 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

# 12.1.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

# 12.1.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 12.1.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 12.1.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

#### Table 12-3. SPI1C2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MODFEN  | <ul> <li>Master Mode-Fault Function Enable — When the SPI is configured for slave mode, this bit has no meaning or effect. (The SS pin is the slave select input.) In master mode, this bit determines how the SS pin is used (refer to Table 12-2 for more details).</li> <li>Mode fault function disabled, master SS pin reverts to general-purpose I/O not controlled by SPI</li> <li>Mode fault function enabled, master SS pin acts as the mode fault input or the slave select output</li> </ul>                                                       |

| 3<br>BIDIROE | <b>Bidirectional Mode Output Enable</b> — When bidirectional mode is enabled by SPI pin control 0 (SPC0) = 1,<br>BIDIROE determines whether the SPI data output driver is enabled to the single bidirectional SPI I/O pin.<br>Depending on whether the SPI is configured as a master or a slave, it uses either the MOSI (MOMI) or MISO<br>(SISO) pin, respectively, as the single SPI data I/O pin. When SPC0 = 0, BIDIROE has no meaning or effect.<br>0 Output driver disabled so SPI data I/O pin acts as an input<br>1 SPI I/O pin enabled as an output |

| 1<br>SPISWAI | SPI Stop in Wait Mode         0 SPI clocks continue to operate in wait mode         1 SPI clocks stop when the MCU enters wait mode                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>SPC0    | <ul> <li>SPI Pin Control 0 — The SPC0 bit chooses single-wire bidirectional mode. If MSTR = 0 (slave mode), the SPI uses the MISO (SISO) pin for bidirectional SPI data transfers. If MSTR = 1 (master mode), the SPI uses the MOSI (MOMI) pin for bidirectional SPI data transfers. When SPC0 = 1, BIDIROE is used to enable or disable the output driver for the single bidirectional SPI I/O pin.</li> <li>O SPI uses separate pins for data input and data output</li> <li>1 SPI configured for single-wire bidirectional operation</li> </ul>           |

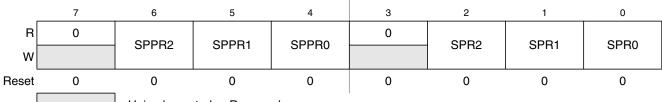

### 12.3.3 SPI Baud Rate Register (SPI1BR)

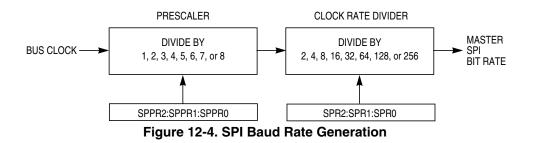

This register is used to set the prescaler and bit rate divisor for an SPI master. This register may be read or written at any time.

= Unimplemented or Reserved

#### Figure 12-7. SPI Baud Rate Register (SPI1BR)

#### Table 12-4. SPI1BR Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4<br>SPPR[2:0] | <b>SPI Baud Rate Prescale Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate prescaler as shown in Table 12-5. The input to this prescaler is the bus rate clock (BUSCLK). The output of this prescaler drives the input of the SPI baud rate divider (see Figure 12-4). |

| 2:0<br>SPR[2:0]  | <b>SPI Baud Rate Divisor</b> — This 3-bit field selects one of eight divisors for the SPI baud rate divider as shown in Table 12-6. The input to this divider comes from the SPI baud rate prescaler (see Figure 12-4). The output of this divider is the SPI bit rate clock for master mode.            |

### 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

### 13.1.2 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop2 will reset the register contents.

# 14.3.1 Analog Power (V<sub>DDAD</sub>)

The ADC analog portion uses  $V_{DDAD}$  as its power connection. In some packages,  $V_{DDAD}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDAD}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDAD}$  for good results.

### 14.3.2 Analog Ground (V<sub>SSAD</sub>)

The ADC analog portion uses  $V_{SSAD}$  as its ground connection. In some packages,  $V_{SSAD}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSAD}$  pin to the same voltage potential as  $V_{SS}$ .

### 14.3.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDAD}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ).

### 14.3.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSAD}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSAD}$ .

### 14.3.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

# 14.4 Register Definition

These memory mapped registers control and monitor operation of the ADC:

- Status and control register, ADC1SC1

- Status and control register, ADC1SC2

- Data result registers, ADC1RH and ADC1RL

- Compare value registers, ADC1CVH and ADC1CVL

- Configuration register, ADC1CFG

- Pin enable registers, APCTL1, APCTL2, APCTL3

### 14.4.1 Status and Control Register 1 (ADC1SC1)

This section describes the function of the ADC status and control register (ADC1SC1). Writing ADC1SC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

# Chapter 15 Development Support

# 15.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

The alternate BDC clock source for MC9S08AW60 Series is the ICGLCLK. See Chapter 8, "Internal Clock Generator (S08ICGV4)" for more information about ICGCLK and how to select clock sources.

#### Appendix A Electrical Characteristics and Timing Specifications

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2 \qquad \qquad Eqn. A-3$$

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

# A.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model               | Description                 | Symbol | Value | Unit |

|---------------------|-----------------------------|--------|-------|------|

|                     | Series Resistance           | R1     | 1500  | Ω    |

| Human Body<br>Model | Storage Capacitance         | С      | 100   | pF   |

|                     | Number of Pulse per pin     | _      | 3     |      |

|                     | Series Resistance           | R1     | 0     | Ω    |

| Machine Model       | Storage Capacitance         | С      | 200   | pF   |

|                     | Number of Pulse per pin     | —      | 3     |      |

| Latch-Up            | Minimum input voltage limit |        | -2.5  | V    |

|                     | Maximum input voltage limit |        | 7.5   | V    |

Table A-4. ESD and Latch-up Test Conditions

| Table A-5. | ESD and | Latch-Up | Protection | Characteristics |

|------------|---------|----------|------------|-----------------|

|------------|---------|----------|------------|-----------------|

| Num | С | Rating                                     | Symbol           | Min    | Мах | Unit |

|-----|---|--------------------------------------------|------------------|--------|-----|------|

| 1   | С | Human Body Model (HBM)                     | V <sub>HBM</sub> | ± 2000 | _   | V    |

| 2   | С | Machine Model (MM)                         | V <sub>MM</sub>  | ± 200  | _   | V    |

| 3   | С | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ± 500  | _   | V    |

| 4   | С | Latch-up Current at T <sub>A</sub> = 125°C | I <sub>LAT</sub> | ± 100  | _   | mA   |

| Num | С | Parameter                                                                                                                                                                                                                        | Symbol             | Min              | Typ <sup>1</sup> | Max                 | Unit                 |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|---------------------|----------------------|

| 9   | Р | High Impedance (off-state) leakage current <sup>2</sup>                                                                                                                                                                          | I <sub>OZ</sub>    |                  | 0.01             | 1                   | μA                   |

| 10  | Ρ | Internal pullup resistors <sup>3</sup>                                                                                                                                                                                           | R <sub>PU</sub>    | 20               | 45               | 65                  | kΩ                   |

| 11  | Ρ | Internal pulldown resistors <sup>4</sup>                                                                                                                                                                                         | R <sub>PD</sub>    | 20               | 45               | 65                  | kΩ                   |

| 12  | С | Input Capacitance; all non-supply pins                                                                                                                                                                                           | C <sub>In</sub>    | _                | —                | 8                   | pF                   |

| 13  | Ρ | POR rearm voltage                                                                                                                                                                                                                | V <sub>POR</sub>   | 0.9              | 1.4              | 2.0                 | V                    |

| 14  | D | POR rearm time                                                                                                                                                                                                                   | t <sub>POR</sub>   | 10               | —                |                     | μs                   |

| 15  | Ρ | Low-voltage detection threshold — high range $V_{DD}$ falling $V_{DD}$ rising                                                                                                                                                    | V <sub>LVDH</sub>  | 4.2<br>4.3       | 4.3<br>4.4       | 4.4<br>4.5          | v                    |

| 16  | Р | Low-voltage detection threshold — low range $V_{DD}$ falling $V_{DD}$ rising                                                                                                                                                     | V <sub>LVDL</sub>  | 2.48<br>2.54     | 2.56<br>2.62     | 2.64<br>2.7         | v                    |

| 17  | Р | Low-voltage warning threshold — high range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                                                                  | V <sub>LVWH</sub>  | 4.2<br>4.3       | 4.3<br>4.4       | 4.4<br>4.5          | v                    |

| 18  | Р | Low-voltage warning threshold — low range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                                                                   | V <sub>LVWL</sub>  | 2.48<br>2.54     | 2.56<br>2.62     | 2.64<br>2.7         | v                    |

| 19  | Р | Low-voltage inhibit reset/recover hysteresis<br>5V<br>3V                                                                                                                                                                         | V <sub>hys</sub>   |                  | 100<br>60        | _                   | mV                   |

| 20  | Ρ | Bandgap Voltage Reference<br>Factory trimmed at<br>V <sub>DD</sub> = 5.0 V<br>Temp = 25 °C                                                                                                                                       | V <sub>BG</sub>    | 1.185            | 1.20             | 1.215               | V                    |

| 21  | D | dc injection current <sup>5, 6, 7, 8</sup><br>DC Injection Current<br>Single pin limit<br>$V_{IN} > V_{DD}$<br>$V_{IN} < V_{SS}$<br>Total MCU limit, includes sum of all stressed pins<br>$V_{IN} > V_{DD}$<br>$V_{IN} < V_{SS}$ | lI <sub>IC</sub> I | 0<br>0<br>0<br>0 | -<br>-<br>-      | 2<br>0.2<br>25<br>5 | mA<br>mA<br>mA<br>mA |

Table A-7. DC Characteristics (continued)

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated.

- <sup>2</sup> Measured with  $V_{In} = V_{DD}$  or  $V_{SS}$ .

- <sup>3</sup> Measured with  $V_{In} = V_{SS}$ .

- <sup>4</sup> Measured with  $V_{In} = V_{DD}$ .

- <sup>5</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which (would reduce overall power consumption).

- $^{6}\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

<sup>7</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

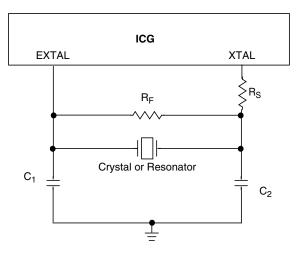

# A.9 Internal Clock Generation Module Characteristics

#### Table A-11. ICG DC Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Characteristic                                                                                                                                                         | Symbol                           | Min                   | Typ <sup>1</sup>          | Max | Unit     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------|-----|----------|--|

| Load capacitors                                                                                                                                                        | C <sub>1</sub><br>C <sub>2</sub> | See Note <sup>2</sup> |                           |     |          |  |

| Feedback resistor<br>Low range (32k to 100 kHz)<br>High range (1M – 16 MHz)                                                                                            | R <sub>F</sub>                   |                       | 10<br>1                   |     | ΜΩ<br>ΜΩ |  |

| Series resistor<br>Low range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>High range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>$\geq 8$ MHz<br>4 MHz<br>1 MHz | R <sub>S</sub>                   |                       | 0<br>100<br>0<br>10<br>20 |     | kΩ       |  |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0V, 25°C or is typical recommended value.

<sup>2</sup> See crystal or resonator manufacturer's recommendation.