Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | S08                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 40MHz                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 54                                                           |

| Program Memory Size        | 32KB (32K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 2K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 16x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-QFP                                                       |

| Supplier Device Package    | 64-QFP (14x14)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08aw32e5mfue |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

the CPU executes a STOP instruction, the MCU will not enter either of the stop modes and an illegal opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

HCS08 devices that are designed for low voltage operation (1.8V to 3.6V) also include stop1 mode. The MC9S08AW60 Series family of devices does not include stop1 mode.

| Mode  | PPDC | CPU, Digital<br>Peripherals,<br>FLASH | RAM     | ICG              | ADC1          | Regulator | I/O Pins       | RTI           |

|-------|------|---------------------------------------|---------|------------------|---------------|-----------|----------------|---------------|

| Stop2 | 1    | Off                                   | Standby | Off              | Disabled      | Standby   | States<br>held | Optionally on |

| Stop3 | 0    | Standby                               | Standby | Off <sup>1</sup> | Optionally on | Standby   | States<br>held | Optionally on |

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

|            |      |      | -        |

|------------|------|------|----------|

| Table 3-1. | Stop | Mode | Behavior |

<sup>1</sup> Crystal oscillator can be configured to run in stop3. Please see the ICG registers.

## 3.6.1 Stop2 Mode

The stop2 mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. To enter stop2, the user must execute a STOP instruction with stop2 selected (PPDC = 1) and stop mode enabled (STOPE = 1). In addition, the LVD must not be enabled to operate in stop (LVDSE = 0 or LVDE = 0). If the LVD is enabled in stop, then the MCU enters stop3 upon the execution of the STOP instruction regardless of the state of PPDC.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers which they want to restore after exit of stop2, to locations in RAM. Upon exit of stop2, these values can be restored by user software before pin latches are opened.

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ADC. Upon entry into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and after exiting stop2 mode until a logic 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting either of the wake-up pins:  $\overline{\text{RESET}}$  or IRQ, or by an RTI interrupt. IRQ is always an active low input when the MCU is in stop2, regardless of how it was configured before entering stop2.

### NOTE

Although this IRQ pin is automatically configured as active low input, the pullup associated with the IRQ pin is not automatically enabled. Therefore, if an external pullup is not used, the internal pullup must be enabled by setting IRQPE in IRQSC.

Upon wake-up from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

#### **Chapter 4 Memory**

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security" for a detailed description of the security feature.

# 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08AW60 Series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC2. The LVD is disabled upon entering any of the stop modes unless the LVDSE bit is set. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be greater.

## 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the chip in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

## 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

## 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF will be set and an LVD interrupt will occur.

### 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC2. Setting the LVW trip voltage equal to the LVD trip voltage is not recommended. Typical use of the LVW would be to select  $V_{LVWH}$  and  $V_{LVDL}$ .

## 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1-kHz internal clock or an external clock if available. The 1-kHz internal clock source is completely independent of any bus clock source and is used only by the RTI module and, on some MCUs, the COP watchdog. To use an external clock source, it must be available and active. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Chapter 5 Resets, Interrupts, and System Configuration

# 5.9.2 System Reset Status Register (SRS)

This register includes seven read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

|           | 7   | 6   | 5               | 4            | 3              | 2              | 1    | 0 |

|-----------|-----|-----|-----------------|--------------|----------------|----------------|------|---|

| R         | POR | PIN | COP             | ILOP         | 0              | ICG            | LVD  | 0 |

| w         |     | Wr  | iting any value | to SIMRS add | ress clears CO | P watchdog tin | ner. |   |

| POR       | 1   | 0   | 0               | 0            | 0              | 0              | 1    | 0 |

| LVR:      | U   | 0   | 0               | 0            | 0              | 0              | 1    | 0 |

| Any other | 0   | (1) | (1)             | (1)          | 0              | (1)            | 0    | 0 |

reset:

U = Unaffected by reset

<sup>1</sup> Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                     |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                             |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source may be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                                 |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

## 6.7.3 Port B I/O Registers (PTBD and PTBDD)

Port B parallel I/O function is controlled by the registers listed below.

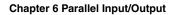

#### Figure 6-14. Port B Data Register (PTBD)

#### Table 6-7. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-15. Data Direction for Port B (PTBDD)

#### Table 6-8. PTBDD Register Field Descriptions

| Field             | Description                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDD[7:0] | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |

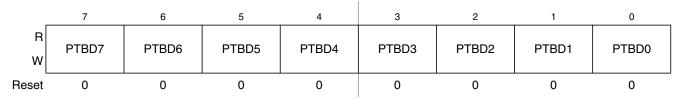

# 6.7.6 Port C Pin Control Registers (PTCPE, PTCSE, PTCDS)

In addition to the I/O control, port C pins are controlled by the registers listed below.

Figure 6-21. Internal Pullup Enable for Port C (PTCPE)

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTCPE[6:0] | <ul> <li>Internal Pullup Enable for Port C Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port C bit n.</li> <li>1 Internal pullup device enabled for port C bit n.</li> </ul> |

| _     | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     |   | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| w     |   | FICSED | FICSES | F103E4 | FICSES | FICSEZ | FICSEI | FICSED |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-22. Output Slew Rate Control Enable for Port C (PTCSE)

### Table 6-15. PTCSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTCSE[6:0] | <ul> <li>Output Slew Rate Control Enable for Port C Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port C bit n.</li> <li>1 Output slew rate control enabled for port C bit n.</li> </ul> |

#### Chapter 7 Central Processor Unit (S08CPUV2)

interrupt service routine, this would allow nesting of interrupts (which is not recommended because it leads to programs that are difficult to debug and maintain).

For compatibility with the earlier M68HC05 MCUs, the high-order half of the H:X index register pair (H) is not saved on the stack as part of the interrupt sequence. The user must use a PSHH instruction at the beginning of the service routine to save H and then use a PULH instruction just before the RTI that ends the interrupt service routine. It is not necessary to save H if you are certain that the interrupt service routine does not use any instructions or auto-increment addressing modes that might change the value of H.

The software interrupt (SWI) instruction is like a hardware interrupt except that it is not masked by the global I bit in the CCR and it is associated with an instruction opcode within the program so it is not asynchronous to program execution.

## 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

## 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

Chapter 7 Central Processor Unit (S08CPUV2)

- IX = 16-bit indexed no offset

- IX+ = 16-bit indexed no offset, post increment (CBEQ and MOV only)

- IX1 = 16-bit indexed with 8-bit offset from H:X

- IX1+ = 16-bit indexed with 8-bit offset, post increment (CBEQ only)

- IX2 = 16-bit indexed with 16-bit offset from H:X

- REL = 8-bit relative offset

- SP1 = Stack pointer with 8-bit offset

- SP2 = Stack pointer with 16-bit offset

#### Table 7-2. HCS08 Instruction Set Summary (Sheet 1 of 7)

| Source                                                                                                          | Operation                                                  | Description                                                        |    |    | Eff<br>on ( |    |    |    | ess<br>de                                           | Opcode                             | Operand                             | /cles <sup>1</sup>              |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|----|----|-------------|----|----|----|-----------------------------------------------------|------------------------------------|-------------------------------------|---------------------------------|

| Form                                                                                                            | Operation                                                  |                                                                    |    | н  | I           | N  | z  | с  | Address<br>Mode                                     |                                    |                                     | Bus Cycles <sup>1</sup>         |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP | Add with Carry                                             | A ← (A) + (M) + (C)                                                | \$ | \$ | _           | \$ | \$ | ¢  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | C9<br>D9<br>E9<br>F9               | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>5<br>4 |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry                                          | A ← (A) + (M)                                                      | \$ | \$ | _           | \$ | \$ | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | BB<br>CB<br>DB                     |                                     | 23443354                        |

| AIS #opr8i                                                                                                      | Add Immediate Value<br>(Signed) to Stack Pointer           | $SP \leftarrow (SP) + (M)$<br>M is sign extended to a 16-bit value | -  | -  | -           | -  | -  | -  | IMM                                                 | A7                                 | ii                                  | 2                               |

| AIX #opr8i                                                                                                      | Add Immediate Value<br>(Signed) to Index<br>Register (H:X) | H:X ← (H:X) + (M)<br>M is sign extended to a 16-bit value          | -  | -  | -           | -  | -  | -  | IMM                                                 | AF                                 | ii                                  | 2                               |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP | Logical AND                                                | A ← (A) & (M)                                                      | 0  | _  | _           | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | C4<br>D4<br>E4<br>F4               | dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| ASL opr8a<br>ASLA<br>ASLX<br>ASL oprx8,X<br>ASL ,X<br>ASL ,X<br>ASL oprx8,SP                                    | Arithmetic Shift Left<br>(Same as LSL)                     | C - 0 b7 b0                                                        | \$ | _  | _           | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68 |                                     | 5<br>1<br>5<br>4<br>6           |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                              | Arithmetic Shift Right                                     |                                                                    | \$ | _  | _           | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37<br>47<br>57<br>67<br>77<br>9E67 |                                     | 5<br>1<br>1<br>5<br>4<br>6      |

| BCC rel                                                                                                         | Branch if Carry Bit Clear                                  | Branch if $(C) = 0$                                                | -  | -  | -           | -  | -  | -  | REL                                                 | 24                                 | rr                                  | 3                               |

## 8.3 Register Definition

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all ICG registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

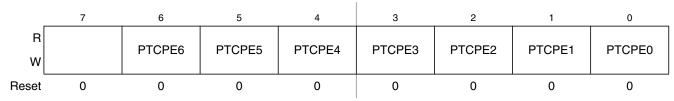

## 8.3.1 ICG Control Register 1 (ICGC1)

#### Figure 8-6. ICG Control Register 1 (ICGC1)

<sup>1</sup> This bit can be written only once after reset. Additional writes are ignored.

#### Table 8-1. ICGC1 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>HGO    | High Gain Oscillator Select — The HGO bit is used to select between low power operation and high gain operation for improved noise immunity. This bit is write-once after reset.         0       Oscillator configured for low power operation.         1       Oscillator configured for high gain operation.                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>RANGE  | <ul> <li>Frequency Range Select — The RANGE bit controls the oscillator, reference divider, and FLL loop prescaler multiplication factor (P). It selects one of two reference frequency ranges for the ICG. The RANGE bit is write-once after a reset. The RANGE bit only has an effect in FLL engaged external and FLL bypassed external modes.</li> <li>O Oscillator configured for low frequency range. FLL loop prescale factor P is 64.</li> <li>1 Oscillator configured for high frequency range. FLL loop prescale factor P is 1.</li> </ul>                                                                                                            |

| 5<br>REFS   | External Reference Select — The REFS bit controls the external reference clock source for ICGERCLK. The REFS bit is write-once after a reset.         0       External clock requested.         1       Oscillator using crystal or resonator requested.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4:3<br>CLKS | Clock Mode Select — The CLKS bits control the clock mode as described below. If FLL bypassed external is requested, it will not be selected until ERCS = 1. If the ICG enters off mode, the CLKS bits will remain unchanged. Writes to the CLKS bits will not take effect if a previous write is not complete.<br>00 Self-clocked<br>01 FLL engaged, internal reference<br>10 FLL bypassed, external reference<br>11 FLL engaged, external reference<br>The CLKS bits are writable at any time, unless the first write after a reset was CLKS = 0X, the CLKS bits cannot be written to 1X until after the next reset (because the EXTAL pin was not reserved). |

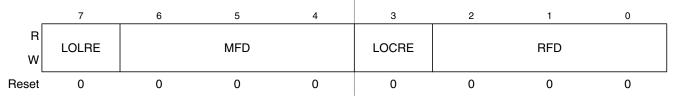

# 8.3.2 ICG Control Register 2 (ICGC2)

Figure 8-7. ICG Control Register 2 (ICGC2)

### Table 8-2. ICGC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOLRE | Loss of Lock Reset Enable — The LOLRE bit determines what type of request is made by the ICG following a loss of lock indication. The LOLRE bit only has an effect when LOLS is set.         0       Generate an interrupt request on loss of lock.         1       Generate a reset request on loss of lock.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6:4<br>MFD | Multiplication Factor — The MFD bits control the programmable multiplication factor in the FLL loop. The value specified by the MFD bits establishes the multiplication factor (N) applied to the reference frequency. Writes to the MFD bits will not take effect if a previous write is not complete. Select a low enough value for N such that f <sub>ICGDCLK</sub> does not exceed its maximum specified value.         000       Multiplication factor = 4         001       Multiplication factor = 6         010       Multiplication factor = 8         011       Multiplication factor = 10         100       Multiplication factor = 14         110       Multiplication factor = 16         111       Multiplication factor = 18 |

| 3<br>LOCRE | <ul> <li>Loss of Clock Reset Enable — The LOCRE bit determines how the system manages a loss of clock condition.</li> <li>Generate an interrupt request on loss of clock.</li> <li>Generate a reset request on loss of clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2:0<br>RFD | Reduced Frequency Divider — The RFD bits control the value of the divider following the clock select circuitry.         The value specified by the RFD bits establishes the division factor (R) applied to the selected output clock source.         Writes to the RFD bits will not take effect if a previous write is not complete.         000       Division factor = 1         001       Division factor = 2         010       Division factor = 4         011       Division factor = 8         100       Division factor = 16         101       Division factor = 64         111       Division factor = 128                                                                                                                         |

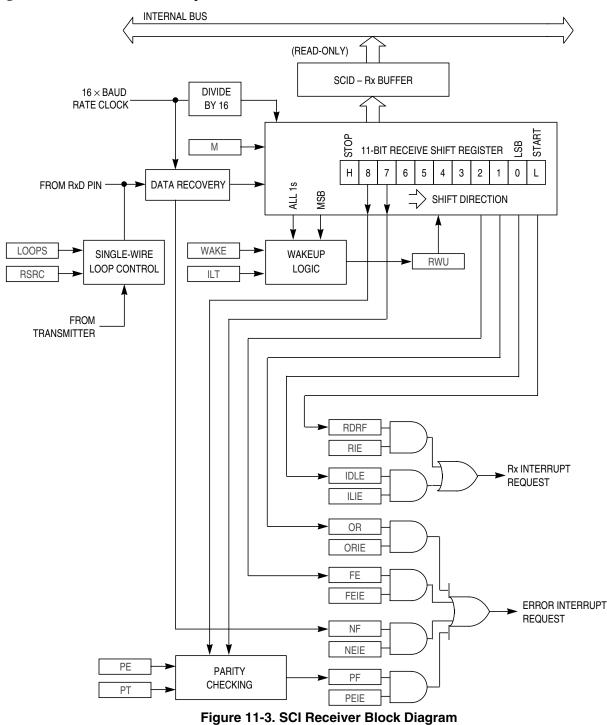

Figure 11-3 shows the receiver portion of the SCI.

## 11.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

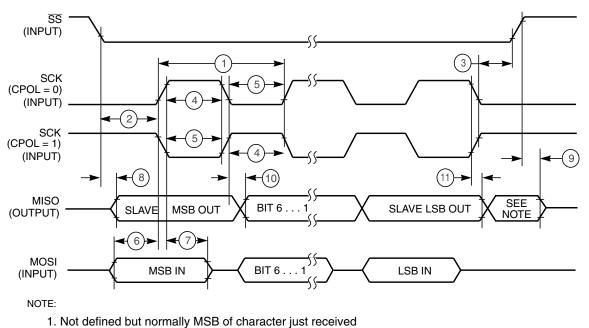

## 12.4.2 SPI Interrupts

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

### 12.4.3 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS}$  pin (provided the  $\overline{SS}$  pin is configured as the mode fault input signal). The  $\overline{SS}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK, MOSI, and MISO (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPI1C1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

### 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

### 13.1.2 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop2 will reset the register contents.

Chapter 13 Inter-Integrated Circuit (S08IICV1)

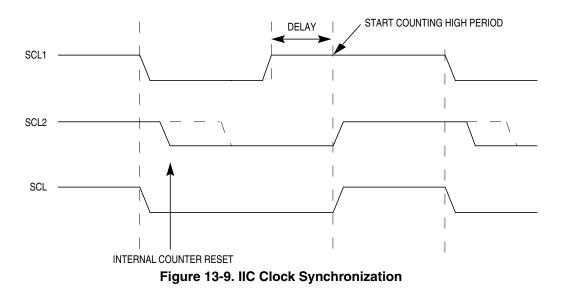

### 13.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 13.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

## 13.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

## 13.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 13-7 occur provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a one to it in the interrupt routine. The user can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

| Table 13-7. Interrupt Summary |

|-------------------------------|

|-------------------------------|

### 14.2.2.1 Analog Pin Enables

The ADC on MC9S08AW60 Series contains only two analog pin enable registers, APCTL1 and APCTL2.

### 14.2.2.2 Low-Power Mode Operation

The ADC is capable of running in stop3 mode but requires LVDSE and LVDE in SPMSC1 to be set.

### 14.2.3 Temperature Sensor

The ADC1 module includes a temperature sensor whose output is connected to one of the ADC analog channel inputs. Equation 14-1 provides an approximate transfer function of the temperature sensor.

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- $V_{\text{TEMP25}}$  is the voltage of the temperature sensor channel at 25°C.

- m is the hot or cold voltage versus temperature slope in  $V/^{\circ}C$ .

For temperature calculations, use the V<sub>TEMP25</sub> and m values from the ADC Electricals table.

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$  the cold slope value is applied in Equation 14-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 14-1.

## 14.3.1 Analog Power (V<sub>DDAD</sub>)

The ADC analog portion uses  $V_{DDAD}$  as its power connection. In some packages,  $V_{DDAD}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDAD}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDAD}$  for good results.

## 14.3.2 Analog Ground (V<sub>SSAD</sub>)

The ADC analog portion uses  $V_{SSAD}$  as its ground connection. In some packages,  $V_{SSAD}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSAD}$  pin to the same voltage potential as  $V_{SS}$ .

## 14.3.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDAD}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ).

## 14.3.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSAD}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSAD}$ .

## 14.3.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

## 14.4 Register Definition

These memory mapped registers control and monitor operation of the ADC:

- Status and control register, ADC1SC1

- Status and control register, ADC1SC2

- Data result registers, ADC1RH and ADC1RL

- Compare value registers, ADC1CVH and ADC1CVL

- Configuration register, ADC1CFG

- Pin enable registers, APCTL1, APCTL2, APCTL3

## 14.4.1 Status and Control Register 1 (ADC1SC1)

This section describes the function of the ADC status and control register (ADC1SC1). Writing ADC1SC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

Figure 14-7. Data Result Low Register (ADC1RL)

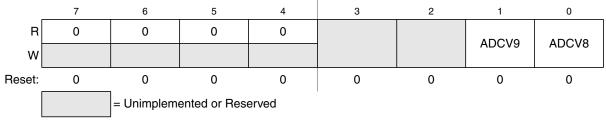

# 14.4.5 Compare Value High Register (ADC1CVH)

This register holds the upper two bits of the 10-bit compare value. These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled. In 8-bit operation, ADC1CVH is not used during compare.

Figure 14-8. Compare Value High Register (ADC1CVH)

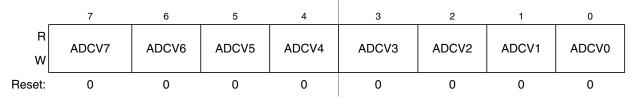

## 14.4.6 Compare Value Low Register (ADC1CVL)

This register holds the lower 8 bits of the 10-bit compare value, or all 8 bits of the 8-bit compare value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in either 10-bit or 8-bit mode.

Figure 14-9. Compare Value Low Register(ADC1CVL)

# 14.4.7 Configuration Register (ADC1CFG)

ADC1CFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

**Chapter 15 Development Support**

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

Appendix A Electrical Characteristics and Timing Specifications

# A.7 Supply Current Characteristics

Table A-8. Supply Current Characteristics

| Num | с                                              | Parameter                                                                                    | Symbol               | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max          | Unit                        | Temp<br>(°C)                |

|-----|------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------|------------------------|------------------|--------------|-----------------------------|-----------------------------|

| 1 0 |                                                | Run supply current <sup>2</sup> measured at<br>(CPU clock = 2 MHz, f <sub>Bus</sub> = 1 MHz) | RI <sub>DD</sub>     | 5                      | 0.750            | 0.950        | mA                          | 40.1.40500                  |

| 1 P | 3                                              |                                                                                              |                      | 0.570                  | 0.770            | –40 to 125°C |                             |                             |

|     |                                                | Run supply current <sup>2</sup> measured at                                                  |                      | 5                      | 4.90             | 5.10         |                             | (0) (0700                   |

| 2 P | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz) | RI <sub>DD</sub>                                                                             | 3                    | 3.50                   | 3.70             | mA           | –40 to 125°C                |                             |

|     |                                                | Run supply current <sup>3</sup> measured at (CPU clock = 40 MHz, f <sub>Bus</sub> = 20 MHz)  | RI <sub>DD</sub>     | 5                      | 16.8             | 18.5         | mA                          |                             |

| 3 P | 3                                              |                                                                                              |                      | 11.5                   | 12.5             | –40 to 125°C |                             |                             |

|     | _                                              | Stop2 mode supply current                                                                    |                      | 5                      | 0.900            | 18.0<br>60   | μA                          | –40 to 85°C<br>–40 to 125°C |

| 4 P |                                                | S2I <sub>DD</sub>                                                                            | 3                    | 0.720                  | 17.0<br>50       | μA           | –40 to 85°C<br>–40 to 125°C |                             |

| 5   | Р                                              | Stop3 mode supply current                                                                    |                      | 5                      | 0.975            | 20.0<br>90   | μA                          | –40 to 85°C<br>–40 to 125°C |

| 5 P |                                                | S3I <sub>DD</sub>                                                                            | 3                    | 0.825                  | 19.0<br>85       | μA           | –40 to 85°C<br>–40 to 125°C |                             |

| 6   | с                                              | RTI adder to stop2 or stop3 <sup>4</sup>                                                     |                      | 5                      | 300              | 500<br>500   | nA                          | –40 to 85°C<br>–40 to 125°C |

| 6 C |                                                | S23I <sub>ddrti</sub>                                                                        | 3                    | 300                    | 500<br>500       | nA           | –40 to 85°C<br>–40 to 125°C |                             |

| 7   | 7 C                                            |                                                                                              | S3I <sub>DDLVD</sub> | 5                      | 110              | 180          | μA                          | –40 to 125°C                |

|     |                                                | LVD adder to stop3 (LVDE = LVDSE = 1)                                                        |                      | 3                      | 90               | 160          | μA                          | –40 to 125°C                |

| 8   | с                                              | Adder to stop3 for oscillator enabled (OSCSTEN =1) <sup>5</sup>                              | S3I <sub>DDOSC</sub> | 5,3                    | 5                | 8            | μA                          | –40 to 125°C                |

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

<sup>2</sup> All modules except ADC enabled, but not active. ICG configured for FBE. Does not include any DC loads on port pins.

<sup>3</sup> All modules except ADC active, ICG configured for FBE and does not include any DC loads on port pins

<sup>4</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 500  $\mu$ A at 5 V with f<sub>Bus</sub> = 1 MHz.

<sup>5</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768 kHz crystal, low power mode (HGO = 0), clock monitor disabled (LOCD = 1).

Appendix A Electrical Characteristics and Timing Specifications

MC9S08AW60 Data Sheet, Rev 2