Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | 508                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 40MHz                                                         |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                            |

| Number of I/O              | 34                                                            |

| Program Memory Size        | 60KB (60K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-LQFP                                                       |

| Supplier Device Package    | 44-LQFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08aw60e5mfger |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                     |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 1/2006           | Initial external release.                                                                                                                                                                                                                                                                                                  |

| 2                  | 12/2006          | Includes KBI block changes; new V <sub>OL</sub> / I <sub>OL</sub> figures; RI <sub>DD</sub> spec changes; SC part numbers with ICG trim modifications; addition of Temp Sensor to ADC. Resolved the stop IDD issues, added RTI figure, bandgap information, and incorporated electricals edits and any ProjectSync issues. |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006. All rights reserved.

# **Section Number**

Title

## Page

|     | 7.2.1     | Accumulator (A)                 | 110 |

|-----|-----------|---------------------------------|-----|

|     | 7.2.2     | Index Register (H:X)            |     |

|     | 7.2.3     | Stack Pointer (SP)              |     |

|     | 7.2.4     | Program Counter (PC)            |     |

|     | 7.2.5     | Condition Code Register (CCR)   |     |

| 7.3 | Addressi  | ng Modes                        | 113 |

|     | 7.3.1     | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2     | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3     | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4     | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5     | Extended Addressing Mode (EXT)  | 114 |

|     | 7.3.6     | Indexed Addressing Mode         | 114 |

| 7.4 | Special C | Operations                      | 115 |

|     | 7.4.1     | Reset Sequence                  | 115 |

|     | 7.4.2     | Interrupt Sequence              |     |

|     | 7.4.3     | Wait Mode Operation             |     |

|     | 7.4.4     | Stop Mode Operation             |     |

|     | 7.4.5     | BGND Instruction                | 117 |

| 7.5 | HCS08 I   | nstruction Set Summary          | 118 |

# Chapter 8 Internal Clock Generator (S08ICGV4)

| Introduc | tion                                                                                                                                                                    | 131                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 8.1.1    | Features                                                                                                                                                                | 131                                         |

| 8.1.2    | Modes of Operation                                                                                                                                                      | 132                                         |

| 8.1.3    | Block Diagram                                                                                                                                                           | 133                                         |

| External | Signal Description                                                                                                                                                      | 133                                         |

| 8.2.1    | EXTAL — External Reference Clock / Oscillator Input                                                                                                                     | 133                                         |

| 8.2.2    | XTAL — Oscillator Output                                                                                                                                                | 133                                         |

| 8.2.3    |                                                                                                                                                                         |                                             |

| 8.2.4    | External Crystal/Resonator Connections                                                                                                                                  | 134                                         |

| Register | Definition                                                                                                                                                              | 135                                         |

| 8.3.1    | ICG Control Register 1 (ICGC1)                                                                                                                                          | 135                                         |

| 8.3.2    | ICG Control Register 2 (ICGC2)                                                                                                                                          | 137                                         |

| 8.3.3    | ICG Status Register 1 (ICGS1)                                                                                                                                           | 138                                         |

| 8.3.4    | ICG Status Register 2 (ICGS2)                                                                                                                                           | 139                                         |

| 8.3.5    | ICG Filter Registers (ICGFLTU, ICGFLTL)                                                                                                                                 | 139                                         |

| 8.3.6    | ICG Trim Register (ICGTRM)                                                                                                                                              | 140                                         |

| Function | al Description                                                                                                                                                          | 140                                         |

| 8.4.1    | Off Mode (Off)                                                                                                                                                          | 141                                         |

| 8.4.2    | Self-Clocked Mode (SCM)                                                                                                                                                 | 141                                         |

| 8.4.3    | FLL Engaged, Internal Clock (FEI) Mode                                                                                                                                  | 142                                         |

|          | 8.1.1<br>8.1.2<br>8.1.3<br>External<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Register<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>Function<br>8.4.1<br>8.4.2 | <ul> <li>8.1.2 Modes of Operation</li></ul> |

**Section Number**

## Title

Page

# Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

| 14.1 | Overview   | 7                                           | 233 |

|------|------------|---------------------------------------------|-----|

| 14.2 | Channel A  | Assignments                                 | 233 |

|      | 14.2.1     | Alternate Clock                             | 234 |

|      | 14.2.2     | Hardware Trigger                            | 234 |

|      | 14.2.3     | Temperature Sensor                          | 235 |

|      | 14.2.4     | Features                                    | 237 |

|      | 14.2.5     | Block Diagram                               | 237 |

| 14.3 | External   | Signal Description                          | 238 |

|      | 14.3.1     | Analog Power (V <sub>DDAD</sub> )           | 239 |

|      | 14.3.2     | Analog Ground (V <sub>SSAD</sub> )          | 239 |

|      | 14.3.3     | Voltage Reference High (V <sub>REFH</sub> ) | 239 |

|      | 14.3.4     | Voltage Reference Low (V <sub>REFL</sub> )  |     |

|      | 14.3.5     | Analog Channel Inputs (ADx)                 |     |

| 14.4 | Register I | Definition                                  | 239 |

|      | 14.4.1     | Status and Control Register 1 (ADC1SC1)     | 239 |

|      | 14.4.2     | Status and Control Register 2 (ADC1SC2)     | 241 |

|      | 14.4.3     | Data Result High Register (ADC1RH)          |     |

|      | 14.4.4     | Data Result Low Register (ADC1RL)           | 242 |

|      | 14.4.5     | Compare Value High Register (ADC1CVH)       | 243 |

|      | 14.4.6     | Compare Value Low Register (ADC1CVL)        |     |

|      | 14.4.7     | Configuration Register (ADC1CFG)            |     |

|      | 14.4.8     | Pin Control 1 Register (APCTL1)             | 245 |

|      | 14.4.9     | Pin Control 2 Register (APCTL2)             |     |

|      | 14.4.10    | Pin Control 3 Register (APCTL3)             |     |

| 14.5 |            | al Description                              |     |

|      | 14.5.1     | Clock Select and Divide Control             | 248 |

|      | 14.5.2     | Input Select and Pin Control                | 249 |

|      | 14.5.3     | Hardware Trigger                            | 249 |

|      | 14.5.4     | Conversion Control                          | 249 |

|      | 14.5.5     | Automatic Compare Function                  | 252 |

|      | 14.5.6     | MCU Wait Mode Operation                     | 252 |

|      | 14.5.7     | MCU Stop3 Mode Operation                    | 252 |

|      | 14.5.8     | MCU Stop1 and Stop2 Mode Operation          | 253 |

| 14.6 |            | ion Information                             |     |

|      | 14.6.1     | ADC Module Initialization Example           | 253 |

| 14.7 | Applicati  | on Information                              |     |

|      | 14.7.1     | External Pins and Routing                   | 255 |

|      | 14.7.2     | Sources of Error                            |     |

|      |            |                                             |     |

Chapter 6 Parallel Input/Output

# 6.7.9 Port E I/O Registers (PTED and PTEDD)

Port E parallel I/O function is controlled by the registers listed below.

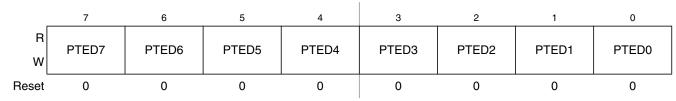

### Figure 6-29. Port E Data Register (PTED)

#### Table 6-22. PTED Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTED[7:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-30. Data Direction for Port E (PTEDD)

#### Table 6-23. PTEDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 7:0        | Data Direction for Port E Bits — These read/write bits control the direction of port E pins and what is read for |

| PTEDD[7:0] | PTED reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.                            |

#### Chapter 6 Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-38. Output Drive Strength Selection for Port F (PTFDS)

### Table 6-31. PTFDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFDS[7:0] | <ul> <li>Output Drive Strength Selection for Port F Bits — Each of these control bits selects between low and high output drive for the associated PTF pin.</li> <li>0 Low output drive enabled for port F bit n.</li> <li>1 High output drive enabled for port F bit n.</li> </ul> |

Chapter 7 Central Processor Unit (S08CPUV2)

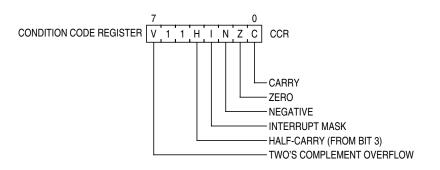

### Figure 7-2. Condition Code Register

#### Table 7-1. CCR Register Field Descriptions

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>V | Two's Complement Overflow Flag — The CPU sets the overflow flag when a two's complement overflow occurs.         The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.         0       No overflow         1       Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4<br>H | <ul> <li>Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.</li> <li>0 No carry between bits 3 and 4</li> <li>1 Carry between bits 3 and 4</li> </ul>                                                                                            |

| 3      | Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.         Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.         0       Interrupts disabled |

| 2<br>N | Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.         0       Non-negative result         1       Negative result                                                                                                                                                                                                                                                                                               |

| 1<br>Z | <ul> <li>Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.</li> <li>0 Non-zero result</li> <li>1 Zero result</li> </ul>                                                                                                                                                                                                                                                                                                                                                |

| 0<br>C | <ul> <li>Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.</li> <li>No carry out of bit 7</li> <li>Carry out of bit 7</li> </ul>                                                                                                                                                                                                                                                                                                   |

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

# 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

## 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

# 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Bit-Manipulation | Branch | Rea | d-Modify-W |                                  | <br>Control Register/Memory |  |                        |      |  |                                  |                        |                                   |

|------------------|--------|-----|------------|----------------------------------|-----------------------------|--|------------------------|------|--|----------------------------------|------------------------|-----------------------------------|

|                  |        |     |            | 9E60 6<br>NEG<br>3 SP1           |                             |  |                        |      |  | 9ED0 5<br>SUB<br>4 SP2           | 9EE0 4<br>SUB<br>3 SP1 |                                   |

|                  |        |     |            | 9E61 6<br>CBEQ<br>4 SP1          |                             |  |                        |      |  | 9ED1 5<br>CMP<br>4 SP2           | 9EE1 4<br>CMP<br>3 SP1 |                                   |

|                  |        |     |            |                                  |                             |  |                        |      |  | 9ED2 5<br>SBC<br>4 SP2           | 3 SP1                  |                                   |

|                  |        |     |            | 9E63 6<br>COM<br>3 SP1           |                             |  |                        |      |  | 9ED3 5<br>CPX<br>4 SP2<br>9ED4 5 | 9EE3 4<br>CPX<br>3 SP1 | 9EF3 6<br>CPHX<br>3 SP1           |

|                  |        |     |            | 9E64 6<br>LSR<br>3 SP1           |                             |  |                        |      |  | AND                              | AND                    |                                   |

|                  |        |     |            |                                  |                             |  |                        |      |  | 9ED5 5<br>BIT<br>4 SP2           | 9EE5 4<br>BIT<br>3 SP1 |                                   |

|                  |        |     |            | 9E66 6<br>ROR<br>3 SP1           |                             |  |                        |      |  | 9ED6 5<br>LDA<br>4 SP2           | 9EE6 4<br>LDA<br>3 SP1 |                                   |

|                  |        |     |            | 9E67 6<br>ASR<br>3 SP1           |                             |  |                        |      |  | 9ED7 5<br>STA<br>4 SP2           | 9EE7 4<br>STA<br>3 SP1 |                                   |

|                  |        |     |            | 9E68 6<br>LSL<br>3 SP1<br>9E69 6 |                             |  |                        |      |  | 9ED8 5<br>EOR<br>4 SP2           | 9EE8 4<br>EOR<br>3 SP1 |                                   |

|                  |        |     |            | ROL<br>3 SP1                     |                             |  |                        |      |  | 9ED9 5<br>ADC<br>4 SP2           | ADC<br>3 SP1           |                                   |

|                  |        |     |            | 9E6A 6<br>DEC<br>3 SP1           |                             |  |                        |      |  | 9EDA 5<br>ORA<br>4 SP2           | ORA<br>3 SP1           |                                   |

|                  |        |     |            | 9E6B 8<br>DBNZ<br>4 SP1          |                             |  |                        |      |  | 9EDB 5<br>ADD<br>4 SP2           | ADD                    |                                   |

|                  |        |     |            | 9E6C 6<br>INC<br>3 SP1           |                             |  |                        |      |  |                                  |                        |                                   |

|                  |        |     |            | 9E6D 5<br>TST<br>3 SP1           |                             |  |                        |      |  |                                  |                        |                                   |

|                  |        |     |            |                                  |                             |  | 9EAE 5<br>LDHX<br>2 IX | LDHX |  | 9EDE 5<br>LDX<br>4 SP2           | א חו                   | 9EFE 5<br>LDHX<br>3 SP1<br>9EFF 5 |

|                  |        |     |            | 9E6F 6<br>CLR<br>3 SP1           |                             |  |                        |      |  | 9EDF 5<br>STX<br>4 SP2           | 9EEF 4<br>STX<br>3 SP1 | 9EFF 5<br>STHX<br>3 SP1           |

#### Table 7-3. Opcode Map (Sheet 2 of 2)

Inherent Immediate Direct Extended DIR to DIR IX+ to DIR REL IX IX1 IX2 IMD DIX+ INH IMM DIR EXT DD IX+D

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment

SP1 SP2 IX+

IX1+

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal 9E60 6 NEG Number of Bytes 3 SP1 Addressing Mode

MC9S08AW60 Data Sheet, Rev 2

# Chapter 8 Internal Clock Generator (S08ICGV4)

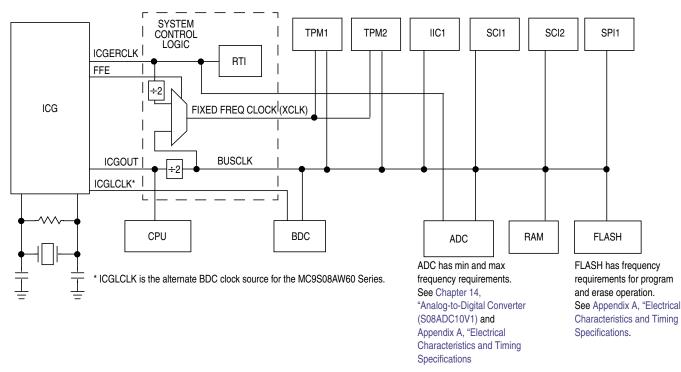

The internal clock generation (ICG) module is used to generate the system clocks for the MC9S08AW60 Series MCU. The analog supply lines  $V_{DDA}$  and  $V_{SSA}$  are internally derived from the MCU's  $V_{DD}$  and  $V_{SS}$  pins. Electrical parametric data for the ICG may be found in Appendix A, "Electrical Characteristics and Timing Specifications."

Figure 8-1. System Clock Distribution Diagram

### NOTE

Freescale Semiconductor recommends that FLASH location \$FFBE be reserved to store a nonvolatile version of ICGTRM. This will allow debugger and programmer vendors to perform a manual trim operation and store the resultant ICGTRM value for users to access at a later time.

## 8.4.4 FLL Engaged Internal Unlocked

FEI unlocked is a temporary state that is entered when FEI is entered and the count error ( $\Delta n$ ) output from the subtractor is greater than the maximum  $n_{unlock}$  or less than the minimum  $n_{unlock}$ , as required by the lock detector to detect the unlock condition.

The ICG will remain in this state while the count error ( $\Delta n$ ) is greater than the maximum  $n_{lock}$  or less than the minimum  $n_{lock}$ , as required by the lock detector to detect the lock condition.

In this state the output clock signal ICGOUT frequency is given by f<sub>ICGDCLK</sub> / R.

## 8.4.5 FLL Engaged Internal Locked

FLL engaged internal locked is entered from FEI unlocked when the count error ( $\Delta n$ ), which comes from the subtractor, is less than  $n_{lock}$  (max) and greater than  $n_{lock}$  (min) for a given number of samples, as required by the lock detector to detect the lock condition. The output clock signal ICGOUT frequency is given by  $f_{ICGDCLK}$  / R. In FEI locked, the filter value is updated only once every four comparison cycles. The update made is an average of the error measurements taken in the four previous comparisons.

## 8.4.6 FLL Bypassed, External Clock (FBE) Mode

FLL bypassed external (FBE) is entered when any of the following conditions occur:

- From SCM when CLKS = 10 and ERCS is high

- When CLKS = 10, ERCS = 1 upon entering off mode, and off is then exited

- From FLL engaged external mode if a loss of DCO clock occurs and the external reference remains valid (both LOCS = 1 and ERCS = 1)

In this state, the DCO and IRG are off and the reference clock is derived from the external reference clock, ICGERCLK. The output clock signal ICGOUT frequency is given by  $f_{ICGERCLK} / R$ . If an external clock source is used (REFS = 0), then the input frequency on the EXTAL pin can be anywhere in the range 0 MHz to 40 MHz. If a crystal or resonator is used (REFS = 1), then frequency range is either low for RANGE = 0 or high for RANGE = 1.

## 8.4.7 FLL Engaged, External Clock (FEE) Mode

The FLL engaged external (FEE) mode is entered when any of the following conditions occur:

- CLKS = 11 and ERCS and DCOS are both high.

- The DCO stabilizes (DCOS = 1) while in SCM upon exiting the off state with CLKS = 11.

In FEE mode, the reference clock is derived from the external reference clock ICGERCLK, and the FLL loop will attempt to lock the ICGDCLK frequency to the desired value, as selected by the MFD bits. To run in FEE mode, there must be a working 32 kHz–100 kHz or 2 MHz–10 MHz external clock source. The maximum external clock frequency is limited to 10 MHz in FEE mode to prevent over-clocking the DCO. The minimum multiplier for the FLL, from Table 8-12 is 4. Because 4 X 10 MHz is 40MHz, which is the operational limit of the DCO, the reference clock cannot be any faster than 10 MHz.

Chapter 8 Internal Clock Generator (S08ICGV4)

Chapter 9 Keyboard Interrupt (S08KBIV1)

## 9.3 Features

The keyboard interrupt (KBI) module features include:

- Four falling edge/low level sensitive

- Four falling edge/low level or rising edge/high level sensitive

- Choice of edge-only or edge-and-level sensitivity

- Common interrupt flag and interrupt enable control

- Capable of waking up the MCU from stop3 or wait mode

# Chapter 13 Inter-Integrated Circuit (S08IICV1)

# 13.1 Introduction

The MC9S08AW60 Series of microcontrollers has an inter-integrated circuit (IIC) module for communication with other integrated circuits. The two pins associated with this module, SCL and SDA, are open-drain outputs and are shared with port C pins 0 and 1, respectively.

Chapter 13 Inter-Integrated Circuit (S08IICV1)

# 13.3.5 IIC Data I/O Register (IIC1D)

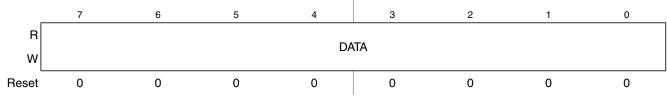

#### Figure 13-7. IIC Data I/O Register (IIC1D)

#### Table 13-6. IIC1D Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>DATA | <b>Data</b> — In master transmit mode, when data is written to the IIC1D, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |

### NOTE

When transmitting out of master receive mode, the IIC mode should be switched before reading the IIC1D register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

Note that the TX bit in IIC1C must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, then reading the IIC1D will not initiate the receive.

Reading the IIC1D will return the last byte received while the IIC is configured in either master receive or slave receive modes. The IIC1D does not reflect every byte that is transmitted on the IIC bus, nor can software verify that a byte has been written to the IIC1D correctly by reading it back.

In master transmit mode, the first byte of data written to IIC1D following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7–bit 1) concatenated with the required R/W bit (in position bit 0).

Chapter 13 Inter-Integrated Circuit (S08IICV1)

## 13.4.1.8 Handshaking

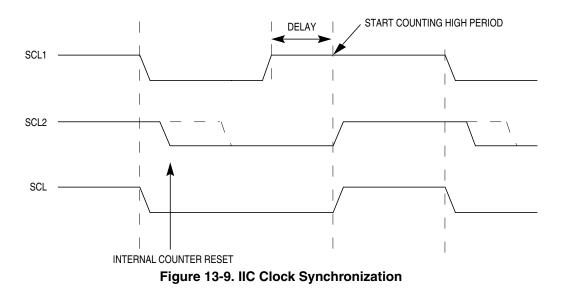

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

## 13.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

## 13.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

## 13.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 13-7 occur provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a one to it in the interrupt routine. The user can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

| Table 13-7. Interrupt Summary |

|-------------------------------|

|-------------------------------|

## 14.2.4 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 10 bits resolution.

- Up to 28 analog inputs.

- Output formatted in 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop3 modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Selectable asynchronous hardware conversion trigger.

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

## 14.2.5 Block Diagram

Figure 14-2 provides a block diagram of the ADC module

| Command<br>Mnemonic |               |                  | Description                                                                              |

|---------------------|---------------|------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive | n/a <sup>1</sup> | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive | D5/d             | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |

| ACK_DISABLE         | Non-intrusive | D6/d             | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |

| BACKGROUND          | Non-intrusive | 90/d             | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive | E4/SS            | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive | C4/CC            | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive | E0/AAAA/d/RD     | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive | E1/AAAA/d/SS/RD  | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive | E8/SS/RD         | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive | C0/AAAA/WD/d     | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive | C1/AAAA/WD/d/SS  | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive | E2/RBKP          | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive | C2/WBKP          | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM    | 08/d             | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM    | 10/d             | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM    | 18/d             | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |

| READ_A              | Active BDM    | 68/d/RD          | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM    | 69/d/RD          | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM    | 6B/d/RD16        | Read program counter (PC)                                                                |

| READ_HX             | Active BDM    | 6C/d/RD16        | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM    | 6F/d/RD16        | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM    | 70/d/RD          | Increment H:X by one then read memory byte located at H:X                                |

| READ_NEXT_WS        | Active BDM    | 71/d/SS/RD       | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM    | 48/WD/d          | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM    | 49/WD/d          | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM    | 4B/WD16/d        | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM    | 4C/WD16/d        | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM    | 4F/WD16/d        | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM    | 50/WD/d          | Increment H:X by one, then write memory byte located at H:X                              |

| WRITE_NEXT_WS       | Active BDM    | 51/WD/d/SS       | Increment H:X by one, then write memory byte located at H:X. Also report status.         |

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

Appendix A Electrical Characteristics and Timing Specifications

# A.7 Supply Current Characteristics

| Table A-8. | Supply | Current | Characteristics |

|------------|--------|---------|-----------------|

|------------|--------|---------|-----------------|

| Num | с | Parameter                                                       | Symbol                | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max        | Unit | Temp<br>(°C)                |

|-----|---|-----------------------------------------------------------------|-----------------------|------------------------|------------------|------------|------|-----------------------------|

|     | _ | Run supply current <sup>2</sup> measured at                     |                       | 5                      | 0.750            | 0.950      |      |                             |

| 1   | P | (CPU clock = 2 MHz, f <sub>Bus</sub> = 1 MHz)                   | RI <sub>DD</sub>      | 3                      | 0.570            | 0.770      | mA   | –40 to 125°C                |

|     |   | Run supply current <sup>2</sup> measured at                     |                       | 5                      | 4.90             | 5.10       |      |                             |

| 2   | P | P (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz)                | RI <sub>DD</sub>      | 3                      | 3.50             | 3.70       | mA   | –40 to 125°C                |

| _   | Р | Run supply current <sup>3</sup> measured at (CPU                |                       | 5                      | 16.8             | 18.5       |      | 40 1 40500                  |

| 3   | P | clock = 40 MHz, f <sub>Bus</sub> = 20 MHz)                      | RI <sub>DD</sub>      | 3                      | 11.5             | 12.5       | mA   | –40 to 125°C                |

| 4   |   | Stop2 mode supply current                                       |                       | 5                      | 0.900            | 18.0<br>60 | μA   | –40 to 85°C<br>–40 to 125°C |

| 4   | P |                                                                 | S2I <sub>DD</sub>     | 3                      | 0.720            | 17.0<br>50 | μA   | –40 to 85°C<br>–40 to 125°C |

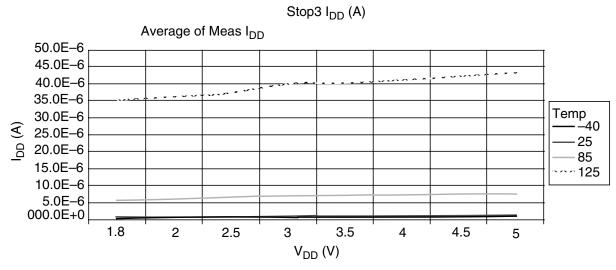

| 5   | Р | Stop3 mode supply current                                       |                       | 5                      | 0.975            | 20.0<br>90 | μA   | –40 to 85°C<br>–40 to 125°C |

| 5   | P |                                                                 | S3I <sub>DD</sub>     | 3                      | 0.825            | 19.0<br>85 | μA   | –40 to 85°C<br>–40 to 125°C |

| 6   | с | RTI adder to stop2 or stop3 <sup>4</sup>                        | S23I <sub>DDRTI</sub> | 5                      | 300              | 500<br>500 | nA   | –40 to 85°C<br>–40 to 125°C |

| 0   |   |                                                                 |                       | 3                      | 300              | 500<br>500 | nA   | –40 to 85°C<br>–40 to 125°C |

| 7   | с |                                                                 | <u></u>               | 5                      | 110              | 180        | μA   | –40 to 125°C                |

|     |   | LVD adder to stop3 (LVDE = LVDSE = 1)                           | S3I <sub>DDLVD</sub>  | 3                      | 90               | 160        | μA   | –40 to 125°C                |

| 8   | с | Adder to stop3 for oscillator enabled (OSCSTEN =1) <sup>5</sup> | S3I <sub>DDOSC</sub>  | 5,3                    | 5                | 8          | μA   | –40 to 125°C                |

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

<sup>2</sup> All modules except ADC enabled, but not active. ICG configured for FBE. Does not include any DC loads on port pins.

<sup>3</sup> All modules except ADC active, ICG configured for FBE and does not include any DC loads on port pins

<sup>4</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 500  $\mu$ A at 5 V with f<sub>Bus</sub> = 1 MHz.

<sup>5</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768 kHz crystal, low power mode (HGO = 0), clock monitor disabled (LOCD = 1).

Appendix A Electrical Characteristics and Timing Specifications

Figure A-7. Typical Stop3 I<sub>DD</sub>

# A.8 ADC Characteristics

| Characteristic                              | Conditions                                                                  | Symb               | Min               | Typ <sup>1</sup>  | Max               | Unit |

|---------------------------------------------|-----------------------------------------------------------------------------|--------------------|-------------------|-------------------|-------------------|------|

| Supply voltage                              | Absolute                                                                    | V <sub>DDAD</sub>  | 2.7               | _                 | 5.5               | V    |

|                                             | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | ΔV <sub>DDAD</sub> | -100              | 0                 | +100              | mV   |

| Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | ΔV <sub>SSAD</sub> | -100              | 0                 | +100              | mV   |

| Ref voltage high                            |                                                                             | V <sub>REFH</sub>  | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V    |

| Ref voltage low                             |                                                                             | V <sub>REFL</sub>  | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V    |

| Input voltage                               |                                                                             | V <sub>ADIN</sub>  | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |

| Input capacitance                           |                                                                             | C <sub>ADIN</sub>  | _                 | 4.5               | 5.5               | pF   |

| Input resistance                            |                                                                             | R <sub>ADIN</sub>  | _                 | 3                 | 5                 | kΩ   |

| Analog source resistance<br>External to MCU | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>    |                   |                   | 5<br>10           | kΩ   |

|                                             | 8-bit mode (all valid f <sub>ADCK</sub> )                                   |                    | _                 | _                 | 10                |      |

| ADC conversion clock frequency              | High speed (ADLPC = 0)                                                      | f <sub>ADCK</sub>  | 0.4               | _                 | 8.0               | MHz  |

|                                             | Low power (ADLPC = 1)                                                       |                    | 0.4               | _                 | 4.0               |      |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> dc potential difference.

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER

- 3. DATUM PLANE H IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS L, M AND N TO BE DETERMINED AT DATUM PLANE H.

5. DIMENSIONS TO BE DETERMINED AT SEATING PLANE T.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

/1. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE DIMENSION TO EXCEED 0.53. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA                      | L OUTLINE    | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|--------------------------------|--------------|------------------|-------------|

| TITLE:                                                  |                                | DOCUMENT NE  | RE∨: D           |             |

| 44 LD LQFP,<br>10 X 10 PKG, 0.8 PITCH, 1.               | CASE NUMBER: 824D-02 26 FEB 20 |              |                  |             |

|                                                         |                                | STANDARD: JE | DEC MS-026 BCB   |             |