### NXP USA Inc. - S9S08AW60E5MPUE Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 54                                                                      |

| Program Memory Size        | 60KB (60K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08aw60e5mpue |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

## Title

Page

# Chapter 15 Development Support

| Introduct | ion                                                                                                                                                               | 261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.1    |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Backgrou  | and Debug Controller (BDC)                                                                                                                                        | 262                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.2.1    | BKGD Pin Description                                                                                                                                              | 263                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.2.2    | Communication Details                                                                                                                                             | 264                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.2.3    | BDC Commands                                                                                                                                                      | 268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.2.4    | BDC Hardware Breakpoint                                                                                                                                           | 270                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| On-Chip   | Debug System (DBG)                                                                                                                                                | 271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.3.1    | Comparators A and B                                                                                                                                               | 271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.3.2    |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15.3.3    | Change-of-Flow Information                                                                                                                                        | 272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.3.4    | Tag vs. Force Breakpoints and Triggers                                                                                                                            | 272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.3.5    | Trigger Modes                                                                                                                                                     | 273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.3.6    | Hardware Breakpoints                                                                                                                                              | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Register  | Definition                                                                                                                                                        | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.4.1    | BDC Registers and Control Bits                                                                                                                                    | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.4.2    | System Background Debug Force Reset Register (SBDFR)                                                                                                              | 277                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.4.3    | DBG Registers and Control Bits                                                                                                                                    | 278                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 15.1.1<br>Backgrou<br>15.2.1<br>15.2.2<br>15.2.3<br>15.2.4<br>On-Chip<br>15.3.1<br>15.3.2<br>15.3.3<br>15.3.4<br>15.3.5<br>15.3.6<br>Register<br>15.4.1<br>15.4.2 | Background Debug Controller (BDC)15.2.1BKGD Pin Description15.2.2Communication Details15.2.3BDC Commands15.2.4BDC Hardware BreakpointOn-Chip Debug System (DBG)15.3.1Comparators A and B15.3.2Bus Capture Information and FIFO Operation15.3.3Change-of-Flow Information15.3.4Tag vs. Force Breakpoints and Triggers15.3.5Trigger Modes15.3.6Hardware BreakpointsRegister Definition15.4.1BDC Registers and Control Bits15.4.2System Background Debug Force Reset Register (SBDFR) |

# Appendix A Electrical Characteristics and Timing Specifications

| A.1  | Introducti | on                                      |     |

|------|------------|-----------------------------------------|-----|

| A.2  | Parameter  | r Classification                        |     |

| A.3  | Absolute   | Maximum Ratings                         |     |

| A.4  | Thermal (  | Characteristics                         |     |

| A.5  | ESD Prot   | ection and Latch-Up Immunity            |     |

| A.6  | DC Chara   | cteristics                              |     |

| A.7  | Supply C   | urrent Characteristics                  | 291 |

| A.8  |            | racteristics                            |     |

| A.9  |            | Clock Generation Module Characteristics |     |

|      | A.9.1      | ICG Frequency Specifications            |     |

| A.10 | AC Chara   | ncteristics                             |     |

|      | A.10.1     | Control Timing                          |     |

|      | A.10.2     | Timer/PWM (TPM) Module Timing           |     |

| A.11 | SPI Chara  | acteristics                             |     |

| A.12 | FLASH S    | pecifications                           |     |

| A.13 | EMC Per    | formance                                | 307 |

|      | A.13.1     | Radiated Emissions                      |     |

|      | A.13.2     | Conducted Transient Susceptibility      | 307 |

MC9S08AW60 Data Sheet, Rev 2

Table 1-3 lists the functional versions of the on-chip modules.

#### Table 1-3. Versions of On-Chip Modules

| Module                          | Version    |   |

|---------------------------------|------------|---|

| Analog-to-Digital Converter     | (S08ADC10) | 1 |

| Internal Clock Generator        | (S08ICG)   | 4 |

| Inter-Integrated Circuit        | (S08IIC)   | 1 |

| Keyboard Interrupt              | (S08KBI)   | 1 |

| Serial Communications Interface | (S08SCI)   | 2 |

| Serial Peripheral Interface     | (S08SPI)   | 3 |

| Timer Pulse-Width Modulator     | (S08TPM)   | 2 |

| Central Processing Unit         | (S08CPU)   | 2 |

| Debug Module                    | (DBG)      | 2 |

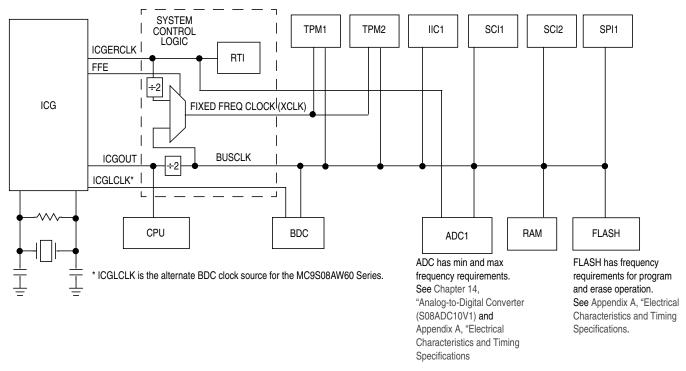

## **1.3 System Clock Distribution**

### Figure 1-2. System Clock Distribution Diagram

Some of the modules inside the MCU have clock source choices. Figure 1-2 shows a simplified clock connection diagram. The ICG supplies the clock sources:

- ICGOUT is an output of the ICG module. It is one of the following:

- The external crystal oscillator

- An external clock source

**Chapter 4 Memory**

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08AW60 Series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC2. The LVD is disabled upon entering any of the stop modes unless the LVDSE bit is set. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be greater.

## 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the chip in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

## 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

## 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF will be set and an LVD interrupt will occur.

### 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC2. Setting the LVW trip voltage equal to the LVD trip voltage is not recommended. Typical use of the LVW would be to select  $V_{LVWH}$  and  $V_{LVDL}$ .

## 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1-kHz internal clock or an external clock if available. The 1-kHz internal clock source is completely independent of any bus clock source and is used only by the RTI module and, on some MCUs, the COP watchdog. To use an external clock source, it must be available and active. The RTICLKS bit in SRTISC is used to select the RTI clock source.

| Field    | Description                                                                                                                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>ICG | Internal Clock Generation Module Reset — Reset was caused by an ICG module reset.         0 Reset not caused by ICG module.         1 Reset caused by ICG module.                                                                                                               |

| 1<br>LVD | <ul> <li>Low Voltage Detect — If the LVDRE and LVDSE bits are set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

### Table 5-3. SRS Register Field Descriptions (continued)

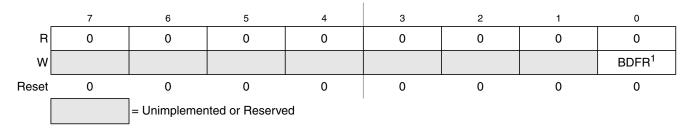

### 5.9.3 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return \$00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

### Table 5-4. SBDFR Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE may be used to allow an external debug host to force a target system reset. Writing logic 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

### 5.9.4 System Options Register (SOPT)

This register may be read at any time. Bits 3 and 2 are unimplemented and always read 0. This is a write-once register so only the first write after reset is honored. Any subsequent attempt to write to SOPT (intentionally or unintentionally) is ignored to avoid accidental changes to these sensitive settings. SOPT should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

Chapter 6 Parallel Input/Output

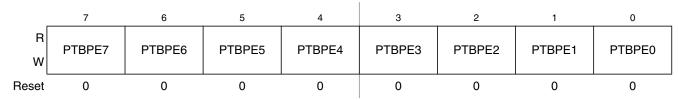

# 6.7.4 Port B Pin Control Registers (PTBPE, PTBSE, PTBDS)

In addition to the I/O control, port B pins are controlled by the registers listed below.

Figure 6-16. Internal Pullup Enable for Port B (PTBPE)

### Table 6-9. PTBPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBPE[7:0] | <ul> <li>Internal Pullup Enable for Port B Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTB pin. For port B pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port B bit n.</li> <li>1 Internal pullup device enabled for port B bit n.</li> </ul> |

| _     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| R     | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| w     | TIDOLI | TIDOLO | TIDOLO | TIDOL4 | TIDOLO | TIDOLZ | TIDOLI | TIDOLO |

| Reset | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-17. Output Slew Rate Control Enable (PTBSE)

### Table 6-10. PTBSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBSE[7:0] | <ul> <li>Output Slew Rate Control Enable for Port B Bits— Each of these control bits determine whether output slew rate control is enabled for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port B bit n.</li> <li>1 Output slew rate control enabled for port B bit n.</li> </ul> |

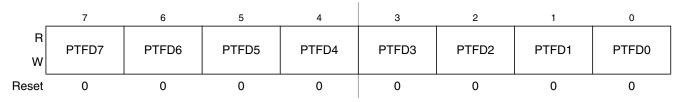

## 6.7.11 Port F I/O Registers (PTFD and PTFDD)

Port F parallel I/O function is controlled by the registers listed below.

### Figure 6-34. Port F Data Register (PTFD)

| Table 6-27. | PTFD | Register | Field | Descriptions |

|-------------|------|----------|-------|--------------|

|-------------|------|----------|-------|--------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFD[7:0] | Port F Data Register Bits— For port F pins that are inputs, reads return the logic level on the pin. For port F pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTFD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDD7 | PTFDD6 | PTFDD5 | PTFDD4 | PTFDD3 | PTFDD2 | PTFDD1 | PTFDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-35. Data Direction for Port F (PTFDD)

### Table 6-28. PTFDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 7:0        | Data Direction for Port F Bits — These read/write bits control the direction of port F pins and what is read for |

| PTFDD[7:0] | PTFD reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port F bit n and PTFD reads return the contents of PTFDn.                            |

#### Chapter 6 Parallel Input/Output

| _     | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     |   | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| w     |   | FIGD30 | FIGDS5 | FIGD34 | FIGDSS | FIGD52 | FIGDST | FIGDSU |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-43. Output Drive Strength Selection for Port G (PTGDS)

### Table 6-36. PTGDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGDS[6:0] | <ul> <li>Output Drive Strength Selection for Port G Bits — Each of these control bits selects between low and high output drive for the associated PTG pin.</li> <li>0 Low output drive enabled for port G bit n.</li> <li>1 High output drive enabled for port G bit n.</li> </ul> |

### Chapter 8 Internal Clock Generator (S08ICGV4)

selected, this pin is not used by the ICG. The oscillator is capable of being configured to provide a higher amplitude output for improved noise immunity. This mode of operation is selected by HGO = 1.

## 8.2.3 External Clock Connections

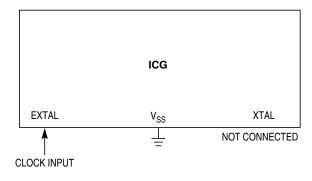

If an external clock is used, then the pins are connected as shown Figure 8-4.

Figure 8-4. External Clock Connections

## 8.2.4 External Crystal/Resonator Connections

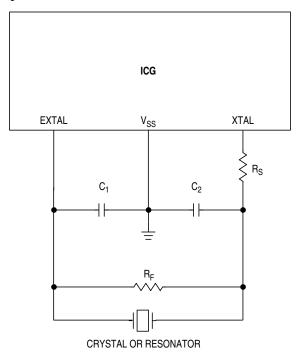

If an external crystal/resonator frequency reference is used, then the pins are connected as shown in Figure 8-5. Recommended component values are listed in the Electrical Characteristics chapter.

Figure 8-5. External Frequency Reference Connection

MC9S08AW60 Data Sheet, Rev 2

Chapter 8 Internal Clock Generator (S08ICGV4)

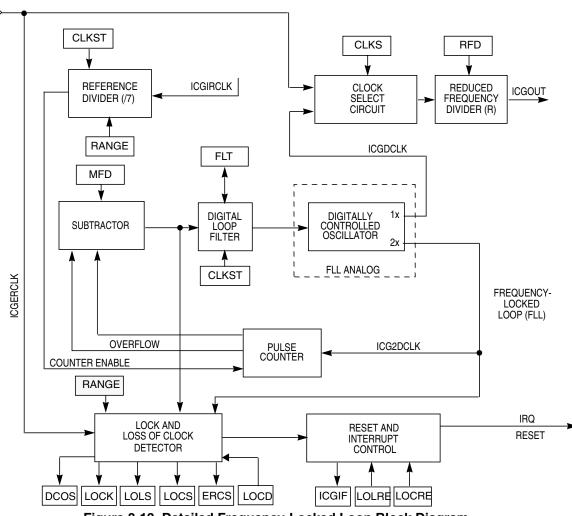

entering off mode. If CLKS bits are set to 01 or 11 coming out of the Off state, the ICG enters this mode until ICGDCLK is stable as determined by the DCOS bit. After ICGDCLK is considered stable, the ICG automatically closes the loop by switching to FLL engaged (internal or external) as selected by the CLKS bits.

Figure 8-13. Detailed Frequency-Locked Loop Block Diagram

# 8.4.3 FLL Engaged, Internal Clock (FEI) Mode

FLL engaged internal (FEI) is entered when any of the following conditions occur:

- CLKS bits are written to 01

- The DCO clock stabilizes (DCOS = 1) while in SCM upon exiting the off state with CLKS = 01

In FLL engaged internal mode, the reference clock is derived from the internal reference clock ICGIRCLK, and the FLL loop will attempt to lock the ICGDCLK frequency to the desired value, as selected by the MFD bits.

## 8.4.9 FLL Loss-of-Clock Detection

The reference clock and the DCO clock are monitored under different conditions (see Table 8-8). Provided the reference frequency is being monitored, ERCS = 1 indicates that the reference clock meets minimum frequency requirements. When the reference and/or DCO clock(s) are being monitored, if either one falls below a certain frequency,  $f_{LOR}$  and  $f_{LOD}$ , respectively, the LOCS status bit will be set to indicate the error. LOCS will remain set until it is acknowledged or until the MCU is reset. LOCS is cleared by reading ICGS1 then writing 1 to ICGIF (LOCRE = 0), or by a loss-of-clock induced reset (LOCRE = 1), or by any MCU reset.

If the ICG is in FEE, a loss of reference clock causes the ICG to enter SCM, and a loss of DCO clock causes the ICG to enter FBE mode. If the ICG is in FBE mode, a loss of reference clock will cause the ICG to enter SCM. In each case, the CLKST and CLKS bits will be automatically changed to reflect the new state.

If the ICG is in FEE mode when a loss of clock occurs and the ERCS is still set to 1, then the CLKST bits are set to 10 and the ICG reverts to FBE mode.

A loss of clock will also cause a loss of lock when in FEE or FEI modes. Because the method of clearing the LOCS and LOLS bits is the same, this would only be an issue in the unlikely case that LOLRE = 1 and LOCRE = 0. In this case, the interrupt would be overridden by the reset for the loss of lock.

| Mode                | CLKS     | REFST | ERCS                   | External Reference<br>Clock<br>Monitored? | DCO Clock<br>Monitored? |

|---------------------|----------|-------|------------------------|-------------------------------------------|-------------------------|

| Off                 | 0X or 11 | Х     | Forced Low             | No                                        | No                      |

|                     | 10       | 0     | Forced Low             | No                                        | No                      |

|                     | 10       | 1     | Real-Time <sup>1</sup> | Yes <sup>(1)</sup>                        | No                      |

| SCM                 | 0X       | Х     | Forced Low             | No                                        | Yes <sup>2</sup>        |

| (CLKST = 00)        | 10       | 0     | Forced High            | No                                        | Yes <sup>(2)</sup>      |

|                     | 10       | 1     | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

|                     | 11       | Х     | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

| FEI                 | 0X       | Х     | Forced Low             | No                                        | Yes                     |

| (CLKST = 01)        | 11       | Х     | Real-Time              | Yes                                       | Yes                     |

| FBE                 | 10       | 0     | Forced High            | No                                        | No                      |

| (CLKST = 10)        | 10       | 1     | Real-Time              | Yes                                       | No                      |

| FEE<br>(CLKST = 11) | 11       | Х     | Real-Time              | Yes                                       | Yes                     |

Table 8-8. Clock Monitoring (When LOCD = 0)

<sup>1</sup> If ENABLE is high (waiting for external crystal start-up after exiting stop).

<sup>2</sup> DCO clock will not be monitored until DCOS = 1 upon entering SCM from off or FLL bypassed external mode.

## 12.4.2 SPI Interrupts

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

### 12.4.3 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS}$  pin (provided the  $\overline{SS}$  pin is configured as the mode fault input signal). The  $\overline{SS}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK, MOSI, and MISO (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPI1C1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

Chapter 12 Serial Peripheral Interface (S08SPIV3)

Chapter 13 Inter-Integrated Circuit (S08IICV1)

Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

- Average the result by converting the analog input many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and averaging. Noise that is synchronous to ADCK cannot be averaged out.

## 14.7.2.4 Code Width and Quantization Error

The ADC quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

### $1LSB = (V_{REFH} - V_{REFL}) / 2^{N}$ Eqn. 14-2

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm 1/2$ LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

## 14.7.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error ( $E_{ZS}$ ) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is used.

- Full-scale error  $(E_{FS})$  This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

## 14.7.2.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the

#### Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around 1/2LSB and will increase with noise. This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 14.7.2.3 will reduce this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values which are never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and to have no missing codes.

# 15.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 15.3.6, "Hardware Breakpoints."

## 15.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

## 15.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

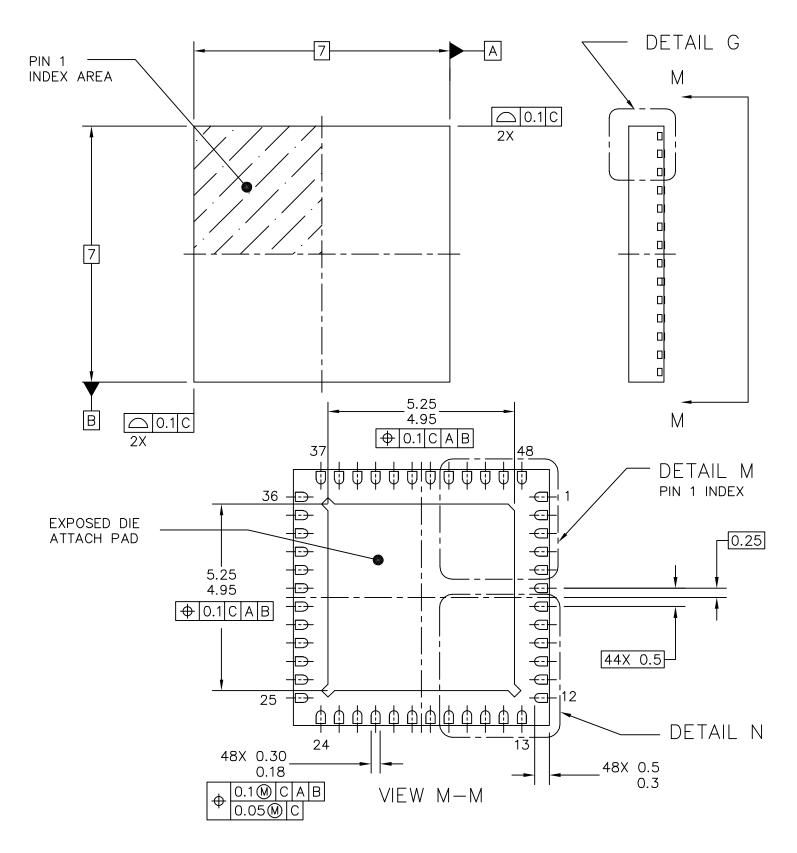

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICA    | L OUTLINE         | PRINT VERSION NO | T TO SCALE |

|---------------------------------------------------------|--------------|-------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED                               | QUAD         | DOCUMENT NO       | ): 98ARH99048A   | REV: F     |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER  | : 1314–05         | 05 DEC 2005      |            |

| 48 TERMINAL, 0.5 PITCH (7                               | STANDARD: JE | DEC-MO-220 VKKD-2 | 2                |            |

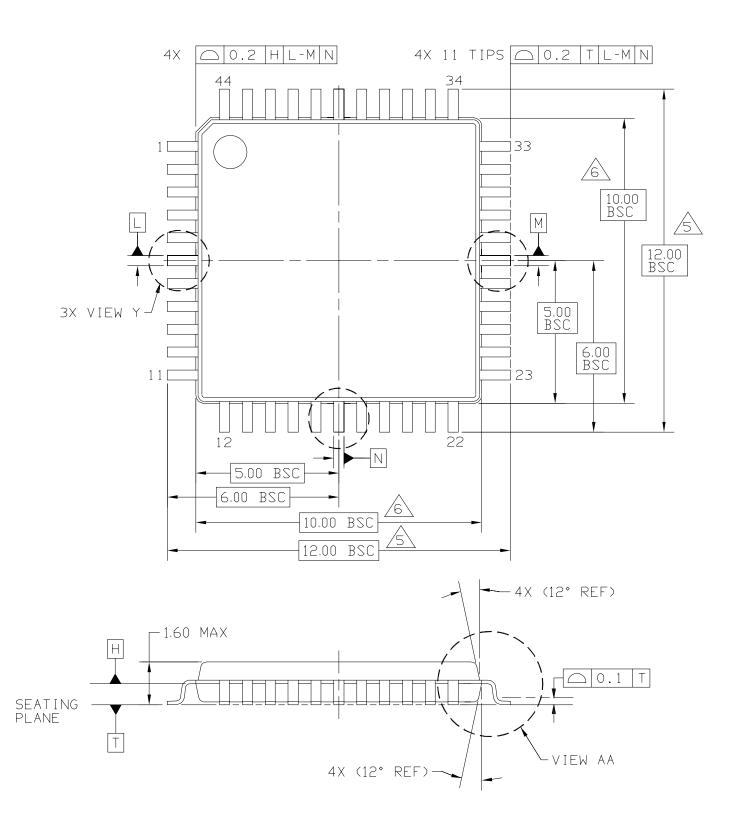

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |             | L OUTLINE      | PRINT VERSION NE | IT TO SCALE |

|---------------------------------------------------------|-------------|----------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NE | ]: 98ASS23225W | RE∨: D           |             |

| 44 LD LQFP,<br>10 X 10 PKG, 0.8 PITCH,                  | CASE NUMBER | 8:824D-02      | 26 FEB 2007      |             |

|                                                         |             | STANDARD: JE   | DEC MS-026-BCB   |             |

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS A-B AND -D- TO BE DETERMINED AT DATUM PLANE -H-.

5 dimensions to be determined at seating plane -C-.

- DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- Z DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDICTION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE |                | PRINT VERSION NOT TO SCALE |  |

|---------------------------------------------------------|--------------------|----------------|----------------------------|--|

| TITLE:                                                  | DOCUMENT NO        | ): 98ASB42844B | REV: B                     |  |

| 64LD QFP (14 X 1                                        | CASE NUMBER        | R: 840B-01     | 20 MAY 2005                |  |

|                                                         | STANDARD: NO       | N-JEDEC        |                            |  |