#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3865axi-019 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

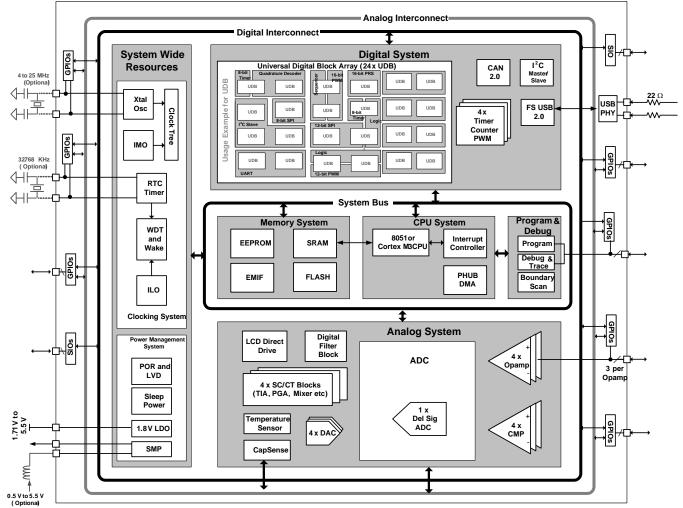

# 1. Architectural Overview

Introducing the CY8C38 family of ultra low-power, flash Programmable System-on-Chip (PSoC<sup>®</sup>) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C38 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

# Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C38 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low-power UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C38 family these blocks can include four 16-bit timers, counters, and PWM blocks; I<sup>2</sup>C slave, master, and multimaster; FS USB; and Full CAN 2.0b.

# 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | А             | Clear accumulator                     | 1     | 1      |

| CPL | А             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | А             | Rotate accumulator left through carry | 1     | 1      |

| RR  | А             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

# 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

### Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

### 4.4.4.1 Simple DMA

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

# 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

| Register Address | 7       | 6         | 5                         | 4 | 3                             | 2         | 1                              | 0        |              |  |      |             |  |

|------------------|---------|-----------|---------------------------|---|-------------------------------|-----------|--------------------------------|----------|--------------|--|------|-------------|--|

| 0x00             | PRT3RE  | DM[1:0]   | PRT2RDM[1:0] PRT1RDM[1:0] |   | i:0] PRT2RDM[                 |           | ] PRT2RDM[1:0] PRT1RDM[1:0] PR |          | PRT1RDM[1:0] |  | PRT0 | RT0RDM[1:0] |  |

| 0x01             | PRT12R  | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0] |   | DM[1:0] PRT4RDM[ <sup>2</sup> |           | RDM[1:0]                       |          |              |  |      |             |  |

| 0x02             | XRESMEN | DBGEN     |                           |   | PRT15                         | 5RDM[1:0] |                                |          |              |  |      |             |  |

| 0x03             |         | DIG_PHS_I | DLY[3:0] ECCEN DPS[       |   | DLY[3:0]                      |           | [1:0]                          | CFGSPEED |              |  |      |             |  |

The details for individual fields and their factory default settings are shown in Table 5-3:.

# Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                      | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     |                                                                                                                                  | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as<br>an external reset. See "Pin Descriptions" on<br>page 12, XRES description. | 0 (default for 68-pin, 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                     |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                     | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during<br>the device boot process, for faster boot or<br>low-power operation           | 0 (default) - 12 MHz IMO<br>1 - 48 MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug<br>port. See "Programming, Debug Interfaces,<br>Resources" on page 65.          | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 23. |                                                                                                                               |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                           | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 113.

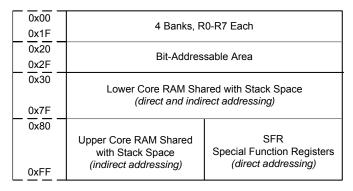

# 5.7 Memory Map

The CY8C38 8051 memory map is very similar to the MCS-51 memory map.

### 5.7.1 Code Space

The CY8C38 8051 code space is 64 KB. Only main flash exists in this space. See the Flash Program Memory on page 23.

### 5.7.2 Internal Data Space

The CY8C38 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 23) and a 128-byte space for special function registers (SFR). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

### Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 13.

# 5.7.3 SFRs

The SFR space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | -    | -    | -    | -   | -   |

| 0×F0    | В          | -          | SFRPRT12SEL | -    | -    | -    | -   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | -    | -    | -    | -   | -   |

| 0×E0    | ACC        | -          | -           | -    | -    | -    | -   | -   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | -    | -    | -    | -   | -   |

| 0×D0    | PSW        | -          | -           | -    | -    | -    | -   | -   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | -    | -    | -   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | -    | -    | -    | -   | -   |

| 0×B8    |            |            |             | -    | -    | -    | -   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | -    | -    | -    | -   | -   |

| 0×A8    | IE         | -          | -           | -    | -    | -    | -   | -   |

| 0×A0    | P2AX       | -          | SFRPRT1SEL  | -    | -    | -    | -   | -   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | -    | -    | -    | -   | -   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | -           | DPX0 | -    | DPX1 | -   | -   |

| 0×88    | -          | SFRPRT0PS  | SFRPRT0SEL  | -    | -    | -    | _   | -   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | -   |

# Table 5-4. SFR Map

The CY8C38 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C38 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C38 family.

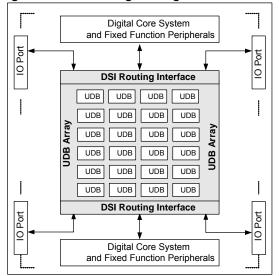

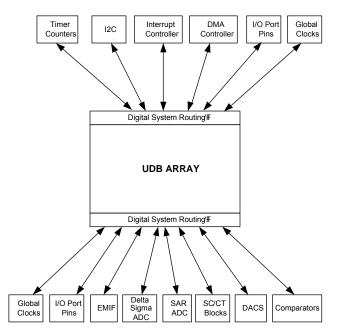

# 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

- UDB These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal digital block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

- Digital system interconnect (DSI) Digital signals from UDBs, fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the digital system interconnect to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the universal digital block array.

#### Figure 7-1. CY8C38 Digital Programmable Architecture

# 7.1 Example Peripherals

The flexibility of the CY8C38 family's UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the data sheet, and the list is always growing. An example of a component available for use in CY8C38 family, but, not explicitly called out in this data sheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- u UART

- 🛛 SPI

- Functions

- B EMIF

- □ PWMs

- Timers

- Counters

- Logic

- NOT

- ם OR

- D XOR

- ם AND

### 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Amplifiers

- □ TIA

- D PGA

- □ opamp

- ADC

- Delta-sigma

- DACs

- Current

- □ Voltage

- Comparators

- Mixers

## Figure 7-9. Digital System Interconnect

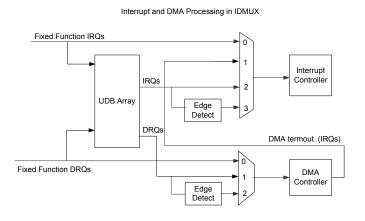

Interrupt and DMA routing is very flexible in the CY8C38 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

# Figure 7-10. Interrupt and DMA Processing in the IDMUX

# 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

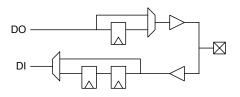

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

# Figure 7-11. I/O Pin Synchronization Routing

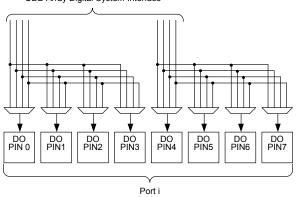

Figure 7-12. I/O Pin Output Connectivity

8 IO Data Output Connections from the UDB Array Digital System Interface

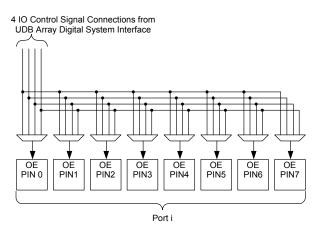

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

### Figure 7-13. I/O Pin Output Enable Connectivity

# 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[16]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master)<sup>[17]</sup>. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup

functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

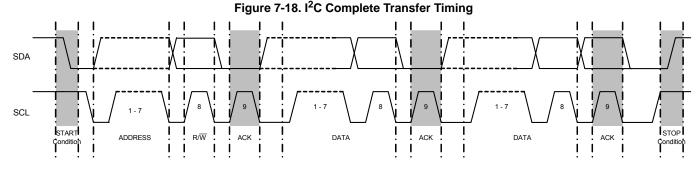

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

# 7.8.1 External Electrical Connections

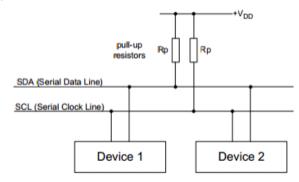

As Figure 7-19 shows, the  $I^2C$  bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

# Figure 7-19. Connection of Devices to the I<sup>2</sup>C Bus

#### Notes

- 16. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 80 for details.

- 17. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

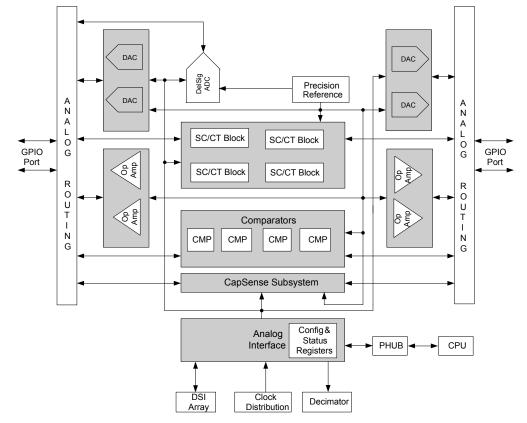

Figure 8-1. Analog Subsystem Block Diagram

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions (PGA, transimpedance amplifier, voltage DAC, current DAC, and so on). The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

# 8.1 Analog Routing

The CY8C38 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C38 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C38, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2 on page 58.

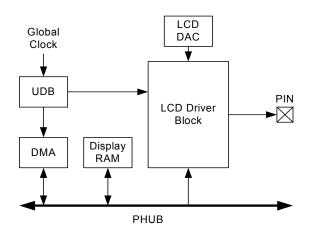

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

### Figure 8-10. LCD System

# 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through the DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

### 8.7 CapSense

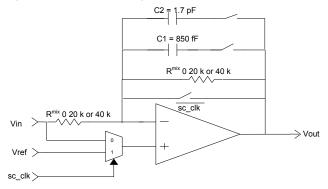

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a Delta-sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

# 8.9 DAC

The CY8C38 parts contain up to four Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features:

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25 percent of gain error

- Source and sink option for current output

- High and low speed / power modes

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

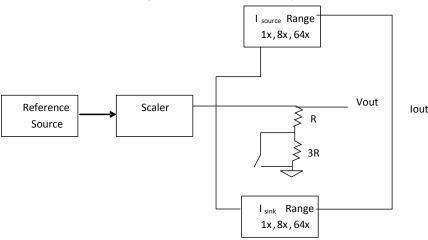

# Figure 8-11. DAC Block Diagram

### 8.9.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 31.875  $\mu$ A, 0 to 255  $\mu$ A, and 0 to 2.04 mA. The IDAC can be configured to source or sink current.

### 8.9.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.02 V and 0 to 4.08 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

### 8.10 Up/Down Mixer

In continuous time mode, the SC/CT block components are used to build an up or down mixer. Any mixing application contains an input signal frequency and a local oscillator frequency. The polarity of the clock, Fclk, switches the amplifier between inverting or noninverting gain. The output is the product of the input and the switching function from the local oscillator, with frequency components at the local oscillator plus and minus the signal frequency (Fclk + Fin and Fclk – Fin) and reduced-level frequency components at odd integer multiples of the local oscillator frequency. The local oscillator frequency is provided by the selected clock source for the mixer.

Continuous time up and down mixing works for applications with input signals and local oscillator frequencies up to 1 MHz.

### Figure 8-12. Mixer Configuration

# 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

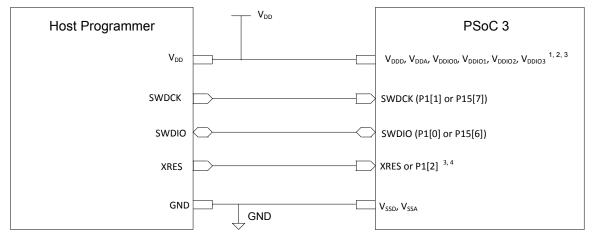

# 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8  $\mu$ s (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

<sup>1</sup> The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDI01</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDI01</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

<sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48pin devices, but use dedicated XRES pin for rest of devices.

# 9.3 Debug Features

Using the JTAG or SWD interface, the CY8C38 supports the following debug features:

- Halt and single-step the CPU

- View and change CPU and peripheral registers, and RAM addresses

- Eight program address breakpoints

- One memory access breakpoint—break on reading or writing any memory address and data value

- Break on a sequence of breakpoints (non recursive)

- Debugging at the full speed of the CPU

- Compatible with PSoC Creator and MiniProg3 programmer and debugger

- Standard JTAG programming and debugging interfaces make CY8C38 compatible with other popular third-party tools (for example, ARM / Keil)

# 9.4 Trace Features

The CY8C38 supports the following trace features when using JTAG or SWD:

- Trace the 8051 program counter (PC), accumulator register (ACC), and one SFR / 8051 core RAM register

- Trace depth up to 1000 instructions if all registers are traced, or 2000 instructions if only the PC is traced (on devices that include trace memory)

- Program address trigger to start tracing

- Trace windowing, that is, only trace when the PC is within a given range

- Two modes for handling trace buffer full: continuous (overwriting the oldest trace data) or break when trace buffer is full

# 9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also be used independently. SWV data is output on the JTAG interface's TDO pin. If using SWV, you must configure the device for SWD, not JTAG. SWV is not supported with the JTAG interface.

SWV is ideal for application debug where it is helpful for the firmware to output data similar to 'printf' debugging on PCs. The SWV is ideal for data monitoring, because it requires only a single pin and can output data in standard UART format or Manchester encoded format. For example, it can be used to tune a PID control loop in which the output and graphing of the three error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

- 32 virtual channels, each 32 bits long

- Simple, efficient packing and serializing protocol

- Supports standard UART format (N81)

# 9.6 Programming Features

The JTAG and SWD interfaces provide full programming support. The entire device can be erased, programmed, and verified. You can increase flash protection levels to protect firmware IP. Flash protection can only be reset after a full device erase. Individual flash blocks can be erased, programmed, and verified, if block security settings permit.

### 9.7 Device Security

PSoC 3 offers an advanced security feature called device security, which permanently disables all test, programming, and debug ports, protecting your application from external access. The device security is activated by programming a 32-bit key (0×50536F43) to a Write Once Latch (WOL).

The Write Once Latch is a type of nonvolatile latch (NVL). The cell itself is an NVL with additional logic wrapped around it. Each WOL device contains four bytes (32 bits) of data. The wrapper outputs a '1' if a super-majority (28 of 32) of its bits match a pre-determined pattern (0×50536F43); it outputs a '0' if this majority is not reached. When the output is 1, the Write Once NV latch locks the part out of Debug and Test modes; it also permanently gates off the ability to erase or alter the contents of the latch. Matching all bits is intentionally not required, so that single (or few) bit failures do not deassert the WOL output. The state of the NVL bits after wafer processing is truly random with no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the NVL's nonvolatile cells, and the part is reset. The output of the WOL is only sampled on reset and used to disable the access. This precaution prevents anyone from reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external access only if no flash protection is set (see "Flash Security" on page 23). However, after setting the values in the WOL, a user still has access to the part until it is reset. Therefore, a user can write the key into the WOL, program the flash protection data, and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out through the SWD port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 3 TRM.

### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 9.8 CSP Package Bootloader

A factory-installed bootloader program is included in all devices with CSP packages. The bootloader is compatible with PSoC Creator 3.0 bootloadable project files and has the following features:

- I<sup>2</sup>C-based

- SCLK and SDAT available at P1[6] and P1[7], respectively

- External pull-up resistors required

- I<sup>2</sup>C slave, address 4, data rate = 100 kbps

- Single application

- Wait two seconds for bootload command

- Other bootloader options are as set by the PSoC Creator 3.0 Bootloader Component default

- Occupies the bottom 9K of flash

For more information on this bootloader, see the following Cypress application notes:

- AN89611 PSoC<sup>®</sup> 3 AND PSoC 5LP Getting Started With Chip Scale Packages (CSP)

- AN73854 PSoC 3 and PSoC 5 LP Introduction to Bootloaders

- AN60317 PSoC 3 and PSoC 5 LP I<sup>2</sup>C Bootloader

Note that a PSOC Creator bootloadable project must be associated with .hex and .elf files for a bootloader project that is configured for the target device. Bootloader .hex and .elf files can be found at www.cypress.com/go/PSoC3datasheet.

The factory-installed bootloader can be overwritten using JTAG or SWD programming.

# 11.5.4 Analog Globals

# Table 11-29. Analog Globals Specifications

| Parameter | Description                                                                        | Conditions             | Min | Тур  | Max  | Units |

|-----------|------------------------------------------------------------------------------------|------------------------|-----|------|------|-------|

| Rppag     | Resistance pin-to-pin through P2[4],<br>AGL0, DSM INP, AGL1, P2[5] <sup>[54]</sup> | V <sub>DDA</sub> = 3 V | _   | 1472 | 2200 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through P2[3], amuxbusL, P2[4] <sup>[54]</sup>               | V <sub>DDA</sub> = 3 V | _   | 706  | 1100 | Ω     |

# 11.5.5 Comparator

# Table 11-30. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                           | Min              | Тур | Max                        | Units |

|-------------------|---------------------------------------------------|------------------------------------------------------|------------------|-----|----------------------------|-------|

|                   | Input offset voltage in fast mode                 | Factory trim, $V_{DDA} > 2.7 V$ , $V_{IN} \ge 0.5 V$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5 V$                        | -                |     | 9                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[55]</sup> | Custom trim                                          | -                | -   | 4                          | mV    |

|                   | Input offset voltage in slow mode <sup>[55]</sup> | Custom trim                                          | -                | -   | 4                          | mV    |

|                   | Input offset voltage in ultra<br>low-power mode   | V <sub>DDA</sub> ≤ 4.6 V                             | -                | ±12 | -                          | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                               | -                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Low current / slow mode                              | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Ultra low-power mode<br>V <sub>DDA</sub> ≤ 4.6 V     | V <sub>SSA</sub> | -   | V <sub>DDA</sub> –<br>1.15 | V     |

| CMRR              | Common mode rejection ratio                       |                                                      | -                | 50  | -                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[56]</sup>       |                                                      | -                | _   | 400                        | μA    |

|                   | Low current mode/slow mode <sup>[56]</sup>        |                                                      | -                | _   | 100                        | μA    |

|                   | Ultra low-power mode <sup>[56]</sup>              | V <sub>DDA</sub> ≤ 4.6 V                             | -                | 6   | -                          | μA    |

# Table 11-31. Comparator AC Specifications

| Parameter         | Description                                         | Conditions                                                        | Min | Тур | Max | Units |

|-------------------|-----------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

|                   | Response time, high current mode <sup>[56]</sup>    | 50 mV overdrive, measured pin-to-pin                              | -   | 75  | 110 | ns    |

| T <sub>RESP</sub> | Response time, low current mode <sup>[56]</sup>     | 50 mV overdrive, measured pin-to-pin                              | _   | 155 | 200 | ns    |

|                   | Response time, ultra low-power mode <sup>[56]</sup> | 50 mV overdrive, measured<br>pin-to-pin, V <sub>DDA</sub> ≤ 4.6 V | _   | 55  | -   | μs    |

55. The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

56. Based on device characterization (Not production tested).

Notes

54. The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

# 11.9.4 kHz External Crystal Oscillator

# Table 11-83. kHzECO DC Specifications<sup>[78]</sup>

| Parameter       | Description       | Conditions                | Min | Тур  | Max | Units |

|-----------------|-------------------|---------------------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current | Low-power mode; CL = 6 pF | -   | 0.25 | 1.0 | μA    |

| DL              | Drive level       |                           | -   | -    | 1   | μW    |

# Table 11-84. kHzECO AC Specifications

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | _   | 32.768 | _   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | _   | 1      | _   | S     |

# 11.9.5 External Clock Reference

# Table 11-85. External Clock Reference AC Specifications<sup>[78]</sup>

| Parameter | Description              | Conditions                         | Min  | Тур | Max | Units |

|-----------|--------------------------|------------------------------------|------|-----|-----|-------|

|           | External frequency range |                                    | 0    | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30   | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.51 | _   | _   | V/ns  |

#### 11.9.6 Phase-Locked Loop

### Table 11-86. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 67 MHz | _   | 400 | _   | μA    |

|                 |                       | In = 3 MHz, Out = 24 MHz | -   | 200 | _   | μA    |

### Table 11-87. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[79]</sup>        |                     | 1   | -   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[80]</sup> | Output of prescaler | 1   | -   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[79]</sup>       |                     | 24  | -   | 67  | MHz   |

|             | Lock time at startup                       |                     | -   | -   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[78]</sup>               |                     | _   | -   | 250 | ps    |

78. Based on device characterization (Not production tested).

79. This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL. 80. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

Notes

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C38 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C38 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

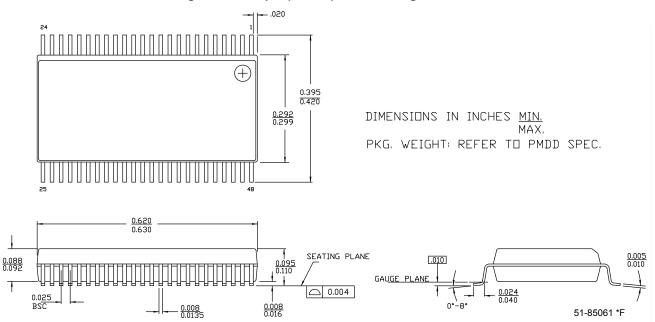

| Table 12-1. | CY8C38 Family | / with Sina | le Cvcle 8051 |

|-------------|---------------|-------------|---------------|

|             |               | , main onig |               |

|                 |                 | MCU        | Cor       | e           |                   |                | An  | alog       |                                        |        |     |          |                      | Dig              | gital  |          |           | I/O  | [83] |        |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|------|--------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[81]</sup> | Opamps | DFB | CapSense | UDBs <sup>[82]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO  | OIBSIO | Package      | JTAG ID <sup>[84]</sup> |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |        |              |                         |

| CY8C3865AXI-019 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 5   | 5        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0×1E013069              |

| CY8C3865LTI-014 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 2   | ۲        | 20                   | 4                | >      | Ι        | 48        | 38   | 8    | 2      | 68-pin QFN   | 0×1E00E069              |

| CY8C3865AXI-204 | 67              | 32         | 8         | 1           | 2                 | 20-bit Del-Sig | 2   | 0          | 0                                      | 0      | -   | 2        | 16                   | 4                | ~      | -        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0x1E0CC069              |

| CY8C3865LTI-205 | 67              | 32         | 8         | 1           | ~                 | 20-bit Del-Sig | 2   | 0          | 0                                      | 0      | I   | ~        | 16                   | 4                | ~      | I        | 48        | 38   | 8    | 2      | 68-pin QFN   | 0x1E0CD069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |        |              |                         |

| CY8C3866LTI-067 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ٢   | ~        | 24                   | 4                | ~      | -        | 31        | 25   | 4    | 2      | 48-pin QFN   | 0×1E043069              |

| CY8C3866PVI-021 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ٢   | ~        | 24                   | 4                | ~      | I        | 31        | 25   | 4    | 2      | 48-pin SSOP  | 0×1E015069              |

| CY8C3866AXI-035 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 2   | ~        | 24                   | 4                | Ι      | ~        | 70        | 62   | 8    | 0      | 100-pin TQFP | 0x1E023069              |

| CY8C3866AXI-039 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | >   | >        | 24                   | 4                | >      | -        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0×1E027069              |

| CY8C3866LTI-030 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | >        | 24                   | 4                | ~      | -        | 48        | 38   | 8    | 2      | 68-pin QFN   | 0×1E01E069              |

| CY8C3866LTI-068 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 31        | 25   | 4    | 2      | 48-pin QFN   | 0×1E044069              |

| CY8C3866AXI-040 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ۲        | 24                   | 4                | ~      | ~        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0×1E028069              |

| CY8C3866PVI-070 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | ~        | 24                   | 4                | -      | ~        | 29        | 25   | 4    | 0      | 48-pin SSOP  | 0×1E046069              |

| CY8C3866AXI-206 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 2   | 2          | 0                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0x1E0CE069              |

| CY8C3866LTI-207 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 2   | 2          | 0                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8    | 2      | 68-pin QFN   | 0x1E0CF069              |

| CY8C3866AXI-208 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 2   | 2          | 2                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 72        | 62   | 8    | 2      | 100-pin TQFP | 0x1E0D0069              |

| CY8C3866LTI-209 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 2   | 2          | 2                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 48        | 38   | 8    | 2      | 68-pin QFN   | 0x1E0D1069              |

| CY8C3866FNI-210 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | >        | 24                   | 4                | ~      | ~        | 48        | 38   | 8    | 2      | 72 WLCSP     | 0x1E0D2069              |

Notes

Analog blocks support a variety of functionality including TIA, PGA, and mixers. See the Example Peripherals on page 44 for more information on how analog blocks can be used.

Be used.

UDBs support a variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 44 for more information on how UDBs can be used.

The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 37 for details on the functionality of each of

these types of I/O.

<sup>84.</sup> The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

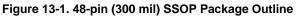

# NOTES:

1. 🗱 HATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE

| PART # | DESCRIPTION |  |  |  |  |  |

|--------|-------------|--|--|--|--|--|

| LT48D  | LEAD FREE   |  |  |  |  |  |

001-45616 \*E

# 14. Acronyms

# Table 14-1. Acronyms Used in this Document

| Acronym | Description                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| abus    | analog local bus                                                                                        |

| ADC     | analog-to-digital converter                                                                             |

| AG      | analog global                                                                                           |

| АНВ     | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU     | arithmetic logic unit                                                                                   |

| AMUXBUS | analog multiplexer bus                                                                                  |

| API     | application programming interface                                                                       |

| APSR    | application program status register                                                                     |

| ARM®    | advanced RISC machine, a CPU architecture                                                               |

| ATM     | automatic thump mode                                                                                    |

| BW      | bandwidth                                                                                               |

| CAN     | Controller Area Network, a communications protocol                                                      |

| CMRR    | common-mode rejection ratio                                                                             |

| CPU     | central processing unit                                                                                 |

| CRC     | cyclic redundancy check, an error-checking protocol                                                     |

| DAC     | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB     | digital filter block                                                                                    |

| DIO     | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA     | direct memory access, see also TD                                                                       |

| DNL     | differential nonlinearity, see also INL                                                                 |

| DNU     | do not use                                                                                              |

| DR      | port write data registers                                                                               |

| DSI     | digital system interconnect                                                                             |

| DWT     | data watchpoint and trace                                                                               |

| ECC     | error correcting code                                                                                   |

| ECO     | external crystal oscillator                                                                             |

| EEPROM  | electrically erasable programmable read-only<br>memory                                                  |

| EMI     | electromagnetic interference                                                                            |

| EMIF    | external memory interface                                                                               |

| EOC     | end of conversion                                                                                       |

| EOF     | end of frame                                                                                            |

| EPSR    | execution program status register                                                                       |

| ESD     | electrostatic discharge                                                                                 |

| ETM     | embedded trace macrocell                                                                                |

# Table 14-1. Acronyms Used in this Document (continued)

| Acronym Description      |                                                        |  |  |  |

|--------------------------|--------------------------------------------------------|--|--|--|

| FIR                      | finite impulse response, see also IIR                  |  |  |  |

| FPB                      | flash patch and breakpoint                             |  |  |  |

| FS                       | full-speed                                             |  |  |  |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |  |  |  |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |  |  |  |

| IC                       | integrated circuit                                     |  |  |  |

| IDAC                     | current DAC, see also DAC, VDAC                        |  |  |  |

| IDE                      | integrated development environment                     |  |  |  |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |  |  |  |

| IIR                      | infinite impulse response, see also FIR                |  |  |  |

| ILO                      | internal low-speed oscillator, see also IMO            |  |  |  |

| IMO                      | internal main oscillator, see also ILO                 |  |  |  |

| INL                      | integral nonlinearity, see also DNL                    |  |  |  |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |  |  |  |

| IPOR                     | initial power-on reset                                 |  |  |  |

| IPSR                     | interrupt program status register                      |  |  |  |

| IRQ                      | interrupt request                                      |  |  |  |

| ITM                      | instrumentation trace macrocell                        |  |  |  |

| LCD                      | liquid crystal display                                 |  |  |  |

| LIN                      | Local Interconnect Network, a communications protocol. |  |  |  |

| LR                       | link register                                          |  |  |  |

| LUT                      | lookup table                                           |  |  |  |

| LVD                      | low-voltage detect, see also LVI                       |  |  |  |

| LVI                      | low-voltage interrupt, see also HVI                    |  |  |  |

| LVTTL                    | low-voltage transistor-transistor logic                |  |  |  |

| MAC                      | multiply-accumulate                                    |  |  |  |

| MCU                      | microcontroller unit                                   |  |  |  |

| MISO                     | master-in slave-out                                    |  |  |  |

| NC                       | no connect                                             |  |  |  |

| NMI                      | nonmaskable interrupt                                  |  |  |  |

| NRZ                      | non-return-to-zero                                     |  |  |  |

| NVIC                     | nested vectored interrupt controller                   |  |  |  |

| NVL                      | nonvolatile latch, see also WOL                        |  |  |  |

| opamp                    | operational amplifier                                  |  |  |  |

| PAL                      | programmable array logic, see also PLD                 |  |  |  |

| PC                       | program counter                                        |  |  |  |

| PCB                      | printed circuit board                                  |  |  |  |

| PGA                      | programmable gain amplifier                            |  |  |  |

|          | Description Title: PSoC <sup>®</sup> 3: CY8C38 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued) Document Number: 001-11729 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|