#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axi-035 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

#### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | А             | Clear accumulator                     | 1     | 1      |

| CPL | А             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | А             | Rotate accumulator left through carry | 1     | 1      |

| RR  | А             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

#### 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

| Register Address | 7            | 6         | 5                         | 4 | 3                    | 2            | 1         | 0        |

|------------------|--------------|-----------|---------------------------|---|----------------------|--------------|-----------|----------|

| 0x00             | PRT3RDM[1:0] |           | PRT2RDM[1:0] PRT1RDM[1:0] |   | DM[1:0] PRT2RDM[1:0] |              | PRT0      | RDM[1:0] |

| 0x01             | PRT12R       | DM[1:0]   | PRT6RDM[1:0] PRT5RDM[1:0] |   | DM[1:0]              | PRT4RDM[1:0] |           |          |

| 0x02             | XRESMEN      | DBGEN     |                           |   |                      | PRT15        | 5RDM[1:0] |          |

| 0x03             |              | DIG_PHS_I | DLY[3:0] ECCEN DPS[       |   | DLY[3:0]             |              | [1:0]     | CFGSPEED |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                      | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     |                                                                                                                                  | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as<br>an external reset. See "Pin Descriptions" on<br>page 12, XRES description. | 0 (default for 68-pin, 72-pin, and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                     |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                     | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during<br>the device boot process, for faster boot or<br>low-power operation           | 0 (default) - 12 MHz IMO<br>1 - 48 MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug<br>port. See "Programming, Debug Interfaces,<br>Resources" on page 65.          | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 23. |                                                                                                                               |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                           | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 113.

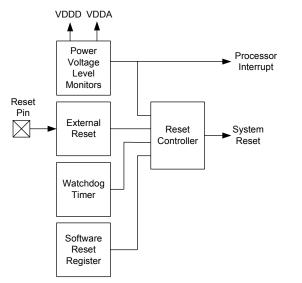

#### Figure 6-8. Resets

The term **device reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to detect and report certain exception conditions. This register is cleared after a power-on reset. For details see the Technical Reference Manual.

#### 6.3.1 Reset Sources

- 6.3.1.1 Power Voltage Level Monitors

- IPOR Initial power-on reset

At initial power on, IPOR monitors the power voltages VDDD, VDDA, VCCD and VCCA. The trip level is not precise. It is set to approximately 1 volt, which is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 150 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

After boot, the IPOR circuit is disabled and voltage supervision is handed off to the precise low-voltage reset (PRES) circuit.

PRES – Precise low voltage reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI – Analog/digital low voltage interrupt, analog high voltage interrupt

Interrupt circuits are available to detect when VDDA and VDDD go outside a voltage range. For AHVI, VDDA is compared to a fixed trip level. For ALVI and DLVI, VDDA and VDDD are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

| Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High |

|--------------------------------------------------------------|

| Voltage Interrupt                                            |

| Interrupt | Supply | Normal Voltage<br>Range | Available Trip Settings               |

|-----------|--------|-------------------------|---------------------------------------|

| DLVI      | VDDD   | 1.71 V–5.5 V            | 1.70 V–5.45 V in 250 mV<br>increments |

| ALVI      | VDDA   | 1.71 V–5.5 V            | 1.70 V–5.45 V in 250 mV<br>increments |

| AHVI      | VDDA   | 1.71 V–5.5 V            | 5.75 V                                |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

The buzz frequency is adjustable, and should be set to be less than the minimum time that any voltage is expected to be out of range. For details on how to adjust the buzz frequency, see the TRM.

- 6.3.1.2 Other Reset Sources

- XRES External reset

PSoC 3 has either a single GPIO pin that is configured as an external reset or a dedicated XRES pin. Either the dedicated XRES pin or the GPIO pin, if configured, holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

After XRES has been deasserted, at least 10  $\mu s$  must elapse before it can be reasserted.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

SRES – Software reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

WRES – Watchdog timer reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

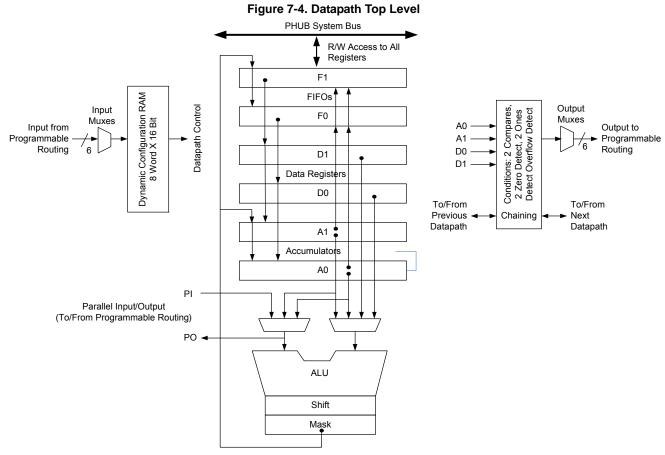

#### 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

#### 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

| Table 7-1. | Working | Datapath | Registers |

|------------|---------|----------|-----------|

|------------|---------|----------|-----------|

| Name      | Function       | Description                                                                                                                                                                                                                 |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                                  |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                                                 |

| F0 and F1 | FIFOs          | These are the primary interface<br>to the system bus. They can be a<br>data source for the data registers<br>and accumulators or they can<br>capture data from the<br>accumulators or ALU. Each FIFO<br>is four bytes deep. |

#### 7.2.2.2 Dynamic Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

#### ALU

The ALU performs eight general purpose functions. They are: Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register.

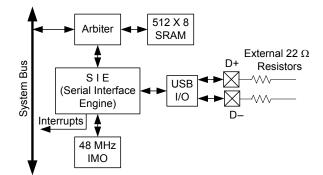

#### 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 37.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

- Automatic memory management with automatic DMA access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

#### Figure 7-16. USB

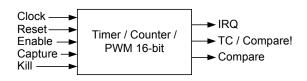

#### 7.7 Timers, Counters, and PWMs

The timer/counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in UDBs as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The timer/counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-17. Timer/Counter/PWM

## 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[16]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master)<sup>[17]</sup>. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup

functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

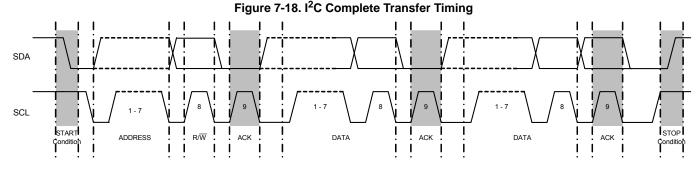

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

#### 7.8.1 External Electrical Connections

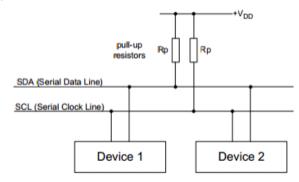

As Figure 7-19 shows, the  $I^2C$  bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

#### Figure 7-19. Connection of Devices to the I<sup>2</sup>C Bus

#### Notes

- 16. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 80 for details.

- 17. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

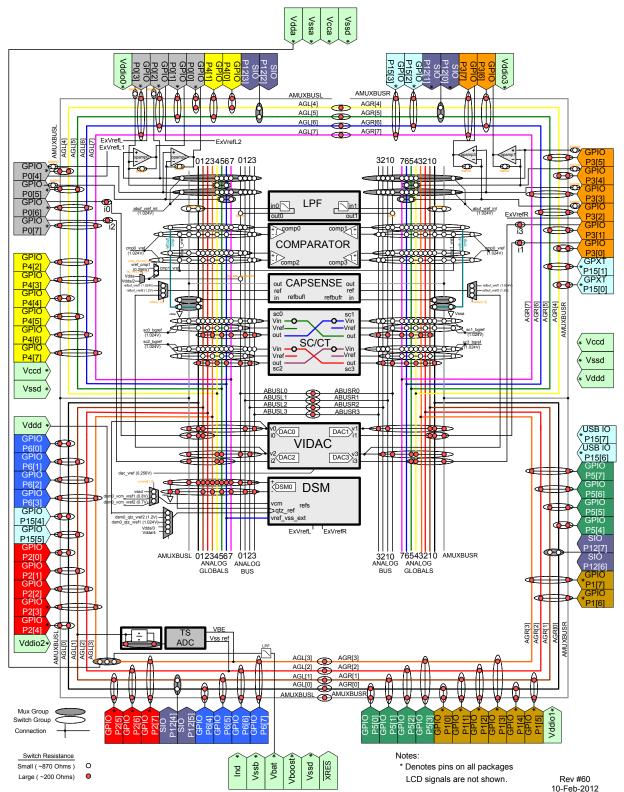

Figure 8-2. CY8C38 Analog Interconnect

To preserve detail of this figure, this figure is best viewed with a PDF display program or printed on a 11" × 17" paper.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C38, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

#### 8.2 Delta-sigma ADC

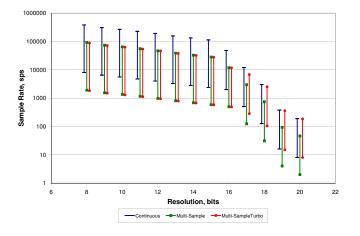

The CY8C38 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for both audio signal processing and measurement applications. The converter's nominal operation is 16 bits at 48 ksps. The ADC can be configured to output 20-bit resolution at data rates of up to 187 sps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 20   | 187                          | -          |

| 16   | 48 k                         | 84         |

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

Table 8-1.

Delta-sigma ADC Performance

#### Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

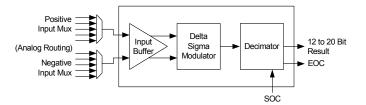

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic

block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

#### Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

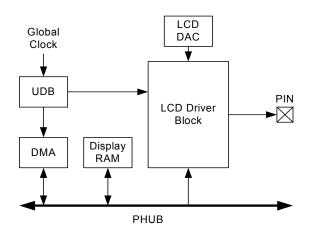

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

#### Figure 8-10. LCD System

#### 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through the DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

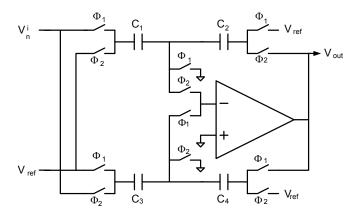

A capacitive sensing method using a Delta-sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

## Figure 8-13. Sample and Hold Topology ( $\Phi$ 1 and $\Phi$ 2 are opposite phases of a clock)

#### 8.11.1 Down Mixer

The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

#### 8.11.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the SC/CT block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low-frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement.

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the PSoC<sup>®</sup> 3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production

device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are fully compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because you cannot access the device later. Because all programming, debug, and test interfaces are disabled when device security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

#### 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

#### **11.2 Device Level Specifications**

Specifications are valid for –40  $^{\circ}C \le T_A \le 85 ^{\circ}C$  and  $T_J \le 100 ^{\circ}C$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.2.1 Device Level Specifications

## Table 11-2. DC Specifications

| Parameter                           | Description                                                                        | Conditions                                                                                                                                                                                      |             | Min       | Typ <sup>[25]</sup> | Max                                                                        | Units |

|-------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|---------------------|----------------------------------------------------------------------------|-------|

| V <sub>DDA</sub>                    | Analog supply voltage and input to analog core regulator                           | Analog core regulat                                                                                                                                                                             | or enabled  | 1.8       | _                   | 5.5                                                                        | V     |

| V <sub>DDA</sub>                    | Analog supply voltage, analog regulator bypassed                                   | Analog core regulator disabled                                                                                                                                                                  |             | 1.71      | 1.8                 | 1.89                                                                       | V     |

| V <sub>DDD</sub>                    | Digital supply voltage relative to V <sub>SSD</sub>                                | Digital core regulato                                                                                                                                                                           | or enabled  | 1.8<br>-  | -                   | V <sub>DDA</sub> <sup>[21]</sup><br>V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | V     |

| V <sub>DDD</sub>                    | Digital supply voltage, digital regulator<br>bypassed                              | Digital core regulato                                                                                                                                                                           | or disabled | 1.71      | 1.8                 | 1.89                                                                       | V     |

| V <sub>DDIO</sub> <sup>[22]</sup>   | I/O supply voltage relative to V <sub>SSIO</sub>                                   |                                                                                                                                                                                                 |             | 1.71<br>- | -                   | V <sub>DDA</sub> <sup>[21]</sup><br>V <sub>DDA</sub> + 0.1 <sup>[27]</sup> | V     |

| V <sub>CCA</sub>                    | Direct analog core voltage input (Analog regulator bypass)                         | Analog core regulat                                                                                                                                                                             | or disabled | 1.71      | 1.8                 | 1.89                                                                       | V     |

| V <sub>CCD</sub>                    | Direct digital core voltage input (Digital regulator bypass)                       | Digital core regulato                                                                                                                                                                           | or disabled | 1.71      | 1.8                 | 1.89                                                                       | V     |

|                                     | Active Mode                                                                        |                                                                                                                                                                                                 |             |           |                     |                                                                            |       |

|                                     | Only IMO and CPU clock enabled. CPU executing simple loop from instruction buffer. | V <sub>DDX</sub> = 2.7 V – 5.5                                                                                                                                                                  | T = -40 °C  | -         | 1.2                 | 2.9                                                                        |       |

|                                     |                                                                                    | V:                                                                                                                                                                                              | I = 25 °C   | -         | 1.2                 | 3.1                                                                        |       |

|                                     |                                                                                    | F <sub>CPU</sub> = 6 MHz <sup>[26]</sup>                                                                                                                                                        | T = 85 °C   | -         | 4.9                 | 7.7                                                                        |       |

|                                     |                                                                                    | V <sub>DDX</sub> = 2.7 V – 5.5                                                                                                                                                                  | T = -40 °C  | 1         | 1.3                 | 2.9                                                                        |       |

|                                     |                                                                                    | V;                                                                                                                                                                                              | T = 25 °C   | 1         | 1.6                 | 3.2                                                                        |       |

|                                     |                                                                                    |                                                                                                                                                                                                 | T = 85 °C   | Ι         | 4.8                 | 7.5                                                                        |       |

|                                     |                                                                                    | V;<br>V;<br>T = 25 °C                                                                                                                                                                           | T = -40 °C  | -         | 2.1                 | 3.7                                                                        |       |

|                                     |                                                                                    |                                                                                                                                                                                                 | T = 25 °C   | -         | 2.3                 | 3.9                                                                        |       |

|                                     |                                                                                    |                                                                                                                                                                                                 | T = 85 °C   | -         | 5.6                 | 8.5                                                                        |       |

| I <sub>DD</sub> <sup>[23, 24]</sup> |                                                                                    | $V_{DDX} = 2.7 V - T = -$                                                                                                                                                                       | T = -40 °C  | -         | 3.5                 | 5.2                                                                        |       |

| DD []                               |                                                                                    | $\begin{array}{c} \text{5.5 V;} \\ \text{F}_{\text{CPU}} = 12 \text{ MHz}^{[26]} \end{array} \begin{array}{c} \text{T} = 25 \ ^{\circ}\text{C} \\ \text{T} = 85 \ ^{\circ}\text{C} \end{array}$ |             | _         | 3.8                 | 5.5                                                                        | mA    |

|                                     | IMO enabled, bus clock and CPU clock                                               |                                                                                                                                                                                                 |             | -         | 7.1                 | 9.8                                                                        |       |

|                                     | enabled. CPU executing program from flash.                                         | $V_{DDY} = 2.7 V_{-}$                                                                                                                                                                           | T = -40 °C  | _         | 6.3                 | 8.1                                                                        | -     |

|                                     |                                                                                    | V <sub>DDX</sub> = 2.7 V–<br>5.5 V;                                                                                                                                                             | T = 25 °C   | _         | 6.6                 | 8.3                                                                        |       |

|                                     |                                                                                    | $F_{CPU} = 24 \text{ MHz}^{[26]}$                                                                                                                                                               | T = 85 °C   | _         | 10                  | 13                                                                         |       |

|                                     |                                                                                    | V <sub>DDX</sub> = 2.7 V - 5.5                                                                                                                                                                  | T = -40 °C  | _         | 11.5                | 13.5                                                                       |       |

|                                     |                                                                                    | V:  T = 25                                                                                                                                                                                      | T = 25 °C   | _         | 12                  | 14                                                                         |       |

|                                     |                                                                                    | $F_{CPU} = 48 \text{ MHz}^{[26]}$                                                                                                                                                               | T = 85 °C   | _         | 15.5                | 18.5                                                                       |       |

|                                     |                                                                                    | $V_{\text{DDX}} = 2.7 \text{ V} - 5.5 \text{ T} = -40$                                                                                                                                          |             | _         | 16                  | 18                                                                         | 1 1   |

|                                     |                                                                                    | V;                                                                                                                                                                                              | T = 25 °C   | _         | 16                  | 18                                                                         | 1     |

|                                     |                                                                                    | $F_{CPU} = 62 \text{ MHz}$ T = 85 °C                                                                                                                                                            |             | _         | 19.5                | 23                                                                         |       |

#### Notes

Notes

21. The power supplies can be brought up in any sequence however once stable V<sub>DDA</sub> must be greater than or equal to all other supplies.

22. The V<sub>DDIO</sub> supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin ≤ V<sub>DDIO</sub> ≤ V<sub>DDA</sub>.

23. Total current for all power domains: digital (I<sub>DDD</sub>), analog (I<sub>DDA</sub>), and I/Os (I<sub>DDIO0, 1, 2, 3</sub>). Boost not included. All I/Os floating.

24. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find the CPU current at the frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

25. V<sub>DDX</sub> = 3.3 V.

26. Based on device specifications (not production tested).

27. Guaranteed by design, not production tested.

Table 11-20.

Opamp AC Specifications

| Parameter      | Description            | Conditions                                               | Min | Тур | Max | Units     |

|----------------|------------------------|----------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = low, 15 pF load                             | 2   | -   | -   | MHz       |

|                |                        | Power mode = medium, 200 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                             | 1.1 | -   | -   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                         | 0.9 | -   | -   | V/µs      |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | V/µs      |

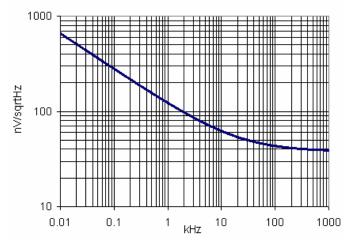

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V,<br>at 100 kHz | _   | 45  | -   | nV/sqrtHz |

# Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, $V_{DDA} = 5V$

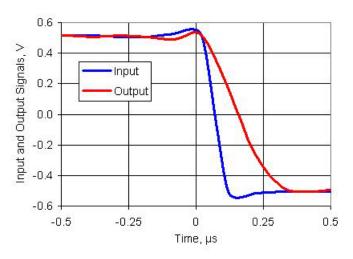

Figure 11-32. Opamp Step Response, Falling

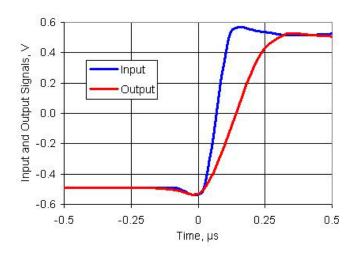

#### Figure 11-31. Opamp Step Response, Rising

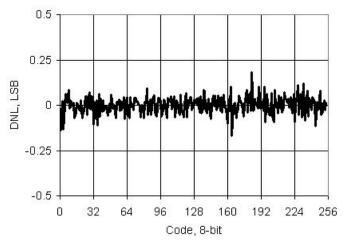

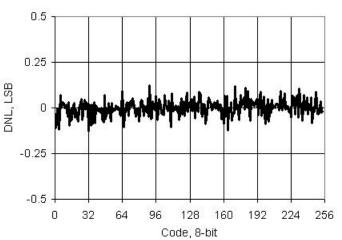

Figure 11-43. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Source Mode

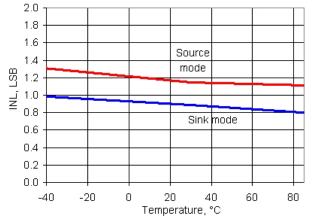

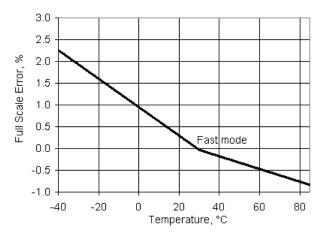

Figure 11-45. IDAC INL vs Temperature, Range = 255  $\mu A,$  High speed mode

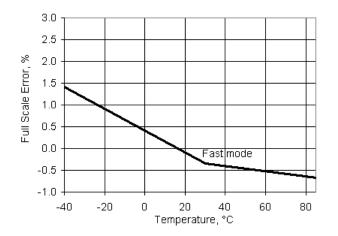

Figure 11-47. IDAC Full Scale Error vs Temperature, Range = 255 μA, Source Mode

Figure 11-44. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Sink Mode

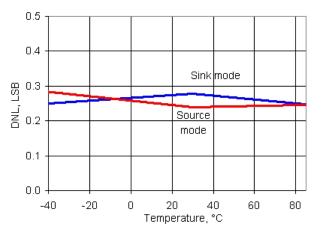

Figure 11-46. IDAC DNL vs Temperature, Range = 255  $\mu$ A, High speed mode

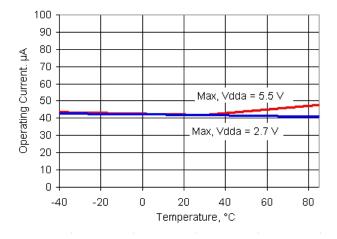

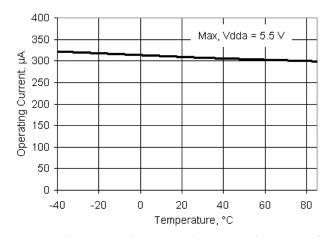

## Figure 11-61. VDAC Operating Current vs Temperature, 1V Mode, Low speed mode

Figure 11-62. VDAC Operating Current vs Temperature, 1 V Mode, High speed mode

#### Table 11-35. VDAC AC Specifications

| Parameter        | Description                            | Conditions                                                      | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                       | -   | -    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                       | -   | -    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.7  | 3    | μs        |

|                  | Voltage noise                          | Range = 1 V, High speed mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | -   | 750  | -    | nV/sqrtHz |

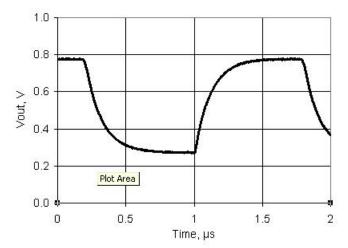

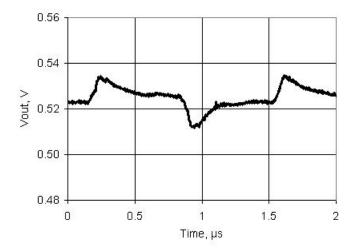

## Figure 11-63. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, High speed mode, $V_{DDA}$ = 5 V

Figure 11-64. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, High speed mode,  $V_{DDA}$  = 5 V

#### 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component data sheet in PSoC Creator.

#### Table 11-47. Counter DC Specifications

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                 | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | _   | μA    |

|           | 48 MHz                    |                                                 | -   | 260 | -   | μA    |

|           | 67 MHz                    |                                                 | -   | 350 | -   | μA    |

#### Table 11-48. Counter AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 67.01 | MHz   |

|           | Capture pulse                 |            | 15  | -   | -     | ns    |

|           | Resolution                    |            | 15  | -   | -     | ns    |

|           | Pulse width                   |            | 15  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  |     |       | ns    |

|           | Enable pulse width            |            | 15  | -   | -     | ns    |

|           | Enable pulse width (external) |            | 30  | -   | -     | ns    |

|           | Reset pulse width             |            | 15  | -   | -     | ns    |

|           | Reset pulse width (external)  |            | 30  | -   | -     | ns    |

#### 11.6.3 Pulse Width Modulation

The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component data sheet in PSoC Creator.

#### Table 11-49. PWM DC Specifications

| Parameter | Description               | Conditions                                     | Min | Тур | Max | Units |

|-----------|---------------------------|------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit PWM, at listed input clock<br>frequency | -   | -   | -   | μA    |

|           | 3 MHz                     |                                                | _   | 15  | -   | μA    |

|           | 12 MHz                    |                                                | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                                | _   | 260 | -   | μA    |

|           | 67 MHz                    |                                                | -   | 350 | _   | μA    |

#### Table 11-50. Pulse Width Modulation (PWM) AC Specifications

| Description                   | Conditions                                                                                                                                                                                  | Min                                                                                                                                                                                                                                       | Тур                                                                                                                                                                             | Max                                                                                                                                                                                                         | Units                                                                                                                                                                                                       |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating frequency           |                                                                                                                                                                                             | DC                                                                                                                                                                                                                                        | _                                                                                                                                                                               | 67.01                                                                                                                                                                                                       | MHz                                                                                                                                                                                                         |

| Pulse width                   |                                                                                                                                                                                             | 15                                                                                                                                                                                                                                        | -                                                                                                                                                                               | _                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Pulse width (external)        |                                                                                                                                                                                             | 30                                                                                                                                                                                                                                        | -                                                                                                                                                                               | -                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Kill pulse width              |                                                                                                                                                                                             | 15                                                                                                                                                                                                                                        | _                                                                                                                                                                               | _                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Kill pulse width (external)   |                                                                                                                                                                                             | 30                                                                                                                                                                                                                                        | -                                                                                                                                                                               | _                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Enable pulse width            |                                                                                                                                                                                             | 15                                                                                                                                                                                                                                        | -                                                                                                                                                                               | -                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Enable pulse width (external) |                                                                                                                                                                                             | 30                                                                                                                                                                                                                                        | _                                                                                                                                                                               | _                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Reset pulse width             |                                                                                                                                                                                             | 15                                                                                                                                                                                                                                        | -                                                                                                                                                                               | -                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

| Reset pulse width (external)  |                                                                                                                                                                                             | 30                                                                                                                                                                                                                                        | -                                                                                                                                                                               | -                                                                                                                                                                                                           | ns                                                                                                                                                                                                          |

|                               | Operating frequency<br>Pulse width<br>Pulse width (external)<br>Kill pulse width<br>Kill pulse width (external)<br>Enable pulse width<br>Enable pulse width (external)<br>Reset pulse width | Operating frequency         Pulse width         Pulse width (external)         Kill pulse width         Kill pulse width (external)         Enable pulse width (external)         Enable pulse width (external)         Reset pulse width | Operating frequencyDCPulse width15Pulse width (external)30Kill pulse width15Kill pulse width (external)30Enable pulse width15Enable pulse width (external)30Reset pulse width15 | Operating frequencyDC-Pulse width15-Pulse width (external)30-Kill pulse width15-Kill pulse width (external)30-Enable pulse width15-Enable pulse width (external)30-Reset pulse width15-Reset pulse width15- | Operating frequencyDC-67.01Pulse width15Pulse width (external)30Kill pulse width15Kill pulse width (external)30Enable pulse width (external)30Enable pulse width (external)30Reset pulse width (external)30 |

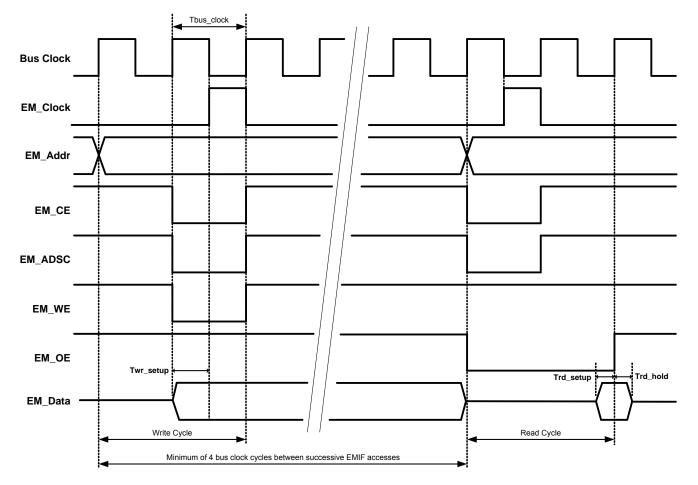

Figure 11-72. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-68. Synchronous Write and Read Timing Specifications<sup>[65]</sup>

| Parameter  | Description                                                    | Conditions | Min             | Тур | Max | Units |

|------------|----------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[66]</sup>                            |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[67]</sup>                               |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock             |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before<br>rising edge of EM_OE |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after<br>rising edge of EM_OE  |            | 5               | -   | -   | ns    |

Notes

- 65. Based on device characterization (Not production tested).

66. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 80.

67. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

### 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

11.9.1 Internal Main Oscillator

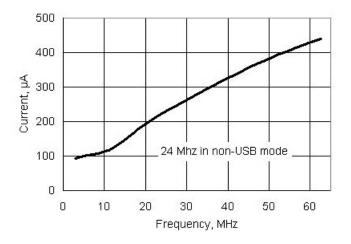

Table 11-77. IMO DC Specifications<sup>[73]</sup>

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|

|           | Supply current        |                                    |     |     |     |       |

|           | 62.6 MHz              |                                    | -   | -   | 600 | μA    |

|           | 48 MHz                |                                    | -   | _   | 500 | μA    |

|           | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | -   | 500 | μA    |

|           | 24 MHz – non USB mode |                                    | -   | -   | 300 | μA    |

|           | 12 MHz                |                                    | -   | _   | 200 | μA    |

|           | 6 MHz                 |                                    | -   | -   | 180 | μA    |

|           | 3 MHz                 |                                    | -   | -   | 150 | μA    |

#### Figure 11-75. IMO Current vs. Frequency

### NOTES:

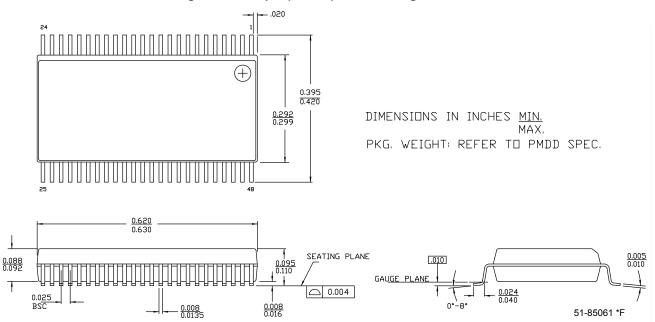

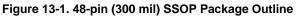

1. 🗱 HATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE

| PART # | DESCRIPTION |

|--------|-------------|

| LT48D  | LEAD FREE   |

001-45616 \*E

## 17. Revision History

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |