#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                  |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axi-035t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1. A | rchitectural Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 4                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|      | inouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| 3. F | in Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                                         |

|      | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|      | 4.1 8051 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                         |

|      | 4.2 Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                         |

|      | 4.3 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|      | 4.4 DMA and PHUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|      | 4.5 Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| 5. N | lemory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|      | 5.1 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|      | 5.2 Flash Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

|      | 5.3 Flash Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|      | 5.4 EEPROM<br>5.5 Nonvolatile Latches (NVLs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|      | 5.6 External Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 <del>4</del><br>25                                                       |

|      | 5.7 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| 6 9  | system Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 0. 0 | 6.1 Clocking System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|      | 6.2 Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|      | 6.3 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

|      | 6.4 I/O System and Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 7. C | igital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                         |

| 7. C | igital Subsystem<br>7.1 Example Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 7. C | <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44<br>46                                                                   |

| 7. C | <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li><li>7.3 UDB Array Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>46<br>49                                                             |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | 44<br>46<br>49<br>49                                                       |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> </ul>                                                                                                                                                                                                                                                                                                                                                        | 44<br>46<br>49<br>49<br>51                                                 |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> </ul>                                                                                                                                                                                                                                                                                                                                       | 44<br>46<br>49<br>49<br>51<br>53                                           |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> </ul>                                                                                                                                                                                                                                                                                               | 44<br>49<br>49<br>51<br>53<br>53                                           |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> </ul>                                                                                                                                                                                                                                                                   | 44<br>49<br>49<br>51<br>53<br>53<br>54                                     |

|      | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul>                                                                                                                                                                                                                                 | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56                               |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem                                                                                                                                                                                                                                   | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br><b>56</b>                  |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>analog Subsystem</b> 8.1 Analog Routing                                                                                                                                                                                                                | 44<br>49<br>49<br>51<br>53<br>53<br>53<br>54<br>56<br>57                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC                                                                                                                                                                                                    | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators                                                                                                                                                                            | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59<br>60             |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>malog Subsystem</b> 8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks                                                                                                    | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59<br>60<br>61<br>61 |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive                                                                                      | 44<br>49<br>49<br>53<br>53<br>53<br>56<br>57<br>59<br>60<br>61<br>61<br>62 |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>nalog Subsystem</b> 8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense                                                  | 44<br>49<br>49<br>53<br>53<br>54<br>56<br>57<br>60<br>61<br>62<br>63       |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor                 | 44<br>49<br>53<br>53<br>54<br>55<br>57<br>60<br>61<br>62<br>63<br>63       |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor         8.9 DAC | 44<br>49<br>53<br>53<br>55<br>56<br>61<br>62<br>63<br>64                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor                 | 44<br>49<br>53<br>53<br>55<br>56<br>57<br>50<br>61<br>62<br>63<br>64<br>64 |

| 9. Programming, Debug Interfaces, Resources           |     |

|-------------------------------------------------------|-----|

| 9.1 JTAG Interface                                    |     |

| 9.2 Serial Wire Debug Interface<br>9.3 Debug Features |     |

| 9.4 Trace Features                                    |     |

| 9.5 Single Wire Viewer Interface                      |     |

| 9.6 Programming Features                              |     |

| 9.7 Device Security                                   |     |

| 9.8 CSP Package Bootloader                            | 69  |

| 10. Development Support                               | 70  |

| 10.1 Documentation                                    | 70  |

| 10.2 Online                                           |     |

| 10.3 Tools                                            |     |

| 11. Electrical Specifications                         |     |

| 11.1 Absolute Maximum Ratings                         |     |

| 11.2 Device Level Specifications                      |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs      |     |

| 11.5 Analog Peripherals                               |     |

| 11.6 Digital Peripherals                              |     |

| 11.7 Memory                                           | 112 |

| 11.8 PSoC System Resources                            |     |

| 11.9 Clocking                                         | 119 |

| 12. Ordering Information                              |     |

| 12.1 Part Numbering Conventions                       |     |

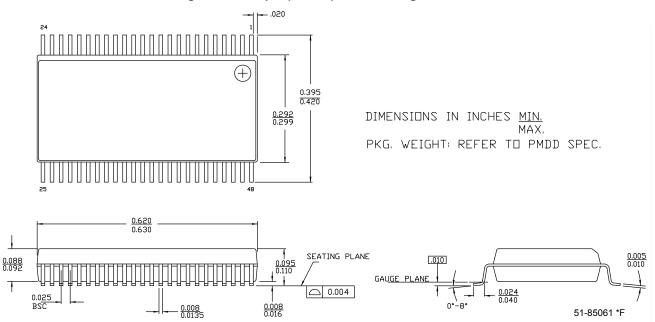

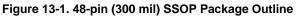

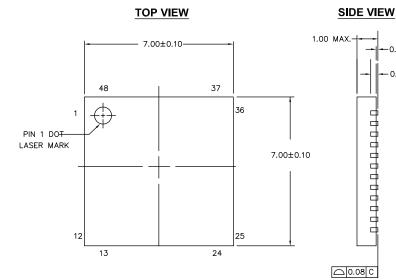

| 13. Packaging                                         | 125 |

| 14. Acronyms                                          | 129 |

| 15. Reference Documents                               | 130 |

| 16. Document Conventions                              | 131 |

| 16.1 Units of Measure                                 | 131 |

| 17. Revision History                                  | 132 |

| 18. Sales, Solutions, and Legal Information           | 140 |

| Worldwide Sales and Design Support                    |     |

| Products                                              |     |

| PSoC® Solutions                                       |     |

| Cypress Developer Community                           |     |

| Technical Support                                     | 140 |

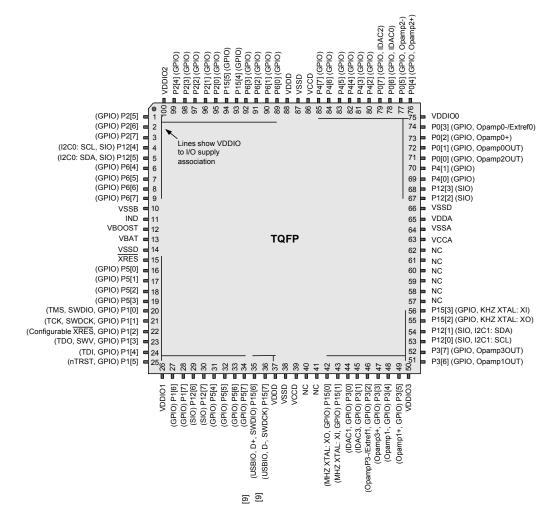

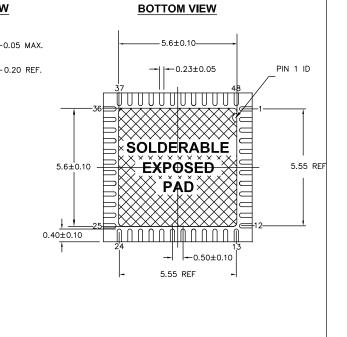

### Figure 2-6. 100-pin TQFP Part Pinout

| Table 2-1. | V <sub>DDIO</sub> and | l Port Pin | Associations |

|------------|-----------------------|------------|--------------|

|------------|-----------------------|------------|--------------|

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

Note 9. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

disable bit

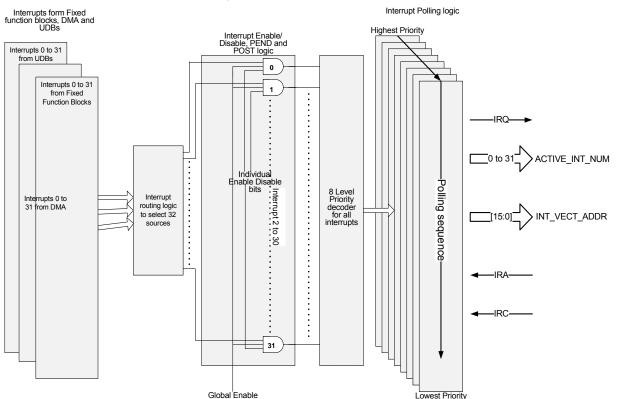

Figure 4-3. Interrupt Structure

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are

direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

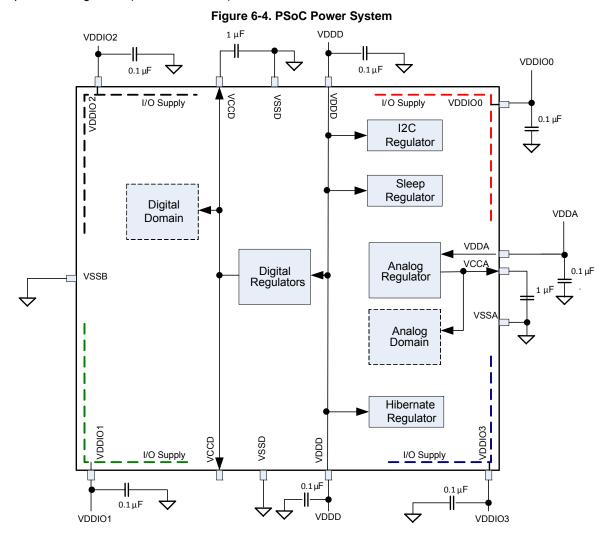

## 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIOX, respectively. It also includes two internal 1.8-V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the

VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a  $1-\mu$ F ±10-percent X5R capacitor. The power system also contains a sleep regulator, an I<sup>2</sup>C regulator, and a hibernate regulator.

#### Notes

- The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (VDDX or VCCX in Figure 6-4) is a significant percentage of the rated working voltage.

- You can power the device in internally regulated mode, where the voltage applied to the VDDx pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the VCCx pins, and do not tie the VDDx pins to the VCCx pins.

- You can also power the device in externally regulated mode, that is, by directly powering the VCCD and VCCA pins. In this configuration, the VDDD pins should be shorted to the VCCD pins and the VDDA pin should be shorted to the VCCA pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, DFB taps, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD drive

- LCD control

- Filters

7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC, DACs, and filters, and communication protocols, such as I<sup>2</sup>C, USB, and CAN. See Example Peripherals on page 44 for more details about available peripherals. All content is fully characterized and carefully documented in data sheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil<sup>™</sup>, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView<sup>™</sup> compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

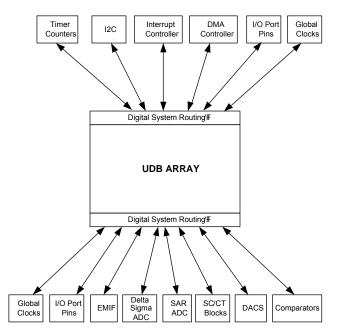

### Figure 7-9. Digital System Interconnect

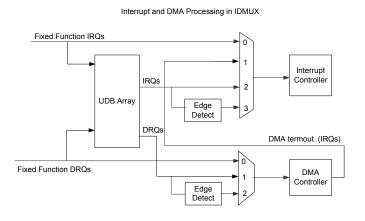

Interrupt and DMA routing is very flexible in the CY8C38 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

## Figure 7-10. Interrupt and DMA Processing in the IDMUX

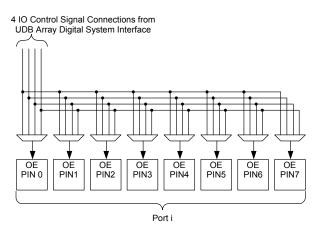

## 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

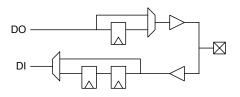

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

## Figure 7-11. I/O Pin Synchronization Routing

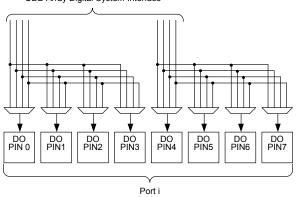

Figure 7-12. I/O Pin Output Connectivity

8 IO Data Output Connections from the UDB Array Digital System Interface

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

#### Figure 7-13. I/O Pin Output Enable Connectivity

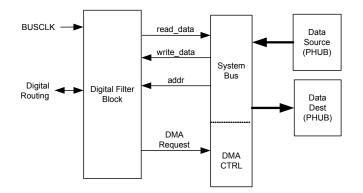

## 7.9 Digital Filter Block

Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

#### Figure 7-20. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- PGA Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

#### 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 kohms.

#### 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a -3 dB bandwidth greater than 6.0 MHz.

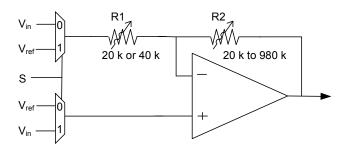

#### 8.5.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-8. The schematic in Figure 8-8 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

#### Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

#### Figure 8-8. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

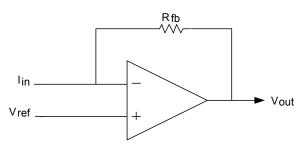

## 8.5.4 TIA

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current I<sub>in</sub>, the output voltage is V<sub>REF</sub> - I<sub>in</sub> x R<sub>fb</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

#### Table 8-4. Feedback Resistor Settings

| Configuration Word | Nominal $R_{fb}(K\Omega)$ |

|--------------------|---------------------------|

| 000b               | 20                        |

| 001b               | 30                        |

| 010b               | 40                        |

| 011b               | 60                        |

| 100b               | 120                       |

| 101b               | 250                       |

| 110b               | 500                       |

| 111b               | 1000                      |

#### Figure 8-9. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the V<sub>REF</sub> TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

## 8.6 LCD Direct Drive

The PSoC LCD driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C38 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

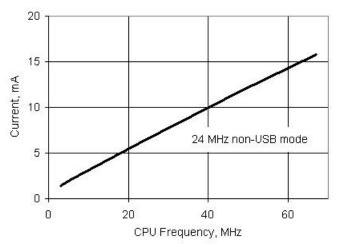

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

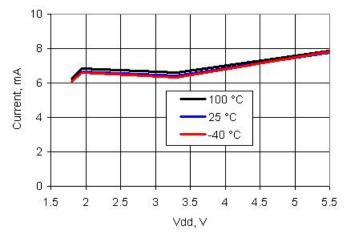

Figure 11-3. Active Mode Current vs  $V_{\text{DD}}$  and Temperature,  $F_{\text{CPU}}$  = 24 MHz

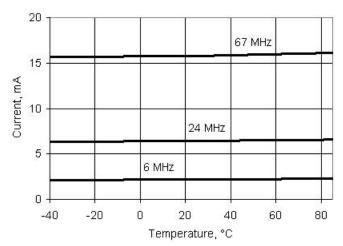

Figure 11-2. Active Mode Current vs Temperature and  $F_{CPU},\ V_{DD}$  = 3.3 V

## Table 11-13. SIO Comparator Specifications<sup>[45]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | -   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | -   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | -   | 250 | µV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | -   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | _   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | -   | -   |       |

| Tresp     | Response time                  |                           | _   | -   | 30  | ns    |

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 72.

## Table 11-14. USBIO DC Specifications

| Parameter                       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb                          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | -   | 3.6            | V     |

| Volusb                          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | -   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode          | $V_{DDD} \ge 3 V$                                  | 2              | -   | -              | V     |

| Vilgpio                         | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 V$                                  | -              | -   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 V$                 | 2.4            | _   | -              | V     |

| Volgpio                         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 V$                 | -              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity         | (D+) – (D–)                                        | -              | -   | 0.2            | V     |

| Vcm                             | Differential input common mode range   | -                                                  | 0.8            | -   | 2.5            | V     |

| Vse                             | Single ended receiver threshold        | -                                                  | 0.8            | -   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext                            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance            | Including Rext                                     | 28             | -   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance      | -                                                  | -              | -   | 20             | pF    |

| I <sub>IL</sub> <sup>[45]</sup> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | -              | -   | 2              | nA    |

## 11.4.4 XRES

# Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[46]</sup>                             |            | —                     | 3   | _                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[46]</sup> |            | -                     | 100 | -                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100                   | μA    |

#### Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

## 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.5.1 Opamp

## Table 11-19. Opamp DC Specifications

| Parameter         | Description                                    | Conditions                                                                                                                                                                                  | Min                     | Тур  | Max                     | Units  |

|-------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|--------|

| VI                | Input voltage range                            |                                                                                                                                                                                             | V <sub>SSA</sub>        | -    | V <sub>DDA</sub>        | V      |

| V <sub>OS</sub>   | Input offset voltage                           |                                                                                                                                                                                             | -                       | -    | 2.5                     | mV     |

|                   |                                                | Operating temperature –40 °C to 70 °C                                                                                                                                                       | -                       | -    | 2                       | mV     |

| TCV <sub>OS</sub> | Input offset voltage drift with<br>temperature | Power mode = high                                                                                                                                                                           | -                       | -    | ±30                     | µV/ °C |

| Ge1               | Gain error, unity gain buffer mode             | Rload = 1 k $\Omega$                                                                                                                                                                        | -                       | -    | ±0.1                    | %      |

| C <sub>IN</sub>   | Input capacitance                              | Routing from pin                                                                                                                                                                            | -                       | -    | 18                      | pF     |

| V <sub>O</sub>    | Output voltage range                           | 1 mA, source or sink, power<br>mode = high                                                                                                                                                  | V <sub>SSA</sub> + 0.05 | -    | V <sub>DDA</sub> – 0.05 | V      |

| I <sub>OUT</sub>  | Output current capability, source or sink      | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ $V_{DDA}$ –500 mV, $V_{DDA}$ > 2.7 V                                                                                                                  | 25                      | -    | -                       | mA     |

|                   |                                                | $\label{eq:VSSA} \begin{array}{l} V_{SSA} \mbox{ + 500 mV} \leq \mbox{Vout} \leq \mbox{V}_{DDA} \\ -500 \mbox{ mV}, \mbox{ 1.7 V} \mbox{ = } \mbox{V}_{DDA} \leq \mbox{ 2.7 V} \end{array}$ | 16                      | _    | -                       | mA     |

| I <sub>DD</sub>   | Quiescent current                              | Power mode = min                                                                                                                                                                            | -                       | 250  | 400                     | uA     |

|                   |                                                | Power mode = low                                                                                                                                                                            | -                       | 250  | 400                     | uA     |

|                   |                                                | Power mode = med                                                                                                                                                                            | -                       | 330  | 950                     | uA     |

|                   |                                                | Power mode = high                                                                                                                                                                           | -                       | 1000 | 2500                    | uA     |

| CMRR              | Common mode rejection ratio                    |                                                                                                                                                                                             | 80                      | -    | -                       | dB     |

| PSRR              | Power supply rejection ratio                   | $V_{DDA} \ge 2.7 V$                                                                                                                                                                         | 85                      | -    | -                       | dB     |

|                   |                                                | V <sub>DDA</sub> < 2.7 V                                                                                                                                                                    | 70                      | -    | -                       | dB     |

| I <sub>IB</sub>   | Input bias current <sup>[46]</sup>             | 25 °C                                                                                                                                                                                       | _                       | 10   | _                       | pА     |

#### Note

46. Based on device characterization (Not production tested).

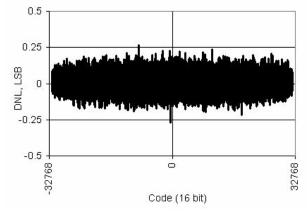

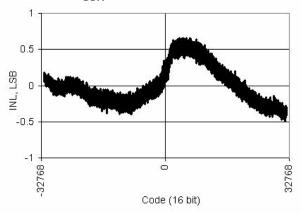

Figure 11-37. Delta-sigma ADC DNL vs Output Code, 16-bit, 48 ksps, 25 °C V<sub>DDA</sub> = 3.3 V

#### Figure 11-38. Delta-sigma ADC INL vs Output Code, 16-bit, 48 ksps, 25 °C V<sub>DDA</sub> = 3.3 V

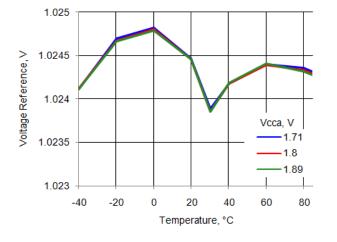

#### 11.5.3 Voltage Reference

#### Table 11-28. Voltage Reference Specifications

See also ADC external reference specifications in Section 11.5.2.

| Parameter                        | Description                                              | Conditions                          |        | Min              | Тур   | Max              | Units   |

|----------------------------------|----------------------------------------------------------|-------------------------------------|--------|------------------|-------|------------------|---------|

| V <sub>REF</sub> <sup>[51]</sup> | Precision reference voltage                              | Initial trimming, 25 °C             |        | 1.023<br>(-0.1%) | 1.024 | 1.025<br>(+0.1%) | V       |

|                                  | After typical PCB assembly,                              | love the and QEO °C and don reflect | –40 °C | -                | ±0.5  | -                | %       |

|                                  | post reflow                                              | Device may be calibrated after      | 25 °C  | -                | ±0.2  | -                | %       |

|                                  |                                                          | assembly to improve performance     | 85 °C  | -                | ±0.2  | -                | %       |

|                                  | Temperature drift <sup>[52]</sup>                        | Box method                          |        | -                | -     | 30               | ppm/°C  |

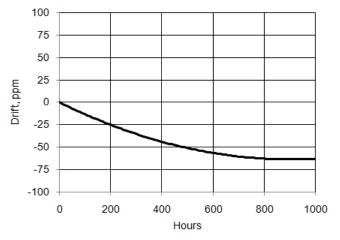

|                                  | Long term drift                                          |                                     |        | -                | 100   | -                | ppm/khr |

|                                  | Thermal cycling drift<br>(stability) <sup>[52, 53]</sup> |                                     |        | -                | 100   | _                | ppm     |

### Figure 11-39. Voltage Reference vs. Temperature and V<sub>CCA</sub>

## Figure 11-40. Voltage Reference Long-Term Drift

#### Notes

51.  $V_{\mathsf{REF}}$  is measured after packaging, and thus accounts for substrate and die attach stresses

52. Based on device characterization (Not production tested).

53. After eight full cycles between -40 °C and 100 °C.

## 11.5.6 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 12 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

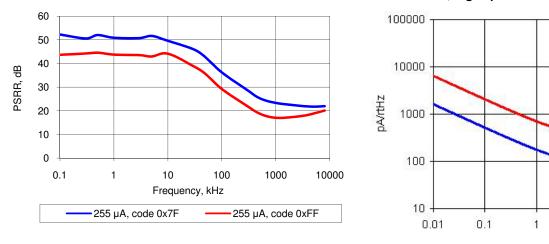

## Table 11-32. IDAC DC Specifications

| Parameter        | Description                          | Conditions                                                                                                                                                                    | Min | Тур    | Max  | Units  |

|------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|

|                  | Resolution                           |                                                                                                                                                                               | _   | -      | 8    | bits   |

| I <sub>OUT</sub> | Output current at code = 255         | $\label{eq:Range} \begin{array}{l} \mbox{Range} = 2.04 \mbox{ mA}, \mbox{ code} = 255, \\ \mbox{V}_{\mbox{DDA}} \geq 2.7 \mbox{ V}, \mbox{ Rload} = 600 \ \Omega \end{array}$ | _   | 2.04   | -    | mA     |

|                  |                                      | Range = 2.04 mA, high speed mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$                                                                                       | _   | 2.04   | -    | mA     |

|                  |                                      | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                                                                      | -   | 255    | _    | μA     |

|                  |                                      | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                                                                   | -   | 31.875 | -    | μA     |

|                  | Monotonicity                         |                                                                                                                                                                               | -   | -      | Yes  |        |

| Ezs              | Zero scale error                     |                                                                                                                                                                               | -   | 0      | ±1   | LSB    |

| Eg               | Gain error                           | Range = 2.04 mA, 25 °C                                                                                                                                                        | _   | -      | ±2.5 | %      |

|                  |                                      | Range = 255 µA, 25 ° C                                                                                                                                                        | _   | -      | ±2.5 | %      |

|                  |                                      | Range = 31.875 µA, 25 ° C                                                                                                                                                     | -   | -      | ±3.5 | %      |

| TC_Eg            | Temperature coefficient of gain      | Range = 2.04 mA                                                                                                                                                               | -   | -      | 0.04 | % / °C |

|                  | error                                | Range = 255 µA                                                                                                                                                                | -   | -      | 0.04 | % / °C |

|                  |                                      | Range = 31.875 µA                                                                                                                                                             | -   | -      | 0.05 | % / °C |

| INL              | Integral nonlinearity                | Sink mode, range = $255 \mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF                                                                                   | _   | ±0.9   | ±1   | LSB    |

|                  |                                      | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF                                                                                 | _   | ±1.2   | ±1.6 | LSB    |

| DNL              | Differential nonlinearity            | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 k $\Omega$ , Cload = 15 pF                                                                                                     | -   | ±0.3   | ±1   | LSB    |

|                  |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                                                                                                   | -   | ±0.3   | ±1   | LSB    |

| Vcompliance      | Dropout voltage, source or sink mode | Voltage headroom at max current, Rload to $V_{DDA}$ or Rload to $V_{SSA},$ Vdiff from $V_{DDA}$                                                                               | 1   | -      | -    | V      |

Code = 255

Code = 64

Current noise

is proportional

to scale \* code

100

10

kHz

1000

Figure 11-53. IDAC PSRR vs Frequency

Figure 11-54. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

# 11.5.7 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

## Table 11-34. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | —   | 8    | _    | bits      |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | —   | 1.02 | _    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | —   | 4.08 | _    | V         |

| INL1             | Integral nonlinearity                     | 1 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[57]</sup>     | 4 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | —   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[57]</sup> | 4 V scale                         | —   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | _   | 4    | _    | kΩ        |

|                  |                                           | 4 V scale                         | —   | 16   | _    | kΩ        |

|                  | Monotonicity                              |                                   | _   | -    | Yes  | -         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale,                        | _   | -    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | _   | -    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale,                        | -   | -    | 0.03 | %FSR / °C |

|                  |                                           | 4 V scale                         | _   | -    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA        |

|                  |                                           | High speed mode                   | -   | -    | 500  | μA        |

# 11.6.4 P<sup>2</sup>C

## Table 11-51. Fixed I<sup>2</sup>C DC Specifications

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | -   | -   | 250 | μA    |

|           | -                         | Enabled, configured for 400 kbps | -   | -   | 260 | μA    |

|           | -                         | Wake from sleep mode             | -   | -   | 30  | μA    |

# Table 11-52. Fixed I<sup>2</sup>C AC Specifications

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | -   | 1   | Mbps  |

#### 11.6.5 Controller Area Network

## Table 11-53. CAN DC Specifications<sup>[59]</sup>

| Parameter       | Description               | Conditions | Min | Тур | Max | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Block current consumption |            | -   | _   | 200 | μA    |

# Table 11-54. CAN AC Specifications<sup>[59]</sup>

| Parameter | Description | Conditions          | Min | Тур | Max | Units |

|-----------|-------------|---------------------|-----|-----|-----|-------|

|           | Bit rate    | Minimum 8 MHz clock | -   | -   | 1   | Mbit  |

### 11.6.6 Digital Filter Block

## Table 11-55. DFB DC Specifications

| Parameter | Description           | Conditions                     | Min | Тур  | Max  | Units |

|-----------|-----------------------|--------------------------------|-----|------|------|-------|

|           | DFB operating current | 64-tap FIR at F <sub>DFB</sub> |     |      |      |       |

|           |                       | 500 kHz (6.7 ksps)             | -   | 0.16 | 0.27 | mA    |

|           |                       | 1 MHz (13.4 ksps)              | -   | 0.33 | 0.53 | mA    |

|           |                       | 10 MHz (134 ksps)              | -   | 3.3  | 5.3  | mA    |

|           |                       | 48 MHz (644 ksps)              | -   | 15.7 | 25.5 | mA    |

|           |                       | 67 MHz (900 ksps)              | _   | 21.8 | 35.6 | mA    |

### Table 11-56. DFB AC Specifications

| Parameter        | Description             | Conditions | Min | Тур | Max   | Units |

|------------------|-------------------------|------------|-----|-----|-------|-------|

| F <sub>DFB</sub> | DFB operating frequency |            | DC  | -   | 67.01 | MHz   |

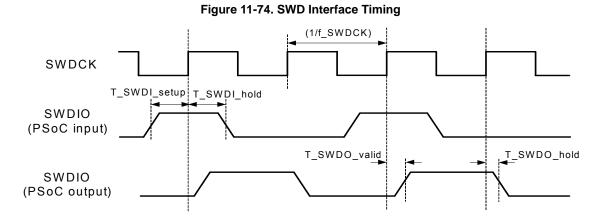

### 11.8.5 SWD Interface

# Table 11-75. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                  | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | _   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | -   | _   | 7 <sup>[72]</sup>   | MHz   |