#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB             |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x20b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axi-208t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- □ AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

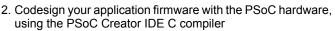

# PSoC Creator

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- 1. Drag and drop component icons to build your hardware system design in the main design workspace

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

# Figure 1. Multiple-Sensor Example Project in PSoC Creator

For more details on the peripherals see the "Example Peripherals" section on page 44 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 44 of this data sheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- Programmable gain amplifiers

- Mixers

- Dother similar analog components

See the "Analog Subsystem" section on page 56 of this data sheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive<sup>[3]</sup>, CapSense<sup>[4]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow V<sub>OH</sub> to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 37 of this data sheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

3. This feature on select devices only. See Ordering Information on page 123 for details.

<sup>4.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

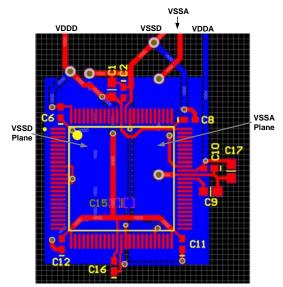

# Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

# IDAC0, IDAC1, IDAC2, IDAC3

Low resistance output pin for high current DACs (IDAC).

#### Opamp0OUT, Opamp1OUT, Opamp2OUT, Opamp3OUT

High current output of uncommitted opamp<sup>[11]</sup>.

#### Extref0, Extref1

External reference input to the analog system.

#### Opamp0–, Opamp1–, Opamp2–, Opamp3–

Inverting input to uncommitted opamp.

## Opamp0+, Opamp1+, Opamp2+, Opamp3+

Noninverting input to uncommitted opamp.

#### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[11]</sup>.

#### I2C0: SCL, I2C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

#### I2C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

# IND

Inductor connection to boost pump.

# kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

## MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

# nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

#### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### SWDCK

Serial wire debug clock programming and debug port connection.

#### **SWDIO**

Serial wire debug input and output programming and debug port connection.

# SWV

Single wire viewer debug output.

# тск

JTAG test clock programming and debug port connection.

# TDI

JTAG test data in programming and debug port connection.

# TDO

JTAG test data out programming and debug port connection.

#### Note

11. GPIOs with opamp outputs are not recommended for use with CapSense.

# Table 4-3. Data Transfer Instructions

| Mr       | nemonic      | Description                                            | Bytes | Cycles |

|----------|--------------|--------------------------------------------------------|-------|--------|

| MOV A,F  | Rn           | Move register to accumulator                           | 1     | 1      |

| MOV A,[  | Direct       | Move direct byte to accumulator                        | 2     | 2      |

| MOV A,@  | @Ri          | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV A,#  | #data        | Move immediate data to accumulator                     | 2     | 2      |

| MOV Rn   | ı,A          | Move accumulator to register                           | 1     | 1      |

| MOV Rn   | n,Direct     | Move direct byte to register                           | 2     | 3      |

| MOV Rn   | n, #data     | Move immediate data to register                        | 2     | 2      |

| MOV Dir  | rect, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV Dir  | rect, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV Dir  | rect, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV Dir  | rect, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV Dir  | rect, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV @    | Ri, A        | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @    | Ri, Direct   | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @    | Ri, #data    | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DF   | PTR, #data16 | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A,  | @A+DPTR      | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A,  | @A + PC      | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,  | @Ri          | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A,  | @DPTR        | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @   | Ri, A        | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @   | DPTR, A      | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Dir | rect         | Push direct byte onto stack                            | 2     | 3      |

| POP Di   | rect         | Pop direct byte from stack                             | 2     | 2      |

| XCH A,   | Rn           | Exchange register with accumulator                     | 1     | 2      |

| XCH A,   | Direct       | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A,   | @Ri          | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A,  | @Ri          | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

# Table 4-4. Boolean Instructions

| Mnemonic   | Description             | Bytes | Cycles |

|------------|-------------------------|-------|--------|

| CLR C      | Clear carry             | 1     | 1      |

| CLR bit    | Clear direct bit        | 2     | 3      |

| SETB C     | Set carry               | 1     | 1      |

| SETB bit   | Set direct bit          | 2     | 3      |

| CPL C      | Complement carry        | 1     | 1      |

| CPL bit    | Complement direct bit   | 2     | 3      |

| ANL C, bit | AND direct bit to carry | 2     | 2      |

# 5.6 External Memory Interface

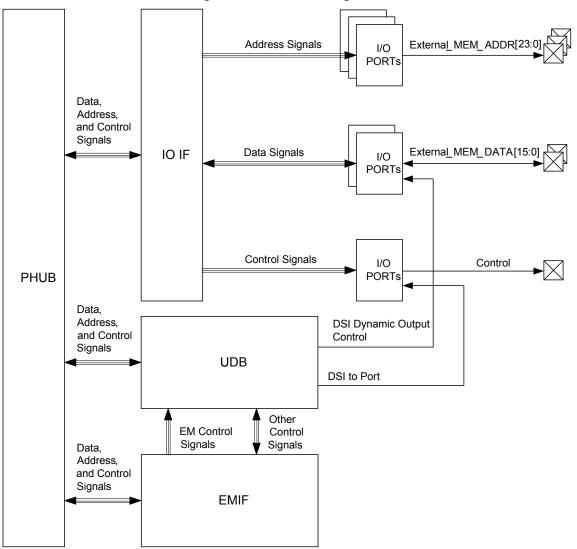

CY8C38 provides an EMIF for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C38 supports only one type of external memory device at a time. External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 27. The memory can be 8 or 16 bits wide.

Figure 5-1. EMIF Block Diagram

# 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[16]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master)<sup>[17]</sup>. In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup

functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

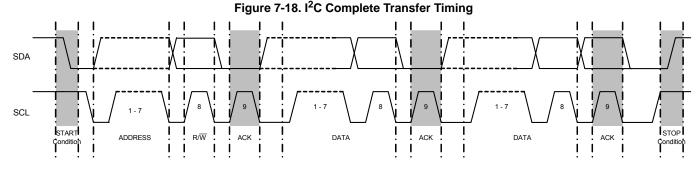

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

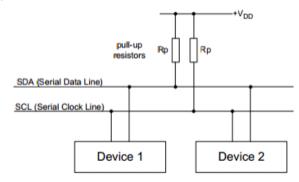

# 7.8.1 External Electrical Connections

As Figure 7-19 shows, the  $I^2C$  bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

# Figure 7-19. Connection of Devices to the I<sup>2</sup>C Bus

#### Notes

- 16. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 80 for details.

- 17. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C38, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

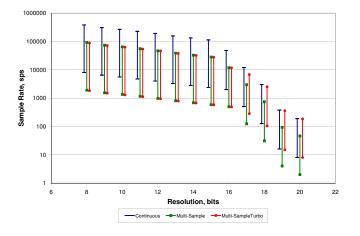

# 8.2 Delta-sigma ADC

The CY8C38 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for both audio signal processing and measurement applications. The converter's nominal operation is 16 bits at 48 ksps. The ADC can be configured to output 20-bit resolution at data rates of up to 187 sps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 20   | 187                          | -          |

| 16   | 48 k                         | 84         |

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

Table 8-1.

Delta-sigma ADC Performance

#### Figure 8-3. Delta-sigma ADC Sample Rates, Range = ±1.024 V

#### 8.2.1 Functional Description

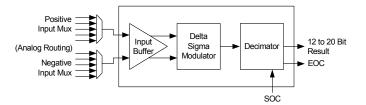

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic

block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

#### Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

#### 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

#### 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

# **10. Development Support**

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

# 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component data sheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

Application Notes: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

## 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

## 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

5 4 3 Voh, V 2 Vddio = 5V Vddio = 3.3V 1 Vddio = 1.8V 0 0 5 10 15 20 25 30 loh, mA

# 2.0 Vddio = 5V 1.5 Vddio = 3.3V Vddio = 1.8V 0.5 0.0 0 5 10 15 20 25 Iol, mA

Figure 11-16. GPIO Output Low Voltage and Current

# Figure 11-15. GPIO Output High Voltage and Current

# Table 11-10. GPIO AC Specifications

| Parameter  | Description                                                                             | Conditions                            | Min | Тур | Max                                   | Units |

|------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|---------------------------------------|-------|

| TriseF     | Rise time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6                                     | ns    |

| TfallF     | Fall time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6                                     | ns    |

| TriseS     | Rise time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60                                    | ns    |

| TfallS     | Fall time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60                                    | ns    |

|            | GPIO output operating frequency                                                         |                                       |     |     |                                       |       |

|            | 2.7 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V, fast strong drive mode                     | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33                                    | MHz   |

| Fgpioout   | 1.71 V $\leq$ V <sub>DDIO</sub> < 2.7 V, fast strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20                                    | MHz   |

|            | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 7                                     | MHz   |

|            | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 6<br>6<br>60<br>60<br>33<br>20        | MHz   |

| Fgpioin    | GPIO input operating frequency                                                          |                                       |     |     |                                       |       |

| i gpioliti | 1.71 V <u>&lt;</u> V <sub>DDIO</sub> <u>&lt;</u> 5.5 V                                  | 90/10% V <sub>DDIO</sub>              | -   | -   | 6<br>60<br>60<br>33<br>20<br>7<br>3.5 | MHz   |

30

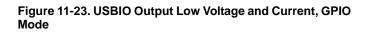

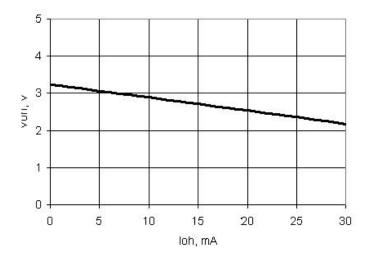

Figure 11-22. USBIO Output High Voltage and Current, GPIO Mode

# Table 11-15. USBIO AC Specifications

| Parameter | Description                                                 | Conditions                                         | Min        | Тур | Max        | Units |

|-----------|-------------------------------------------------------------|----------------------------------------------------|------------|-----|------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                    | 12 – 0.25% | 12  | 12 + 0.25% | MHz   |

| Tjr1      | Receiver data jitter tolerance to next transition           |                                                    | -8         | -   | 8          | ns    |

| Tjr2      | Receiver data jitter tolerance to pair transition           |                                                    | -5         | -   | 5          | ns    |

| Tdj1      | Driver differential jitter to next transition               |                                                    | -3.5       | -   | 3.5        | ns    |

| Tdj2      | Driver differential jitter to pair transition               |                                                    | -4         | -   | 4          | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                    | -2         | -   | 5          | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                    | 160        | -   | 175        | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                    | 82         | _   | _          | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                    | -          | -   | 14         | ns    |

| Fgpio_out | GPIO mode output operating frequency                        | $3 \text{ V} \le \text{V}_{DDD} \le 5.5 \text{ V}$ | -          | _   | 20         | MHz   |

|           |                                                             | V <sub>DDD</sub> = 1.71 V                          | -          | -   | 6          | MHz   |

| Tr_gpio   | Rise time, GPIO mode, 10%/90% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                 | -          | -   | 12         | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load              | -          | _   | 40         | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                 | -          | _   | 12         | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load              | -          | -   | 40         | ns    |

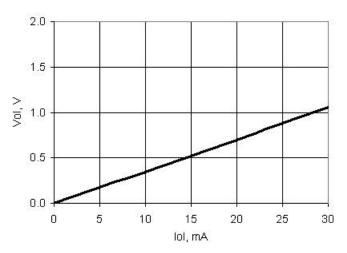

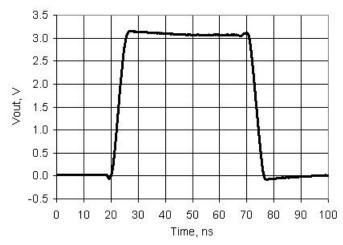

Figure 11-24. USBIO Output Rise and Fall Times, GPIO Mode,  $V_{DDD}$  = 3.3 V, 25 pF Load

Table 11-16. USB Driver AC Specifications

| Parameter | Description                     | Conditions                                                                           | Min | Тур | Max  | Units |

|-----------|---------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

| Tr        | Transition rise time            |                                                                                      | -   | -   | 20   | ns    |

| Tf        | Transition fall time            |                                                                                      | _   | -   | 20   | ns    |

| TR        | Rise/fall time matching         | V <sub>USB_5</sub> , V <sub>USB_3.3</sub> , see USB<br>DC Specifications on page 111 | 90% | _   | 111% |       |

| Vcrs      | Output signal crossover voltage |                                                                                      | 1.3 | Ι   | 2    | V     |

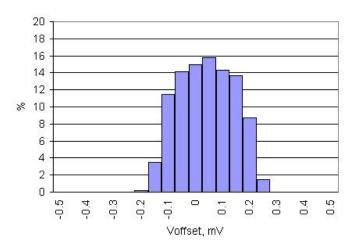

Figure 11-25. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C, V<sub>DDA</sub> = 5 V

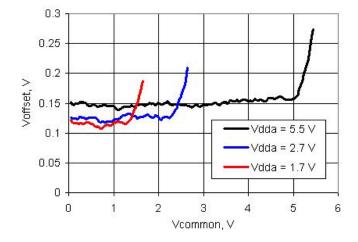

Figure 11-27. Opamp Voffset vs Vcommon and V<sub>DDA</sub>, 25  $^{\circ}\text{C}$

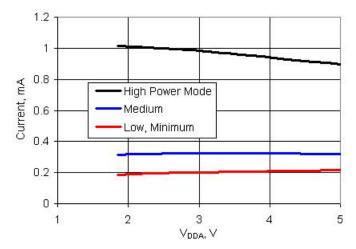

Figure 11-29. Opamp Operating Current vs  $V_{\mbox{\scriptsize DDA}}$  and Power Mode

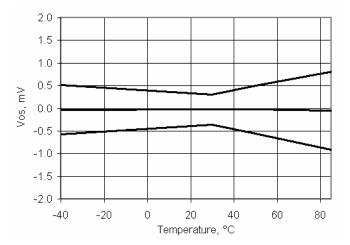

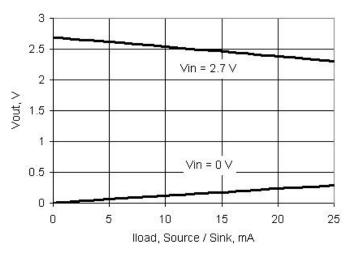

Figure 11-26. Opamp Voffset vs Temperature, V<sub>DDA</sub> = 5V

Figure 11-28. Opamp Output Voltage vs Load Current and Temperature, High Power Mode, 25 °C,  $V_{DDA}$  = 2.7 V

Table 11-20.

Opamp AC Specifications

| Parameter      | Description            | Conditions                                               | Min | Тур | Max              | Units     |

|----------------|------------------------|----------------------------------------------------------|-----|-----|------------------|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                         | 1   | -   | -                | MHz       |

|                |                        | Power mode = low, 15 pF load                             | 2   | -   | <br><br><br><br> | MHz       |

|                |                        | Power mode = medium, 200 pF load                         | 1   | -   | -                | MHz       |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -                | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                             | 1.1 | -   | -                | V/µs      |

|                |                        | Power mode = medium, 200 pF load                         | 0.9 | -   | -                | V/µs      |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -                | V/µs      |

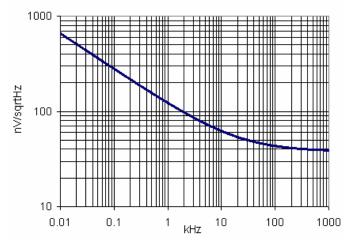

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V,<br>at 100 kHz | _   | 45  | -                | nV/sqrtHz |

# Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, $V_{DDA} = 5V$

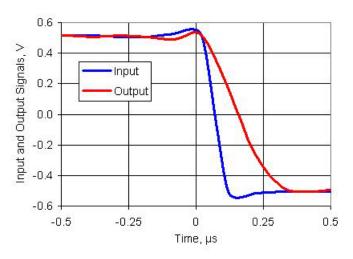

Figure 11-32. Opamp Step Response, Falling

# Figure 11-31. Opamp Step Response, Rising

# 11.5.4 Analog Globals

# Table 11-29. Analog Globals Specifications

| Parameter | Description                                                                        | Conditions             | Min | Тур  | Max  | Units |

|-----------|------------------------------------------------------------------------------------|------------------------|-----|------|------|-------|

| Rppag     | Resistance pin-to-pin through P2[4],<br>AGL0, DSM INP, AGL1, P2[5] <sup>[54]</sup> | V <sub>DDA</sub> = 3 V | _   | 1472 | 2200 | Ω     |

| Rppmuxbus | Resistance pin-to-pin through P2[3], amuxbusL, P2[4] <sup>[54]</sup>               | V <sub>DDA</sub> = 3 V | _   | 706  | 1100 | Ω     |

# 11.5.5 Comparator

# Table 11-30. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                           | Min              | Тур | Max                        | Units |

|-------------------|---------------------------------------------------|------------------------------------------------------|------------------|-----|----------------------------|-------|

|                   | Input offset voltage in fast mode                 | Factory trim, $V_{DDA} > 2.7 V$ , $V_{IN} \ge 0.5 V$ | -                |     | 10                         | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5 V$                        | -                |     | 9                          | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[55]</sup> | Custom trim                                          | -                | -   | 4                          | mV    |

|                   | Input offset voltage in slow mode <sup>[55]</sup> | Custom trim                                          | -                | -   | 4                          | mV    |

|                   | Input offset voltage in ultra<br>low-power mode   | V <sub>DDA</sub> ≤ 4.6 V                             | -                | ±12 | -                          | mV    |

| V <sub>HYST</sub> | Hysteresis                                        | Hysteresis enable mode                               | -                | 10  | 32                         | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                         | High current / fast mode                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Low current / slow mode                              | V <sub>SSA</sub> | -   | V <sub>DDA</sub>           | V     |

|                   |                                                   | Ultra low-power mode<br>V <sub>DDA</sub> ≤ 4.6 V     | V <sub>SSA</sub> | -   | V <sub>DDA</sub> –<br>1.15 | V     |

| CMRR              | Common mode rejection ratio                       |                                                      | -                | 50  | -                          | dB    |

| I <sub>CMP</sub>  | High current mode/fast mode <sup>[56]</sup>       |                                                      | -                | _   | 400                        | μA    |

|                   | Low current mode/slow mode <sup>[56]</sup>        |                                                      | -                | _   | 100                        | μA    |

|                   | Ultra low-power mode <sup>[56]</sup>              | V <sub>DDA</sub> ≤ 4.6 V                             | -                | 6   | -                          | μA    |

# Table 11-31. Comparator AC Specifications

| Parameter         | Description                                         | Conditions                                                        | Min | Тур | Max | Units |

|-------------------|-----------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>RESP</sub> | Response time, high current mode <sup>[56]</sup>    | 50 mV overdrive, measured<br>pin-to-pin                           | -   | 75  | 110 | ns    |

|                   | Response time, low current mode <sup>[56]</sup>     | 50 mV overdrive, measured pin-to-pin                              | _   | 155 | 200 | ns    |

|                   | Response time, ultra low-power mode <sup>[56]</sup> | 50 mV overdrive, measured<br>pin-to-pin, V <sub>DDA</sub> ≤ 4.6 V | _   | 55  | -   | μs    |

55. The recommended procedure for using a custom trim value for the on-chip comparators can be found in the TRM.

56. Based on device characterization (Not production tested).

Notes

54. The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

The resistance of the analog global and analog mux bus is high if V<sub>DDA</sub> ≤ 2.7 V, and the chip is in either sleep or hibernate mode. Use of analog global and analog mux bus under these conditions is not recommended.

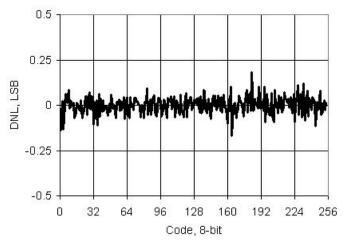

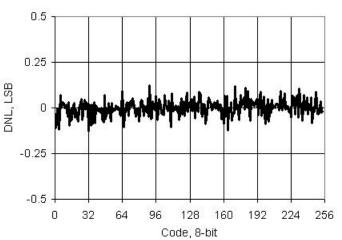

Figure 11-43. IDAC DNL vs Input Code, Range = 255  $\mu\text{A},$  Source Mode

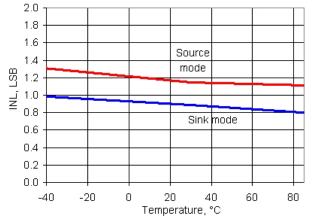

Figure 11-45. IDAC INL vs Temperature, Range = 255  $\mu A,$  High speed mode

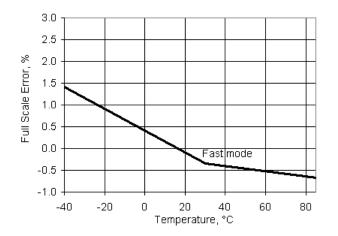

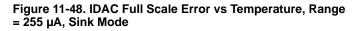

Figure 11-47. IDAC Full Scale Error vs Temperature, Range = 255 μA, Source Mode

Figure 11-44. IDAC DNL vs Input Code, Range = 255  $\mu$ A, Sink Mode

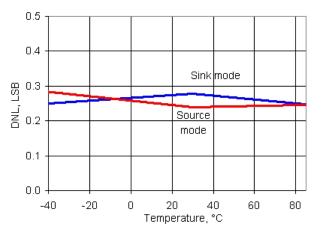

Figure 11-46. IDAC DNL vs Temperature, Range = 255  $\mu$ A, High speed mode

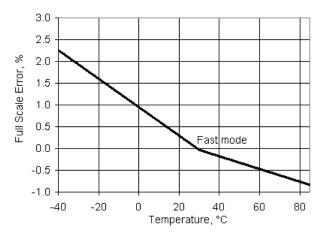

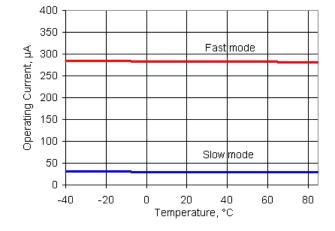

400 350 Fast mode Operating Current, µA 300 250 200 150 100 Slow mode 50 0 0 40 60 80 -40 -20 20 Temperature, °C

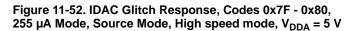

# Figure 11-49. IDAC Operating Current vs Temperature, Range = 255 $\mu$ A, Code = 0, Source Mode

# Table 11-33. IDAC AC Specifications

Parameter Description Conditions Min Тур Max Units Update rate 8 Msps FDAC \_ — Settling time to 0.5 LSB Range = 31.875 µA or 255 µA, full \_ 125 **T<sub>SETTLE</sub>** ns scale transition, High speed mode, 600 Ω 15-pF load Range = 255 µA, source mode, 340 pA/sqrtHz Current noise \_ \_ High speed mode,  $V_{DDA} = 5 V$ , 10 kHz

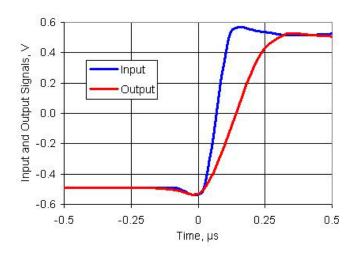

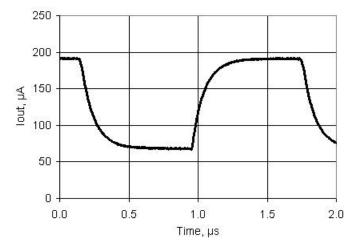

Figure 11-51. IDAC Step Response, Codes 0x40 - 0xC0, 255  $\mu$ A Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

# 11.6.7 USB

## Table 11-57. USB DC Specifications

| Parameter            | Description                                                                   | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | Device supply (V <sub>DDD</sub> ) for USB operation                           | USB configured, USB regulator<br>enabled                                                            | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                                                               | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>   |                                                                               | USB configured, USB regulator bypassed <sup>[60]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      | Device supply current in device<br>active mode, bus clock and IMO =<br>24 MHz | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | -    | 8   | -    | mA    |

| IUSB_Suspended       | Device supply current in device<br>sleep mode                                 | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | _    | 0.5 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | -    | 0.3 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | -    | 0.3 | -    | mA    |

## 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component data sheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

#### Table 11-58. UDB AC Specifications

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max   | Units |  |  |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|--|--|

| Datapath Per           | Datapath Performance                                          |                                                  |     |     |       |       |  |  |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | -   | _   | 67.01 | MHz   |  |  |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | _   | 67.01 | MHz   |  |  |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                  | -   | _   | 67.01 | MHz   |  |  |

| PLD Perform            | PLD Performance                                               |                                                  |     |     |       |       |  |  |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair |                                                  | -   | -   | 67.01 | MHz   |  |  |

| Clock to Outp          | but Performance                                               |                                                  |     |     |       |       |  |  |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-70. | 25 °C, $V_{DDD} \ge 2.7 V$                       | -   | 20  | 25    | ns    |  |  |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-70. | Worst-case placement, routing, and pin selection | _   | -   | 55    | ns    |  |  |

Note 60. Rise/fall time matching (TR) not guaranteed, see USB Driver AC Specifications on page 87.

□ 6: 64 KB

# **12.1 Part Numbering Conventions**

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

| CY8Cabcdefg-xxx                                                                                             |                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| ■ a: Architecture<br>□ 3: PSoC 3<br>□ 5: PSoC 5                                                             | <ul> <li>ef: Package code</li> <li>Two character alphanumeric</li> <li>AX: TQFP</li> </ul>                                              |

| <ul> <li>b: Family group within architecture</li> <li>4: CY8C34 family</li> <li>6: CY8C36 family</li> </ul> | □ LT: QFN<br>□ PV: SSOP<br>□ FN: CSP                                                                                                    |

| <ul> <li>□ 8: CY8C38 family</li> <li>■ c: Speed grade</li> <li>□ 4: 48 MHz</li> <li>□ 6: 67 MHz</li> </ul>  | <ul> <li>g: Temperature range</li> <li>□ C: commercial</li> <li>□ I: industrial</li> <li>□ A: automotive</li> </ul>                     |

| ■ d: Flash capacity<br>□ 4: 16 KB<br>□ 5: 32 KB                                                             | <ul> <li>xxx: Peripheral set</li> <li>Three character numeric</li> <li>No meaning is associated with these three characters.</li> </ul> |

Examples CY8C 3 8 6 6 P V I Х хх **Cypress Prefix** 3: PSoC 3 Architecture Family Group within Architecture 8: CY8C38 Family 6: 67 MHz Speed Grade 6: 64 KB Flash Capacity -**PV: SSOP** Package Code -I: Industrial Temperature Range — Peripheral Set —

Tape and reel versions of these devices are available and are marked with a "T" at the end of the part number.

All devices in the PSoC 3 CY8C38 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high-level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration data sheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.

# Table 14-1. Acronyms Used in this Document (continued)

| Acronym           | Description                                                  |  |  |

|-------------------|--------------------------------------------------------------|--|--|

| PHUB              | peripheral hub                                               |  |  |

| PHY               | physical layer                                               |  |  |

| PICU              | port interrupt control unit                                  |  |  |

| PLA               | programmable logic array                                     |  |  |

| PLD               | programmable logic device, see also PAL                      |  |  |

| PLL               | phase-locked loop                                            |  |  |

| PMDD              | package material declaration data sheet                      |  |  |

| POR               | power-on reset                                               |  |  |

| PRES              | precise low-voltage reset                                    |  |  |

| PRS               | pseudo random sequence                                       |  |  |

| PS                | port read data register                                      |  |  |

| PSoC <sup>®</sup> | Programmable System-on-Chip™                                 |  |  |

| PSRR              | power supply rejection ratio                                 |  |  |

| PWM               | pulse-width modulator                                        |  |  |

| RAM               | random-access memory                                         |  |  |

| RISC              | reduced-instruction-set computing                            |  |  |

| RMS               | root-mean-square                                             |  |  |

| RTC               | real-time clock                                              |  |  |

| RTL               | register transfer language                                   |  |  |

| RTR               | remote transmission request                                  |  |  |

| RX                | receive                                                      |  |  |

| SAR               | successive approximation register                            |  |  |

| SC/CT             | switched capacitor/continuous time                           |  |  |

| SCL               | I <sup>2</sup> C serial clock                                |  |  |

| SDA               | l <sup>2</sup> C serial data                                 |  |  |

| S/H               | sample and hold                                              |  |  |

| SINAD             | signal to noise and distortion ratio                         |  |  |

| SIO               | special input/output, GPIO with advanced features. See GPIO. |  |  |

| SOC               | start of conversion                                          |  |  |

# Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                            |

|---------|------------------------------------------------------------------------|

| SOF     | start of frame                                                         |

| SPI     | Serial Peripheral Interface, a communications protocol                 |

| SR      | slew rate                                                              |

| SRAM    | static random access memory                                            |

| SRES    | software reset                                                         |

| SWD     | serial wire debug, a test protocol                                     |

| SWV     | single-wire viewer                                                     |

| TD      | transaction descriptor, see also DMA                                   |

| THD     | total harmonic distortion                                              |

| TIA     | transimpedance amplifier                                               |

| TRM     | technical reference manual                                             |

| TTL     | transistor-transistor logic                                            |

| ТХ      | transmit                                                               |

| UART    | Universal Asynchronous Transmitter Receiver, a communications protocol |

| UDB     | universal digital block                                                |

| USB     | Universal Serial Bus                                                   |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port              |

| VDAC    | voltage DAC, see also DAC, IDAC                                        |

| WDT     | watchdog timer                                                         |

| WOL     | write once latch, see also NVL                                         |

| WRES    | watchdog timer reset                                                   |

| XRES    | external reset I/O pin                                                 |

| XTAL    | crystal                                                                |

# **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

# 17. Revision History

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|----------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| **       | 571504  | See ECN            | HMT                | New data sheet for new device Part Number family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| *A       | 754416  | See ECN            | HMT                | Prepare Preliminary for PR1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| *В       | 2253366 | See ECN            | DSG                | Prepare Preliminary2 for PR3total rewrite.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| *C       | 2350209 | See ECN            | DSG                | Minor change: Added "Confidential" watermark. Corrected typo on 68QFN pinout: pin 13 XREF to XRES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *D       | 2481747 | See ECN            | SFV                | Changed part numbers and data sheet title.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| *E       | 2521877 | See ECN            | DSG                | Prelim3 release-extensive spec, writing, and formatting changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| *F       | 2660161 | 02/16/09           | GDK                | Reorganized content to be consistent with the TRM. Added Xdata Space<br>Access SFRs and DAC sections. Updated Boost Converter section and<br>Conversion Signals section. Classified Ordering Information according to CP<br>speed; added information on security features and ROHS compliance<br>Added a section on XRES Specifications under Electrical Specification.<br>Updated Analog Subsystem and CY8C35/55 Architecture block diagrams.<br>Updated Electrical Specifications. Renamed CyDesigner as PSoC Creator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| *G       | 2712468 | 05/29/09           | MKEA               | Updates to Electrical Specifications. Added Analog Routing section<br>Updates to Ordering Information table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| *H       | 2758970 | 09/02/09           | MKEA               | Updated Part Numbering Conventions. Added Section 11.7.5 (EMIF Figures<br>and Tables). Updated GPIO and SIO AC specifications. Updated XRES Pin<br>Description and Xdata Address Map specifications. Updated DFB and<br>Comparator specifications. Updated PHUB features section and RTC in slee<br>mode. Updated IDAC and VDAC DC and Analog Global specifications<br>Updated USBIO AC and Delta Sigma ADC specifications. Updated PPOR an<br>Voltage Monitors DC specifications. Updated Drive Mode diagram<br>Added 48-QFN Information. Updated other electrical specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *        | 2824546 | 12/09/09           | MKEA               | Updated I2C section to reflect 1 Mbps. Updated Table 11-6 and 11-7 (Boost<br>AC and DC specs); also added Shottky Diode specs. Changed current for<br>sleep/hibernate mode to include SIO; Added footnote to analog global specs<br>Updated Figures 1-1, 6-2, 7-14, and 8-1. Updated Table 6-2 and Table 6-3<br>(Hibernate and Sleep rows) and Power Modes section. Updated GPIO and SIA<br>AC specifications. Updated Gain error in IDAC and VDAC specifications.<br>Updated description of V <sub>DDA</sub> spec in Table 11-1 and removed GPIO Clamp<br>Current parameter. Updated number of UDBs on page 1.<br>Moved FILO from ILO DC to AC table.<br>Added PCB Layout and PCB Schematic diagrams.<br>Updated Fgpioout spec (Table 11-9). Added duty cycle frequency in PLL AC<br>spec table. Added note for Sleep and Hibernate modes and Active Mode spec<br>in Table 11-2. Linked URL in Section 10.3 to PSoC Creator site.<br>Updated Ja and Jc values in Table 13-1. Updated Single Sample Mode and<br>Fast FIR Mode sections. Updated Input Resistance specification in Del-Sig<br>ADC table. Added Tio_init parameter. Updated PGA and UGB AC Specs.<br>Removed SPC ADC. Updated Boost Converter section.<br>Added section 'SIO as Comparator'; updated Hysteresis spec (differential<br>mode) in Table 11-10.<br>Updated V <sub>BAT</sub> condition and deleted Vstart parameter in Table 11-6.<br>Added 'Bytes' column for Tables 4-1 to 4-5. |  |

| *ئ       | 2873322 | 02/04/10           | MKEA               | Changed maximum value of PPOR_TR to '1'. Updated V <sub>BIAS</sub> specification.<br>Updated PCB Schematic. Updated Figure 8-1 and Figure 6-3. Updated<br>Interrupt Vector table, Updated Sales links. Updated JTAG and SWD specific<br>cations. Removed Jp-p and Jperiod from ECO AC Spec table. Added note of<br>sleep timer in Table 11-2. Updated ILO AC and DC specifications. Added<br>Resolution parameter in VDAC and IDAC tables. Updated I <sub>OUT</sub> typical and<br>maximum values. Changed Temperature Sensor range to -40 °C to +85 °C.<br>Removed Latchup specification from Table 11-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |