#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB             |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 72-UFBGA, WLCSP                                                             |

| Supplier Device Package    | 72-WLCSP (4.3x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866fni-210t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1. A | rchitectural Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 4                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|      | inouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| 3. F | in Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                                         |

|      | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|      | 4.1 8051 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                         |

|      | 4.2 Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                         |

|      | 4.3 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|      | 4.4 DMA and PHUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|      | 4.5 Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| 5. N | lemory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|      | 5.1 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|      | 5.2 Flash Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

|      | 5.3 Flash Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|      | 5.4 EEPROM<br>5.5 Nonvolatile Latches (NVLs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|      | 5.6 External Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 <del>4</del><br>25                                                       |

|      | 5.7 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| 6 9  | system Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 0. 0 | 6.1 Clocking System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|      | 6.2 Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|      | 6.3 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

|      | 6.4 I/O System and Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 7. C | igital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                         |

| 7. C | igital Subsystem<br>7.1 Example Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 7. C | <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44<br>46                                                                   |

| 7. C | <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li><li>7.3 UDB Array Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>46<br>49                                                             |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | 44<br>46<br>49<br>49                                                       |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> </ul>                                                                                                                                                                                                                                                                                                                                                        | 44<br>46<br>49<br>49<br>51                                                 |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> </ul>                                                                                                                                                                                                                                                                                                                                       | 44<br>46<br>49<br>49<br>51<br>53                                           |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> </ul>                                                                                                                                                                                                                                                                                               | 44<br>49<br>49<br>51<br>53<br>53                                           |

| 7. C | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> </ul>                                                                                                                                                                                                                                                                   | 44<br>49<br>49<br>51<br>53<br>53<br>54                                     |

|      | <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul>                                                                                                                                                                                                                                 | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56                               |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem                                                                                                                                                                                                                                   | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br><b>56</b>                  |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>analog Subsystem</b> 8.1 Analog Routing                                                                                                                                                                                                                | 44<br>49<br>49<br>51<br>53<br>53<br>53<br>54<br>56<br>57                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC                                                                                                                                                                                                    | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators                                                                                                                                                                            | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59<br>60             |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>malog Subsystem</b> 8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks                                                                                                    | 44<br>49<br>49<br>51<br>53<br>53<br>54<br>56<br>57<br>59<br>60<br>61<br>61 |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive                                                                                      | 44<br>49<br>49<br>53<br>53<br>53<br>56<br>57<br>59<br>60<br>61<br>61<br>62 |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block <b>nalog Subsystem</b> 8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense                                                  | 44<br>49<br>49<br>53<br>53<br>54<br>56<br>57<br>60<br>61<br>62<br>63       |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor                 | 44<br>49<br>53<br>53<br>54<br>55<br>57<br>60<br>61<br>62<br>63<br>63       |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor         8.9 DAC | 44<br>49<br>53<br>53<br>55<br>56<br>61<br>62<br>63<br>64                   |

|      | 7.1 Example Peripherals         7.2 Universal Digital Block         7.3 UDB Array Description         7.4 DSI Routing Interface Description         7.5 CAN         7.6 USB         7.7 Timers, Counters, and PWMs         7.8 I <sup>2</sup> C         7.9 Digital Filter Block         nalog Subsystem         8.1 Analog Routing         8.2 Delta-sigma ADC         8.3 Comparators         8.4 Opamps         8.5 Programmable SC/CT Blocks         8.6 LCD Direct Drive         8.7 CapSense         8.8 Temp Sensor                 | 44<br>49<br>53<br>53<br>55<br>56<br>57<br>50<br>61<br>62<br>63<br>64<br>64 |

| 9. Programming, Debug Interfaces, Resources           |     |

|-------------------------------------------------------|-----|

| 9.1 JTAG Interface                                    |     |

| 9.2 Serial Wire Debug Interface<br>9.3 Debug Features |     |

| 9.4 Trace Features                                    |     |

| 9.5 Single Wire Viewer Interface                      |     |

| 9.6 Programming Features                              |     |

| 9.7 Device Security                                   |     |

| 9.8 CSP Package Bootloader                            | 69  |

| 10. Development Support                               | 70  |

| 10.1 Documentation                                    | 70  |

| 10.2 Online                                           |     |

| 10.3 Tools                                            |     |

| 11. Electrical Specifications                         |     |

| 11.1 Absolute Maximum Ratings                         |     |

| 11.2 Device Level Specifications                      |     |

| 11.3 Power Regulators<br>11.4 Inputs and Outputs      |     |

| 11.5 Analog Peripherals                               |     |

| 11.6 Digital Peripherals                              |     |

| 11.7 Memory                                           | 112 |

| 11.8 PSoC System Resources                            |     |

| 11.9 Clocking                                         | 119 |

| 12. Ordering Information                              |     |

| 12.1 Part Numbering Conventions                       |     |

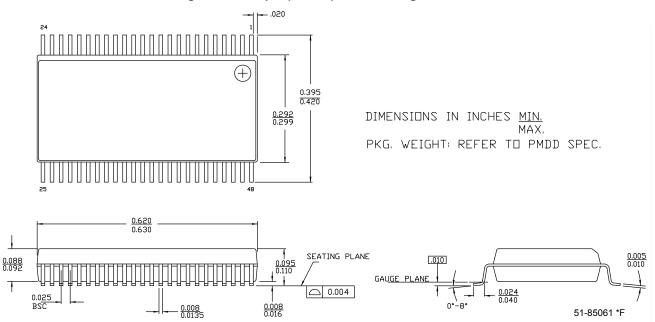

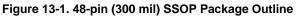

| 13. Packaging                                         | 125 |

| 14. Acronyms                                          | 129 |

| 15. Reference Documents                               | 130 |

| 16. Document Conventions                              | 131 |

| 16.1 Units of Measure                                 | 131 |

| 17. Revision History                                  | 132 |

| 18. Sales, Solutions, and Legal Information           | 140 |

| Worldwide Sales and Design Support                    |     |

| Products                                              |     |

| PSoC® Solutions                                       |     |

| Cypress Developer Community                           |     |

| Technical Support                                     | 140 |

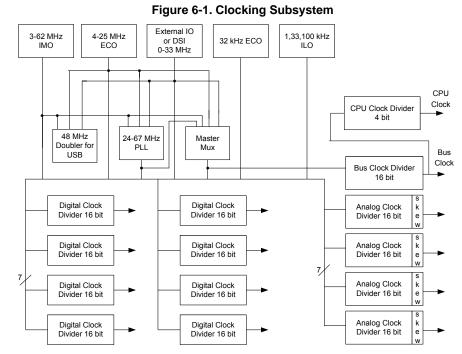

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C38 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as  $1.8 V \pm 5\%$ ,  $2.5 V \pm 10\%$ ,  $3.3 V \pm 10\%$ , or  $5.0 V \pm 10\%$ , or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery or solar cell. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3-V supply for LCD glass drive. The boost's output is available on the VBOOST pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a  $1-\mu$ A sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 31 of this data sheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 65 of this data sheet.

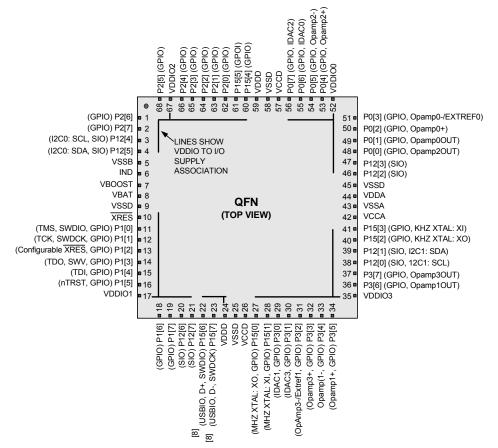

# 2. Pinouts

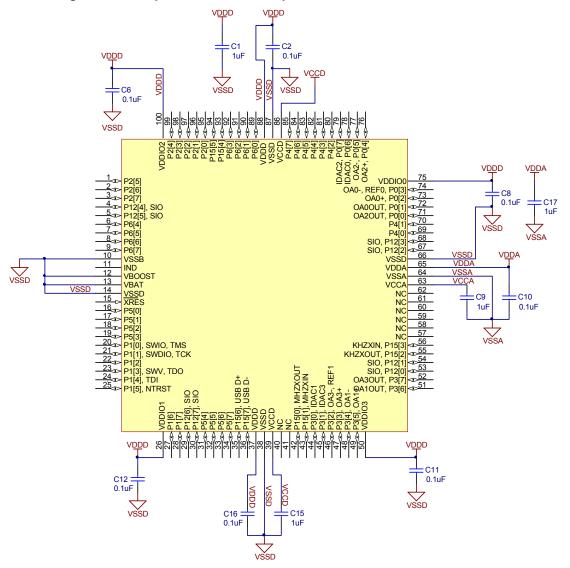

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-6, as well as Table 2-1, show the pins that are powered by each VDDIO.

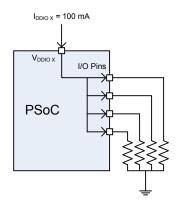

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

#### Figure 2-1. VDDIO Current Limit

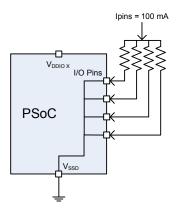

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

# Figure 2-5. 68-pin QFN Part Pinout<sup>[7]</sup>

Notes

The center pad on the QFN package should be connected to digital ground (V<sub>SSD</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices 7

8. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating

# Figure 2-7. Example Schematic for 100-pin TQFP Part with Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

# 5. Memory

# 5.1 Static RAM

CY8C38 SRAM is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 26. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

# 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for ECC. If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

# 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a bootloader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the "Device Security" section on page 68). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

#### Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as 'unbreakable'. Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C38 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the 8051 xdata space, the CPU can not execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

# 6. System Integration

# 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 66 MHz clock, accurate to  $\pm 1$  percent over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC. Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 62-MHz IMO, ±1% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30.

- DSI signal from an external I/O pin or other logic

- 24- to 67-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- 1-kHz, 33-kHz, 100-kHz ILO for WDT and sleep timer

32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                         |

|---------|--------|----------------------------------|---------|-------------------|--------------------------------------|

| IMO     | 3 MHz  | ±1% over voltage and temperature | 62 MHz  | ±7%               | 13 µs max                            |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is crystal dependent   |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                      |

| PLL     | 24 MHz | Input dependent                  | 67 MHz  | Input dependent   | 250 µs max                           |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                             |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode       |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is crystal dependent |

#### Table 6-1. Oscillator Summary

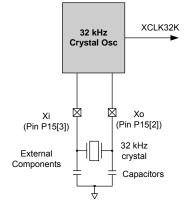

# Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 80.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The master clock is used to select and supply the fastest clock in the system for general clock requirements and clock synchronization of the PSoC device.

- Bus clock 16-bit divider uses the master clock to generate the bus clock used for data transfers. Bus clock is the source clock for the CPU clock divider.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the UDBs and fixed function timer/counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50 percent duty cycle clocks, master clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

#### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

#### Figure 6-10. SIO Input/Output Block Diagram

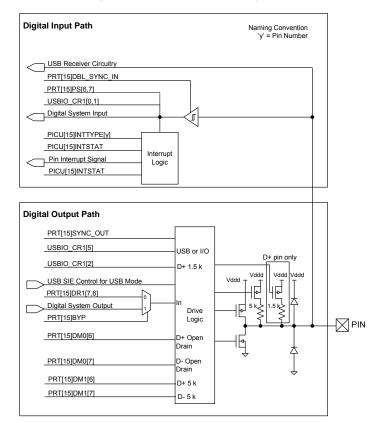

Figure 6-11. USBIO Block Diagram

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

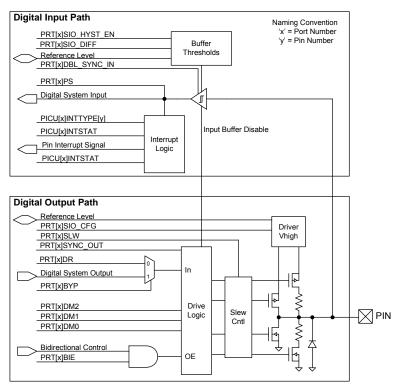

#### ■ High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

■ High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pullup and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the I<sup>2</sup>C bus signal lines.

Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pullup and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

# 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

#### 6.4.5 Pin Interrupts

All GPIO and SIO pins are able to generate interrupts to the system. All eight pins in each port interface to their own Port Interrupt Control Unit (PICU) and associated interrupt vector. Each pin of the port is independently configurable to detect rising edge, falling edge, both edge interrupts, or to not generate an interrupt.

Depending on the configured mode for each pin, each time an interrupt event occurs on a pin, its corresponding status bit of the interrupt status register is set to '1' and an interrupt request is sent to the interrupt controller. Each PICU has its own interrupt vector in the interrupt controller and the pin status register providing easy determination of the interrupt source down to the pin level.

Port pin interrupts remain active in all sleep modes allowing the PSoC device to wake from an externally generated interrupt. While level sensitive interrupts are not directly supported; UDB provide this functionality to the system when needed.

#### 6.4.6 Input Buffer Mode

GPIO and SIO input buffers can be configured at the port level for the default CMOS input thresholds or the optional LVTTL input thresholds. All input buffers incorporate Schmitt triggers for input hysteresis. Additionally, individual pin input buffers can be disabled in any drive mode.

#### 6.4.7 I/O Power Supplies

Up to four I/O pin power supplies are provided depending on the device and package. Each I/O supply must be less than or equal to the voltage on the chip's analog (VDDA) pin. This feature allows users to provide different I/O voltage levels for different pins on the device. Refer to the specific device package pinout to determine VDDIO capability for a given port and pin. The SIO port pins support an additional regulated high output capability, as described in Adjustable Output Level.

#### 6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may be used as analog inputs or outputs. The analog voltage present on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs. Each GPIO may connect to one of the analog global busses or to one of the analog mux buses to connect any pin to any internal analog resource such as ADC or comparators. In addition, select pins provide direct connections to specific analog features such as the high current DACs or uncommitted opamps.

#### 6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be used to create CapSense buttons and sliders<sup>[15]</sup>. See the "CapSense" section on page 63 for more information.

#### 6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be used to generate Segment and Common drive signals for direct glass drive of LCD glass. See the "LCD Direct Drive" section on page 62 for details.

#### 6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the ability to provide a regulated high output level for interface to external signals that are lower in voltage than the SIO's respective VDDIO. SIO pins are individually configurable to output either the standard VDDIO level or the regulated output, which is based on an internally generated reference. Typically a voltage DAC (VDAC) is used to generate the reference (see Figure 6-13). The "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins. Resistive pullup and pull-down drive modes are not available with SIO in regulated output mode.

#### 6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support the standard CMOS and LVTTL input levels but also support a differential mode with programmable levels. SIO pins are grouped into pairs. Each pair shares a reference generator block which, is used to set the digital input buffer reference level for interface to external signals that differ in voltage from VDDIO. The reference sets the pins voltage threshold for a high logic level (see Figure 6-13). Available input thresholds are:

- 0.5 × VDDIO

- 0.4 × VDDIO

- $\blacksquare 0.5 \times V_{REF}$

- V<sub>REF</sub>

Typically a voltage DAC (VDAC) generates the V<sub>REF</sub> reference. "DAC" section on page 64 has more details on VDAC use and reference routing to the SIO pins.

<sup>15.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

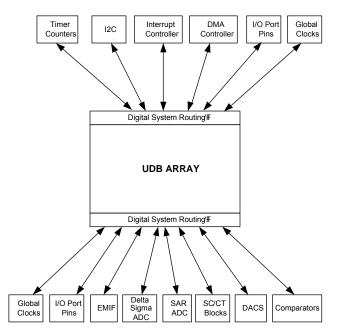

#### Figure 7-9. Digital System Interconnect

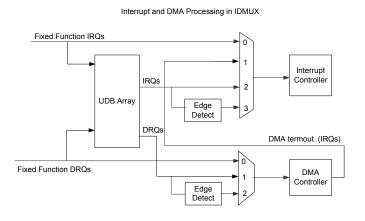

Interrupt and DMA routing is very flexible in the CY8C38 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

# Figure 7-10. Interrupt and DMA Processing in the IDMUX

# 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

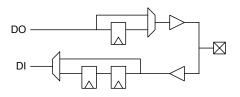

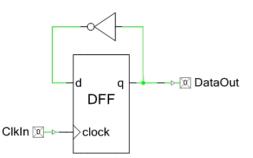

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

#### Figure 7-11. I/O Pin Synchronization Routing

Figure 7-12. I/O Pin Output Connectivity

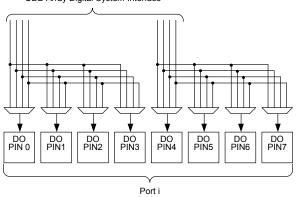

8 IO Data Output Connections from the UDB Array Digital System Interface

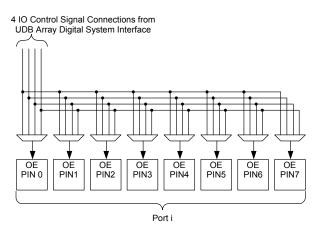

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

#### Figure 7-13. I/O Pin Output Enable Connectivity

# 7.5 CAN

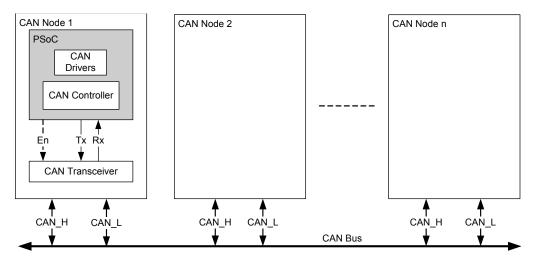

The CAN peripheral is a fully functional controller area network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- □ Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE, and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

- CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

# 7.9 Digital Filter Block

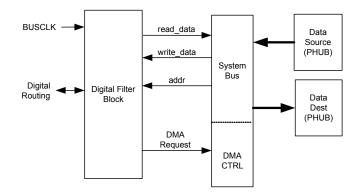

Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

#### Figure 7-20. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

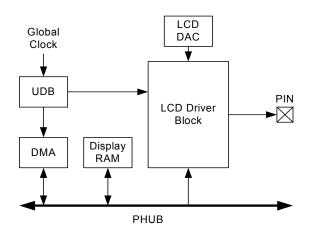

#### Figure 8-10. LCD System

#### 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through the DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a Delta-sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

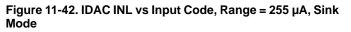

Table 11-32. IDAC DC Specifications (continued)

| Parameter       | Description                                  | Conditions                                         | Min | Тур | Max | Units |

|-----------------|----------------------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Operating current, code = 0                  | Low speed mode, source mode, range = 31.875 µA     | -   | 44  | 100 | μA    |

|                 |                                              | Low speed mode, source mode, range = 255 µA,       | -   | 33  | 100 | μA    |

|                 |                                              | Low speed mode, source mode,<br>range = 2.04 mA    | -   | 33  | 100 | μΑ    |

|                 | Low speed mode, sink mode, range = 31.875 µA | -                                                  | 36  | 100 | μA  |       |

|                 |                                              | Low speed mode, sink mode,<br>range = 255 µA       | -   | 33  | 100 | μA    |

|                 |                                              | Low speed mode, sink mode,<br>range = 2.04 mA      | -   | 33  | 100 | μA    |

|                 |                                              | High speed mode, source mode,<br>range = 31.875 μA | -   | 310 | 500 | μA    |

|                 |                                              | High speed mode, source mode, range = 255 µA       | -   | 305 | 500 | μΑ    |

|                 |                                              | High speed mode, source mode,<br>range = 2.04 mA   | -   | 305 | 500 | μΑ    |

|                 |                                              | High speed mode, sink mode,<br>range = 31.875 μA   | -   | 310 | 500 | μA    |

|                 |                                              | High speed mode, sink mode,<br>range = 255 µA      | -   | 300 | 500 | μA    |

|                 |                                              | High speed mode, sink mode,<br>range = 2.04 mA     | -   | 300 | 500 | μA    |

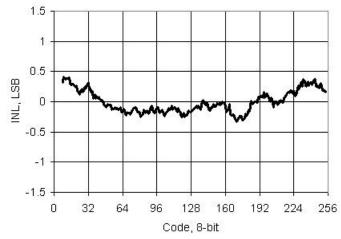

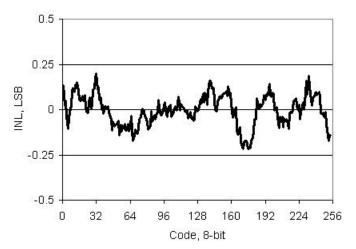

# Figure 11-41. IDAC INL vs Input Code, Range = 255 $\mu$ A, Source Mode

# Figure 11-55. VDAC INL vs Input Code, 1 V Mode

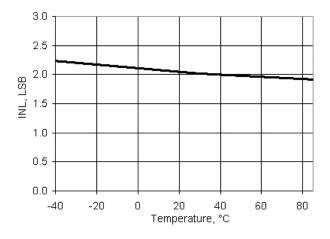

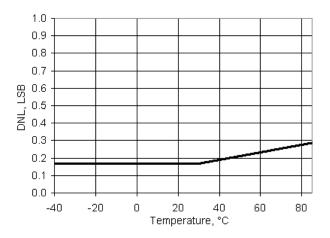

Figure 11-57. VDAC INL vs Temperature, 1 V Mode

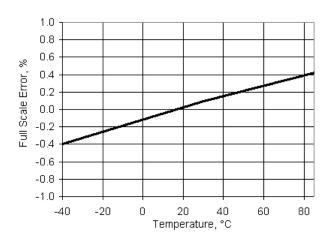

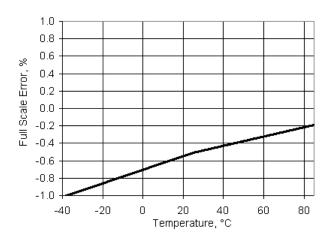

Figure 11-59. VDAC Full Scale Error vs Temperature, 1 V Mode

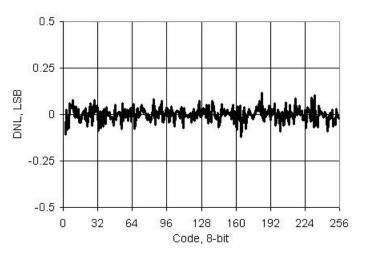

Figure 11-56. VDAC DNL vs Input Code, 1 V Mode

Figure 11-58. VDAC DNL vs Temperature, 1 V Mode

Figure 11-60. VDAC Full Scale Error vs Temperature, 4 V Mode

# 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT analog block; see the TIA component data sheet in PSoC Creator for full electrical specifications and APIs.

| Table 11-38. | Transimpedance | Amplifier ( | (TIA) DC | <b>Specifications</b> |

|--------------|----------------|-------------|----------|-----------------------|

|--------------|----------------|-------------|----------|-----------------------|

| Parameter         | Description                           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IOFF</sub> | Input offset voltage                  |                      | -   | -   | 10  | mV    |

| Rconv             | Conversion resistance <sup>[58]</sup> | R = 20K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 30K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 40K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 80K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 120K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R = 250K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R= 500K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 1M; 40 pF load   | -25 | -   | +35 | %     |

|                   | Quiescent current                     |                      | -   | 1.1 | 2   | mA    |

# Table 11-39. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions           | Min  | Тур | Max | Units |

|-----------|-------------------------|----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (-3 dB) | R = 20K; –40 pF load | 1500 | -   | -   | kHz   |

|           |                         |                      |      |     |     |       |

|           |                         | R = 120K;            | 240  | -   | -   | kHz   |

|           |                         | R = 1M; –40 pF load  | 25   | -   | -   | kHz   |

Note

58. Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

# 11.6.7 USB

#### Table 11-57. USB DC Specifications

| Parameter            | Description                                                                   | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | Device supply (V <sub>DDD</sub> ) for USB operation                           | USB configured, USB regulator<br>enabled                                                            | 4.35 | -   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                                                               | USB configured, USB regulator bypassed                                                              | 3.15 | -   | 3.6  | V     |

| V <sub>USB_3</sub>   | -                                                                             | USB configured, USB regulator bypassed <sup>[60]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      | Device supply current in device<br>active mode, bus clock and IMO =<br>24 MHz | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | -    | 8   | -    | mA    |

| IUSB_Suspended       | Device supply current in device sleep mode                                    | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | _    | 0.5 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | -    | 0.3 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | _    | 0.5 | -    | mA    |

|                      |                                                                               | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | -    | 0.3 | -    | mA    |

#### 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component data sheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

#### Table 11-58. UDB AC Specifications