#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

ЭХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866lti-067 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

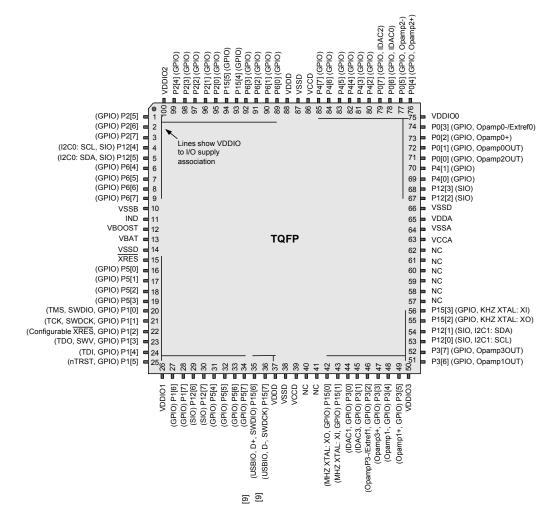

### Figure 2-6. 100-pin TQFP Part Pinout

| Table 2-1. | V <sub>DDIO</sub> and | l Port Pin | Associations |

|------------|-----------------------|------------|--------------|

|------------|-----------------------|------------|--------------|

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

Note 9. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

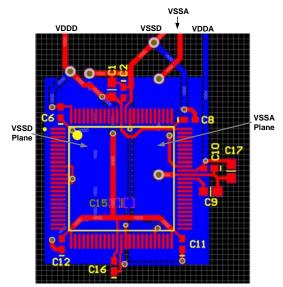

### Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

# 3. Pin Descriptions

### IDAC0, IDAC1, IDAC2, IDAC3

Low resistance output pin for high current DACs (IDAC).

### Opamp0OUT, Opamp1OUT, Opamp2OUT, Opamp3OUT

High current output of uncommitted opamp<sup>[11]</sup>.

### Extref0, Extref1

External reference input to the analog system.

### Opamp0–, Opamp1–, Opamp2–, Opamp3–

Inverting input to uncommitted opamp.

### Opamp0+, Opamp1+, Opamp2+, Opamp3+

Noninverting input to uncommitted opamp.

### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[11]</sup>.

### I2C0: SCL, I2C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

### I2C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

### IND

Inductor connection to boost pump.

# kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

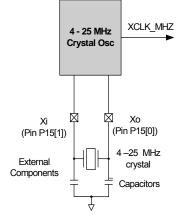

### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

### nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

### SWDCK

Serial wire debug clock programming and debug port connection.

### **SWDIO**

Serial wire debug input and output programming and debug port connection.

### SWV

Single wire viewer debug output.

### тск

JTAG test clock programming and debug port connection.

### TDI

JTAG test data in programming and debug port connection.

### TDO

JTAG test data out programming and debug port connection.

#### Note

11. GPIOs with opamp outputs are not recommended for use with CapSense.

### Table 4-3. Data Transfer Instructions

| Mr       | nemonic      | Description                                            | Bytes | Cycles |

|----------|--------------|--------------------------------------------------------|-------|--------|

| MOV A,F  | Rn           | Move register to accumulator                           | 1     | 1      |

| MOV A,[  | Direct       | Move direct byte to accumulator                        | 2     | 2      |

| MOV A,@  | @Ri          | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV A,#  | #data        | Move immediate data to accumulator                     | 2     | 2      |

| MOV Rn   | ı,A          | Move accumulator to register                           | 1     | 1      |

| MOV Rn   | n,Direct     | Move direct byte to register                           | 2     | 3      |

| MOV Rn   | n, #data     | Move immediate data to register                        | 2     | 2      |

| MOV Dir  | rect, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV Dir  | rect, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV Dir  | rect, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV Dir  | rect, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV Dir  | rect, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV @    | Ri, A        | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @    | Ri, Direct   | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @    | Ri, #data    | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DF   | PTR, #data16 | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A,  | @A+DPTR      | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A,  | @A + PC      | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,  | @Ri          | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A,  | @DPTR        | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @   | Ri, A        | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @   | DPTR, A      | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Dir | rect         | Push direct byte onto stack                            | 2     | 3      |

| POP Di   | rect         | Pop direct byte from stack                             | 2     | 2      |

| XCH A,   | Rn           | Exchange register with accumulator                     | 1     | 2      |

| XCH A,   | Direct       | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A,   | @Ri          | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A,  | @Ri          | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

### Table 4-4. Boolean Instructions

| Mnemonic   | Description             | Bytes | Cycles |

|------------|-------------------------|-------|--------|

| CLR C      | Clear carry             | 1     | 1      |

| CLR bit    | Clear direct bit        | 2     | 3      |

| SETB C     | Set carry               | 1     | 1      |

| SETB bit   | Set direct bit          | 2     | 3      |

| CPL C      | Complement carry        | 1     | 1      |

| CPL bit    | Complement direct bit   | 2     | 3      |

| ANL C, bit | AND direct bit to carry | 2     | 2      |

#### 6.1.1 Internal Oscillators

Figure 6-1 shows that there are two internal oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm$ 1-percent accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm$ 1 percent at 3 MHz, up to  $\pm$ 7 percent at 62 MHz. The IMO, in conjunction with the PLL, allows generation of other clocks up to the device's maximum frequency (see PLL). The IMO provides clock outputs at 3, 6, 12, 24, 48, and 62 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works at input frequency of 24 MHz, providing 48 MHz for the USB. It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin).

#### 6.1.1.3 PLL

The PLL allows low-frequency, high-accuracy clocks to be multiplied to higher frequencies. This is a trade off between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 67 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the other clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHZECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz. The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power master clock. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate other clocks up to the device's maximum frequency (see PLL). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

#### Figure 6-2. MHzECO Block Diagram

### 6.1.2.2 32.768-kHz ECO

The 32.768-kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

### ■ High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

■ High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pullup and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the I<sup>2</sup>C bus signal lines.

Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pullup and pull-down are not available with SIO in regulated output mode.

### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

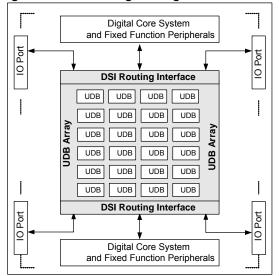

# 7. Digital Subsystem

The digital programmable system creates application specific combinations of both standard and advanced digital peripherals and custom logic functions. These peripherals and logic are then interconnected to each other and to any pin on the device, providing a high level of design flexibility and IP security.

The features of the digital programmable system are outlined here to provide an overview of capabilities and architecture. You do not need to interact directly with the programmable digital system at the hardware and register level. PSoC Creator provides a high level schematic capture graphical interface to automatically place and route resources similar to PLDs.

The main components of the digital programmable system are:

- UDB These form the core functionality of the digital programmable system. UDBs are a collection of uncommitted logic (PLD) and structural logic (Datapath) optimized to create all common embedded peripherals and customized functionality that are application or design specific.

- Universal digital block array UDB blocks are arrayed within a matrix of programmable interconnect. The UDB array structure is homogeneous and allows for flexible mapping of digital functions onto the array. The array supports extensive and flexible routing interconnects between UDBs and the Digital System Interconnect.

- Digital system interconnect (DSI) Digital signals from UDBs, fixed function peripherals, I/O pins, interrupts, DMA, and other system core signals are attached to the digital system interconnect to implement full featured device connectivity. The DSI allows any digital function to any pin or other feature routability when used with the universal digital block array.

#### Figure 7-1. CY8C38 Digital Programmable Architecture

### 7.1 Example Peripherals

The flexibility of the CY8C38 family's UDBs and analog blocks allow the user to create a wide range of components (peripherals). The most common peripherals were built and characterized by Cypress and are shown in the PSoC Creator component catalog, however, users may also create their own custom components using PSoC Creator. Using PSoC Creator, users may also create their own components for reuse within their organization, for example sensor interfaces, proprietary algorithms, and display interfaces.

The number of components available through PSoC Creator is too numerous to list in the data sheet, and the list is always growing. An example of a component available for use in CY8C38 family, but, not explicitly called out in this data sheet is the UART component.

#### 7.1.1 Example Digital Components

The following is a sample of the digital components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Communications

- □ I<sup>2</sup>C

- u UART

- 🛛 SPI

- Functions

- B EMIF

- □ PWMs

- Timers

- Counters

- Logic

- NOT

- ם OR

- D XOR

- ם AND

### 7.1.2 Example Analog Components

The following is a sample of the analog components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- Amplifiers

- □ TIA

- D PGA

- □ opamp

- ADC

- Delta-sigma

- DACs

- Current

- □ Voltage

- Comparators

- Mixers

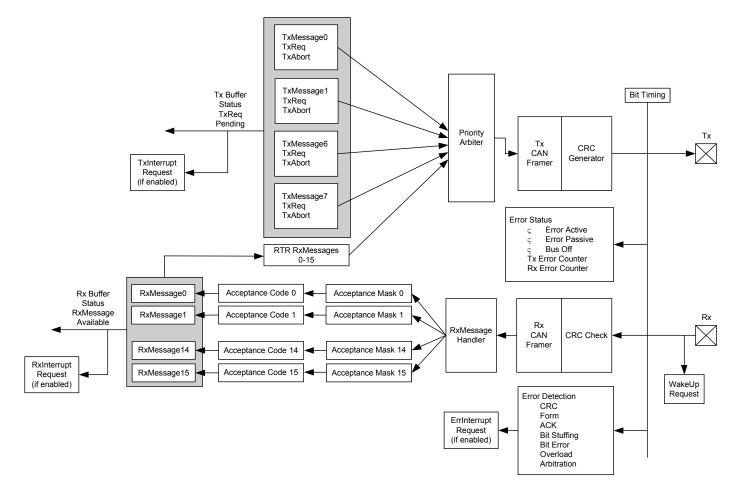

Figure 7-15. CAN Controller Block Diagram

### 8.3.2 LUT

The CY8C38 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | <b>FALSE</b> ('0')              |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT A) AND B                   |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT A) OR B                    |

| 1110b        | A NAND B                        |

| 1111b        | <b>TRUE</b> ('1')               |

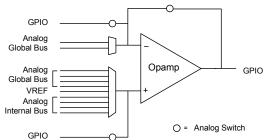

### 8.4 Opamps

The CY8C38 family of devices contain up to four general purpose opamps in a device.

### Figure 8-6. Opamp

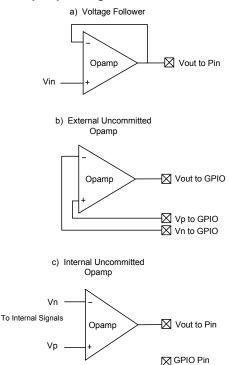

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-7. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

#### Figure 8-7. Opamp Configurations

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

### 8.5 Programmable SC/CT Blocks

The CY8C38 family of devices contains up to four switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity, V<sub>REF</sub> connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

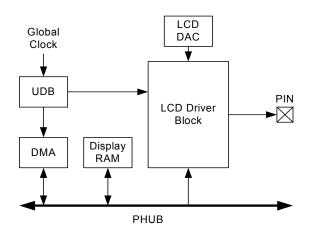

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

### Figure 8-10. LCD System

### 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through the DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a Delta-sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

### **11.3 Power Regulators**

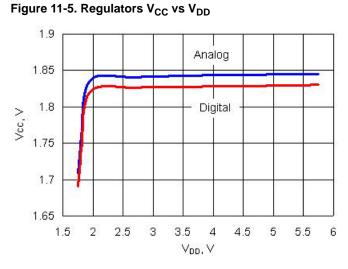

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.3.1 Digital Core Regulator

### Table 11-4. Digital Core Regulator DC Specifications

| Parameter        | Description                | Conditions                                                                                                                                                 | Min | Тур  | Max | Units |

|------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| V <sub>DDD</sub> | Input voltage              |                                                                                                                                                            | 1.8 | -    | 5.5 | V     |

| V <sub>CCD</sub> | Output voltage             |                                                                                                                                                            | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | $\pm 10\%$ , X5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 31 | 0.9 | 1    | 1.1 | μF    |

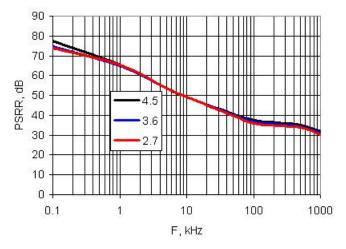

### Figure 11-6. Digital Regulator PSRR vs Frequency and V<sub>DD</sub>

### 11.3.2 Analog Core Regulator

### Table 11-5. Analog Core Regulator DC Specifications

| Parameter        | Description                | Conditions                  | Min | Тур  | Max | Units |

|------------------|----------------------------|-----------------------------|-----|------|-----|-------|

| V <sub>DDA</sub> | Input voltage              |                             | 1.8 | -    | 5.5 | V     |

| V <sub>CCA</sub> | Output voltage             |                             | -   | 1.80 | _   | V     |

|                  | Regulator output capacitor | ±10%, X5R ceramic or better | 0.9 | 1    | 1.1 | μF    |

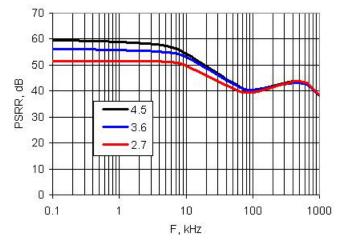

Figure 11-7. Analog Regulator PSRR vs Frequency and V<sub>DD</sub>

5 4 3 Voh, V 2 Vddio = 5V Vddio = 3.3V 1 Vddio = 1.8V 0 0 5 10 15 20 25 30 loh, mA

# 2.0 Vddio = 5V 1.5 Vddio = 3.3V Vddio = 1.8V 0.5 0.0 0 5 10 15 20 25 Iol, mA

Figure 11-16. GPIO Output Low Voltage and Current

### Figure 11-15. GPIO Output High Voltage and Current

# Table 11-10. GPIO AC Specifications

| Parameter  | Description                                                                             | Conditions                            | Min | Тур | Max | Units |

|------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF     | Rise time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TfallF     | Fall time in Fast Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TriseS     | Rise time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS     | Fall time in Slow Strong Mode <sup>[41]</sup>                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

|            | GPIO output operating frequency                                                         |                                       |     |     |     |       |

|            | 2.7 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V, fast strong drive mode                     | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

| Fgpioout   | 1.71 V $\leq$ V <sub>DDIO</sub> < 2.7 V, fast strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20  | MHz   |

|            | $3.3 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 7   | MHz   |

|            | 1.71 V $\leq$ V <sub>DDIO</sub> < 3.3 V, slow strong drive mode                         | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin    | GPIO input operating frequency                                                          |                                       |     |     |     |       |

| i gpioliti | 1.71 V <u>&lt;</u> V <sub>DDIO</sub> <u>&lt;</u> 5.5 V                                  | 90/10% V <sub>DDIO</sub>              | -   | -   | 33  | MHz   |

30

### 11.4.2 SIO

### Table 11-11. SIO DC Specifications

| Parameter       | Description                                                   | Conditions                                                                 | Min                     | Тур | Max                     | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| Vinmax          | Maximum input voltage                                         | All allowed values of $V_{DDIO}$ and $V_{DDD}$ , see Section 11.1          | -                       | -   | 5.5                     | V     |

| Vinref          | Input voltage reference<br>(Differential input mode)          |                                                                            | 0.5                     | -   | $0.52 \times V_{DDIO}$  | V     |

|                 | Output voltage reference (Regulat                             | ed output mode)                                                            | L II                    |     |                         |       |

| Voutref         |                                                               | V <sub>DDIO</sub> > 3.7                                                    | 1                       | _   | V <sub>DDIO</sub> – 1   | V     |

|                 |                                                               | V <sub>DDIO</sub> < 3.7                                                    | 1                       | _   | V <sub>DDIO</sub> - 0.5 | V     |

|                 | Input voltage high threshold                                  |                                                                            | L II                    |     |                         |       |

| V <sub>IH</sub> | GPIO mode                                                     | CMOS input                                                                 | $0.7 \times V_{DDIO}$   | -   | -                       | V     |

|                 | Differential input mode <sup>[42]</sup>                       | Hysteresis disabled                                                        | SIO_ref + 0.2           | _   | _                       | V     |

|                 | Input voltage low threshold                                   | 1                                                                          | L I                     |     | -1                      |       |

| V <sub>IL</sub> | GPIO mode                                                     | CMOS input                                                                 | _                       | _   | $0.3 \times V_{DDIO}$   | V     |

|                 | Differential input mode <sup>[42]</sup>                       | Hysteresis disabled                                                        | _                       | _   | SIO_ref - 0.2           | V     |

|                 | Output voltage high                                           |                                                                            | I                       |     | -1                      |       |

| N/              | Unregulated mode                                              | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                          | V <sub>DDIO</sub> – 0.4 | _   | -                       | V     |

| V <sub>OH</sub> | Regulated mode <sup>[42]</sup>                                | I <sub>OH</sub> = 1 mA                                                     | SIO_ref-0.65            | -   | SIO_ref + 0.2           | V     |

|                 | Regulated mode <sup>[42]</sup>                                | I <sub>OH</sub> = 0.1 mA                                                   | SIO_ref – 0.3           | -   | SIO_ref + 0.2           | V     |

| V <sub>OL</sub> | Output voltage low                                            | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 25 mA                        | _                       | -   | 0.8                     | V     |

|                 |                                                               | V <sub>DDIO</sub> = 3.30 V, I <sub>OL</sub> = 20 mA                        | _                       | -   | 0.4                     | V     |

|                 |                                                               | V <sub>DDIO</sub> = 1.80 V, I <sub>OL</sub> = 4 mA                         | _                       | _   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                              |                                                                            | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                            |                                                                            | 3.5                     | 5.6 | 8.5                     | kΩ    |

| IIL             | Input leakage current<br>(Absolute value) <sup>[43]</sup>     |                                                                            |                         |     |                         |       |

|                 | V <sub>IH</sub> ≤ Vddsio                                      | 25 °C, Vddsio = $3.0 \text{ V}$ , $\text{V}_{\text{IH}}$ = $3.0 \text{ V}$ | _                       | _   | 14                      | nA    |

|                 | V <sub>IH</sub> > Vddsio                                      | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                               | _                       | _   | 10                      | μA    |

| C <sub>IN</sub> | Input Capacitance <sup>[43]</sup>                             |                                                                            | _                       | _   | 7                       | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[43]</sup> | Single ended mode (GPIO mode)                                              | -                       | 40  | -                       | mV    |

|                 |                                                               | Differential mode                                                          | _                       | 35  | _                       | mV    |

| Idiode          | Current through protection diode to $V_{SSIO}$                |                                                                            | -                       | -   | 100                     | μA    |

42. See Figure 6-10 on page 39 and Figure 6-13 on page 43 for more information on SIO reference.

43. Based on device characterization (Not production tested).

### 11.4.4 XRES

### Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[46]</sup>                             |            | -                     | 3   | _                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[46]</sup> |            | -                     | 100 | -                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | _   | 100                   | μA    |

### Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

### 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.5.1 Opamp

### Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                                                                                                                  | Min                     | Тур  | Max                     | Units  |

|-------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|--------|

| VI                | Input voltage range                         |                                                                                                                                                                                             | V <sub>SSA</sub>        | -    | V <sub>DDA</sub>        | V      |

| V <sub>OS</sub>   | Input offset voltage                        |                                                                                                                                                                                             | -                       | -    | 2.5                     | mV     |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                                                                                                       | -                       | -    | 2                       | mV     |

| TCV <sub>OS</sub> | Input offset voltage drift with temperature | Power mode = high                                                                                                                                                                           | -                       | -    | ±30                     | µV/ °C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = 1 k $\Omega$                                                                                                                                                                        | -                       | -    | ±0.1                    | %      |

| C <sub>IN</sub>   | Input capacitance                           | Routing from pin                                                                                                                                                                            | -                       | -    | 18                      | pF     |

| V <sub>O</sub>    | Output voltage range                        | 1 mA, source or sink, power<br>mode = high                                                                                                                                                  | V <sub>SSA</sub> + 0.05 | -    | V <sub>DDA</sub> – 0.05 | V      |

| I <sub>OUT</sub>  | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ $V_{DDA}$ –500 mV, $V_{DDA}$ > 2.7 V                                                                                                                  | 25                      | -    | -                       | mA     |

|                   |                                             | $\label{eq:VSSA} \begin{array}{l} V_{SSA} \mbox{ + 500 mV} \leq \mbox{Vout} \leq \mbox{V}_{DDA} \\ -500 \mbox{ mV}, \mbox{ 1.7 V} \mbox{ = } \mbox{V}_{DDA} \leq \mbox{ 2.7 V} \end{array}$ | 16                      | _    | -                       | mA     |

| I <sub>DD</sub>   | Quiescent current                           | Power mode = min                                                                                                                                                                            | -                       | 250  | 400                     | uA     |

|                   |                                             | Power mode = low                                                                                                                                                                            | -                       | 250  | 400                     | uA     |

|                   |                                             | Power mode = med                                                                                                                                                                            | -                       | 330  | 950                     | uA     |

|                   |                                             | Power mode = high                                                                                                                                                                           | -                       | 1000 | 2500                    | uA     |

| CMRR              | Common mode rejection ratio                 |                                                                                                                                                                                             | 80                      | -    | -                       | dB     |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 V$                                                                                                                                                                         | 85                      | -    | -                       | dB     |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                                                                                                    | 70                      | -    | -                       | dB     |

| I <sub>IB</sub>   | Input bias current <sup>[46]</sup>          | 25 °C                                                                                                                                                                                       | _                       | 10   | _                       | pА     |

#### Note

46. Based on device characterization (Not production tested).

| Decelution Dite  | Cont | inuous | Multi- | Sample | Multi-Sar | nple Turbo |

|------------------|------|--------|--------|--------|-----------|------------|

| Resolution, Bits | Min  | Max    | Min    | Max    | Min       | Max        |

| 8                | 8000 | 384000 | 1911   | 91701  | 1829      | 87771      |

| 9                | 6400 | 307200 | 1543   | 74024  | 1489      | 71441      |

| 10               | 5566 | 267130 | 1348   | 64673  | 1307      | 62693      |

| 11               | 4741 | 227555 | 1154   | 55351  | 1123      | 53894      |

| 12               | 4000 | 192000 | 978    | 46900  | 956       | 45850      |

| 13               | 3283 | 157538 | 806    | 38641  | 791       | 37925      |

| 14               | 2783 | 133565 | 685    | 32855  | 674       | 32336      |

| 15               | 2371 | 113777 | 585    | 28054  | 577       | 27675      |

| 16               | 2000 | 48000  | 495    | 11861  | 489       | 11725      |

| 17               | 500  | 12000  | 124    | 2965   | 282       | 6766       |

| 18               | 125  | 3000   | 31     | 741    | 105       | 2513       |

| 19               | 16   | 375    | 4      | 93     | 15        | 357        |

| 20               | 8    | 187.5  | 2      | 46     | 8         | 183        |

### Table 11-23. Delta-sigma ADC Sample Rates, Range = ±1.024 V

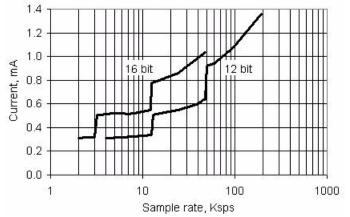

Figure 11-33. Delta-sigma ADC IDD vs sps, Range = ±1.024 V, Figure 11-34. Delta-sigma ADC Noise Histogram, 1000 Continuous Sample Mode, Input Buffer Bypassed

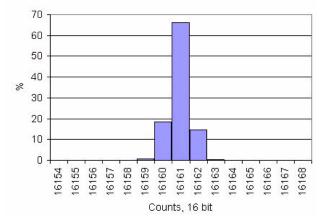

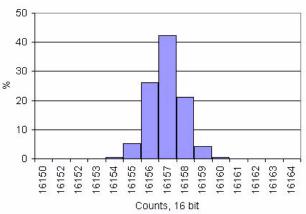

Figure 11-35. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

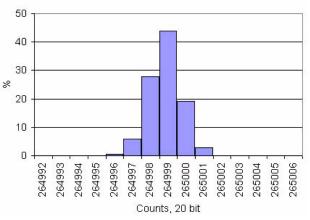

Samples, 20-Bit, 187 sps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Figure 11-36. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Code = 255

Code = 64

Current noise

is proportional

to scale \* code

100

10

kHz

1000

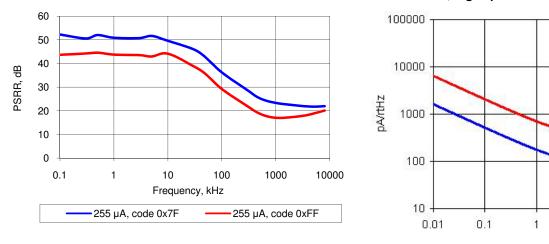

Figure 11-53. IDAC PSRR vs Frequency

Figure 11-54. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, High speed mode, V<sub>DDA</sub> = 5 V

## 11.5.7 Voltage Digital to Analog Converter (VDAC)

See the VDAC component datasheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

### Table 11-34. VDAC DC Specifications

| Parameter        | Description                               | Conditions                        | Min | Тур  | Max  | Units     |

|------------------|-------------------------------------------|-----------------------------------|-----|------|------|-----------|

|                  | Resolution                                |                                   | —   | 8    | _    | bits      |

| V <sub>OUT</sub> | Output voltage range, code = 255          | 1 V scale                         | —   | 1.02 | _    | V         |

|                  |                                           | 4 V scale, V <sub>DDA</sub> = 5 V | —   | 4.08 | _    | V         |

| INL1             | Integral nonlinearity                     | 1 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| INL4             | Integral nonlinearity <sup>[57]</sup>     | 4 V scale                         | _   | ±2.1 | ±2.5 | LSB       |

| DNL1             | Differential nonlinearity                 | 1 V scale                         | —   | ±0.3 | ±1   | LSB       |

| DNL4             | Differential nonlinearity <sup>[57]</sup> | 4 V scale                         | —   | ±0.3 | ±1   | LSB       |

| Rout             | Output resistance                         | 1 V scale                         | _   | 4    | _    | kΩ        |

|                  |                                           | 4 V scale                         | —   | 16   | _    | kΩ        |

|                  | Monotonicity                              |                                   | _   | -    | Yes  | -         |

| V <sub>OS</sub>  | Zero scale error                          |                                   | -   | 0    | ±0.9 | LSB       |

| Eg               | Gain error                                | 1 V scale,                        | _   | -    | ±2.5 | %         |

|                  |                                           | 4 V scale                         | _   | -    | ±2.5 | %         |

| TC_Eg            | Temperature coefficient, gain error       | 1 V scale,                        | -   | -    | 0.03 | %FSR / °C |

|                  |                                           | 4 V scale                         | _   | -    | 0.03 | %FSR / °C |

| I <sub>DD</sub>  | Operating current                         | Low speed mode                    | -   | -    | 100  | μA        |

|                  |                                           | High speed mode                   | -   | -    | 500  | μA        |

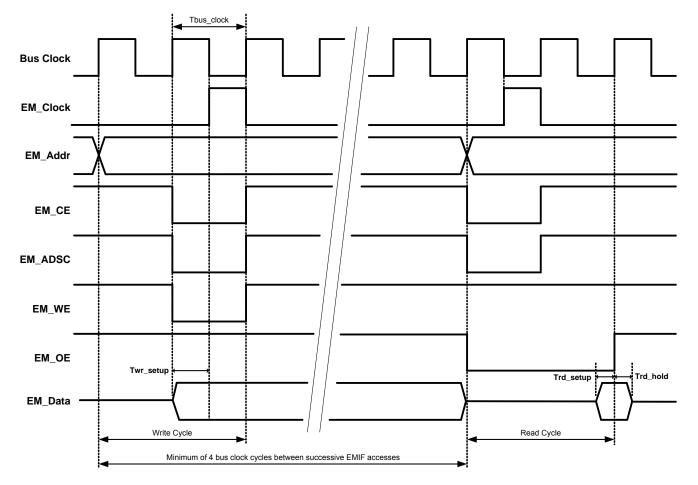

Figure 11-72. Synchronous Write and Read Cycle Timing, No Wait States

Table 11-68. Synchronous Write and Read Timing Specifications<sup>[65]</sup>

| Parameter  | Description                                                   | Conditions | Min             | Тур | Max | Units |

|------------|---------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[66]</sup>                           |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[67]</sup>                              |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock            |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE   |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after<br>rising edge of EM_OE |            | 5               | -   | -   | ns    |

Notes

- 65. Based on device characterization (Not production tested).

66. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 80.

67. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

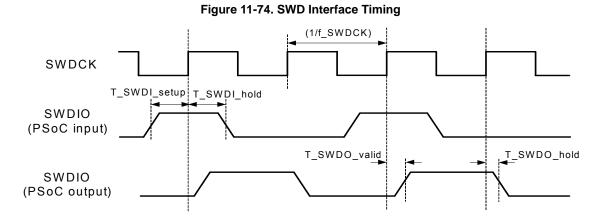

### 11.8.5 SWD Interface

### Table 11-75. SWD Interface AC Specifications<sup>[71]</sup>

| Parameter    | Description                         | Conditions                                                  | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \le V_{DDD} \le 5~V$                                 | _   | _   | 14 <sup>[72]</sup>  | MHz   |

|              |                                     | $1.71 \text{ V} \le \text{V}_{\text{DDD}} < 3.3 \text{ V}$  | -   | _   | 7 <sup>[72]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V <sub>DDD</sub> < 3.3 V, SWD over USBIO pins | -   | -   | 5.5 <sup>[72]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                           | T/4 | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                           | T/4 | -   | -                   |       |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                           | -   | _   | 2T/5                |       |

### 11.8.6 SWV Interface

### Table 11-76. SWV Interface AC Specifications<sup>[71]</sup>

| Parameter | Description           | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------|------------|-----|-----|-----|-------|

|           | SWV mode SWV bit rate |            | _   | -   | 33  | Mbit  |

71. Based on device characterization (Not production tested).

72. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C38 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C38 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

| Table 12-1. | CY8C38 Family | with Sin | ale Cycle 8051 |

|-------------|---------------|----------|----------------|

|             |               |          | gio oyoic cooi |

|                 |                 | MCU        | Cor       | e           |                   |                | An  | alog       |                                        |        |     |          |                      | Dig              | gital  |          |           | I/O  | [83] |       |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|------|-------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[81]</sup> | Opamps | DFB | CapSense | UDBs <sup>[82]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO  | USBIO | Package      | JTAG ID <sup>[84]</sup> |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3865AXI-019 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 5   | 5        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×1E013069              |

| CY8C3865LTI-014 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 2   | ۲        | 20                   | 4                | >      | Ι        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×1E00E069              |

| CY8C3865AXI-204 | 67              | 32         | 8         | 1           | 2                 | 20-bit Del-Sig | 2   | 0          | 0                                      | 0      | -   | 2        | 16                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0x1E0CC069              |

| CY8C3865LTI-205 | 67              | 32         | 8         | 1           | ~                 | 20-bit Del-Sig | 2   | 0          | 0                                      | 0      | I   | ~        | 16                   | 4                | ~      | I        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0x1E0CD069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |     |          |                      |                  |        |          |           |      |      |       |              |                         |

| CY8C3866LTI-067 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | 2        | 24                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-pin QFN   | 0×1E043069              |

| CY8C3866PVI-021 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ٢   | ~        | 24                   | 4                | ~      | I        | 31        | 25   | 4    | 2     | 48-pin SSOP  | 0×1E015069              |

| CY8C3866AXI-035 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | 2   | >        | 24                   | 4                | Ι      | >        | 70        | 62   | 8    | 0     | 100-pin TQFP | 0x1E023069              |

| CY8C3866AXI-039 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | >   | >        | 24                   | 4                | >      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×1E027069              |

| CY8C3866LTI-030 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | >   | >        | 24                   | 4                | >      | -        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0×1E01E069              |

| CY8C3866LTI-068 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 31        | 25   | 4    | 2     | 48-pin QFN   | 0×1E044069              |

| CY8C3866AXI-040 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | ۲        | 24                   | 4                | ~      | ~        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0×1E028069              |

| CY8C3866PVI-070 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~   | >        | 24                   | 4                | -      | ~        | 29        | 25   | 4    | 0     | 48-pin SSOP  | 0×1E046069              |

| CY8C3866AXI-206 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 2   | 2          | 0                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0x1E0CE069              |

| CY8C3866LTI-207 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 2   | 2          | 0                                      | 2      | ~   | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0x1E0CF069              |

| CY8C3866AXI-208 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 2   | 2          | 2                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 72        | 62   | 8    | 2     | 100-pin TQFP | 0x1E0D0069              |

| CY8C3866LTI-209 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 2   | 2          | 2                                      | 2      | ~   | >        | 24                   | 4                | ~      | ~        | 48        | 38   | 8    | 2     | 68-pin QFN   | 0x1E0D1069              |

| CY8C3866FNI-210 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~   | >        | 24                   | 4                | ~      | ~        | 48        | 38   | 8    | 2     | 72 WLCSP     | 0x1E0D2069              |

Notes

Analog blocks support a variety of functionality including TIA, PGA, and mixers. See the Example Peripherals on page 44 for more information on how analog blocks can be used.

Be used.

UDBs support a variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 44 for more information on how UDBs can be used.

The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 37 for details on the functionality of each of

these types of I/O.

<sup>84.</sup> The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

| Document | Number: 0 | 01-11729           | -                  | asheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | ECN       | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *P       | 3107314   | 12/10/2010         | MKEA               | Updated delta-sigma tables and graphs.<br>Formatted table 11.2.<br>Updated interrupt controller table<br>Updated transimpedance amplifier section<br>Updated SIO DC specs table<br>Updated Voltage Monitors DC Specifications table<br>Updated LCD Direct Drive DC specs table<br>Replaced the Discrete Time Mixer and Continuous Time Mixer tables with Mixer<br>DC and AC specs tables<br>Updated ESD <sub>HBM</sub> value.<br>Updated IDAC and VDAC sections<br>Removed ESO parts from ordering information<br>Changed USBIO pins from NC to DNU and removed redundant USBIO pin<br>description notes<br>Updated POR with brown out DC and AC specs<br>Updated POR with brown out DC and AC specs<br>Updated 32 kHz External Crystal DC Specifications<br>Updated opamp AC specs<br>Updated Inductive boost regulator section<br>Delta sigma ADC spec updates<br>Updated comparator section<br>Removed buzz mode from Power Mode Transition diagram<br>Updated opamp DC and AC spec tables<br>Updated PGA DC table                           |

| *Q       | 3179219   | 22/02/2011         | MKEA               | Updated conditions for flash data retention time<br>Updated 100-pin TQFP package spec.<br>Updated EEPROM AC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *R       | 3200146   | 03/28/2011         | MKEA               | Removed Preliminary status from the data sheet.<br>Updated JTAG ID<br>Deleted Cin_G1, ADC input capacitance from Delta-Sigma ADC DC spec table<br>Updated JTAG Interface AC Specifications and SWD Interface Specifications<br>tables<br>Updated USBIO DC specs<br>Added 0.01 to max speed<br>Updated Features on page 1<br>Added Section 5.5, Nonvolatile Latches<br>Updated Flash AC specs<br>Added CAN DC specs<br>Updated delta-sigma graphs, noise histogram figures and RMS Noise spec<br>tables<br>Add reference to application note AN58304 in section 8.1<br>Updated 100-pin TQFP package spec<br>Added oscillator, I/O, VDAC, regulator graphs<br>Updated GPIO and SIO AC specs<br>Updated GPIO and SIO AC specs<br>Updated POR with Brown Out AC spec table<br>Updated IDAC graphs<br>Added DMA timing diagram, interrupt timing and interrupt vector, I2C timing<br>diagrams<br>Updated opamp graphs and PGA graphs<br>Added full chip performance graphs<br>Changed MHzECO range.<br>Added "Solder Reflow Peak Temperature" table. |

# 18. Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

# **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2006-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other sont, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parents you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.