Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB            |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866lti-209 |

# 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | Α             | Clear accumulator                     | 1     | 1      |

| CPL | Α             | Complement accumulator                | 1     | 1      |

| RL  | Α             | Rotate accumulator left               | 1     | 1      |

| RLC | Α             | Rotate accumulator left through carry | 1     | 1      |

| RR  | Α             | Rotate accumulator right              | 1     | 1      |

| RRC | A             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

Document Number: 001-11729 Rev. AF Page 15 of 140

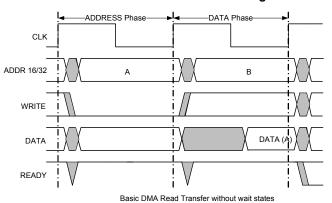

Figure 4-1. DMA Timing Diagram

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data

phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase 'subchains' can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty-two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

Figure 4-2 on page 20 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 21 shows the interrupt structure and priority polling.

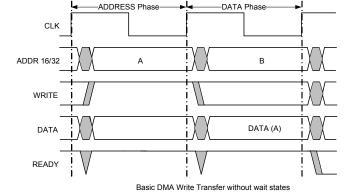

### 5.7 Memory Map

The CY8C38 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C38 8051 code space is 64 KB. Only main flash exists in this space. See the Flash Program Memory on page 23.

#### 5.7.2 Internal Data Space

The CY8C38 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 23) and a 128-byte space for special function registers (SFR). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 13.

5.7.3 SFRs

The SFR space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

Table 5-4. SFR Map

|         | Of it map  |            |             |      |      |      |     |     |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | _    | _    | _    | _   | _   |

| 0×F0    | В          | _          | SFRPRT12SEL | _    | _    | _    | _   | _   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | _    | -    | _    | _   | _   |

| 0×E0    | ACC        | _          | _           | _    | _    | _    | _   | _   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | _    | _    | _    | _   | _   |

| 0×D0    | PSW        | _          | _           | _    | _    | _    | _   | _   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | _    | _    | _    | _   | _   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | _    | _    | _    | _   | _   |

| 0×B8    |            |            |             | _    | -    | _    | _   | _   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | _    | -    | _    | _   | _   |

| 0×A8    | IE         | _          | _           | _    | -    | _    | _   | _   |

| 0×A0    | P2AX       | _          | SFRPRT1SEL  | _    | -    | _    | _   | _   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | _    | _    | _    | _   | _   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | _           | DPX0 | _    | DPX1 | _   | _   |

| 0×88    | _          | SFRPRT0PS  | SFRPRT0SEL  | _    | -    | _    | _   | _   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | _   |

The CY8C38 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C38 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C38 family.

Document Number: 001-11729 Rev. AF Page 26 of 140

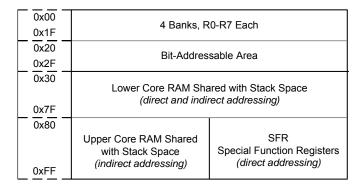

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-6. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-6 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register When HW connection is disabled).

The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected. The 'An' connection connects to the Analog System.

#### Table 6-6. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedance analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High Impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[14]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[14]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[14]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

#### Note

<sup>14.</sup> Resistive pull-up and pull-down are not available with SIO in regulated output mode.

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

|   | PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|---|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

|   | 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

|   | 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| Ī | 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

|   | 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

#### ■ High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

#### ■ High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (High Z) state recommended for digital inputs.

#### ■ Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pullup and pull-down are not available with SIO in regulated output mode.

#### ■ Open drain, drives high and open drain, drives low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the I<sup>2</sup>C bus signal lines.

#### ■ Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

#### ■ Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pullup and pull-down are not available with SIO in regulated output mode.

#### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

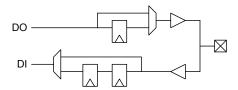

### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

Document Number: 001-11729 Rev. AF Page 41 of 140

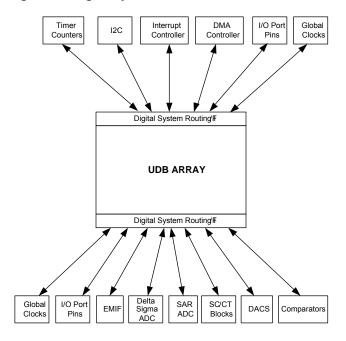

Figure 7-9. Digital System Interconnect

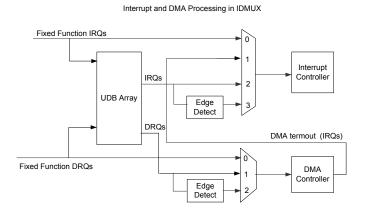

Interrupt and DMA routing is very flexible in the CY8C38 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

Figure 7-10. Interrupt and DMA Processing in the IDMUX

# 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be

single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

Figure 7-11. I/O Pin Synchronization Routing

Figure 7-12. I/O Pin Output Connectivity

8 IO Data Output Connections from the

UDB Array Digital System Interface

DO PIN 0 PIN 1 PIN 2 PIN 3 PIN 4 PIN 5 PIN 6 PIN 7 PIN 7

Port i

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

Figure 7-13. I/O Pin Output Enable Connectivity

4 IO Control Signal Connections from UDB Array Digital System Interface OE OE OE OE OE OE OE OE PIN 0 PIN1 PIN2 PIN3 PIN4 PIN5 PIN6 PIN7 Port i

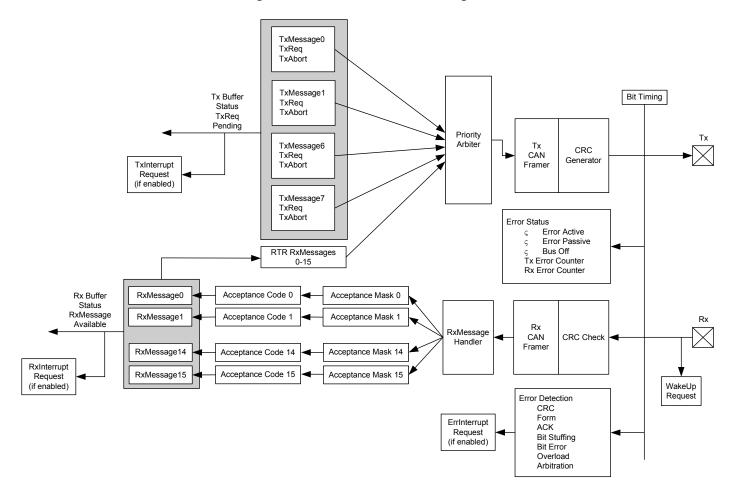

Figure 7-15. CAN Controller Block Diagram

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

#### 8.2.2.4 Multi Sample (Turbo)

The multi sample (turbo) mode operates identical to the Multi-sample mode for resolutions of 8 to 16 bits. For resolutions of 17 to 20 bits, the performance is about four times faster than the multi sample mode, because the ADC is only reset once at the end of conversion.

More information on output formats is provided in the Technical Reference Manual.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

#### 8.3 Comparators

The CY8C38 family of devices contains four comparators in a device. Comparators have these features:

- Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (VSSA to VDDA)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO, DAC outputs and SC block outputs

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB DSI.

**ANAIF** From Analog comp0 From Routing comp1 Analog Routing From Analog comp3 Routing From comp2 Analog Routing

Figure 8-5. Analog Comparator

Document Number: 001-11729 Rev. AF Page 60 of 140

UDBs

# 9.8 CSP Package Bootloader

A factory-installed bootloader program is included in all devices with CSP packages. The bootloader is compatible with PSoC Creator 3.0 bootloadable project files and has the following features:

- I<sup>2</sup>C-based

- SCLK and SDAT available at P1[6] and P1[7], respectively

- External pull-up resistors required

- I<sup>2</sup>C slave, address 4, data rate = 100 kbps

- Single application

- Wait two seconds for bootload command

- Other bootloader options are as set by the PSoC Creator 3.0 Bootloader Component default

- Occupies the bottom 9K of flash

For more information on this bootloader, see the following Cypress application notes:

- AN89611 PSoC® 3 AND PSoC 5LP Getting Started With Chip Scale Packages (CSP)

- AN73854 PSoC 3 and PSoC 5 LP Introduction to Bootloaders

- AN60317 PSoC 3 and PSoC 5 LP I<sup>2</sup>C Bootloader

Note that a PSOC Creator bootloadable project must be associated with .hex and .elf files for a bootloader project that is configured for the target device. Bootloader .hex and .elf files can be found at www.cypress.com/go/PSoC3datasheet.

The factory-installed bootloader can be overwritten using JTAG or SWD programming.

Document Number: 001-11729 Rev. AF Page 69 of 140

# 10. Development Support

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

#### 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component data sheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes**: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

#### 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

#### 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at <a href="https://www.cypress.com/go/psoccreator">www.cypress.com/go/psoccreator</a> for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

Document Number: 001-11729 Rev. AF Page 70 of 140

Table 11-3. AC Specifications [33]

| Parameter              | Description                                                                                                                    | Conditions                                                                                                                                   | Min | Тур | Max   | Units |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| F <sub>CPU</sub>       | CPU frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                                                                            | DC  | _   | 67.01 | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                                  | 1.71 V ≤ V <sub>DDD</sub> ≤ 5.5 V                                                                                                            | DC  | _   | 67.01 | MHz   |

| Svdd                   | V <sub>DD</sub> ramp rate                                                                                                      |                                                                                                                                              | _   | _   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ IPOR to I/O ports set to their reset states |                                                                                                                                              | -   | _   | 10    | μs    |

| T <sub>STARTUP</sub>   | Time from V <sub>DDD</sub> /V <sub>DDA</sub> /V <sub>CCD</sub> /V <sub>CCA</sub> ≥ PRES to CPU executing code at reset vector  | V <sub>CCA</sub> /V <sub>DDA</sub> = regulated from<br>V <sub>DDA</sub> /V <sub>DDD</sub> , no PLL used, fast IMO<br>boot mode (48 MHz typ.) | -   | _   | 40    | μs    |

|                        |                                                                                                                                | $V_{CCA}/V_{CCD}$ = regulated from $V_{DDA}/V_{DDD}$ , no PLL used, slow IMO boot mode (12 MHz typ.)                                         | -   | _   | 74    | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep mode –<br>Application of non-LVD interrupt to<br>beginning of execution of next CPU<br>instruction           |                                                                                                                                              | -   | _   | 15    | μs    |

| T <sub>HIBERNATE</sub> | Wakeup from hibernate mode –<br>Application of external interrupt to<br>beginning of execution of next CPU<br>instruction      |                                                                                                                                              | -   | _   | 100   | μs    |

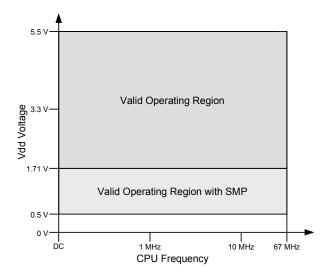

Figure 11-4. F<sub>CPU</sub> vs. V<sub>DD</sub>

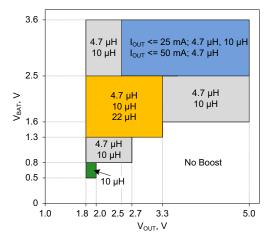

Table 11-7. Recommended External Components for Boost Circuit

| Parameter          | Description                                                              | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                           | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                          | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                          | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μΗ    |

| C <sub>BOOST</sub> | Total capacitance sum of $V_{\rm DDD}, V_{\rm DDA}, V_{\rm DDIO}^{[37]}$ |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                 |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average forward current                                   |                | 1.0  | -    | 1    | А     |

| V <sub>R</sub>     | Schottky reverse voltage                                                 |                | 20.0 | _    | _    | V     |

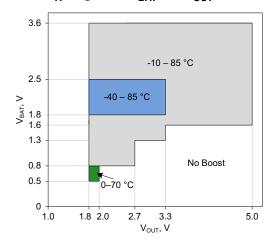

Figure 11-8.  $T_A$  range over  $V_{BAT}$  and  $V_{OUT}$

Figure 11-10.  $L_{\mbox{\footnotesize{BOOST}}}$  values over  $V_{\mbox{\footnotesize{BAT}}}$  and  $V_{\mbox{\footnotesize{OUT}}}$

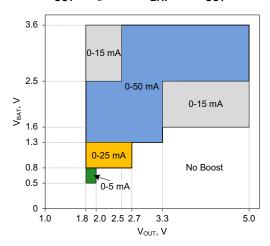

Figure 11-9.  $I_{OUT}$  range over  $V_{BAT}$  and  $V_{OUT}$

#### Note

37. Based on device characterization (Not production tested).

# 11.4 Inputs and Outputs

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

11.4.1 GPIO

Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                   | Conditions                                               | Min                     | Тур | Max                     | Units |

|-----------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| $V_{IH}$        | Input voltage high threshold                                  | CMOS Input, PRT[×]CTL = 0                                | $0.7 \times V_{DDIO}$   | _   | _                       | V     |

| $V_{IL}$        | Input voltage low threshold                                   | CMOS Input, PRT[x]CTL = 0                                | -                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[*]CTL = 1,<br>V <sub>DDIO</sub> < 2.7 V | 0.7 × V <sub>DDIO</sub> | -   | _                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                  | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7V$ | 2.0                     | -   | -                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[×]CTL = 1,<br>V <sub>DDIO</sub> < 2.7 V | _                       | ı   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7V$ | -                       | Ī   | 0.8                     | V     |

| $V_{OH}$        | Output voltage high                                           | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>          | V <sub>DDIO</sub> - 0.6 | -   | _                       | V     |

|                 |                                                               | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>          | V <sub>DDIO</sub> - 0.5 | ı   | _                       | V     |

| V <sub>OL</sub> | Output voltage low                                            | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>          | _                       | _   | 0.6                     | V     |

|                 |                                                               | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>          | -                       | -   | 0.6                     | V     |

|                 |                                                               | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>          | _                       | _   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                              |                                                          | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                            |                                                          | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value)[39]                    | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | -   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[39]</sup>                             | GPIOs not shared with opamp outputs, MHz ECO or kHzECO   | _                       | 4   | 7                       | pF    |

|                 |                                                               | GPIOs shared with MHz ECO or kHzECO <sup>[40]</sup>      | _                       | 5   | 7                       | pF    |

|                 |                                                               | GPIOs shared with opamp outputs                          | _                       | -   | 18                      | pF    |

| $V_{H}$         | Input voltage hysteresis (Schmitt-Trigger)[39]                |                                                          | -                       | 40  | _                       | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |                                                          | _                       | -   | 100                     | μΑ    |

| Rglobal         | Resistance pin to analog global bus                           | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | -                       | 320 | _                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                              | 25 °C, V <sub>DDIO</sub> = 3.0 V                         | _                       | 220 | _                       | Ω     |

#### Notes

<sup>39.</sup> Based on device characterization (Not production tested).

<sup>40.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

Table 11-13. SIO Comparator Specifications<sup>[45]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | -   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | -   |       |

| Tresp     | Response time                  |                           | _   | -   | 30  | ns    |

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 72.

Table 11-14. USBIO DC Specifications

| Parameter                       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb                          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | -   | 3.6            | V     |

| Volusb                          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | _              | _   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode          | $V_{DDD} \ge 3 \text{ V}$                          | 2              | _   | _              | V     |

| Vilgpio                         | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 \text{ V}$                          | -              | _   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode         | I <sub>OH</sub> = 4 mA, V <sub>DDD</sub> ≥ 3 V     | 2.4            | _   | _              | V     |

| Volgpio                         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | -              | -   | 0.3            | V     |

| Vdi                             | Differential input sensitivity         | (D+) - (D-)                                        | -              | -   | 0.2            | V     |

| Vcm                             | Differential input common mode range   | _                                                  | 0.8            | _   | 2.5            | V     |

| Vse                             | Single ended receiver threshold        | _                                                  | 0.8            | _   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext                            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance      | _                                                  | _              | _   | 20             | pF    |

| I <sub>IL</sub> <sup>[45]</sup> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | _              | _   | 2              | nA    |

#### Note

Document Number: 001-11729 Rev. AF

<sup>45.</sup> Based on device characterization (Not production tested).

# 11.5.2 Delta-sigma ADC

Unless otherwise specified, operating conditions are:

- Operation in continuous sample mode

- fclk = 3.072 MHz for resolution = 16 to 20 bits; fclk = 6.144 MHz for resolution = 8 to 15 bits

- Reference = 1.024 V internal reference bypassed on P3.2 or P0.3

- Unless otherwise specified, all charts and graphs show typical values

Table 11-21. 20-bit Delta-sigma ADC DC Specifications

| Parameter  | Description                                                  | Conditions                                                      | Min       | Тур                    | Max                  | Units      |

|------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------|------------------------|----------------------|------------|

|            | Resolution                                                   |                                                                 | 8         | _                      | 20                   | bits       |

|            | Number of channels, single ended                             |                                                                 | -         | -                      | No. of<br>GPIO       | -          |

|            | Number of channels, differential                             | Differential pair is formed using a pair of GPIOs.              | -         | -                      | No. of<br>GPIO/2     | -          |

|            | Monotonic                                                    | Yes                                                             | _         | -                      | _                    | _          |

| Ge         | Gain error                                                   | Buffered, buffer gain = 1, Range = ±1.024 V, 16-bit mode, 25 °C | -         | -                      | ±0.2                 | %          |

| Gd         | Gain drift                                                   | Buffered, buffer gain = 1, Range = ±1.024 V, 16-bit mode        | _         | -                      | 50                   | ppm/°<br>C |

| Vos        | Input offset voltage                                         | Buffered, 16-bit mode, full voltage range                       | -         | -                      | ±0.2                 | mV         |

| VOS        | input onset voltage                                          | Buffered, 16-bit mode,<br>V <sub>DDA</sub> = 1.8 V ±5%, 25 °C   | -         | -                      | ±0.1                 | mV         |

| TCVos      | Temperature coefficient, input offset voltage                | Buffer gain = 1, 16-bit,<br>Range = ±1.024 V                    | -         | -                      | 1                    | μV/°C      |

|            | Input voltage range, single ended <sup>[47]</sup>            |                                                                 | $V_{SSA}$ | _                      | $V_{DDA}$            | V          |

|            | Input voltage range, differential unbuffered <sup>[47]</sup> |                                                                 | $V_{SSA}$ | -                      | $V_{DDA}$            | ٧          |

|            | Input voltage range, differential, buffered <sup>[47]</sup>  |                                                                 | $V_{SSA}$ | -                      | V <sub>DDA</sub> – 1 | V          |

| PSRRb      | Power supply rejection ratio, buffered <sup>[47]</sup>       | Buffer gain = 1, 16-bit,<br>Range = ±1.024 V                    | 90        | -                      | _                    | dB         |

| CMRRb      | Common mode rejection ratio, buffered <sup>[47]</sup>        | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V                    | 85        | -                      | _                    | dB         |

| INL20      | Integral non linearity <sup>[47]</sup>                       | Range = ±1.024 V, unbuffered                                    | _         | -                      | ±32                  | LSB        |

| DNL20      | Differential non linearity <sup>[47]</sup>                   | Range = ±1.024 V, unbuffered                                    | _         | _                      | ±1                   | LSB        |

| INL16      | Integral non linearity <sup>[47]</sup>                       | Range = ±1.024 V, unbuffered                                    | -         | _                      | ±2                   | LSB        |

| DNL16      | Differential non linearity <sup>[47]</sup>                   | Range = ±1.024 V, unbuffered                                    | _         | _                      | ±1                   | LSB        |

| INL12      | Integral non linearity <sup>[47]</sup>                       | Range = ±1.024 V, unbuffered                                    | -         | -                      | ±1                   | LSB        |

| DNL12      | Differential non linearity <sup>[47]</sup>                   | Range = ±1.024 V, unbuffered                                    | ı         | _                      | ±1                   | LSB        |

| INL8       | Integral non linearity <sup>[47]</sup>                       | Range = ±1.024 V, unbuffered                                    | ı         | _                      | ±1                   | LSB        |

| DNL8       | Differential non linearity <sup>[47]</sup>                   | Range = ±1.024 V, unbuffered                                    | ı         | _                      | ±1                   | LSB        |

| Rin_Buff   | ADC input resistance                                         | Input buffer used                                               | 10        | _                      | _                    | MΩ         |

| Rin_ADC16  | ADC input resistance                                         | Input buffer bypassed, 16-bit, Range = ±1.024 V                 | ı         | 74 <sup>[48]</sup>     | _                    | kΩ         |

| Rin_ADC12  | ADC input resistance                                         | Input buffer bypassed, 12 bit, Range = ±1.024 V                 | _         | 148 <sup>[48]</sup>    | _                    | kΩ         |

| Rin_ExtRef | ADC external reference input resistance                      |                                                                 | _         | 70 <sup>[48, 49]</sup> | _                    | kΩ         |

#### Notes

Document Number: 001-11729 Rev. AF Page 91 of 140

<sup>47.</sup> Based on device characterization (not production tested).

<sup>48.</sup> By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

<sup>49.</sup> Recommend an external reference device with an output impedance <100 Ω, for example, the LM185/285/385 family. A 1-μF capacitor is recommended. For more information, see AN61290 - PSoC® 3 and PSoC 5LP Hardware Design Considerations.

| Table 11-23. Delta-sigma ADC Sample Rates, Range = $\pm 1.02$ |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Resolution, Bits | Continuous |        | Multi-Sample |       | Multi-Sample Turbo |       |

|------------------|------------|--------|--------------|-------|--------------------|-------|

|                  | Min        | Max    | Min          | Max   | Min                | Max   |

| 8                | 8000       | 384000 | 1911         | 91701 | 1829               | 87771 |

| 9                | 6400       | 307200 | 1543         | 74024 | 1489               | 71441 |

| 10               | 5566       | 267130 | 1348         | 64673 | 1307               | 62693 |

| 11               | 4741       | 227555 | 1154         | 55351 | 1123               | 53894 |

| 12               | 4000       | 192000 | 978          | 46900 | 956                | 45850 |

| 13               | 3283       | 157538 | 806          | 38641 | 791                | 37925 |

| 14               | 2783       | 133565 | 685          | 32855 | 674                | 32336 |

| 15               | 2371       | 113777 | 585          | 28054 | 577                | 27675 |

| 16               | 2000       | 48000  | 495          | 11861 | 489                | 11725 |

| 17               | 500        | 12000  | 124          | 2965  | 282                | 6766  |

| 18               | 125        | 3000   | 31           | 741   | 105                | 2513  |

| 19               | 16         | 375    | 4            | 93    | 15                 | 357   |

| 20               | 8          | 187.5  | 2            | 46    | 8                  | 183   |

Continuous Sample Mode, Input Buffer Bypassed

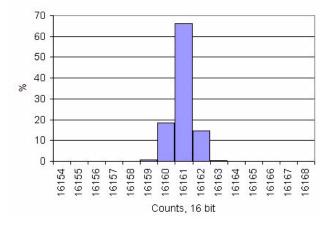

Figure 11-35. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

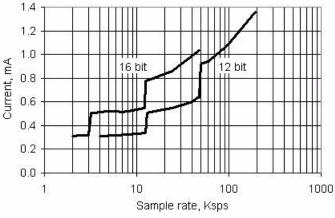

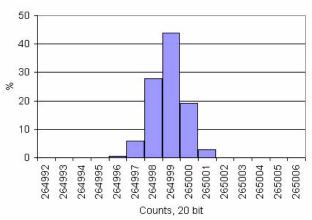

Figure 11-33. Delta-sigma ADC IDD vs sps, Range = ±1.024 V, Figure 11-34. Delta-sigma ADC Noise Histogram, 1000 Samples, 20-Bit, 187 sps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

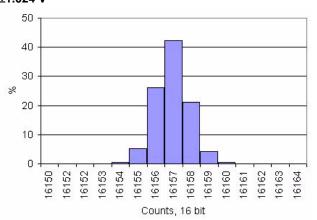

Figure 11-36. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

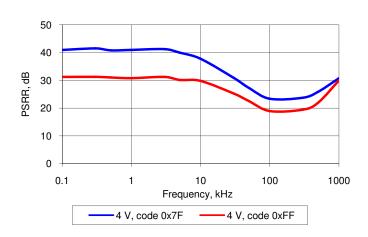

Figure 11-65. VDAC PSRR vs Frequency

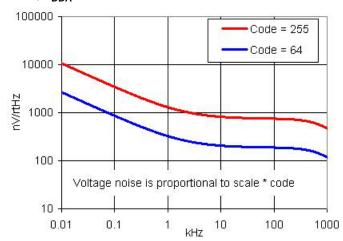

Figure 11-66. VDAC Voltage Noise, 1 V Mode, High speed mode,  $V_{DDA}$  = 5 V

11.5.8 Mixer

The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs.

Table 11-36. Mixer DC Specifications

| Parameter       | Description          | Conditions | Min | Тур | Max | Units |

|-----------------|----------------------|------------|-----|-----|-----|-------|

| V <sub>OS</sub> | Input offset voltage |            | _   | _   | 15  | mV    |

|                 | Quiescent current    |            | _   | 0.9 | 2   | mA    |

| G               | Gain                 |            | _   | 0   | _   | dB    |

Table 11-37. Mixer AC Specifications

| Parameter       | Description                | Conditions      | Min | Тур | Max | Units |

|-----------------|----------------------------|-----------------|-----|-----|-----|-------|

| $f_{LO}$        | Local oscillator frequency | Down mixer mode | _   | _   | 4   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Down mixer mode | _   | _   | 14  | MHz   |

| $f_{LO}$        | Local oscillator frequency | Up mixer mode   | _   | _   | 1   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Up mixer mode   | _   | _   | 1   | MHz   |

| SR              | Slew rate                  |                 | 3   | _   | _   | V/µs  |

Document Number: 001-11729 Rev. AF Page 104 of 140

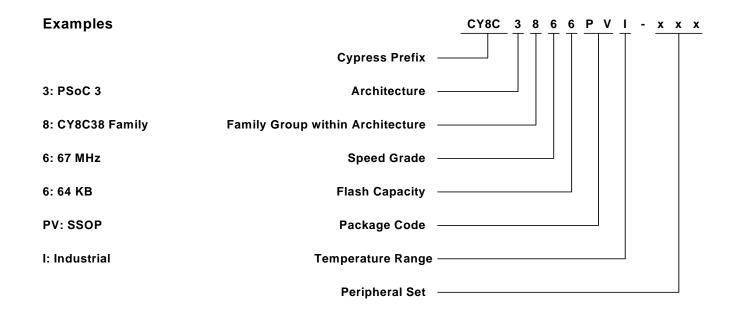

# 12.1 Part Numbering Conventions

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

#### CY8Cabcdefg-xxx

- a: Architecture

- 3: PSoC 3

- □ 5: PSoC 5

- b: Family group within architecture

- 4: CY8C34 family

- □ 6: CY8C36 family

- 8: CY8C38 family

- c: Speed grade

- □ 4: 48 MHz

- □ 6: 67 MHz

- d: Flash capacity

- □ 4: 16 KB

- □ 5: 32 KB

- □ 6: 64 KB

- ef: Package code

- Two character alphanumeric

- AX: TQFP

- LT: QFN

- □ PV: SSOP

- □ FN: CSP

- g: Temperature range

- □ C: commercial

- □ I: industrial

- A: automotive

- xxx: Peripheral set

- □ Three character numeric

- □ No meaning is associated with these three characters.

Tape and reel versions of these devices are available and are marked with a "T" at the end of the part number.

All devices in the PSoC 3 CY8C38 family comply to RoHS-6 specifications, demonstrating the commitment by Cypress to lead-free products. Lead (Pb) is an alloying element in solders that has resulted in environmental concerns due to potential toxicity. Cypress uses nickel-palladium-gold (NiPdAu) technology for the majority of leadframe-based packages.

A high-level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration data sheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end of life" requirements.

Document Number: 001-11729 Rev. AF Page 124 of 140

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *U       | 3645908 | 06/14/2012         | MKEA               | Section 2: Changed text and added figures describing Vddio source and sink Corrected example PCB layout figure.  Sections 3, 6.2: Added text about usage in externally regulated mode.  Section 5.2 and elsewhere: Added text describing flash cache, and updated related text.  Section 6.1, 11.91: Changed IMO startup time specification.  Section 6.2.1.4: Added paragraph clarifying limiting the frequency of IO inpu signals to achieve low hibernate current.  Section 6.3.1.4: Added paragraph clarifying limiting the frequency of IO inpu signals to achieve low hibernate current.  Sections 6.3.1.1, 13.1: Revised description of IPOR and clarified PRES term Added text on adjustability of buzz frequency.  Sections 6.3.1.1, 11.8.1: Revised description of IPOR and clarified PRES term Added text on adjustability of buzz frequency.  Section 6.4.14, 11.4: Deleted and updated text regarding SIO performance under certain power ramp conditions.  Section 6.4.15: Changed text describing SIO modes for overvoltage tolerance Section 7.8: Changed "compliant with I2C" to "compatible with I2C".  Section 7.9: Updated DFB description text.  Sections 8.9, 11.5.6, 11.5.7: Changed DAC high and low speed/power mode descriptions and conditions.  Section 9.1: Added a statement about support for JTAG programmers and fil formats.  Section 9.3: Deleted the text "debug operations are possible while the device is reset".  Section 11.1: Added specification for ESDHBM for when Vssa and Vssd are separate. Changed footnote to state that all GPIO input voltages must be lest than Vddio. Changed supply ramp rate specification.  Section 11.2.1: Added chip Idd specs for active and low-power modes, for multiple voltage, temperature and usage conditions.  Section 11.3.3: Removed from boost mention of 22 µH inductors, and relate graphs.  Section 11.5.1: Changed load capacitor conditions in opamp specifications. Clarified description of opamp lout specification.  Section 11.5.4: Changed analog global specification descriptions and values Section 11.5.5: Changed compa |

| *V       | 3648803 | 06/18/2012         | WKA/MKEA           | Throughout document: updated terminology for "master" and "system" clock Updated the description of changes for previous (*U) revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *W       | 3732521 | 09/03/2012         | MKEA               | Replaced I <sub>DDDR</sub> and I <sub>DDAR</sub> specs in Table 11-2, "DC Specifications," on page 72 that were dropped out in *U revision.  Updated V <sub>OS</sub> Max value from 10 to 15 in Table 11-36, "Mixer DC Specifications," on page 104.  Updated Table 11-21, "20-bit Delta-sigma ADC DC Specifications," on page 91 I <sub>DD_20</sub> Max value from 1.25 to 1.5 mA I <sub>DD_16</sub> Max value from 1.2 to 1.5 mA I <sub>DD_16</sub> Max value from 1.4 to 1.95 mA Replaced PSoC® 3 Programming AN62391 with TRM in footnote #61 and "Programming, Debug Interfaces, Resources" section on page 65.  Removed Figure 11-8 (Efficiency vs Vout) Updated Table 11-19, "Opamp DC Specifications," on page 88, I <sub>DD</sub> Quiescent current row values from 200 and 270 to 250 and 400 respectively. Updated conditions for Storage Temperature in Table 11-1, "Absolute Maximum Ratings DC Specifications[18]," on page 71 Updated conditions and min values for NVL data retention time in Table 11-64, "NVL AC Specifications," on page 113 Updated Table 11-79, "ILO DC Specifications," on page 121. Removed the following pruned parts from the "Ordering Information" section on page 123. CY8C3865PVI-060 CY8C3865PVI-060 CY8C3866AXI-035 Updated PSoC 3 boost circuit value throughout the document. Removed 100 kHz sub row in Table 11-55, "DFB DC Specifications," on page 110. Updated package diagram 51-85061 to *F revision. |

| *X       | 3922905 | 03/25/2013         | MKEA               | Updated I <sub>DD_XX</sub> parameters under Table 11-21, "20-bit Delta-sigma ADC DC Specifications," on page 91.  Updated Temperature Drift spec in Voltage Reference Specifications.  Added CY8C3865AXI-204, CY8C3865LTI-205, CY8C3866AXI-206, CY8C3866LTI-207, CY8C3866AXI-208, and CY8C3866LTI-209 part numbers in Ordering Information.  Updated I <sup>2</sup> C section and GPIO and SIO DC specification tables.  Corrected Hibernate max limit.  Changed INL max value from ±1.5 to ±1.6 in IDAC DC Specifications.  Updated ECCEN default setting in Fields and Factory Default Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *Y       | 4064707 | 07/18/2013         | MKEA               | Added USB test ID in Features. Updated schematic in Section 2 Added paragraph for device reset warning in Section 5.4. Added NVL bit for DEBUG_EN in Section 5.5. Updated UDB PLD array diagram in Section 7.2.1. Changed Tstartup specs in Section 11.2.1. Changed GPIO rise and fall time specs in Section 11.4. Added Opamp IIB spec in Section 11.5.1. Changed Del-sig Vos spec in Section 11.5.2. Added VREF spec condition: pre-assembly and added "box method" to VREF temperature drift spec conditions in Section 11.5.3. Added IMO spec condition: pre-assembly in Section 11.9.1. Added Appendix for CSP package (preliminary).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *Z       | 4118845 | 09/10/2013         | MKEA               | Removed T <sub>STG</sub> spec. and added note clarifying the maximum storage temper ature range in Table 11-1.  Updated Vos spec conditions and TCVos in Table 11-21.  Updated F <sub>IMO</sub> spec (3 MHz).  Updated 100-TQFP package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |