#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 48MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 83                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                                |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg380f512g-e-qfp100r |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **3 Electrical Characteristics**

### **3.1 Test Conditions**

### **3.1.1 Typical Values**

The typical data are based on  $T_{AMB}$ =25°C and  $V_{DD}$ =3.0 V, as defined in Table 3.2 (p. 10), unless otherwise specified.

### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 10), unless otherwise specified.

### **3.2 Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 10) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 10).

#### Table 3.1. Absolute Maximum Ratings

| Symbol             | Parameter                         | Condition                              | Min  | Тур | Max                  | Unit |

|--------------------|-----------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range    |                                        | -40  |     | 150                  | °C   |

| Τ <sub>S</sub>     | Maximum soldering temperature     | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main sup-<br>ply voltage |                                        | 0    |     | 3.8                  | V    |

| V <sub>IOPIN</sub> | Voltage on any I/O pin            |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

| 1                  | Current per I/O pin<br>(sink)     |                                        |      |     | 100                  | mA   |

| I <sub>IOMAX</sub> | Current per I/O pin<br>(source)   |                                        |      |     | -100                 | mA   |

### **3.3 General Operating Conditions**

### 3.3.1 General Operating Conditions

#### Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 48  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 48  | MHz  |

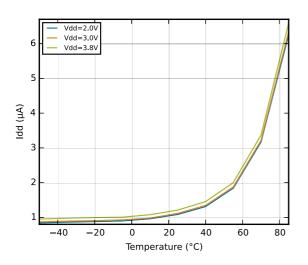

### 3.4.1 EM2 Current Consumption

Figure 3.1. EM2 current consumption. RTC<sup>1</sup> prescaled to 1 Hz, 32.768 kHz LFRCO.

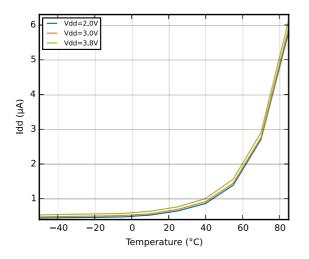

### 3.4.2 EM3 Current Consumption

Figure 3.2. EM3 current consumption.

<sup>&</sup>lt;sup>1</sup>Using backup RTC.

#### Table 3.5. Power Management

| Symbol                   | Parameter                                                                   | Condition                                                               | Min  | Тур  | Max  | Unit |

|--------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| M                        | BOD threshold on                                                            | EMO                                                                     | 1.74 |      | 1.96 | V    |

| V <sub>BODextthr</sub> - | falling external sup-<br>ply voltage                                        | EM2                                                                     | 1.74 |      | 1.98 | V    |

| V <sub>BODintthr</sub> - | BOD threshold on<br>falling internally reg-<br>ulated supply volt-<br>age   |                                                                         | 1.57 |      | 1.70 | V    |

| V <sub>BODextthr+</sub>  | BOD threshold on<br>rising external sup-<br>ply voltage                     |                                                                         |      | 1.85 | 1.98 | V    |

| V <sub>PORthr+</sub>     | Power-on Reset<br>(POR) threshold on<br>rising external sup-<br>ply voltage |                                                                         |      |      | 1.98 | V    |

| t <sub>reset</sub>       | Delay from reset<br>is released until<br>program execution<br>starts        | Applies to Power-on Reset,<br>Brown-out Reset and pin reset.            |      | 163  |      | μs   |

| C <sub>DECOUPLE</sub>    | Voltage regulator<br>decoupling capaci-<br>tor.                             | X5R capacitor recommended.<br>Apply between DECOUPLE pin<br>and GROUND  |      | 1    |      | μF   |

| C <sub>USB_VREGO</sub>   | USB voltage regu-<br>lator out decoupling<br>capacitor.                     | X5R capacitor recommended.<br>Apply between USB_VREGO<br>pin and GROUND |      | 1    |      | μF   |

| $C_{USB_VREGI}$          | USB voltage regula-<br>tor in decoupling ca-<br>pacitor.                    | X5R capacitor recommended.<br>Apply between USB_VREGI<br>pin and GROUND |      | 4.7  |      | μF   |

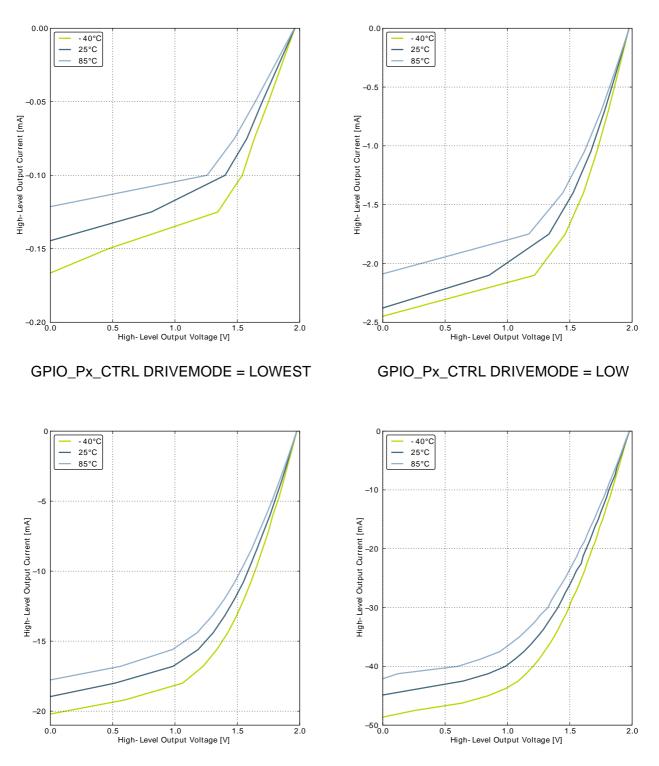

### Figure 3.5. Typical High-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

### 3.9 Oscillators

### 3.9.1 LFXO

#### Table 3.8. LFXO

| Symbol              | Parameter                                                      | Condition                                                                                                      | Min            | Тур    | Max  | Unit |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--------|------|------|

| f <sub>LFXO</sub>   | Supported nominal crystal frequency                            |                                                                                                                |                | 32.768 |      | kHz  |

| ESR <sub>LFXO</sub> | Supported crystal<br>equivalent series re-<br>sistance (ESR)   |                                                                                                                |                | 30     | 120  | kOhm |

| C <sub>LFXOL</sub>  | Supported crystal external load range                          |                                                                                                                | X <sup>1</sup> |        | 25   | pF   |

| DC <sub>LFXO</sub>  | Duty cycle                                                     |                                                                                                                | 48             | 50     | 53.5 | %    |

| I <sub>LFXO</sub>   | Current consump-<br>tion for core and<br>buffer after startup. | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>LFXOBOOST in CMU_CTRL is<br>1                                           |                | 190    |      | nA   |

| t <sub>LFXO</sub>   | Start- up time.                                                | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>40% - 60% duty cycle has<br>been reached, LFXOBOOST in<br>CMU_CTRL is 1 |                | 400    |      | ms   |

<sup>1</sup>See Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup in energyAware Designer in Simplicity Studio

For safe startup of a given crystal, the Configurator tool in Simplicity Studio contains a tool to help users configure both load capacitance and software settings for using the LFXO. For details regarding the crystal configuration, the reader is referred to application note "AN0016 EFM32 Oscillator Design Consideration".

### 3.9.2 HFXO

#### Table 3.9. HFXO

| Symbol              | Parameter                                                                       | Condition                                                                          | Min | Тур | Max  | Unit |

|---------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>HFXO</sub>   | Supported nominal crystal Frequency                                             |                                                                                    | 4   |     | 48   | MHz  |

|                     | Supported crystal                                                               | Crystal frequency 48 MHz                                                           |     |     | 50   | Ohm  |

| ESR <sub>HFXO</sub> | equivalent series re-                                                           | Crystal frequency 32 MHz                                                           |     | 30  | 60   | Ohm  |

|                     | sistance (ESR)                                                                  | Crystal frequency 4 MHz                                                            |     | 400 | 1500 | Ohm  |

| 9 <sub>mHFXO</sub>  | The transconduc-<br>tance of the HFXO<br>input transistor at<br>crystal startup | HFXOBOOST in CMU_CTRL<br>equals 0b11                                               | 20  |     |      | mS   |

| C <sub>HFXOL</sub>  | Supported crystal external load range                                           |                                                                                    | 5   |     | 25   | pF   |

|                     | Current consump-                                                                | 4 MHz: ESR=400 Ohm,<br>C <sub>L</sub> =20 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11 |     | 85  |      | μΑ   |

| IHFXO               | startup                                                                         | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11 |     | 165 |      | μA   |

| t <sub>HFXO</sub>   | Startup time                                                                    | 32 MHz: ESR=30 Ohm,<br>$C_L$ =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11          |     | 400 |      | μs   |

| Symbol                         | Parameter                                           | Condition                    | Min | Тур              | Max | Unit |

|--------------------------------|-----------------------------------------------------|------------------------------|-----|------------------|-----|------|

|                                |                                                     | f <sub>HFRCO</sub> = 28 MHz  |     | 165              | 190 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 21 MHz  |     | 134              | 155 | μA   |

| 1                              | Current consump-                                    | f <sub>HFRCO</sub> = 14 MHz  |     | 106              | 120 | μA   |

|                                | tion (Production test<br>condition = 14MHz)         | f <sub>HFRCO</sub> = 11 MHz  |     | 94               | 110 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 6.6 MHz |     | 77               | 90  | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 1.2 MHz |     | 25               | 32  | μA   |

| TUNESTEP <sub>H-</sub><br>FRCO | Frequency step<br>for LSB change in<br>TUNING value |                              |     | 0.3 <sup>3</sup> |     | %    |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_HFRCOCTRL register may be used to adjust the HFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the HFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

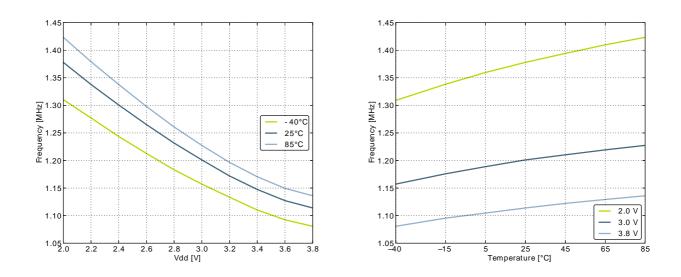

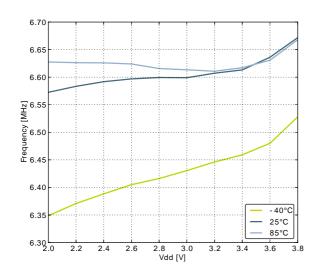

Figure 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature

Figure 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature

### 3.9.6 ULFRCO

#### Table 3.13. ULFRCO

| Symbol               | Parameter                       | Condition | Min  | Тур   | Мах  | Unit |

|----------------------|---------------------------------|-----------|------|-------|------|------|

| fulfrco              | Oscillation frequen-<br>cy      | 25°C, 3V  | 0.70 |       | 1.75 | kHz  |

| TC <sub>ULFRCO</sub> | Temperature coeffi-<br>cient    |           |      | 0.05  |      | %/°C |

| VC <sub>ULFRCO</sub> | Supply voltage co-<br>efficient |           |      | -18.2 |      | %/V  |

## 3.10 Analog Digital Converter (ADC)

### Table 3.14. ADC

| Symbol                    | Parameter                                                                             | Condition                                                                                       | Min                  | Тур  | Мах                   | Unit |

|---------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|------|-----------------------|------|

| \/                        |                                                                                       | Single ended                                                                                    | 0                    |      | V <sub>REF</sub>      | V    |

| V <sub>ADCIN</sub>        | Input voltage range                                                                   | Differential                                                                                    | -V <sub>REF</sub> /2 |      | V <sub>REF</sub> /2   | V    |

| V <sub>ADCREFIN</sub>     | Input range of exter-<br>nal reference volt-<br>age, single ended<br>and differential |                                                                                                 | 1.25                 |      | V <sub>DD</sub>       | V    |

| V <sub>ADCREFIN_CH7</sub> | Input range of ex-<br>ternal negative ref-<br>erence voltage on<br>channel 7          | See V <sub>ADCREFIN</sub>                                                                       | 0                    |      | V <sub>DD</sub> - 1.1 | V    |

| V <sub>ADCREFIN_CH6</sub> | Input range of ex-<br>ternal positive ref-<br>erence voltage on<br>channel 6          | See V <sub>ADCREFIN</sub>                                                                       | 0.625                |      | V <sub>DD</sub>       | V    |

| V <sub>ADCCMIN</sub>      | Common mode in-<br>put range                                                          |                                                                                                 | 0                    |      | V <sub>DD</sub>       | V    |

|                           | Input current                                                                         | 2pF sampling capacitors                                                                         |                      | <100 |                       | nA   |

| CMRR <sub>ADC</sub>       | Analog input com-<br>mon mode rejection ratio                                         |                                                                                                 |                      | 65   |                       | dB   |

|                           |                                                                                       | 1 MSamples/s, 12 bit, external reference                                                        |                      | 351  |                       | μA   |

|                           |                                                                                       | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b00 |                      | 67   |                       | μA   |

| I <sub>ADC</sub>          | Average active cur-<br>rent                                                           | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b01 |                      | 63   |                       | μA   |

|                           |                                                                                       | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b10 |                      | 64   |                       | μA   |

| I <sub>ADCREF</sub>       | Current consump-<br>tion of internal volt-<br>age reference                           | Internal voltage reference                                                                      |                      | 65   |                       | μA   |

| Symbol               | Parameter                                          | Condition                                                                | Min | Тур | Мах | Unit |

|----------------------|----------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

|                      |                                                    | 200 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 62  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference          |     | 67  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 | 63  | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, 2xV <sub>DD</sub> reference   |     | 70  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single<br>ended, internal 1.25V refer-<br>ence     |     | 58  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single<br>ended, internal 2.5V reference           |     | 62  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, single<br>ended, V <sub>DD</sub> reference         |     | 64  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25V reference        |     | 60  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5V reference         |     | 64  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differen-<br>tial, 5V reference                    |     | 54  |     | dB   |

|                      |                                                    | 1 MSamples/s, 12 bit, differential, $V_{DD}$ reference                   |     | 66  |     | dB   |

| SINAD <sub>ADC</sub> | SIgnal-to-Noise<br>And Distortion-ratio<br>(SINAD) | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference     |     | 68  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 61  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 65  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference          |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 63  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |     | 66  |     | dB   |

|                      |                                                    | 200 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 | 62  | 65  |     | dB   |

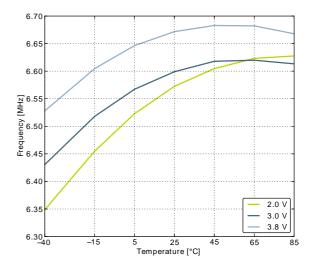

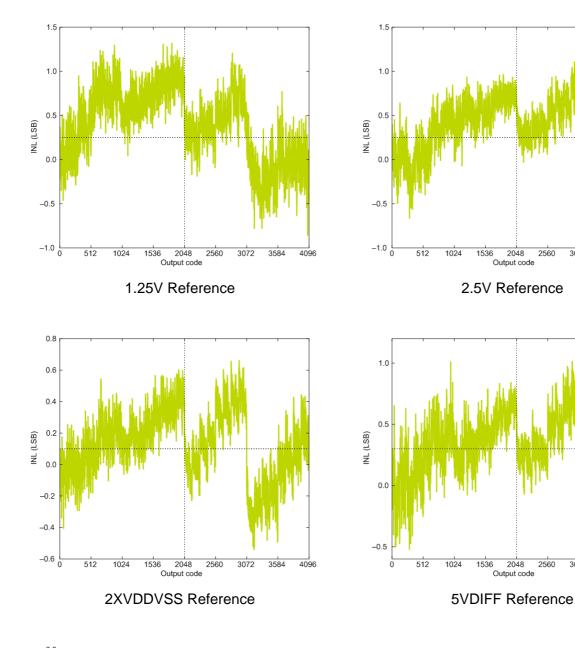

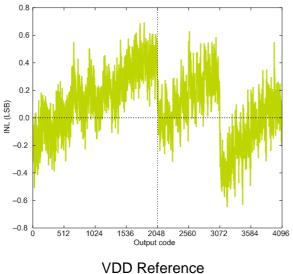

### Figure 3.20. ADC Integral Linearity Error vs Code, Vdd = 3V, Temp = 25°C

2016-03-21 - EFM32GG380FXX - d0039\_Rev1.40

| Symbol                    | Parameter                     | Condition                                                                            | Min             | Тур  | Max                  | Unit              |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|------|----------------------|-------------------|

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain                             |                 | 13   | 17                   | μA                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 101  |                      | dB                |

| G <sub>OL</sub>           | Open Loop Gain                | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 98   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 91   |                      | dB                |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 6.1  |                      | MHz               |

| GBW <sub>OPAMP</sub>      | Gain Bandwidth<br>Product     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 1.8  |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.25 |                      | MHz               |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, CL=75<br>pF                               |                 | 64   |                      | 0                 |

| PM <sub>OPAMP</sub>       | Phase Margin                  | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | o                 |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1, C <sub>L</sub> =75<br>pF                  |                 | 58   |                      | o                 |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100  |                      | Mohm              |

| R <sub>LOAD</sub>         | Load Resistance               |                                                                                      | 200             |      |                      | Ohm               |

| I <sub>LOAD_DC</sub>      | DC Load Current               |                                                                                      |                 |      | 11                   | mA                |

| V <sub>INPUT</sub>        | Input Voltage                 | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub>      | V                 |

| * INPUT                   | input voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |      | V <sub>DD</sub> -1.2 | V                 |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |      | V <sub>DD</sub>      | V                 |

| Voffset                   | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     | -13             | 0    | 11                   | mV                |

| VOFFSET                   | input Onset Voltage           | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1    |                      | mV                |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |      | 0.02                 | mV/°C             |

|                           |                               | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0                                            |                 | 3.2  |                      | V/µs              |

| SR <sub>OPAMP</sub>       | Slew Rate                     | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.8  |                      | V/µs              |

|                           |                               | (OPA2)BIASPROG=0x0,<br>(OPA2)HALFBIAS=0x1                                            |                 | 0.1  |                      | V/µs              |

| N                         |                               | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=0</f<10>  |                 | 101  |                      | μV <sub>RMS</sub> |

| N <sub>OPAMP</sub>        | Voltage Noise                 | V <sub>out</sub> =1V, RESSEL=0,<br>0.1 Hz <f<10 khz,="" opax-<br="">HCMDIS=1</f<10>  |                 | 141  |                      | μV <sub>RMS</sub> |

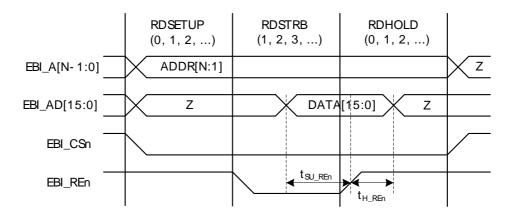

#### Figure 3.34. EBI Read Enable Related Timing Requirements

#### Table 3.22. EBI Read Enable Related Timing Requirements

| Symbol                                | Parameter                                               | Min | Тур | Мах | Unit |

|---------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| t <sub>SU_REn 1234</sub>              | Setup time, from EBI_AD valid to trailing EBI_REn edge  | 37  |     |     | ns   |

| t <sub>H_Ren</sub> <sup>1 2 3 4</sup> | Hold time, from trailing EBI_REn edge to EBI_AD invalid | -1  |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D16A8).

<sup>2</sup>Applies for both EBI\_REn and EBI\_NANDREn (figure only shows EBI\_REn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^{4}$ Measurement done at 10% and 90% of V<sub>DD</sub> (figure shows 50% of <sub>VDD</sub>)

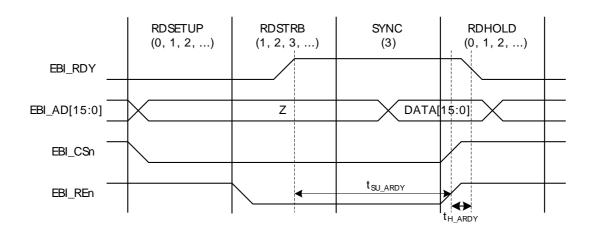

#### Figure 3.35. EBI Ready/Wait Related Timing Requirements

#### Table 3.23. EBI Ready/Wait Related Timing Requirements

| Symbol                               | Parameter                                                         | Min                                | Тур | Мах | Unit |

|--------------------------------------|-------------------------------------------------------------------|------------------------------------|-----|-----|------|

| t <sub>SU_ARDY</sub> <sup>1234</sup> | Setup time, from EBI_ARDY valid to trailing EBI_REn, EBI_WEn edge | 37 + (3 * t <sub>HFCORECLK</sub> ) |     |     | ns   |

#### Table 3.26. I2C Fast-mode Plus (Fm+)

| Symbol              | Parameter                                        | Min  | Тур | Max               | Unit |

|---------------------|--------------------------------------------------|------|-----|-------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0    |     | 1000 <sup>1</sup> | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 0.5  |     |                   | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.26 |     |                   | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 50   |     |                   | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8    |     |                   | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.26 |     |                   | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.26 |     |                   | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.26 |     |                   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 0.5  |     |                   | μs   |

<sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode Plus, see the I2C chapter in the EFM32GG Reference Manual.

### 3.17 USART SPI

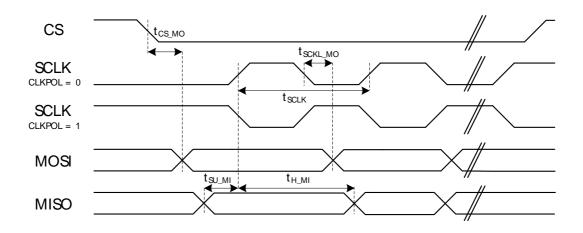

#### Figure 3.36. SPI Master Timing

#### Table 3.27. SPI Master Timing

| Symbol                             | Parameter       | Condition      | Min                            | Тур | Мах  | Unit |

|------------------------------------|-----------------|----------------|--------------------------------|-----|------|------|

| t <sub>SCLK</sub> <sup>12</sup>    | SCLK period     |                | 2 * t <sub>HFPER-</sub><br>CLK |     |      | ns   |

| t <sub>CS_MO</sub> <sup>12</sup>   | CS to MOSI      |                | -2.00                          |     | 1.00 | ns   |

| t <sub>SCLK_MO</sub> <sup>12</sup> | SCLK to MOSI    |                | -4.00                          |     | 3.00 | ns   |

| t <sub>SU_MI</sub> <sup>12</sup>   | MISO setup time | IOVDD = 1.98 V | 36.00                          |     |      | ns   |

|                                    |                 | IOVDD = 3.0 V  | 29.00                          |     |      | ns   |

| t <sub>H_MI</sub> <sup>1 2</sup>   | MISO hold time  |                | -4.00                          |     |      | ns   |

<sup>1</sup>Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

$^2\text{Measurement}$  done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $V_{\text{DD}})$

| Symbol               | Parameter       | Condition                              | Min | Тур  | Мах | Unit       |

|----------------------|-----------------|----------------------------------------|-----|------|-----|------------|

| I <sub>TIMER</sub>   | TIMER current   | TIMER_0 idle current, clock enabled    |     | 6.9  |     | µA/<br>MHz |

| I <sub>LETIMER</sub> | LETIMER current | LETIMER idle current, clock<br>enabled |     | 119  |     | nA         |

| I <sub>PCNT</sub>    | PCNT current    | PCNT idle current, clock en-<br>abled  |     | 54   |     | nA         |

| I <sub>RTC</sub>     | RTC current     | RTC idle current, clock enabled        |     | 54   |     | nA         |

| I <sub>AES</sub>     | AES current     | AES idle current, clock enabled        |     | 3.2  |     | μΑ/<br>MHz |

| I <sub>GPIO</sub>    | GPIO current    | GPIO idle current, clock en-<br>abled  |     | 3.7  |     | μA/<br>MHz |

| I <sub>EBI</sub>     | EBI current     | EBI idle current, clock enabled        |     | 11.8 |     | μA/<br>MHz |

| I <sub>PRS</sub>     | PRS current     | PRS idle current                       |     | 3.5  |     | μA/<br>MHz |

| I <sub>DMA</sub>     | DMA current     | Clock enable                           |     | 11.0 |     | μA/<br>MHz |

## **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32GG380.

### 4.1 Pinout

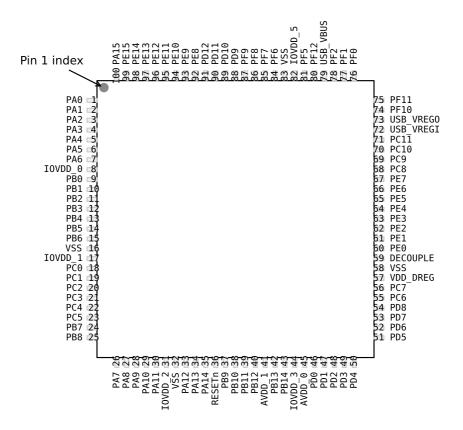

The *EFM32GG380* pinout is shown in Figure 4.1 (p. 53) and Table 4.1 (p. 53). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32GG380 Pinout (top view, not to scale)

Table 4.1. Device Pinout

|       | QFP100 Pin#<br>and Name | Pin Alternate Functionality / Description |                 |                 |                           |                           |

|-------|-------------------------|-------------------------------------------|-----------------|-----------------|---------------------------|---------------------------|

| Pin # | Pin Name                | Analog                                    | EBI             | Timers          | Communication             | Other                     |

| 1     | PA0                     |                                           | EBI_AD09 #0/1/2 | TIM0_CC0 #0/1/4 | I2C0_SDA #0<br>LEU0_RX #4 | PRS_CH0 #0<br>GPIO_EM4WU0 |

| 2     | PA1                     |                                           | EBI_AD10 #0/1/2 | TIM0_CC1 #0/1   | I2C0_SCL #0               | CMU_CLK1 #0<br>PRS_CH1 #0 |

| 3     | PA2                     |                                           | EBI_AD11 #0/1/2 | TIM0_CC2 #0/1   |                           | CMU_CLK0 #0               |

# 6 Chip Marking, Revision and Errata

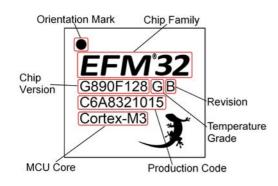

## 6.1 Chip Marking

In the illustration below package fields and position are shown.

Figure 6.1. Example Chip Marking (top view)

## 6.2 Revision

The revision of a chip can be determined from the "Revision" field in Figure 6.1 (p. 69).

### 6.3 Errata

Please see the errata document for EFM32GG380 for description and resolution of device erratas. This document is available in Simplicity Studio and online at: http://www.silabs.com/support/pages/document-library.aspx?p=MCUs--32-bit

# **7 Revision History**

## 7.1 Revision 1.40

March 21st, 2016

Added clarification on conditions for INL<sub>ADC</sub> and DNL<sub>ADC</sub> parameters.

Reduced maximum and typical current consumption for all EM0 entries except 48 MHz in the Current Consumption table in the Electrical Characteristics section.

Increased maximum specifications for EM2 current, EM3 current, and EM4 current in the Current Consumption table in the Electrical Characteristics section.

Increased typical specification for EM2 and EM3 current at 85 C in the Current Consumption table in the Electrical Characteristics section.

Added EM2, EM3, and EM4 current consumption vs. temperature graphs.

Added a new EM2 entry and specified the existing specification is for EM0 for the BOD threshold on falling external supply voltage in the Power Management table in the Electrical Characteristics section.

Reduced maximum input leakage current in the GPIO table in the Electrical Characteristics section.

Added a maximum current consumption specification to the LFRCO table in the Electrical Characteristics section.

Added maximum specifications for the active current including references for two channels to the DAC table in the Electrical Characteristics section.

Increased the maximum specification for DAC offset voltage in the DAC table in the Electrical Characteristics section.

Increased the typical specifications for active current with FULLBIAS=1 and capacitive sense internal resistance in the ACMP table in the Electrical Characteristics section.

Added minimum and maximum specifications and updated the typical value for the VCMP offset voltage in the VCMP table in the Electrical Characteristics section.

Removed the maximum specification and reduced the typical value for hysteresis in the VCMP table in the Electrical Characteristics section.

Updated all graphs in the Electrical Characteristics section to display data for 2.0 V as the minimum voltage.

### 7.2 Revision 1.30

May 23rd, 2014

Removed "preliminary" markings

Updated HFRCO figures.

Corrected single power supply voltage minimum value from 1.85V to 1.98V.

Updated Current Consumption information.

Updated Power Management information.

### **EFM<sup>®</sup>32**

Updated GPIO information.

Updated LFRCO information.

Updated HFRCO information.

Updated ULFRCO information.

Updated ADC information.

Updated DAC information.

Updated OPAMP information.

Updated ACMP information.

Updated VCMP information.

Added AUXHFRCO information.

### 7.3 Revision 1.21

November 21st, 2013

Updated figures.

Updated errata-link.

Updated chip marking.

Added link to Environmental and Quality information.

Re-added missing DAC-data.

### 7.4 Revision 1.20

September 30th, 2013

Added I2C characterization data.

Added SPI characterization data.

Added EBI characterization data.

Corrected the DAC and OPAMP2 pin sharing information in the Alternate Functionality Pinout section.

Corrected GPIO operating voltage from 1.8 V to 1.85 V.

Added the USB bootloader information.

Updated that the EM2 current consumption test was carried out with only one RAM block enabled.

Corrected the ADC resolution from 12, 10 and 6 bit to 12, 8 and 6 bit.

Updated Environmental information.

Updated trademark, disclaimer and contact information.

Other minor corrections.

## 7.10 Revision 0.91

March 21th, 2011

Added new alternative locations for EBI and SWO.

Added new USB Pin to pinout table.

Corrected slew rate data for Opamps.

### 7.11 Revision 0.90

February 4th, 2011

Initial preliminary release.

# **B** Contact Information

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

# List of Equations

| 3.1. Total ACMP Active Current                         | 43 |

|--------------------------------------------------------|----|

| 3.2. VCMP Trigger Level as a Function of Level Setting | 45 |