Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Detuns                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62a-04-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

## 9.0 TIMER2 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

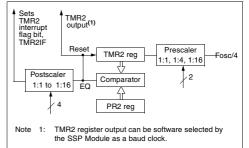

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

#### Applicable Devices

### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

#### 9.2 Output of TMR2

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

| Addr                 | Name    | Bit 7                    | Bit 6         | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|----------------------|---------|--------------------------|---------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                      | PEIE          | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000<br>000x             | 0000<br>000u                    |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup>     | (3)           | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000                     | 0000                            |

| 0Dh <sup>(4)</sup>   | PIR2    | —                        | _             | _                   | _                   | _       | _      | _       | CCP2IF  |                          | <br>0                           |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup>     | (3)           | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000                     | 0000                            |

| 8Dh <sup>(4)</sup>   | PIE2    | —                        | _             | -                   | _                   | -       | _      | -       | CCP2IE  |                          | <br>0                           |

| 87h                  | TRISC   | PORTC [                  | Data Directio | on register         |                     |         |        |         |         | 1111<br>1111             | 1111<br>1111                    |

| 11h                  | TMR2    | Timer2 module's register |               |                     |                     |         |        |         |         | 0000                     | 0000                            |

| 92h                  | PR2     | Timer2 m                 | iodule's Per  | iod register        |                     |         |        |         |         | 1111<br>1111             | 1111<br>1111                    |

| 12h                  | T2CON   | —                        | TOUTPS3       | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000<br>0000             | -000<br>0000                    |

| 15h                  | CCPR1L  | Capture/0                | Compare/P     | VM1 (LSB)           | 1                   |         |        |         |         | xxxx<br>xxxx             | uuuu<br>uuuu                    |

| 16h                  | CCPR1H  | Capture/0                | Compare/P     | VM1 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 17h                  | CCP1CON | —                        | —             | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00<br>0000               | 00<br>0000                      |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/0                | Compare/P     | VM2 (LSB)           | 1                   |         | 1      |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/0                | Compare/P\    | VM2 (MSB            | )                   |         |        |         |         | xxxx<br>xxxx             | นนนน<br>นนนน                    |

| 1Dh <sup>(4)</sup>   | CCP2CON | -                        | —             | CCP2X               | CCP2Y               | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00<br>0000               | 00<br>0000                      |

### TABLE 10-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend:

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in this mode.

Note

1:

These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

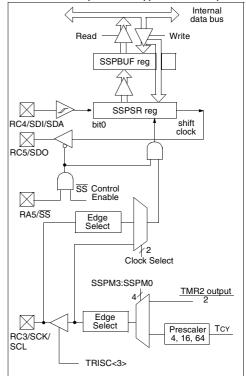

#### 11.3.1 SSP MODULE IN SPI MODE FOR PIC16C66/67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- · Clock Rate (Master mode only)

- · Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device. MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

#### EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C66/67)

| LOOP | BCF<br>BSF<br>BTFSS | STATUS,<br>STATUS,<br>SSPSTAT, | RP0 | ;Specify Bank 1<br>;<br>;Has data been<br>;received<br>;(transmit<br>;complete)? |

|------|---------------------|--------------------------------|-----|----------------------------------------------------------------------------------|

|      | GOTO                | LOOP                           |     | ;No                                                                              |

|      | BCF                 | STATUS,                        | RP0 | ;Specify Bank 0                                                                  |

|      | MOVF                | SSPBUF,                        | W   | ;W reg = contents<br>; of SSPBUF                                                 |

|      | MOVWF               | RXDATA                         |     | ;Save in user RAM                                                                |

|      | MOVF                | TXDATA,                        | W   | ;W reg = contents<br>; of TXDATA                                                 |

|      | MOVWF               | SSPBUF                         |     | ;New data to xmit                                                                |

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

#### FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C66/67)

#### 12.3 USART Synchronous Master Mode

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Synchronous Master mode the data is transmitted in a half-duplex manner i.e., transmission and reception do not occur at the same time. When transmitting data the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6 and RC7 I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR register is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG register is empty and interrupt flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the status of enable bit TXIE and cannot be cleared in software. It will clear only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR register is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in reset when bits TXEN. CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG register. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hi-impedance. If, during a transmission, either bit CREN or bit SREN is set the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however, is not reset although it is disconnected from the pins. In order to reset the transmitter, the user has to clear enable bit TXEN. If enable bit SREN is set (to interrupt an on going transmission and receive a single word), then after the single word is received, enable bit SREN will be cleared, and the serial port will revert back to transmitting since enable bit TXEN is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, enable bit TXEN should be cleared.

In order to select 9-bit transmission, bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR register was empty and the TXREG register was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{TXIE}}$  .

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

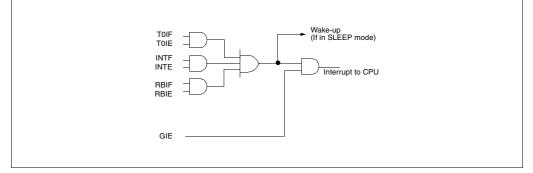

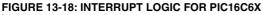

## FIGURE 13-17: INTERRUPT LOGIC FOR PIC16C61

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|-------|--------|--------|--------|--------|

| PIC16C62  | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C62A | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16CR62 | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C63  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR63 | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64A | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C65  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C65A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR65 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C66  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C67  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 15.0 ELECTRICAL CHARACTERISTICS FOR PIC16C61

### Absolute Maximum Ratings †

this pin directly to Vss.

| Ambient temperature under bias                                                                             | -55°C to +125°C                    |

|------------------------------------------------------------------------------------------------------------|------------------------------------|

| •                                                                                                          |                                    |

| Storage temperature                                                                                        | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                         | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to VSS                                                                         | -0.3V to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                               | 0V to +14V                         |

| Voltage on RA4 pin with respect to Vss                                                                     | 0V to +14V                         |

| Total power dissipation (Note 1)                                                                           | 800 mW                             |

| Maximum current out of Vss pin                                                                             | 150 mA                             |

| Maximum current into VDD pin                                                                               | 100 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                               | ± 20 mA                            |

| Output clamp current, Iок (Vo < 0 or Vo > VDD)                                                             | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                 | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                              | 20 mA                              |

| Maximum current sunk by PORTA                                                                              | 80 mA                              |

| Maximum current sourced by PORTA                                                                           | 50 mA                              |

| Maximum current sunk by PORTB                                                                              | 150 mA                             |

| Maximum current sourced by PORTB                                                                           | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD- | VOH) x IOH} + $\Sigma$ (VOI x IOL) |

**Note 2:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 15-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C61-04                | PIC16C61-20              | PIC16LC61-04               | JW Devices                 |

|-----|----------------------------|--------------------------|----------------------------|----------------------------|

| RC  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| XT  | VDD: 4.0V to 6.0V          | VDD: 4.5V to 5.5V        | VDD: 3.0V to 6.0V          | VDD: 4.0V to 6.0V          |

|     | IDD: 3.3 mA max. at 5.5V   | IDD: 1.8 mA typ. at 5.5V | IDD: 1.4 mA typ. at 3.0V   | IDD: 3.3 mA max. at 5.5V   |

|     | IPD: 14 μA max. at 4V      | IPD: 1.0 μA typ. at 4V   | IPD: 0.6 μA typ. at 3V     | IPD: 14 μA max. at 4V      |

|     | Freq: 4 MHz max.           | Freq: 4 MHz max.         | Freq: 4 MHz max.           | Freq: 4 MHz max.           |

| HS  | VDD: 4.5V to 5.5V          | VDD: 4.5V to 5.5V        |                            | VDD: 4.5V to 5.5V          |

|     | IDD: 13.5 mA typ. at 5.5V  | IDD: 30 mA max. at 5.5V  | Not recommended for use in | IDD: 30 mA max. at 5.5V    |

|     | IPD: 1.0 μA typ. at 4.5V   | IPD: 1.0 μA typ. at 4.5V | HS mode                    | IPD: 1.0 μA typ. at 4.5V   |

|     | Freq: 4 MHz max.           | Freq: 20 MHz max.        |                            | Freq: 20 MHz max.          |

| LP  | VDD: 4.0V to 6.0V          |                          | VDD: 3.0V to 6.0V          | VDD: 3.0V to 6.0V          |

|     | IDD: 15 μA typ. at 32 kHz, | Not recommended for      | IDD: 32 μA max. at 32 kHz, | IDD: 32 μA max. at 32 kHz, |

|     | 4.0V                       | use in LP mode           | 3.0V                       | 3.0V                       |

|     | IPD: 0.6 μA typ. at 4.0V   | use in LP mode           | IPD: 9 μA max. at 3.0V     | IPD: 9 μA max. at 3.0V     |

|     | Freq: 200 kHz max.         |                          | Freq: 200 kHz max.         | Freq: 200 kHz max.         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 15.2 DC Characteristics: PIC16LC61-04 (Commercial, Industrial)

|              |                                                                  | Standa   | rd Ope  | rating ( | Condi | tions (u | Inless otherwise stated)                                         |

|--------------|------------------------------------------------------------------|----------|---------|----------|-------|----------|------------------------------------------------------------------|

| DC CHA       | RACTERISTICS                                                     | Operatir | ng temp | perature | -40   | °C ≤     | $TA \le +85^{\circ}C$ for industrial and                         |

|              |                                                                  |          |         |          | 0°C   | ≥ ≤      | $TA \le +70^{\circ}C$ for commercial                             |

| Param<br>No. | Characteristic                                                   | Sym      | Min     | Тур†     | Max   | Units    | Conditions                                                       |

| D001         | Supply Voltage                                                   | Vdd      | 3.0     | -        | 6.0   | V        | XT, RC, and LP osc configuration                                 |

| D002*        | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr      | -       | 1.5      | -     | V        |                                                                  |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR     | -       | Vss      | -     | V        | See section on Power-on Reset for details                        |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD     | 0.05    | -        | -     | V/ms     | See section on Power-on Reset for details                        |

| D010         | Supply Current (Note 2)                                          | Idd      | -       | 1.4      | 2.5   | mA       | Fosc = 4 MHz, VDD = 3.0V (Note 4)                                |

| D010A        |                                                                  |          | -       | 15       | 32    | μA       | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc configuration |

| D020         | Power-down Current                                               | IPD      | -       | 5        | 20    | μΑ       | VDD = 3.0V, WDT enabled, -40°C to +85°C                          |

| D021         | (Note 3)                                                         |          | -       | 0.6      | 9     | μA       | VDD = 3.0V, WDT disabled, 0°C to +70°C                           |

| D021A        |                                                                  |          | -       | 0.6      | 12    | μA       | VDD = 3.0V, WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

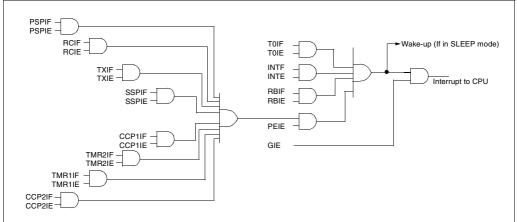

## FIGURE 15-5: TIMER0 EXTERNAL CLOCK TIMINGS

## TABLE 15-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         | acteristic     |                                                 | Тур† | Max | Units | Conditions         |

|------------------|------|------------------------|----------------|-------------------------------------------------|------|-----|-------|--------------------|

| 40*              | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20                                     | _    | _   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | _   | ns    | parameter 42       |

| 41*              | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TCY + 20                                     | —    | —   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | —   | ns    | parameter 42       |

| 42*              | Tt0P | T0CKI Period           | No Prescaler   | TCY + 40                                        | _    | _   |       | N = prescale value |

|                  |      |                        | With Prescaler | Greater of:<br>20 ns or<br><u>Tcy + 40</u><br>N | _    | _   | ns    | (2, 4,, 256)       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

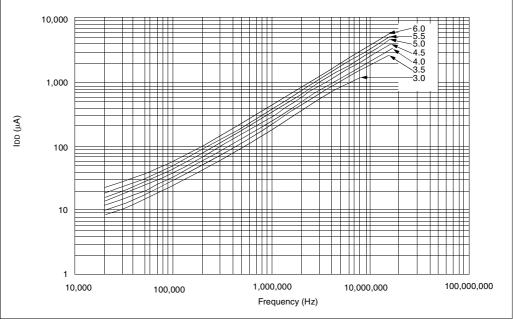

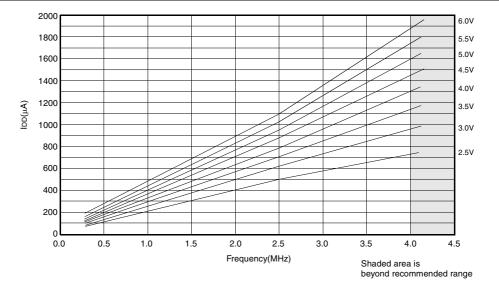

FIGURE 16-12: TYPICAL IDD VS. FREQUENCY (EXTERNAL CLOCK, 25°C)

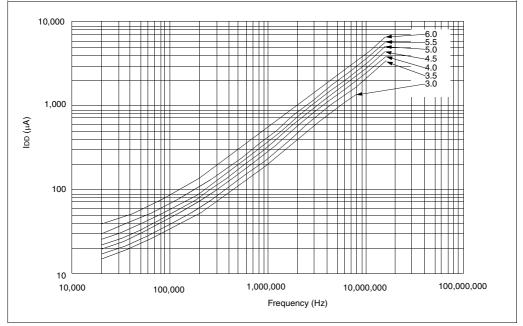

FIGURE 16-13: MAXIMUM IDD vs. FREQUENCY (EXTERNAL CLOCK, -40° TO +85°C)

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

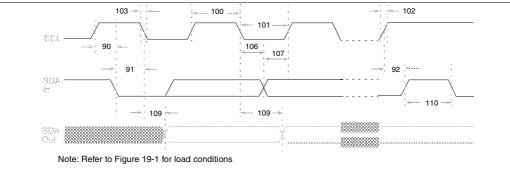

## FIGURE 19-10: I<sup>2</sup>C BUS DATA TIMING

### TABLE 19-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Тнідн   | Clock high time        | 100 kHz mode | 4.0        |      | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | -    | μs    | Devce must operate at a mini-<br>mum of 10 MHz   |

|                  |         |                        | SSP Module   | 1.5Tcy     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | -    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                                  |

| 102              | TR      | SDA and SCL rise       | 100 kHz mode | _          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |

| 103              | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF             |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | _    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | _    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        |      | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        |      | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | TAA     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | —          | _    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | before a new transmission can<br>start           |

|                  | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz)  $I^2C$ -bus device can be used in a standard-mode (100 kHz)  $I^2C$ -bus system, but the requirement tsu;DAT  $\ge$  250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode  $I^2C$  bus specification) before the SCL line is released.

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 20.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | opS                                    | 3. Tcc:st        | (I <sup>2</sup> C specifications only) |

|-----------------------|----------------------------------------|------------------|----------------------------------------|

| 2. TppS               |                                        | 4. Ts            | (I <sup>2</sup> C specifications only) |

| Т                     |                                        |                  | · · · · ·                              |

| F                     | Frequency                              | Т                | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:   |                  |                                        |

| рр                    |                                        |                  |                                        |

| сс                    | CCP1                                   | osc              | OSC1                                   |

| ck                    | CLKOUT                                 | rd               | RD                                     |

| CS                    | CS                                     | rw               | RD or WR                               |

| di                    | SDI                                    | sc               | SCK                                    |

| do                    | SDO                                    | SS               | SS                                     |

| dt                    | Data in                                | tO               | TOCKI                                  |

| io                    | I/O port                               | t1               | T1CKI                                  |

| mc                    | MCLR                                   | wr               | WR                                     |

| Upperca               | ase letters and their meanings:        |                  |                                        |

| S                     |                                        |                  |                                        |

| F                     | Fall                                   | Р                | Period                                 |

| Н                     | High                                   | R                | Rise                                   |

| I                     | Invalid (Hi-impedance)                 | V                | Valid                                  |

| L                     | Low                                    | Z                | Hi-impedance                           |

| I <sup>2</sup> C only |                                        |                  |                                        |

| AA                    | output access                          | High             | High                                   |

| BUF                   | Bus free                               | Low              | Low                                    |

| Tcc:st                | (I <sup>2</sup> C specifications only) |                  |                                        |

| CC                    | · · · ·                                |                  |                                        |

| HD                    | Hold                                   | SU               | Setup                                  |

| ST                    |                                        |                  |                                        |

| DAT                   | DATA input hold                        | STO              | STOP condition                         |

| STA                   | START condition                        |                  |                                        |

|                       | 20-1: LOAD CONDITIONS FOR DEVIC        |                  | SPECIFICATIONS                         |

|                       |                                        |                  |                                        |

|                       | Load condition 1                       |                  | Load condition 2                       |

|                       | VDD/2                                  |                  |                                        |

|                       | Ŷ                                      |                  |                                        |

|                       |                                        |                  | Pin CL                                 |

|                       | $\leq$ $^{\text{\tiny ML}}$            |                  | FIII                                   |

|                       |                                        |                  | Vss                                    |

|                       |                                        |                  |                                        |

|                       |                                        | $RL = 464\Omega$ |                                        |

|                       | Vss                                    | C∟ = 50 pF       | for all pins except OSC2/CLKOUT        |

| Note 1.               | PORTD and PORTE are not imple-         | •                | but including D and E outputs as ports |

| NOLE I.               | mented on the PIC16C63.                | 15 pF            | for OSC2 output                        |

|                       |                                        |                  | •                                      |

|                       |                                        |                  |                                        |

|                       |                                        |                  |                                        |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

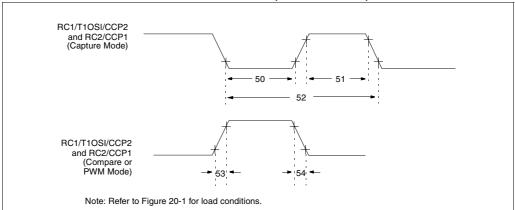

## FIGURE 20-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 20-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym            | Characteristic                      |                        |                        | Min         | Тур† | Max | Units                              | Conditions |

|------------------|----------------|-------------------------------------|------------------------|------------------------|-------------|------|-----|------------------------------------|------------|

| 50*              | TccL           | CCP1 and CCP2                       | No Prescaler           |                        | 0.5Tcy + 20 | _    | _   | ns                                 |            |

|                  | inpu           | input low time                      | With Prescaler         | PIC16 <b>C</b> 63/65A  | 10          | —    |     | ns                                 |            |

|                  |                |                                     |                        | PIC16LC63/65A          | 20          | —    |     | ns                                 |            |

| 51*              | TccH           | CCP1 and CCP2                       | No Prescaler           |                        | 0.5TCY + 20 | -    |     | ns                                 |            |

|                  | input high tim | input high time                     | With Prescaler         | PIC16 <b>C</b> 63/65A  | 10          | —    |     | ns                                 |            |

|                  |                |                                     | PIC16 <b>LC</b> 63/65A | 20                     | -           |      | ns  |                                    |            |

| 52*              | TccP           | CCP1 and CCP2 input period          |                        | <u>3Tcy + 40</u><br>N  | -           |      | ns  | N = prescale value<br>(1,4, or 16) |            |

| 53*              | TccR           | CCP1 and CCP2 output rise time      |                        | PIC16 <b>C</b> 63/65A  | _           | 10   | 25  | ns                                 |            |

|                  |                |                                     |                        | PIC16 <b>LC</b> 63/65A | _           | 25   | 45  | ns                                 |            |

| 54*              | TccF           | TccF CCP1 and CCP2 output fall time |                        | PIC16 <b>C</b> 63/65A  | _           | 10   | 25  | ns                                 |            |

|                  |                |                                     |                        | PIC16 <b>LC</b> 63/65A | _           | 25   | 45  | ns                                 |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 21.3 DC Characteristics: PIC16CR63/R65-04 (Commercial, Industrial) PIC16CR63/R65-10 (Commercial, Industrial) PIC16CR63/R65-20 (Commercial, Industrial) PIC16LCR63/R65-04 (Commercial, Industrial)

|              |                                    |                     | rd Operat |          |                   |       | ss otherwise stated)<br>$A \le +85^{\circ}C$ for industrial and    |

|--------------|------------------------------------|---------------------|-----------|----------|-------------------|-------|--------------------------------------------------------------------|

| DC CHA       | RACTERISTICS                       | Operatir<br>Section |           | Vdd      | 0°C<br>range as o |       | $A \le +70^{\circ}C$ for commercial ed in DC spec Section 21.1 and |

| Param<br>No. | Characteristic                     | Sym                 | Min       | Тур<br>† | Мах               | Units | Conditions                                                         |

|              | Input Low Voltage                  |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | VIL                 |           |          |                   |       |                                                                    |

| D030         | with TTL buffer                    |                     | Vss       | -        | 0.15Vdd           | v     | For entire VDD range                                               |

| D030A        |                                    |                     | Vss       | -        | 0.8V              | v     | $4.5V \le VDD \le 5.5V$                                            |

| D031         | with Schmitt Trigger buffer        |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D032         | MCLR, OSC1 (in RC mode)            |                     | Vss       | -        | 0.2VDD            | v     |                                                                    |

| D033         | OSC1 (in XT, HS and LP)            |                     | Vss       | -        | 0.3VDD            | v     | Note1                                                              |

|              | Input High Voltage                 |                     |           |          |                   |       |                                                                    |

|              | I/O ports                          | Vін                 |           | -        |                   |       |                                                                    |

| D040         | with TTL buffer                    |                     | 2.0       | -        | Vdd               | v     | $4.5V \le V$ DD $\le 5.5V$                                         |

| D040A        |                                    |                     | 0.25VDD   | -        | Vdd               | v     | For entire VDD range                                               |

|              |                                    |                     | + 0.8V    |          |                   |       |                                                                    |

| D041         | with Schmitt Trigger buffer        |                     | 0.8VDD    | -        | Vdd               | v     | For entire VDD range                                               |

| D042         | MCLR                               |                     | 0.8VDD    | -        | Vdd               | V     |                                                                    |

| D042A        | OSC1 (XT, HS and LP)               |                     | 0.7Vdd    | -        | Vdd               | V     | Note1                                                              |

| D043         | OSC1 (in RC mode)                  |                     | 0.9Vdd    | -        | Vdd               | V     |                                                                    |

| D070         | PORTB weak pull-up current         | IPURB               | 50        | 250      | 400               | μΑ    | VDD = 5V, VPIN = VSS                                               |

|              | Input Leakage Current (Notes 2, 3) |                     |           |          |                   |       |                                                                    |

| D060         | I/O ports                          | lı∟                 | -         | -        | ±1                | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-<br>impedance                |

| D061         | MCLR, RA4/T0CKI                    |                     | -         | -        | ±5                | μA    | $Vss \le VPIN \le VDD$                                             |

| D063         | OSC1                               |                     | -         | -        | ±5                | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and                             |

|              |                                    |                     |           |          |                   |       | LP osc configuration                                               |

|              | Output Low Voltage                 |                     |           |          |                   |       | -                                                                  |

| D080         | I/O ports                          | Vol                 | -         | -        | 0.6               | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

| D083         | OSC2/CLKOUT (RC osc config)        |                     | -         | -        | 0.6               | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

|              | Output High Voltage                |                     |           |          |                   |       |                                                                    |

| D090         | I/O ports (Note 3)                 | Vон                 | VDD-0.7   | -        | -                 | v     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                       |

| D092         | OSC2/CLKOUT (RC osc config)        |                     | VDD-0.7   | -        | -                 | v     | IOH = -1.3  mA,  VDD = 4.5 V,<br>-40°C to +85°C                    |

| D150*        | Open-Drain High Voltage            | Vod                 | -         | -        | 14                | V     | RA4 pin                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## 21.4 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                     | 3. Tcc:st  | (I <sup>2</sup> C specifications only)                                    |

|-----------------------|----------------------------------------|------------|---------------------------------------------------------------------------|

| 2. TppS               |                                        | 4. Ts      | (I <sup>2</sup> C specifications only)                                    |

| т                     |                                        |            |                                                                           |

| F                     | Frequency                              | Т          | Time                                                                      |

| Lowerca               | ase letters (pp) and their meanings:   | ш          |                                                                           |

| рр                    |                                        |            |                                                                           |

| сс                    | CCP1                                   | osc        | OSC1                                                                      |

| ck                    | CLKOUT                                 | rd         | RD                                                                        |

| cs                    | CS                                     | rw         | RD or WR                                                                  |

| di                    | SDI                                    | sc         | SCK                                                                       |

| do                    | SDO                                    | ss         | SS                                                                        |

| dt                    | Data in                                | tO         | TOCKI                                                                     |

| io                    | I/O port                               | t1         | T1CKI                                                                     |

| mc                    | MCLR                                   | wr         | WR                                                                        |

| Upperca               | ase letters and their meanings:        |            |                                                                           |

| S                     | -                                      |            |                                                                           |

| F                     | Fall                                   | Р          | Period                                                                    |

| н                     | High                                   | R          | Rise                                                                      |

| I                     | Invalid (Hi-impedance)                 | v          | Valid                                                                     |

| L                     | Low                                    | z          | Hi-impedance                                                              |

| I <sup>2</sup> C only |                                        |            |                                                                           |

| AA                    | output access                          | High       | High                                                                      |

| BUF                   | Bus free                               | Low        | Low                                                                       |

|                       | (I <sup>2</sup> C specifications only) | 2011       |                                                                           |

| CC                    |                                        |            |                                                                           |

| HD                    | Hold                                   | SU         | Setup                                                                     |

| ST                    | Tiold                                  | 30         | Selup                                                                     |

| DAT                   | DATA input hold                        | STO        | STOP condition                                                            |

| STA                   | START condition                        | 310        | STOP condition                                                            |

| 1                     |                                        |            |                                                                           |

| FIGURE 2              | 21-1: LOAD CONDITIONS FOR DEVIC        | E TIMING S | PECIFICATIONS                                                             |

|                       | Load condition 1                       |            | Load condition 2                                                          |

|                       | VDD/2                                  |            |                                                                           |

|                       | φ                                      | Γ          | $\checkmark$                                                              |

|                       | 2                                      |            |                                                                           |

|                       | $\geq$ RL                              | I          | Pin — CL                                                                  |

|                       |                                        |            | •                                                                         |

|                       |                                        |            | Vss                                                                       |

|                       |                                        | RL = 464Ω  |                                                                           |

|                       | •                                      |            | for all pipe execut OSCO/OLKOUT                                           |

|                       | ¥85                                    | •          | for all pins except OSC2/CLKOUT<br>but including D and E outputs as ports |

| Note 1:               | PORTD and PORTE are not imple-         |            |                                                                           |

|                       | mented on the PIC16CR63.               | 15 pF      | for OSC2 output                                                           |

|                       |                                        |            |                                                                           |

|                       |                                        |            |                                                                           |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

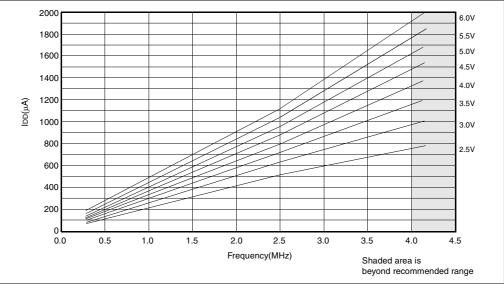

## FIGURE 23-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

### Package Marking Information (Cont'd)

## 28-Lead SOIC

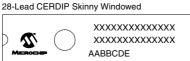

28-Lead Side Brazed Skinny Windowed

Example PIC16C66/JW  $\mathcal{D}$ 9517CAT

PIC16C62/JW

9517SBT

Example

Example

PIC16C62-20/S0111

5 9515SBA

#### 40-Lead PDIP

Example

| Legend: | MMM                 | Microchip part number information                                                                                                                                        |  |

|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | XXX                 | Customer specific information*                                                                                                                                           |  |

|         | AA                  | Year code (last 2 digits of calender year)                                                                                                                               |  |

|         | BB                  | Week code (week of January 1 is week '01')                                                                                                                               |  |

|         | С                   | Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.                                                |  |

|         | D <sub>1</sub><br>E | Mask revision number for microcontroller<br>Assembly code of the plant or country of origin in which<br>part was assembled.                                              |  |

| Note:   | line, it will b     | t the full Microchip part number cannot be marked on one<br>be carried over to the next line thus limiting the number of<br>naracters for customer specific information. |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## **PIN COMPATIBILITY**

Devices that have the same package type and VDD, VSs and  $\overline{\text{MCLR}}$  pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

| Pin Compatible Devices                                                                                                                                                                                                                                                                                                                                                                      | Package           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PIC12C508, PIC12C509, PIC12C671, PIC12C672                                                                                                                                                                                                                                                                                                                                                  | 8-pin             |

| PIC16C154, PIC16CR154, PIC16C156,<br>PIC16CR156, PIC16C158, PIC16CR158,<br>PIC16C52, PIC16C54, PIC16C54A,<br>PIC16C56,<br>PIC16C58A, PIC16CR58A,<br>PIC16C554, PIC16CR58A,<br>PIC16C554, PIC16C556, PIC16C558<br>PIC16C620, PIC16C621, PIC16C622<br>PIC16C641, PIC16C642, PIC16C661, PIC16C662<br>PIC16C710, PIC16C71, PIC16C711, PIC16C715<br>PIC16F83, PIC16CR83,<br>PIC16F84A, PIC16CR84 | 18-pin,<br>20-pin |

| PIC16C55, PIC16C57, PIC16CR57B                                                                                                                                                                                                                                                                                                                                                              | 28-pin            |

| PIC16CR62, PIC16C62A, PIC16C63, PIC16CR63,<br>PIC16C66, PIC16C72, PIC16C73A, PIC16C76                                                                                                                                                                                                                                                                                                       | 28-pin            |