Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

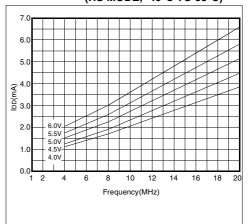

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                     |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

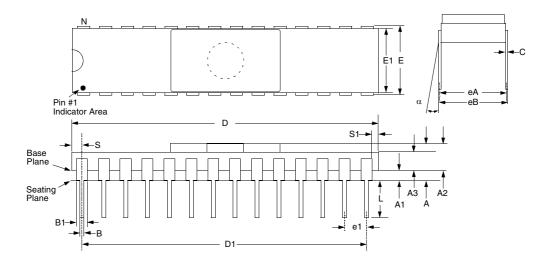

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62a-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16CXX is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C61** device has 36 bytes of RAM and 13 I/O pins. In addition a timer/counter is available.

The **PIC16C62/62A/R62** devices have 128 bytes of RAM and 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI<sup>TM</sup>) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus.

The **PIC16C63/R63** devices have 192 bytes of RAM, while the **PIC16C66** has 368 bytes. All three devices have 22 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit ( $I^2C$ ) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also know as a Serial Communications Interface or SCI.

The **PIC16C64/64A/R64** devices have 128 bytes of RAM and 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. An 8-bit Parallel Slave Port is also provided.

The **PIC16C65/65A/R65** devices have 192 bytes of RAM, while the **PIC16C67** has 368 bytes. All four devices have 33 I/O pins. In addition, several peripheral features are available, including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmit-

ter (USART) is also known as a Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is also provided.

The PIC16C6X device family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers a power saving mode. The user can wake the chip from SLEEP through several external and internal interrupts, and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C6X family fits perfectly in applications ranging from high-speed automotive and appliance control to low-power remote sensors, keyboards and telecom processors. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high performance, ease-of-use, and I/O flexibility make the PIC16C6X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions, and co-processor applications).

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16CXX family of devices (Appendix B).

### 1.2 Development Support

PIC16C6X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 15.0 for more details about Microchip's development tools.

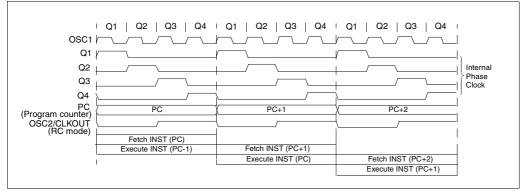

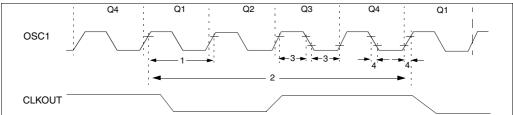

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

#### 3.2 Instruction Flow/Pipelining

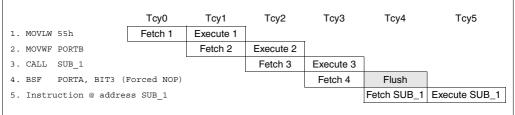

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

| Address              | Name    | Bit 7              | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                    |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad        | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   |                    | _                  | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat          | ta Latch whe       | n written: PC | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat          | ta Latch whe       | n written: PC | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat          | ta Latch whe       | n written: PC | ORTD pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                    | _                  | _             | _              | _             | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                  | —                  | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                    | _                  | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L    | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the M    | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                    | _                  | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                  | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | is Serial Port     | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                  | —                  | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                | SREN          | CREN           | —             | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai         | nsmit Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red          | ceive Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM          | 2 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM          | 2 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                  | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted               |               |                |               |                 |               |           | —                        | _                                              |

#### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

| Address               | Name   | Bit 7        | Bit 6          | Bit 5         | Bit 4         | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|-----------------------|--------|--------------|----------------|---------------|---------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 2                |        |              |                |               |               |              |                 |               |           |                          |                                                |

| 100h <sup>(1)</sup>   | INDF   | Addressing   | this location  | uses conter   | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 101h                  | TMR0   | Timer0 mod   | dule's registe | r             |               |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 102h <sup>(1)</sup>   | PCL    | Program Co   | ounter's (PC)  | Least Signi   | ficant Byte   |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 103h <sup>(1)</sup>   | STATUS | IRP          | RP1            | RP0           | TO            | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 104h <sup>(1)</sup>   | FSR    | Indirect dat | a memory ac    | Idress pointe | ər            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 105h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 106h                  | PORTB  | PORTB Da     | ta Latch whe   | n written: PO | ORTB pins wi  | nen read     |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 107h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | —                                              |

| 108h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 109h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | —                        | —                                              |

| 10Ah <sup>(1,2)</sup> | PCLATH | -            | —              | —             | Write Buffer  | for the uppe | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 10Bh <sup>(1)</sup>   | INTCON | GIE          | PEIE           | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 10Ch-<br>10Fh         | —      | Unimpleme    | nted           |               |               |              |                 |               |           | -                        | —                                              |

| Bank 3                |        |              |                |               |               |              |                 |               |           |                          |                                                |

| 180h <sup>(1)</sup>   | INDF   | Addressing   | this location  | uses conter   | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 181h                  | OPTION | RBPU         | INTEDG         | TOCS          | TOSE          | PSA          | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 182h <sup>(1)</sup>   | PCL    | Program Co   | ounter's (PC)  | Least Sigr    | nificant Byte |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 183h <sup>(1)</sup>   | STATUS | IRP          | RP1            | RP0           | TO            | PD           | Z               | DC            | с         | 0001 1xxx                | 000q quuu                                      |

| 184h <sup>(1)</sup>   | FSR    | Indirect dat | a memory ac    | Idress pointe | ər            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 185h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | _                                              |

| 186h                  | TRISB  | PORTB Da     | ta Direction I | Register      |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 187h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | —                        | —                                              |

| 188h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | —                        | —                                              |

| 189h                  | —      | Unimpleme    | nted           |               |               |              |                 |               |           | _                        | —                                              |

| 18Ah <sup>(1,2)</sup> | PCLATH | -            | —              | -             | Write Buffer  | for the uppe | r 5 bits of th  | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 18Bh <sup>(1)</sup>   | INTCON | GIE          | PEIE           | TOIE          | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 0000                                      |

| 18Ch-<br>19Fh         | -      | Unimpleme    | nted           |               |               | 1            |                 |               |           | -                        | -                                              |

### TABLE 4-6: SPECIAL FUNCTION REGISTERS FOR THE PIC16C66/67 (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: PIE1<6> and PIR1<6> are reserved on the PIC16C66/67, always maintain these bits clear.

5: PORTD, PORTE, TRISD, and TRISE are not implemented on the PIC16C66, read as '0'.

6: PSPIF (PIR1<7>) and PSPIE (PIE1<7>) are reserved on the PIC16C66, maintain these bits clear.

NOTES:

-

#### SWITCHING PRESCALER ASSIGNMENT 7.3.1

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

| Note: | To avoid an unintended device RESET, the |

|-------|------------------------------------------|

|       | following instruction sequence (shown in |

|       | Example 7-1) must be executed when       |

|       | changing the prescaler assignment from   |

|       | Timer0 to the WDT. This precaution must  |

|       | be followed even if the WDT is disabled. |

### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

|                                                                   | 1)  | BSF    | STATUS, RPO | ;Bank 1                                    |

|-------------------------------------------------------------------|-----|--------|-------------|--------------------------------------------|

| Lines 2 and 3 do NOT have to                                      | 2)  | MOVLW  | b'xx0x0xxx' | ;Select clock source and prescale value of |

| be included if the final desired                                  | 3)  | MOVWF  | OPTION_REG  | ;other than 1:1                            |

| prescale value is other than 1:1.                                 | 4)  | BCF    | STATUS, RPO | ;Bank 0                                    |

| If 1:1 is final desired value, then a temporary prescale value is | 5)  | CLRF   | TMR0        | ;Clear TMR0 and prescaler                  |

| set in lines 2 and 3 and the final                                | 6)  | BSF    | STATUS, RP1 | ;Bank 1                                    |

| prescale value will be set in lines                               | 7)  | MOVLW  | b'xxxx1xxx' | ;Select WDT, do not change prescale value  |

| 10 and 11.                                                        | 8)  | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 9)  | CLRWDT |             | ;Clears WDT and prescaler                  |

|                                                                   | 10) | MOVLW  | b'xxxx1xxx' | ;Select new prescale value and WDT         |

|                                                                   | 11) | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 12) | BCF    | STATUS, RPO | ;Bank 0                                    |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT → TIMER0)

CLRWDT ;Clear WDT and prescaler BSF STATUS, RP0 ;Bank 1 MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and clock source MOVWF OPTION REG ; BCF STATUS, RPO ;Bank 0

#### TABLE 7-1: **REGISTERS ASSOCIATED WITH TIMER0**

| Address               | Name   | Bit 7  | Bit 6               | Bit 5      | Bit 4       | Bit 3                   | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|---------------------|------------|-------------|-------------------------|-------|-------|-------|--------------------------|---------------------------|

| 01h, 101h             | TMR0   | Timer0 | module's r          | egister    |             |                         |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE <sup>(1)</sup> | TOIE       | INTE        | RBIE                    | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h, 181h             | OPTION | RBPU   | INTEDG              | T0CS       | T0SE        | PSA                     | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | —      | _                   | PORTA Data | Direction F | Register <sup>(1)</sup> |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

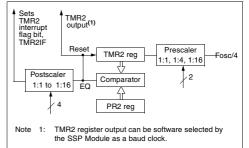

# 9.0 TIMER2 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer2 is an 8-bit timer with a prescaler and a postscaler. It is especially suitable as PWM time-base for PWM mode of CCP module(s). TMR2 is a readable and writable register, and is cleared on any device reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of the TMR2 register goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling, inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

The Timer2 module can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register. T2CON is cleared upon reset which initializes Timer2 as shut off with the prescaler and postscaler at a 1:1 value.

#### 9.1 Timer2 Prescaler and Postscaler

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- · a write to the T2CON register

- any device reset (POR, BOR, MCLR Reset, or WDT Reset).

TMR2 is not cleared when T2CON is written.

#### 9.2 Output of TMR2

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0            | R/W-0                                                        | R/W-0                              | R/W-0      | R/W-0        | R/W-0         | R/W-0   | R/W-0   |                                                                                       |

|----------------|--------------------------------------------------------------|------------------------------------|------------|--------------|---------------|---------|---------|---------------------------------------------------------------------------------------|

| _              | TOUTPS3                                                      | TOUTPS2                            | TOUTPS1    | TOUTPS0      | TMR2ON        | T2CKPS1 | T2CKPS0 | R = Readable bit                                                                      |

| bit7<br>bit 7: | Unimplem                                                     | <b>ented</b> : Rea                 | ud as '0'  |              |               |         | bit0    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 6-3:       |                                                              | TOUTPS0:<br>postscale<br>postscale | Timer2 Ou  | itput Postsc | ale Select bi | ts      |         |                                                                                       |

| bit 2:         | <b>TMR2ON</b> :<br>1 = Timer2<br>0 = Timer2                  | is on                              | bit        |              |               |         |         |                                                                                       |

| bit 1-0:       | <b>T2CKPS1:</b><br>00 = 1:1 pr<br>01 = 1:4 pr<br>1x = 1:16 p | escale<br>rescale                  | Timer2 Clo | ock Prescale | e Select bits |         |         |                                                                                       |

### FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                      | R/W-0          | R/W-0        | R/W-0           | R/W-0       | R/W-0                        |                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|--------------|-----------------|-------------|------------------------------|---------------------------------------------------------------------|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SSPEN                      | CKP            | SSPM3        | SSPM2           | SSPM1       | SSPM0                        | R = Readable bit                                                    |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             | bit0                         | W = Writable bit<br>U = Unimplemented bit, read                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | as '0'                                                              |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | - n =Value at POR reset                                             |

| bit 7:   | WCOL: W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rite Collisio              | on Detect      | bit          |                 |             |                              | <u>.</u>                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                | ritten while | e it is still t | ransmitting | the previo                   | us word                                                             |

|          | (must be c<br>0 = No col                                                                                                                                                                                                                                                                                                                                                                                                                                                         | leared in s                | oftware)       |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              |                                                                     |

| bit 6:   | SSPOV: R                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            | erriow Dei     | IECT DIT     |                 |             |                              |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | الماريد اممريا |              |                 |             | والمراجع والمراجع            |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             |                              | evious data. In case of overflow,<br>e. The user must read the SSP- |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | 0              |              |                 | ,           |                              | mode the overflow bit is not set                                    |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | ption (and     | l transmiss  | sion) is init   | iated by w  | riting to the                | SSPBUF register.                                                    |

|          | 0 = No over                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |                |              |                 |             |                              |                                                                     |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = A byte<br>in transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              | us byte. SSPOV is a "don't care"                                    |

|          | 0 = No ove                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | r Ov mus       | t De cleate  | su in sonw      |             | er moue.                     |                                                                     |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vnchronou                  | s Serial F     | ort Enable   | e bit           |             |                              |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | ort and co     | nfigures S   | CK, SDO,        | and SDI a   | s serial por                 | t pins                                                              |

|          | 0 = Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es serial p                | ort and co     | onfigures th | nese pins       | as I/O port | pins                         |                                                                     |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = Enable<br>0 = Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              | ial port pins                                                       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                | •            | •               | •           | •                            | s input or output.                                                  |

| bit 4:   | CKP: Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             | <u>9</u>                     |                                                                     |

|          | In SPI mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ,                          |                |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | k is a higł    | n level. Tra | nsmit hap       | pens on fa  | lling edge,                  | receive on rising edge.                                             |

|          | 0 = Idle sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ate for cloc               | k is a low     | level. Trar  | nsmit happ      | ens on ris  | ing edge, re                 | eceive on falling edge.                                             |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                |              |                 |             |                              |                                                                     |

|          | SCK relea                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                |              |                 |             |                              |                                                                     |

|          | 1 = Enable<br>0 = Holds                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | clock stra     | tch) (Llead  | to onsure       | data satu   | n tima)                      |                                                                     |

| hit 2 0. | SSPM3:S                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |                | , ,          |                 |             | P ane)                       |                                                                     |

| DII 3-0. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                |                |              |                 | elect bits  |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                | ,              |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                | ,              |              |                 |             |                              |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI master n                |                |              |                 | ontrol one  | blod                         |                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PI slave mo<br>PI slave mo |                |              |                 |             |                              | an be used as I/O pin.                                              |

|          | 0110 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 0101 = 01000 = 00000000 | C slave mo                 | de, 7-bit a    | address      |                 |             |                              |                                                                     |

|          | $0111 = I^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C slave mo                 | de, 10-bit     | address      |                 |             |                              |                                                                     |

|          | $1011 =  ^{2}($                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C firmware                 | controlled     | d Master N   | lode (slav      | e idle)     |                              | b.ld                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                |              |                 |             | interrupts e<br>t interrupts |                                                                     |

|          | 1111 - I (                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 Slave 110                |                | auuress V    | viui stait d    | na stop bli | interrupts                   | enabled                                                             |

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                 | Name    | Bit 7                | Bit 6                                                                      | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|-------------------------|---------|----------------------|----------------------------------------------------------------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                                                       | TOIE                   | INTE       | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                     | PIR1    | PSPIF <sup>(1)</sup> | PSPIF <sup>(1)</sup> <sup>(2)</sup> RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF 0 |                        |            |            |          |        |        |                         | 0000 0000                 |

| 8Ch                     | PIE1    | PSPIE <sup>(1)</sup> | (2)                                                                        | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                     | SSPBUF  | Synchrono            | us Serial                                                                  | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                     | SSPADD  | Synchrono            | us Serial                                                                  | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                     | SSPCON  | WCOL                 | SSPOV                                                                      | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                     | SSPSTAT | SMP <sup>(3)</sup>   | CKE <sup>(3)</sup>                                                         | D/A                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                     | TRISC   | PORTC Da             | ita Directi                                                                | on registe             | er         |            |          |        |        | 1111 1111               | 1111 1111                 |

#### TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16C66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

3: The SMP and CKE bits are implemented on the PIC16C66/67 only. All other PIC16C6X devices have these two bits unimplemented, read as '0'.

| BTFSS             | Bit Test f                                                                                                                                                  | , Skip if S               | Set                       |                  | _ | CALL              | Call Sub                               | routine                                              |                                        |                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------------------|---|-------------------|----------------------------------------|------------------------------------------------------|----------------------------------------|-------------------------------|

| Syntax:           | [ <i>label</i> ] BT                                                                                                                                         | FSS f,b                   |                           |                  |   | Syntax:           | [ label ]                              | CALL k                                               |                                        |                               |

| Operands:         | $0 \leq f \leq 12$                                                                                                                                          | 7                         |                           |                  |   | Operands:         | $0 \le k \le 2$                        | 047                                                  |                                        |                               |

| _                 | 0 ≤ b < 7                                                                                                                                                   |                           |                           |                  |   | Operation:        | (PC)+ 1-                               | ,                                                    |                                        |                               |

| Operation:        | skip if (f <l< td=""><td>b&gt;) = 1</td><td></td><td></td><td></td><td></td><td><math>k \rightarrow PC &lt;</math></td><td>,</td><td></td><td>44.</td></l<> | b>) = 1                   |                           |                  |   |                   | $k \rightarrow PC <$                   | ,                                                    |                                        | 44.                           |

| Status Affected:  | None                                                                                                                                                        |                           | 1                         |                  | 7 | o                 | (PCLATH                                | 1<4:3>) -                                            | > PG<12:                               | 11>                           |

| Encoding:         | 01                                                                                                                                                          | 11bb                      | bfff                      | ffff             |   | Status Affected:  | None                                   | 1                                                    |                                        | ·                             |

| Description:      | If bit 'b' in r<br>instruction                                                                                                                              |                           |                           | ne next          |   | Encoding:         | 10                                     | 0kkk                                                 | kkkk                                   | kkkk                          |

|                   | If bit 'b' is '<br>discarded<br>instead, m                                                                                                                  | 1', then the<br>and a NOF | e next instr<br>s execute | əd               |   | Description:      | (PC+1) is<br>eleven bit<br>into PC bit | putine. Firs<br>pushed on<br>immediate<br>ts <10:0>. | to the stac<br>address is<br>The upper | k. The<br>s loaded<br>bits of |

| Words:            | 1                                                                                                                                                           |                           |                           |                  |   |                   | the PC are<br>is a two cy              |                                                      |                                        | H. CALL                       |

| Cycles:           | 1(2)                                                                                                                                                        |                           |                           |                  |   | Words:            | 1                                      |                                                      |                                        |                               |

| Q Cycle Activity: | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | - | Cycles:           | 2                                      |                                                      |                                        |                               |

|                   | Decode                                                                                                                                                      | Read<br>register 'f'      | Process<br>data           | No-<br>Operation |   | Q Cycle Activity: | Q1                                     | Q2                                                   | Q3                                     | Q4                            |

| If Skip:          | (2nd Cyc                                                                                                                                                    | le)                       |                           |                  |   | 1st Cycle         | Decode                                 | Read<br>literal 'k',                                 | Process<br>data                        | Write to<br>PC                |

| ·                 | Q1                                                                                                                                                          | Q2                        | Q3                        | Q4               | 7 |                   |                                        | Push PC<br>to Stack                                  | uulu                                   | 10                            |

|                   | No-<br>Operation                                                                                                                                            | No-<br>Operation          | No-<br>Operation          | No-<br>Operation |   | 2nd Cycle         | No-<br>Operation                       | No-<br>Operation                                     | No-<br>Operation                       | No-<br>Operation              |