Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62a-20i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)         | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2К                         | —                          | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2К                         | —                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _              | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | —                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz)      | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory<br>(x14 words)          | 2К                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | —                      | 2К                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

## 2.0 PIC16C6X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C6X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C6X family of devices, there are four device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**64. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC64. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**64. These devices have ROM program memory and operate over the standard voltage range.

- 4. LCR, as in PIC16LCR64. These devices have ROM program memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C6X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

ROM devices do not allow serialization information in the program memory space. The user may have this information programmed in the data memory space.

For information on submitting ROM code, please contact your regional sales office.

## 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

| Pin Name          | DIP<br>Pin#     | SOIC<br>Pin#      | Pin Type | Buffer<br>Type                   | Description                                                                                                                                                                                                   |

|-------------------|-----------------|-------------------|----------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 16              | 16                | I        | ST/CMOS(1)                       | Oscillator crystal input/external clock source input.                                                                                                                                                         |

| OSC2/CLKOUT       | 15              | 15                | 0        | _                                | Oscillator crystal output. Connects to crystal or resonator in crystal<br>oscillator mode. In RC mode, the pin outputs CLKOUT which has<br>1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP          | 4               | 4                 | I/P      | ST                               | Master clear reset input or programming voltage input. This pin is an active low reset to the device.                                                                                                         |

|                   |                 |                   |          |                                  | PORTA is a bi-directional I/O port.                                                                                                                                                                           |

| RA0               | 17              | 17                | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA1               | 18              | 18                | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA2               | 1               | 1                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA3               | 2               | 2                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RA4/T0CKI         | 3               | 3                 | I/O      | ST                               | RA4 can also be the clock input to the Timer0 timer/counter.<br>Output is open drain type.                                                                                                                    |

|                   |                 |                   |          |                                  | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT           | 6               | 6                 | I/O      | TTL/ST <sup>(2)</sup>            | RB0 can also be the external interrupt pin.                                                                                                                                                                   |

| RB1               | 7               | 7                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB2               | 8               | 8                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB3               | 9               | 9                 | I/O      | TTL                              |                                                                                                                                                                                                               |

| RB4               | 10              | 10                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                      |

| RB5               | 11              | 11                | I/O      | TTL                              | Interrupt on change pin.                                                                                                                                                                                      |

| RB6               | 12              | 12                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming clock.                                                                                                                                                            |

| RB7               | 13              | 13                | I/O      | TTL/ST <sup>(3)</sup>            | Interrupt on change pin. Serial programming data.                                                                                                                                                             |

| Vss               | 5               | 5                 | Р        | -                                | Ground reference for logic and I/O pins.                                                                                                                                                                      |

| Vdd               | 14              | 14                | Р        | _                                | Positive supply for logic and I/O pins.                                                                                                                                                                       |

| Legend: I = input | 0 = ou<br>— = N | utput<br>lot used |          | ) = input/outpu<br>L = TTL input |                                                                                                                                                                                                               |

#### **PIC16C61 PINOUT DESCRIPTION TABLE 3-1:**

Note

1:

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

2:

This buffer is a Schmitt Trigger input when configured as the external interrupt.

Configured as the external interrup

3: This buffer is a Schmitt Trigger input when used in serial programming mode.

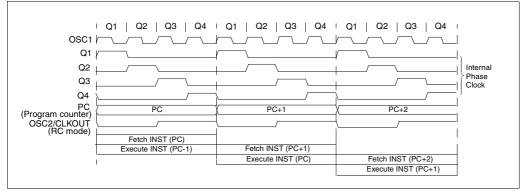

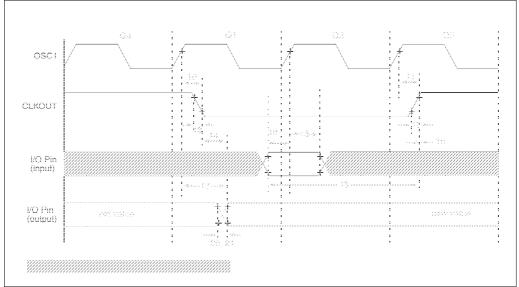

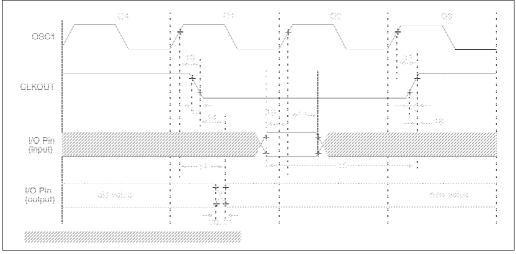

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

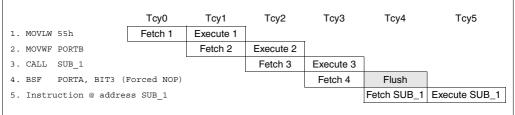

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

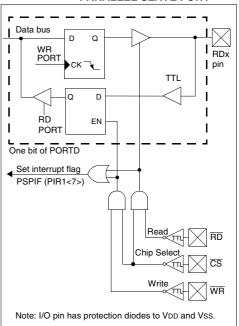

### 5.7 Parallel Slave Port

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD operates as an 8-bit wide parallel slave port (microprocessor port) when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input (RE0/ $\overline{\text{RD}}$ ) and  $\overline{\text{WR}}$  control input pin (RE1/ $\overline{\text{WR}}$ ).

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$  lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-11: PORTD AND PORTE AS A PARALLEL SLAVE PORT

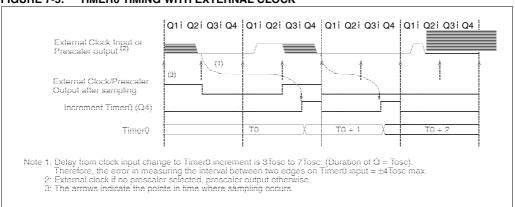

#### 7.2 Using Timer0 with External Clock

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

NOTES:

-

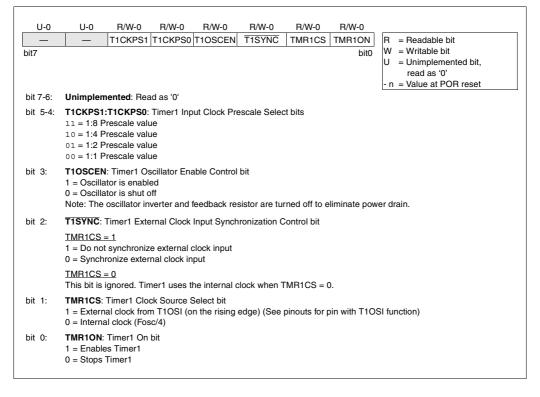

## 8.0 TIMER1 MODULE

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Timer1 is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. Register TMR1 (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by clock select bit, TMR1CS (T1CON<1>) (Figure 8-2).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by CCP1 or CCP2 (Capture/Compare/ PWM) module. See Section 10.0 for details. Figure 8-1 shows the Timer1 control register.

For the PIC16C62A/R62/63/R63/64A/R64/65A/R65/ R66/67, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1 and RC0 pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C62/64/65, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1 pin becomes an input, however the RC0 pin will have to be configured as an input by setting the TRISC<0> bit.

The Timer1 module also has a software programmable prescaler.

#### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

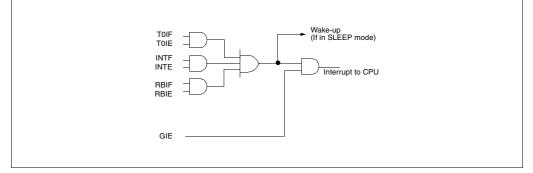

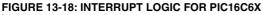

## FIGURE 13-17: INTERRUPT LOGIC FOR PIC16C61

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|-------|--------|--------|--------|--------|

| PIC16C62  | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C62A | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16CR62 | Yes  | Yes  | Yes  | -     | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C63  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR63 | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64A | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C64  | Yes  | Yes  | Yes  | Yes   | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C65  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C65A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16CR65 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C66  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C67  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| RLF               | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RRF               | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:           | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operation:        | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status Affected:  | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Encoding:         | 00 1101 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | Decode Read register 'f' Vite to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | Decode Read register data Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example           | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Example           | RRF REG1,0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -           After Instruction         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td></td> <td>Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -&lt;</td> |                   | Before Instruction         REG1         =         1110         0110           C         =         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -< |

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

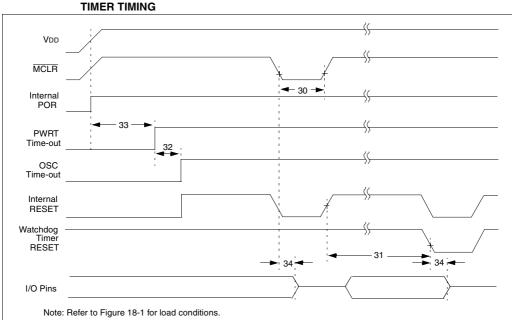

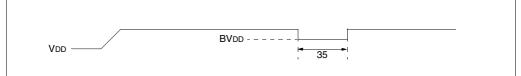

## FIGURE 15-3: CLKOUT AND I/O TIMING

#### **CLKOUT AND I/O TIMING REQUIREMENTS TABLE 15-3:**

| Parameter<br>No. | Sym      | Characteristic                                            |                   | Min          | Тур† | Max         | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|-------------------|--------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1↑ to CLKOUT↓                                          |                   | —            | 15   | 30          | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1↑ to CLKOUT↑                                          |                   | _            | 15   | 30          | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                          |                   | _            | 5    | 15          | ns    | Note 1     |