Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c63-04e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

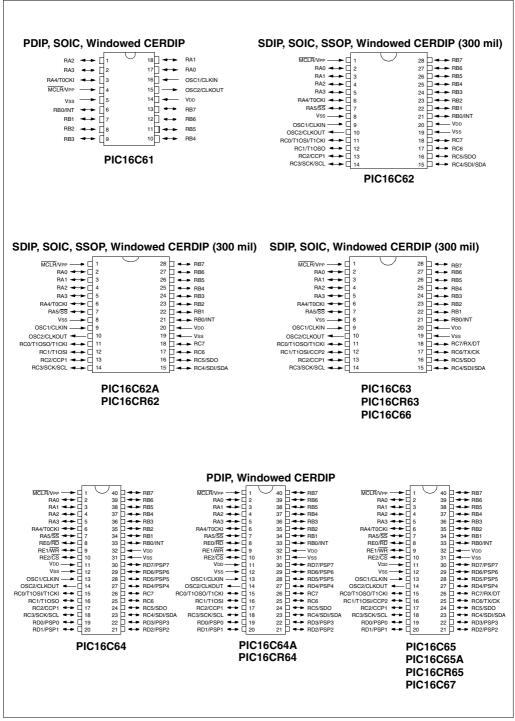

#### **Pin Diagrams**

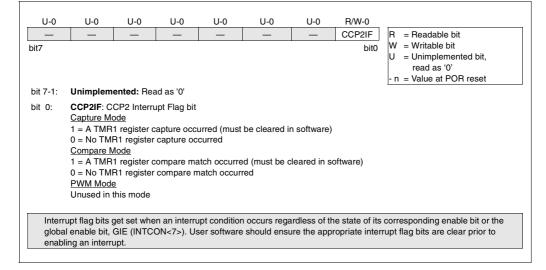

#### 4.2.2.7 PIR2 REGISTER

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-21: PIR2 REGISTER (ADDRESS 0Dh)

#### TABLE 5-1: PORTA FUNCTIONS

| Name       | Bit# | Buffer Type | Function                                                                       |

|------------|------|-------------|--------------------------------------------------------------------------------|

| RA0        | bit0 | TTL         | Input/output                                                                   |

| RA1        | bit1 | TTL         | Input/output                                                                   |

| RA2        | bit2 | TTL         | Input/output                                                                   |

| RA3        | bit3 | TTL         | Input/output                                                                   |

| RA4/T0CKI  | bit4 | ST          | Input/output or external clock input for Timer0.<br>Output is open drain type. |

| RA5/SS (1) | bit5 | TTL         | Input/output or slave select input for synchronous serial port.                |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C61 does not have PORTA<5> or TRISA<5>, read as '0'.

#### TABLE 5-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5              | Bit 4        | Bit 3                  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|--------------------|--------------|------------------------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA | —     | —     | RA5 <sup>(1)</sup> | RA4          | RA3                    | RA2   | RA1   | RA0   | xx xxxx                  | uu uuuu                   |

| 85h     | TRISA | —     | —     | PORTA Data         | Direction Re | egister <sup>(1)</sup> |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5> and TRISA<5> are not implemented on the PIC16C61, read as '0'.

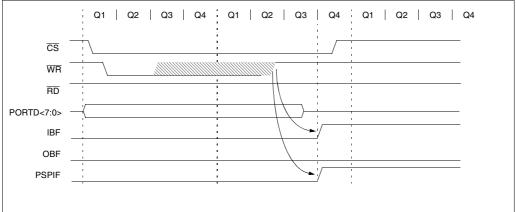

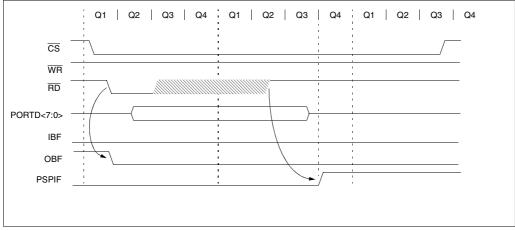

#### FIGURE 5-12: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### TABLE 5-13: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name  | Bit 7 | Bit 6 | Bit 5               | Bit 4               | Bit 3 | Bit 2 Bit 1 Bit 0 |               | Value on:<br>POR,<br>BOR | Value on all other resets |           |

|---------|-------|-------|-------|---------------------|---------------------|-------|-------------------|---------------|--------------------------|---------------------------|-----------|

| 08h     | PORTD | PSP7  | PSP6  | PSP5                | PSP4                | PSP3  | PSP2              | PSP1          | PSP0                     | xxxx xxxx                 | uuuu uuuu |

| 09h     | PORTE | _     |       |                     | _                   | _     | RE2               | RE1           | RE0                      | xxx                       | uuu       |

| 89h     | TRISE | IBF   | OBF   | IBOV                | PSPMODE             | _     | PORTE Da          | ata Directior | n Bits                   | 0000 -111                 | 0000 -111 |

| 0Ch     | PIR1  | PSPIF | (1)   | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF | CCP1IF            | TMR2IF        | TRM1IF                   | 0000 0000                 | 0000 0000 |

| 8Ch     | PIE1  | PSPIE | (1)   | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE | CCP1IE            | TMR2IE        | TMR1IE                   | 0000 0000                 | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by the PSP.

Note 1: These bits are reserved, always maintain these bits clear.

2: These bits are implemented on the PIC16C65/65A/R65/67 only.

### FIGURE 11-27: OPERATION OF THE I<sup>2</sup>C MODULE IN IDLE\_MODE, RCV\_MODE OR XMIT\_MODE

| DLE_MODE (7-bit):                                     |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---|--|

| if (Addr_match)                                       | { 5                                                                                                                                                                                | Set interrupt;                                                                                                                                                                                           |                                                                      |   |  |

|                                                       |                                                                                                                                                                                    | f (R/W = 1)                                                                                                                                                                                              | Send $\overline{ACK} = 0;$                                           |   |  |

|                                                       |                                                                                                                                                                                    | (1011 – 1)                                                                                                                                                                                               | set XMIT_MODE                                                        |   |  |

|                                                       |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      | , |  |

|                                                       |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       | e                                                                                                                                                                                  | else if $(R/W = 0)$                                                                                                                                                                                      | set RCV_MODE;                                                        |   |  |

|                                                       | }                                                                                                                                                                                  |                                                                                                                                                                                                          |                                                                      |   |  |

| RCV_MODE:                                             |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| if ((SSPBUF=Full) OR (SSF                             | POV = 1))                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                      |   |  |

| { Set SSF                                             | POV;                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                      |   |  |

| Do not a                                              | acknowledge;                                                                                                                                                                       |                                                                                                                                                                                                          |                                                                      |   |  |

| }                                                     | -                                                                                                                                                                                  |                                                                                                                                                                                                          |                                                                      |   |  |

| else { transfer                                       | $r SSPSR \rightarrow SSPI$                                                                                                                                                         | BUF:                                                                                                                                                                                                     |                                                                      |   |  |

| send AC                                               |                                                                                                                                                                                    | - ,                                                                                                                                                                                                      |                                                                      |   |  |

| }                                                     |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| Receive 8-bits in SSPSR;                              |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| Set interrupt;                                        |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| XMIT_MODE:                                            |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| While ((SSPBUF = Empty)                               | AND (CKP=0)) H                                                                                                                                                                     | old SCL LOW;                                                                                                                                                                                             |                                                                      |   |  |

| Send byte;                                            |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| Set interrupt;                                        |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| if (ACK Received = 1)                                 |                                                                                                                                                                                    | End of transmiss                                                                                                                                                                                         | ,                                                                    |   |  |

|                                                       | (                                                                                                                                                                                  | Go back to IDLE                                                                                                                                                                                          | _MODE;                                                               |   |  |

|                                                       | }                                                                                                                                                                                  |                                                                                                                                                                                                          |                                                                      |   |  |

| else if ( ACK Received = 0)                           | Go back to XM                                                                                                                                                                      | T_MODE;                                                                                                                                                                                                  |                                                                      |   |  |

| IDLE_MODE (10-Bit):                                   |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

| If (High_byte_addr_match /                            | AND (R/W = 0))                                                                                                                                                                     |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       | _ADDR_MATCH                                                                                                                                                                        | = FALSE:                                                                                                                                                                                                 |                                                                      |   |  |

| Set inter                                             |                                                                                                                                                                                    | - ,                                                                                                                                                                                                      |                                                                      |   |  |

|                                                       | BUF = Full) OR (                                                                                                                                                                   |                                                                                                                                                                                                          |                                                                      |   |  |

| 1 ((001                                               |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       |                                                                                                                                                                                    |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       | { Set SSF                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                      |   |  |

|                                                       |                                                                                                                                                                                    | cknowledge;                                                                                                                                                                                              |                                                                      |   |  |

|                                                       | Do not a                                                                                                                                                                           | cknowledge;                                                                                                                                                                                              |                                                                      |   |  |

|                                                       | Do not a<br>}<br>{ Set UA =                                                                                                                                                        | cknowledge;                                                                                                                                                                                              |                                                                      |   |  |

|                                                       | Do not a<br>}<br>{ Set UA =<br>Send AC                                                                                                                                             | cknowledge;<br>1;<br>$\overline{K} = 0;$                                                                                                                                                                 |                                                                      |   |  |

|                                                       | Do not a<br>}<br>{ Set UA =<br>Send AC<br>While (S                                                                                                                                 | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda                                                                                                                                                            | ted) Hold SCL low;                                                   |   |  |

|                                                       | Do not a<br>}<br>{ Set UA =<br>Send AC                                                                                                                                             | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda                                                                                                                                                            | ted) Hold SCL low;                                                   |   |  |

|                                                       | Do not at<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA                                                                                                                    | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda                                                                                                                                                            | ted) Hold SCL low;                                                   |   |  |

|                                                       | Do not at<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA                                                                                                                    | t;                                                                                                                                                                                                       | ted) Hold SCL low;                                                   |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive                                                                                                         | cknowledge;<br>1;<br>$\overline{K} = 0;$<br>SPADD not upda<br>x = 0;<br>Low_addr_byte;<br>rupt;                                                                                                          | ted) Hold SCL low;                                                   |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =                                                                               | cknowledge;<br>1;<br>$\overline{K} = 0;$<br>SPADD not upda<br>x = 0;<br>Low_addr_byte;<br>rupt;<br>1;                                                                                                    |                                                                      |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | <pre>cknowledge;<br/>1;<br/>K = 0;<br/>SPADD not upda<br/>= 0;<br/>Low_addr_byte;<br/>upt;<br/>1;<br/>yyte_addr_matcl</pre>                                                                              | )                                                                    |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =                                                                               | <pre>cknowledge;<br/>1;<br/>K = 0;<br/>SPADD not upda<br/>= 0;<br/>Low_addr_byte;<br/>upt;<br/>1;<br/>yte_addr_matcl<br/>PRIOR_</pre>                                                                    | )<br>ADDR_MATCH = TRUE;                                              |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>ytle_addr_matcl<br>PRIOR_<br>Send AC                                                                            | )<br>ADDR_MATCH = TRUE;<br>$\vec{K} = 0;$                            |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (Si                                                               | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol         |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S<br>Clear UA                                                    | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S<br>Clear UA                                                    | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol         |   |  |

|                                                       | Do not ar<br>}<br>{ Set UA =<br>Send ĀC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                  | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (Si<br>Clear UA<br>Set RCV                                        | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else                                                  | <pre>Do not ar } { Set UA = Send AC While (S Clear UA Receive Set inter Set UA = If (Low_t { } } }</pre>                                                                           | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (Si<br>Clear UA<br>Set RCV                                        | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else                                                  | }<br>Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t                                                                                 | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (Si<br>Clear UA<br>Set RCV                                        | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else                                                  | <pre>Do not a } { Set UA = Send AC While (S Clear UA Receive Set inter Set UA = If (Low_t } } }</pre>                                                                              | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>byte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S<br>Clear UA<br>Set RCV                                         | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma               | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>}<br>}<br>atch AND (R/W =                                     | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>yte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S:<br>Clear U/<br>Set RCV<br>1)                                  | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma               | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>}<br>}<br>atch AND (R/W =                                     | cknowledge;<br>1;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>yte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S:<br>Clear U/<br>Set RCV<br>1)                                  | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>{<br>}<br>}<br>atch AND (R/W =                                | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>vyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S:<br>Clear UA<br>Set RCV<br>1)<br>1)                           | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>{<br>atch AND (R/W =<br>R_ADDR_MATCH<br>{ send AC             | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>vyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S;<br>Clear UA<br>Set RCV<br>1)<br>T)<br>H)                     | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>{<br>}<br>}<br>atch AND (R/W =                                | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>vyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S;<br>Clear UA<br>Set RCV<br>1)<br>T)<br>H)                     | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>{<br>atch AND (R/W =<br>R_ADDR_MATCH<br>{ send AC             | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>vyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S;<br>Clear UA<br>Set RCV<br>1)<br>T)<br>H)                     | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>                                                              | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>pyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S;<br>Clear UA<br>Set RCV<br>1)<br>T)<br>H)<br>K = 0;<br>_MODE; | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

| else<br>}<br>else if (High_byte_addr_ma<br>{ if (PRIO | Do not ar<br>}<br>{ Set UA =<br>Send AC<br>While (S<br>Clear UA<br>Receive<br>Set intern<br>Set UA =<br>If (Low_t<br>{<br>atch AND (R/W =<br>R_ADDR_MATC:<br>{ send AC<br>set XMIT | cknowledge;<br>T;<br>K = 0;<br>SPADD not upda;<br>= 0;<br>Low_addr_byte;<br>upt;<br>1;<br>pyte_addr_matcl<br>PRIOR_<br>Send AC<br>while (S;<br>Clear UA<br>Set RCV<br>1)<br>T)<br>H)<br>K = 0;<br>_MODE; | )<br>ADDR_MATCH = TRUE;<br>K = 0;<br>\$PADD not updated) Hol<br>= 0; |   |  |

#### 12.1.1 SAMPLING

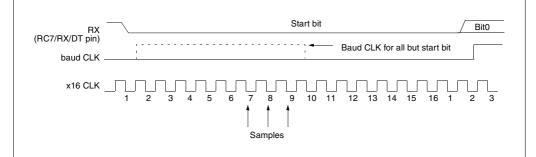

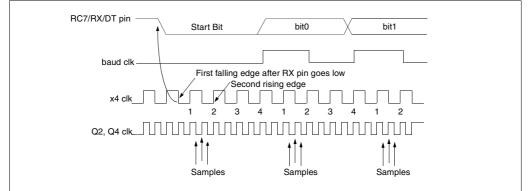

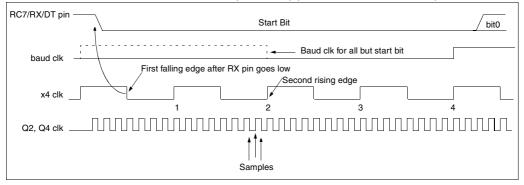

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

#### FIGURE 12-3: RX PIN SAMPLING SCHEME (BRGH = 0) PIC16C63/R63/65/65A/R65)

#### FIGURE 12-4: RX PIN SAMPLING SCHEME (BRGH = 1) (PIC16C63/R63/65/65A/R65)

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | (2)       | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x               | x00- 0000                       |

| 19h     | TXREG                                  | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | (2)       | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        |                         | 0000 0000                       |

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

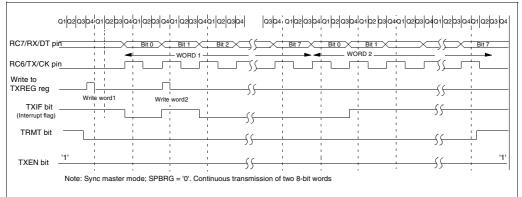

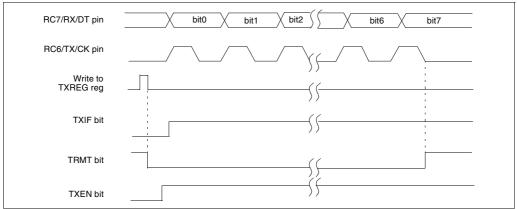

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

#### FIGURE 12-13: SYNCHRONOUS TRANSMISSION THROUGH TXEN

#### 13.2 Oscillator Configurations

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 13.2.1 OSCILLATOR TYPES

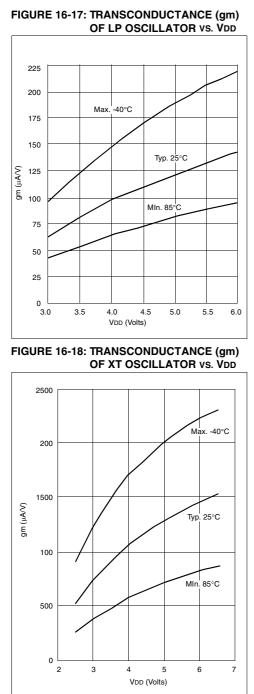

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

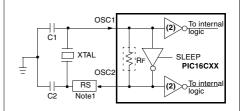

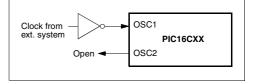

- 13.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In LP, XT, or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 13-4). The PIC16CXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in LP, XT, or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 13-5).

#### FIGURE 13-4: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

See Table 13-1, Table 13-3, Table 13-2 and Table 13-4 for recommended values of C1 and C2.

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: For the PIC16C61 the buffer is on the OSC2 pin, all other devices have the buffer on the OSC1 pin.

#### FIGURE 13-5: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

| Register |    |    |     |     |    | Appli | cab | le De | vices | 3  |     |     |    |    | Power-on Reset<br>Brown-out<br>Reset | MCLR Reset during:<br>– normal operation<br>– SLEEP<br>WDT Reset | Wake-up via<br>interrupt or<br>WDT Wake-up |

|----------|----|----|-----|-----|----|-------|-----|-------|-------|----|-----|-----|----|----|--------------------------------------|------------------------------------------------------------------|--------------------------------------------|

| W        | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| INDF     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | N/A                                  | N/A                                                              | N/A                                        |

| TMR0     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | XXXX XXXX                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| PCL      | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000h                                | 0000h                                                            | PC + 1(2)                                  |

| STATUS   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0001 1xxx                            | 000q quuu <b>(3)</b>                                             | uuuq quuu(3)                               |

| FSR      | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

|          | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | x xxxx                               | u uuuu                                                           | u uuuu                                     |

| PORTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xx xxxx                              | uu uuuu                                                          | uu uuuu                                    |

| PORTB    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| PORTC    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| PORTD    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| PORTE    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxx                                  | uuu                                                              | uuu                                        |

| PCLATH   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0 0000                               | 0 0000                                                           | u uuuu                                     |

| INTCON   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 000x                            | 0000 000u                                                        | uuuu uuuu <b>(1)</b>                       |

| PIR1     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 000 0000                             | 00 0000                                                          | uu uuuu <b>(1)</b>                         |

|          | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu <b>(1)</b>                       |

| PIR2     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0                                    | 0                                                                | u(2)                                       |

| TMR1L    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| TMR1H    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| T1CON    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 0000                              | uu uuuu                                                          | uu uuuu                                    |

| TMR2     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu                                  |

| T2CON    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | -000 0000                            | -000 0000                                                        | -uuu uuuu                                  |

| SSPBUF   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| SSPCON   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu                                  |

| CCPR1L   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| CCPR1H   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| CCP1CON  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 0000                              | 00 0000                                                          | uu uuuu                                    |

| RCSTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 -00x                            | 0000 -00x                                                        | uuuu -uuu                                  |

| TXREG    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu                                  |

| RCREG    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu                                  |

| CCPR2L   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| CCPR2H   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | xxxx xxxx                            | uuuu uuuu                                                        | uuuu uuuu                                  |

| CCP2CON  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                        | uuuu uuuu                                  |

| OPTION   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 1111                            | 1111 1111                                                        | uuuu uuuu                                  |

| TDICA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1 1111                               | 1 1111                                                           | u uuuu                                     |

| TRISA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 11 1111                              | 11 1111                                                          | uu uuuu                                    |

| TRISB    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 1111                            | 1111 1111                                                        | uuuu uuuu                                  |

| TRISC    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 1111                            | 1111 1111                                                        | uuuu uuuu                                  |

TABLE 13-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0', q = value depends on condition.

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

3: See Table 13-10 and Table 13-11 for reset value for specific conditions.

#### 13.6 Context Saving During Interrupts

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 13-1 stores and restores the STATUS and W registers. Example 13-2 stores and restores the STATUS, W, and PCLATH registers (Devices with paged program memory). For all PIC16C6X devices with greater than 1K of program memory (all devices except PIC16C61), the register, W\_TEMP, must be

defined in banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1, 0x120 in bank 2, and 0x1A0 in bank 3).

The examples:

- a) Stores the W register

- b) Stores the STATUS register in bank 0

- c) Stores PCLATH

- d) Executes ISR code

- e) Restores PCLATH

- f) Restores STATUS register (and bank select bit)

- g) Restores W register

#### EXAMPLE 13-1: SAVING STATUS AND W REGISTERS IN RAM (PIC16C61)

| MOVWF<br>SWAPF<br>MOVWF<br>:<br>:(ISR)<br>: | W_TEMP<br>STATUS,W<br>STATUS_TEMP | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W<br>;Save status to bank zero STATUS_TEMP register |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SWAPF                                       | STATUS_TEMP,W                     | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                                                      |

| MOVWF                                       | STATUS                            | ;Move W into STATUS register                                                                                                             |

| SWAPF                                       | W_TEMP,F                          | ;Swap W_TEMP                                                                                                                             |

| SWAPF                                       | W_TEMP,W                          | ;Swap W_TEMP into W                                                                                                                      |

#### EXAMPLE 13-2: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM (ALL OTHER PIC16C6X DEVICES)

| SWAPF<br>CLRF | W_TEMP<br>STATUS,W<br>STATUS | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W<br>;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|---------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF         | STATUS_TEMP                  | ;Save status to bank zero STATUS_TEMP register                                                                                                    |

| MOVF          | PCLATH, W                    | ;Only required if using pages 1, 2 and/or 3                                                                                                       |

| MOVWF         | PCLATH_TEMP                  | ;Save PCLATH into W                                                                                                                               |

| CLRF          | PCLATH                       | ;Page zero, regardless of current page                                                                                                            |

| BCF           | STATUS, IRP                  | ;Return to Bank 0                                                                                                                                 |

| MOVF          | FSR, W                       | ;Copy FSR to W                                                                                                                                    |

| :(ISR)        | FSR_TEMP                     | ;Copy FSR from W to FSR_TEMP                                                                                                                      |

| :<br>MOVF     | PCLATH TEMP, W               | ·Pestore DCLATH                                                                                                                                   |

|               | PCLATH                       | ;Move W into PCLATH                                                                                                                               |

| SWAPF         |                              | ,                                                                                                                                                 |

| MOVWF         | STATUS                       | ;Move W into STATUS register                                                                                                                      |

| SWAPF         | W TEMP,F                     | ;Swap W TEMP                                                                                                                                      |

| SWAPF         | W_TEMP,W                     | ;Swap W_TEMP into W                                                                                                                               |

#### 13.8 Power-down Mode (SLEEP)

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

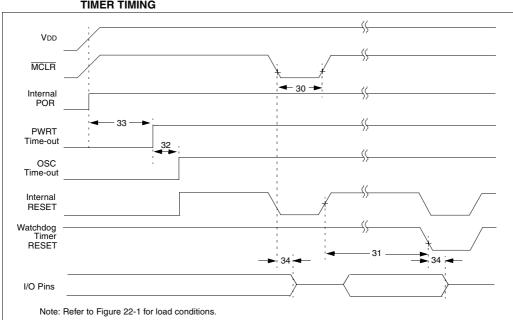

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, status bit  $\overline{PD}$  (STATUS<3>) is cleared, status bit  $\overline{TO}$  (STATUS<4>) is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or VSS, ensure no external circuitry is drawing current from the I/O pin, and disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC).

#### 13.8.1 WAKE-UP FROM SLEEP

The device can wake from SLEEP through one of the following events:

- 1. External reset input on MCLR/VPP pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, RB port change, or some peripheral interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. USART TX or RX (synchronous slave mode).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the subset of the new provide the instruction after the subset (on address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 13.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

#### TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | e    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A  | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

|            | ĸ      |                              | · ·    | 11  | TOTO   | ĸĸĸĸ   | кккк | ~        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

#### Instruction Descriptions 14.1

| Add Lite           | ral and                                                                                                                                                                               | w                                                      |                                                                                                                                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ <i>label</i> ] A | DDLW                                                                                                                                                                                  | k                                                      |                                                                                                                                                                                                                                                |

| $0 \le k \le 25$   | 55                                                                                                                                                                                    |                                                        |                                                                                                                                                                                                                                                |

| (W) + k –          | → (W)                                                                                                                                                                                 |                                                        |                                                                                                                                                                                                                                                |

| C, DC, Z           |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| 11                 | 111x                                                                                                                                                                                  | kkkk                                                   | kkkk                                                                                                                                                                                                                                           |

| added to t         | he eight b                                                                                                                                                                            | it literal 'k'                                         | and the                                                                                                                                                                                                                                        |

| 1                  |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| 1                  |                                                                                                                                                                                       |                                                        |                                                                                                                                                                                                                                                |

| Q1                 | Q2                                                                                                                                                                                    | Q3                                                     | Q4                                                                                                                                                                                                                                             |

| Decode             | Read<br>literal 'k'                                                                                                                                                                   | Process<br>data                                        | Write to<br>W                                                                                                                                                                                                                                  |

| After Inst         | W =<br>ruction                                                                                                                                                                        | 0x10<br>0x25                                           |                                                                                                                                                                                                                                                |

|                    | [ <i>label</i> ] All<br>$0 \le k \le 2\xi$<br>(W) + k -<br>C, DC, Z<br>11<br>The conte<br>added to the<br>result is pl<br>1<br>1<br>Q1<br>Decode<br>ADDLW<br>Before Inn<br>After Inst | $ \begin{array}{l lllllllllllllllllllllllllllllllllll$ | $0 \le k \le 255$ (W) + k → (W) C, DC, Z $11  111x  kkkk$ The contents of the W register added to the eight bit literal 'k' result is placed in the W regist 1 1 2 2 2 2 2 3 2 2 2 3 2 2 3 2 3 2 3 3 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |

| ANDLW             | AND Literal w                                                                                                       | th W      |               |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|-----------|---------------|--|--|--|--|--|

| Syntax:           | [label] ANDLW                                                                                                       |           |               |  |  |  |  |  |

| Operands:         | 0 ≤ k ≤ 255                                                                                                         |           |               |  |  |  |  |  |