Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c63-10i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PIC16C6X FAMILY OF DEVICES

|             |                                                 | PIC16C61       | PIC16C62A                  | PIC16CR62                  | PIC16C63                       | PIC16CR63                     |

|-------------|-------------------------------------------------|----------------|----------------------------|----------------------------|--------------------------------|-------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20             | 20                         | 20                         | 20                             | 20                            |

|             | EPROM Program Memory<br>(x14 words)             | 1K             | 2K                         |                            | 4K                             | _                             |

| Memory      | ROM Program Memory<br>(x14 words)               |                | _                          | 2K                         | _                              | 4K                            |

|             | Data Memory (bytes)                             | 36             | 128                        | 128                        | 192                            | 192                           |

|             | Timer Module(s)                                 | TMR0           | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2        |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _              | 1                          | 1                          | 2                              | 2                             |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) |                | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C<br>USART |

|             | Parallel Slave Port                             | _              | _                          | _                          | _                              | _                             |

|             | Interrupt Sources                               | 3              | 7                          | 7                          | 10                             | 10                            |

|             | I/O Pins                                        | 13             | 22                         | 22                         | 22                             | 22                            |

|             | Voltage Range (Volts)                           | 3.0-6.0        | 2.5-6.0                    | 2.5-6.0                    | 2.5-6.0                        | 2.5-6.0                       |

| Features    | In-Circuit Serial Programming                   | Yes            | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Brown-out Reset                                 | _              | Yes                        | Yes                        | Yes                            | Yes                           |

|             | Packages                                        | 18-pin DIP, SO | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           | 28-pin SDIP,<br>SOIC          |

|             |                                              | PIC16C64A              | PIC16CR64                                 | PIC16C65A                      | PIC16CR65                                       | PIC16C66                       | PIC16C67                                        |

|-------------|----------------------------------------------|------------------------|-------------------------------------------|--------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)         | 20                     | 20                                        | 20                             | 20                                              | 20                             | 20                                              |

|             | EPROM Program Memory (x14 words)             | 2K                     | _                                         | 4K                             | _                                               | 8K                             | 8K                                              |

| Memory      | ROM Program Memory (x14 words)               | _                      | 2K                                        | _                              | 4K                                              | _                              | _                                               |

|             | Data Memory (bytes)                          | 128                    | 128                                       | 192                            | 192                                             | 368                            | 368                                             |

|             | Timer Module(s)                              | TMR0,<br>TMR1,<br>TMR2 | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          | TMR0,<br>TMR1,<br>TMR2         | TMR0,<br>TMR1,<br>TMR2                          |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)           | 1                      | 1                                         | 2                              | 2                                               | 2                              | 2                                               |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, USART) | SPI/I <sup>2</sup> C   | SPI/I <sup>2</sup> C                      | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  | SPI/I <sup>2</sup> C,<br>USART | SPI/I <sup>2</sup> C,<br>USART                  |

|             | Parallel Slave Port                          | Yes                    | Yes                                       | Yes                            | Yes                                             | _                              | Yes                                             |

|             | Interrupt Sources                            | 8                      | 8                                         | 11                             | 11                                              | 10                             | 11                                              |

|             | I/O Pins                                     | 33                     | 33                                        | 33                             | 33                                              | 22                             | 33                                              |

|             | Voltage Range (Volts)                        | 2.5-6.0                | 2.5-6.0                                   | 2.5-6.0                        | 2.5-6.0                                         | 2.5-6.0                        | 2.5-6.0                                         |

|             | In-Circuit Serial Programming                | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

| Features    | Brown-out Reset                              | Yes                    | Yes                                       | Yes                            | Yes                                             | Yes                            | Yes                                             |

|             | Packages                                     |                        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |                                | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP | 28-pin SDIP,<br>SOIC           | 40-pin DIP;<br>44-pin<br>PLCC,<br>MQFP,<br>TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6X Family devices use serial programming with clock pin RB6 and data pin RB7.

NOTES:

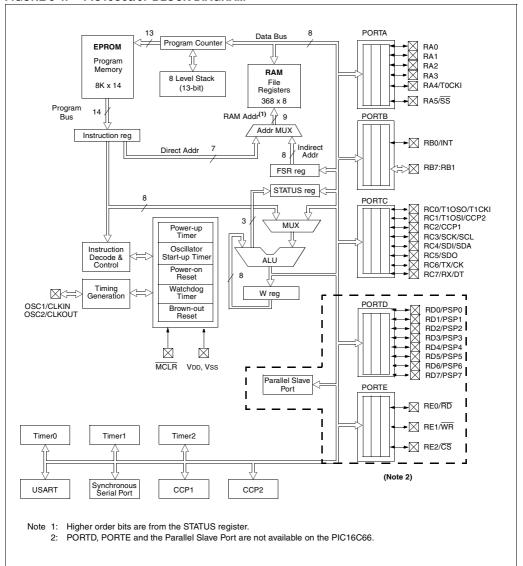

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data may be fetched from the same memory using the same bus. Separating program and data busses further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C61 addresses 1K x 14 of program memory. The PIC16C62/62A/R62/64/64A/R64 address 2K x 14 of program memory, and the PIC16C63/R63/65/65A/R65 devices address 4K x 14 of program memory. The PIC16C66/67 address 8K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of "special optimal situations" makes programming with the PIC16CXX simple yet efficient, thus significantly reducing the learning curve.

The PIC16CXX device contains an 8-bit ALU and working register (W). The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending upon the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. Bits C and DC operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

FIGURE 3-4: PIC16C66/67 BLOCK DIAGRAM

TABLE 4-3: SPECIAL FUNCTION REGISTERS FOR THE PIC16C63/R63 (Cont.'d)

| Address              | Name    | Bit 7              | Bit 6              | Bit 5                     | Bit 4         | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|---------------------------|---------------|--------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 1               |         |                    |                    |                           |               |              |                 |               |           |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter               | nts of FSR to | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU               | INTEDG             | T0CS                      | T0SE          | PSA          | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Sigr                | nificant Byte |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0                       | TO            | PD           | Z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ac        | Idress pointe             | er            |              |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 85h                  | TRISA   | _                  | _                  | PORTA Dat                 | a Direction R | egister      |                 |               |           | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat          | ta Direction F     | Register                  |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da           | ta Direction F     | Register                  |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 88h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 89h                  | _       | Unimpleme          | Unimplemented      |                           |               |              |                 |               | _         | _                        |                                                |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                  | _                  | -                         | Write Buffer  | for the uppe | r 5 bits of the | Program C     | ounter    | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE                      | INTE          | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 8Ch                  | PIE1    | (5)                | (5)                | RCIE                      | TXIE          | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE    | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                  | _                  | _                         | _             | _            | _               | _             | CCP2IE    | 0                        | 0                                              |

| 8Eh                  | PCON    | _                  | _                  | _                         | _             | _            | _               | POR           | BOR       | qq                       | uu                                             |

| 8Fh                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 90h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 91h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 92h                  | PR2     | Timer2 Peri        | iod Register       |                           |               |              |                 |               |           | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou         | us Serial Port     | t (I <sup>2</sup> C mode) | Address Reg   | gister       |                 |               |           | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | _                  | _                  | D/Ā                       | Р             | S            | R/W             | UA            | BF        | 00 0000                  | 00 0000                                        |

| 95h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 96h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 97h                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 98h <sup>(2)</sup>   | TXSTA   | CSRC               | TX9                | TXEN                      | SYNC          | _            | BRGH            | TRMT          | TX9D      | 0000 -010                | 0000 -010                                      |

| 99h <sup>(2)</sup>   | SPBRG   | Baud Rate          | Generator Re       | egister                   |               |              |                 |               |           | 0000 0000                | 0000 0000                                      |

| 9Ah                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 9Bh                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 9Ch                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 9Dh                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 9Eh                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

| 9Fh                  | _       | Unimpleme          | nted               |                           |               |              |                 |               |           | _                        | _                                              |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value depends on condition}, \ \textbf{-} = \textbf{unimplemented location read as '0'}.$

Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

- 3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C63/R63, always maintain these bits clear.

- 5: PIE1<7:6> and PIR1<7:6> are reserved on the PIC16C63/R63, always maintain these bits clear.

#### FIGURE 4-18: PIR1 REGISTER FOR PIC16C64/64A/R64 (ADDRESS 0Ch)

| R/W-0    | R/W-0      | U-0          | U-0              | R/W-0        | R/W-0        | R/W-0        | R/W-0    |                                       |

|----------|------------|--------------|------------------|--------------|--------------|--------------|----------|---------------------------------------|

| PSPIF    | _          | _            | _                | SSPIF        | CCP1IF       | TMR2IF       | TMR1IF   | R = Readable bit                      |

| bit7     |            |              | W = Writable bit |              |              |              |          |                                       |

|          |            |              |                  |              |              |              |          | U = Unimplemented bit,<br>read as '0' |

|          |            |              |                  |              |              |              |          | - n = Value at POR reset              |

| bit 7:   | PSPIF: Par | rallel Slave | Port Interru     | ıpt Flag bit |              |              |          |                                       |

|          |            |              | •                |              | ice (must be | cleared in s | oftware) |                                       |

|          | 0 = No rea | a or write o | peration na      | is taken pia | ce           |              |          |                                       |

| bit 6:   | Reserved:  | Always ma    | intain this l    | oit clear.   |              |              |          |                                       |

| bit 5-4: | Unimplem   | ented: Rea   | ad as '0'        |              |              |              |          |                                       |

0 = Waiting to transmit/receive

Capture Mode

bit 3:

bit 2:

1 = A TMR1 register capture occurred (must be cleared in software)

1 = The transmission/reception is complete (must be cleared in software)

0 = No TMR1 register capture occurred

CCP1IF: CCP1 Interrupt Flag bit

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

SSPIF: Synchronous Serial Port Interrupt Flag bit

PWM Mode

Unused in this mode

bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflow occurred (must be cleared in software)

0 = No TMR1 register occurred

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 4-19: PIR1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 0Ch)

| R/W-0 R/W-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0  PSPIF — RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF  bit7 bit7 bit0  PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place bit 6: Reserved: Always maintain this bit clear. bit 5: RCIF: USART Receive Interrupt Flag bit |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit7 bit0 W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset  bit 7: PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place  bit 6: Reserved: Always maintain this bit clear.  bit 5: RCIF: USART Receive Interrupt Flag bit           |  |

| bit 7: PSPIF: Parallel Slave Port Interrupt Flag bit 1 = A read or a write operation has taken place (must be cleared in software) 0 = No read or write operation has taken place bit 6: Reserved: Always maintain this bit clear. bit 5: RCIF: USART Receive Interrupt Flag bit                                                                                                     |  |

| bit 5: RCIF: USART Receive Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                        |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                    |  |

| <ul><li>1 = The USART receive buffer is full (cleared by reading RCREG)</li><li>0 = The USART receive buffer is empty</li></ul>                                                                                                                                                                                                                                                      |  |

| bit 4: TXIF: USART Transmit Interrupt Flag bit  1 = The USART transmit buffer is empty (cleared by writing to TXREG)  0 = The USART transmit buffer is full                                                                                                                                                                                                                          |  |

| bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit  1 = The transmission/reception is complete (must be cleared in software)  0 = Waiting to transmit/receive                                                                                                                                                                                                                  |  |

| bit 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode  1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode  1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode                                                        |  |

| bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                   |  |

| bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflow occurred (must be cleared in software) 0 = No TMR1 register overflow occurred                                                                                                                                                                                                                             |  |

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# EXAMPLE 10-2: PWM PERIOD AND DUTY CYCLE CALCULATION

Desired PWM frequency is 78.125 kHz, Fosc = 20 MHz

TMR2 prescale = 1

$1/78.125 \text{ kHz} = [(PR2) + 1] \cdot 4 \cdot 1/20 \text{ MHz} \cdot 1$  $12.8 \text{ } \mu\text{s} = [(PR2) + 1] \cdot 4 \cdot 50 \text{ ns} \cdot 1$

PR2 = 63

Find the maximum resolution of the duty cycle that can be used with a 78.125 kHz frequency and 20 MHz oscillator:

$1/78.125 \text{ kHz} = 2^{\text{PWM RESOLUTION}} \cdot 1/20 \text{ MHz} \cdot 1$

12.8 μs =  $2^{\text{PWM RESOLUTION}} \cdot 50 \text{ ns} \cdot 1$

$= 2^{\text{PWM RESOLUTION}}$

log(256) = (PWM Resolution) • log(2)

8.0 = PWM Resolution

At most, an 8-bit resolution duty cycle can be obtained from a 78.125 kHz frequency and a 20 MHz oscillator, i.e.,  $0 \le \text{CCPR1L:CCP1CON} < 5:4 > \le 255$ . Any value greater than 255 will result in a 100% duty cycle.

In order to achieve higher resolution, the PWM frequency must be decreased. In order to achieve higher PWM frequency, the resolution must be decreased.

Table 10-3 lists example PWM frequencies and resolutions for Fosc = 20 MHz. The TMR2 prescaler and PR2 values are also shown.

#### 10.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Set the PWM period by writing to the PR2 register

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

TABLE 10-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

TABLE 10-4: REGISTERS ASSOCIATED WITH TIMER1, CAPTURE AND COMPARE

| Add                  | Name    | Bit 7                | Bit 6                         | Bit 5               | Bit 4               | Bit 3       | Bit 2      | Bit 1       | Bit 0  | PC   | e on:<br>DR,<br>DR | all c | e on<br>other<br>sets |

|----------------------|---------|----------------------|-------------------------------|---------------------|---------------------|-------------|------------|-------------|--------|------|--------------------|-------|-----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                          | TOIE                | INTE                | RBIE        | TOIF       | INTF        | RBIF   | 0000 | 000x               | 0000  | 000u                  |

| 0Ch                  | PIR1    | PSPIF <sup>(2)</sup> | (3)                           | RCIF <sup>(1)</sup> | TXIF <sup>(1)</sup> | SSPIF       | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000               | 0000  | 0000                  |

| 0Dh <sup>(4)</sup>   | PIR2    | _                    | _                             | _                   | _                   | _           | _          | _           | CCP2IF |      | 0                  |       | 0                     |

| 8Ch                  | PIE1    | PSPIE <sup>(2)</sup> | (3)                           | RCIE <sup>(1)</sup> | TXIE <sup>(1)</sup> | SSPIE       | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000               | 0000  | 0000                  |

| 8Dh <sup>(4)</sup>   | PIE2    | _                    | _                             |                     |                     | _           | _          | -           | CCP2IE |      | 0                  |       | 0                     |

| 87h                  | TRISC   | PORTC D              | PORTC Data Direction register |                     |                     |             |            |             |        | 1111 | 1111               | 1111  | 1111                  |

| 0Eh                  | TMR1L   | Holding re           | egister fo                    | r the Least         | Significant         | Byte of the | 16-bit TMI | R1 register | •      | xxxx | xxxx               | uuuu  | uuuu                  |

| 0Fh                  | TMR1H   | Holding re           | egister fo                    | r the Most S        | Significant         | Byte of the | 16-bit TMF | 11 register |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 10h                  | T1CON   | _                    | _                             | T1CKPS1             | T1CKPS0             | T10SCEN     | T1SYNC     | TMR1CS      | TMR10N | 00   | 0000               | uu    | uuuu                  |

| 15h                  | CCPR1L  | Capture/C            | Compare/                      | PWM1 (LS            | B)                  |             |            |             |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 16h                  | CCPR1H  | Capture/C            | Compare/                      | PWM1 (MS            | SB)                 |             |            |             |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 17h                  | CCP1CON | _                    | _                             | CCP1X               | CCP1Y               | CCP1M3      | CCP1M2     | CCP1M1      | CCP1M0 | 00   | 0000               | 00    | 0000                  |

| 1Bh <sup>(4)</sup>   | CCPR2L  | Capture/C            | Compare/                      | PWM2 (LS            | B)                  |             |            |             |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Ch <sup>(4)</sup>   | CCPR2H  | Capture/C            | Compare/                      | PWM2 (MS            | SB)                 |             |            |             |        | xxxx | xxxx               | uuuu  | uuuu                  |

| 1Dh <sup>(4)</sup>   | CCP2CON | _                    | _                             | CCP2X               | CCP2Y               | CCP2M3      | CCP2M2     | CCP2M1      | CCP2M0 | 00   | 0000               | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used in these modes.

- Note 1: These bits are associated with the USART module, which is implemented on the PIC16C63/R63/65/65A/R65/66/67 only.

- 2: Bits PSPIE and PSPIF are reserved on the PIC16C62/62A/R62/63/R63/66, always maintain these bits clear.

- 3: The PIR1<6> and PIE1<6> bits are reserved, always maintain these bits clear.

- 4: These registers are associated with the CCP2 module, which is only implemented on the PIC16C63/R63/65/65A/R65/66/67.

| IORWF             | Inclusive                                                   | OR W                         | with f           |                      |

|-------------------|-------------------------------------------------------------|------------------------------|------------------|----------------------|

| Syntax:           | [ label ]                                                   | IORWF                        | f,d              |                      |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                              | 27                           |                  |                      |

| Operation:        | (W) .OR.                                                    | $(f) \rightarrow (de$        | estination       | 1)                   |

| Status Affected:  | Z                                                           |                              |                  |                      |

| Encoding:         | 0.0                                                         | 0100                         | dfff             | ffff                 |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg | is 0 the re<br>: If 'd' is 1 | sult is plac     | ced in the           |

| Words:            | 1                                                           |                              |                  |                      |

| Cycles:           | 1                                                           |                              |                  |                      |

| Q Cycle Activity: | Q1                                                          | Q2                           | Q3               | Q4                   |

|                   | Decode                                                      | Read<br>register<br>'f'      | Process<br>data  | Write to destination |

| Example           | IORWF                                                       |                              | RESULT,          | 0                    |

|                   | Before In                                                   |                              |                  |                      |

|                   |                                                             | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |

|                   | After Inst                                                  | • •                          | _ 0.891          |                      |

|                   |                                                             | RESULT                       | = 0x13           | 3                    |

0x93

| MOVLW             | Move Lit        | eral to V           | V                            |               |

|-------------------|-----------------|---------------------|------------------------------|---------------|

| Syntax:           | [ label ]       | MOVLW               | / k                          |               |

| Operands:         | $0 \le k \le 2$ | 55                  |                              |               |

| Operation:        | $k\to (W)$      |                     |                              |               |

| Status Affected:  | None            |                     |                              |               |

| Encoding:         | 11              | 00xx                | kkkk                         | kkkk          |

| Description:      |                 |                     | k' is loaded<br>ares will as |               |

| Words:            | 1               |                     |                              |               |

| Cycles:           | 1               |                     |                              |               |

| Q Cycle Activity: | Q1              | Q2                  | Q3                           | Q4            |

|                   | Decode          | Read<br>literal 'k' | Process<br>data              | Write to<br>W |

| Example           | MOVLW           | 0x5A                |                              |               |

|                   | After Inst      |                     |                              |               |

|                   |                 | W =                 | 0x5A                         |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

|                   |                 |                     |                              |               |

| MOVF              | Move f                                                                                                                                                                                                                                                  |                         |                 |                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                               | MOVF                    | f,d             |                      |  |  |  |

| Operands:         | $\begin{aligned} 0 & \leq f \leq 127 \\ d & \in [0,1] \end{aligned}$                                                                                                                                                                                    |                         |                 |                      |  |  |  |

| Operation:        | $(f) \rightarrow (destination)$                                                                                                                                                                                                                         |                         |                 |                      |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Encoding:         | 00 1000 dfff ffff                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flaq Z is affected. |                         |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                      | Q2                      | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                  | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |

| Example           | MOVF                                                                                                                                                                                                                                                    | FSR,                    | 0               |                      |  |  |  |

|                   | After Instruction W = value in FSR register                                                                                                                                                                                                             |                         |                 |                      |  |  |  |

Z = 1

| MOVWF             | Move W                                      | to f                    |                 |                       |  |  |  |

|-------------------|---------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ label ]                                   | MOVWI                   | F f             |                       |  |  |  |

| Operands:         | $0 \leq f \leq 127$                         |                         |                 |                       |  |  |  |

| Operation:        | $(W) \rightarrow (f)$                       |                         |                 |                       |  |  |  |

| Status Affected:  | None                                        |                         |                 |                       |  |  |  |

| Encoding:         | 00                                          | 0000                    | 1fff            | ffff                  |  |  |  |

| Description:      | Move data                                   | from W r                | egister to      | register              |  |  |  |

| Words:            | 1                                           |                         |                 |                       |  |  |  |

| Cycles:           | 1                                           |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                          | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                      | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | MOVWF                                       | OPTIC                   | ON_REG          |                       |  |  |  |

|                   | Before Instruction  OPTION = 0xFF  W = 0x4F |                         |                 |                       |  |  |  |

|                   | After Inst                                  | ruction<br>OPTION       | = 0x4F          | =                     |  |  |  |

W = 0x4F

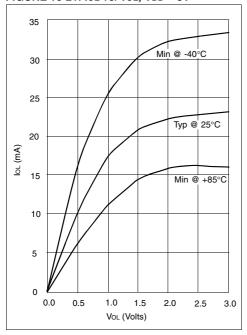

FIGURE 16-21: IOL VS. VOL, VDD = 3V

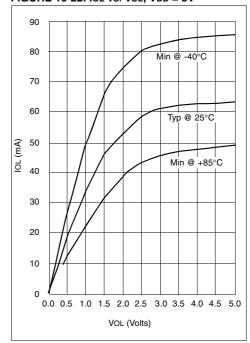

FIGURE 16-22: IOL VS. VOL, VDD = 5V

TABLE 16-2: INPUT CAPACITANCE\*

| Pin Name    | Typical Capa | acitance (pF) |

|-------------|--------------|---------------|

|             | 18L PDIP     | 18L SOIC      |

| RA port     | 5.0          | 4.3           |

| RB port     | 5.0          | 4.3           |

| MCLR        | 17.0         | 17.0          |

| OSC1/CLKIN  | 4.0          | 3.5           |

| OSC2/CLKOUT | 4.3          | 3.5           |

| TOCKI       | 3.2          | 2.8           |

\*All capacitance values are typical at 25°C. A part to part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

### 17.0 ELECTRICAL CHARACTERISTICS FOR PIC16C62/64

#### **Absolute Maximum Ratings †**

| • .                                                                |                      |

|--------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                     | 55°C to +85°C        |

| Storage temperature                                                | -65°C to +150°C      |

| Voltage on any pin with respect to VSS (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +14V           |

| Voltage on RA4 with respect to Vss                                 | 0V to +14V           |

| Total power dissipation (Note 1)                                   |                      |

| Maximum current out of Vss pin                                     |                      |

| Maximum current into VDD pin                                       |                      |

| Input clamp current, lik (VI < 0 or VI > VDD)                      | ±20 mA               |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA, PORTB, and PORTE* (combined)        | 200 mA               |

| Maximum current sourced by PORTA, PORTB, and PORTE* (combined)     | 200 mA               |

| Maximum current sunk by PORTC and PORTD* (combined)                | 200 mA               |

| Maximum current sourced by PORTC and PORTD* (combined)             | 200 mA               |

| * PORTD and PORTE not available on the PIC16C62                    |                      |

<sup>\*</sup> PORTD and PORTE not available on the PIC16C62.

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C62-04<br>PIC16C64-04                                                                                 | PIC16C62-10<br>PIC16C64-10                                                                              | PIC16C62-20<br>PIC16C64-20                                                                              | PIC16LC62-04<br>PIC16LC64-04                                                                              | JW Devices                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V IDD: 3.8 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                      | VDD: 4.5V to 5.5V IDD: 2.0 mA typ. at 5.5V IPD: 1.5 μA typ. at 4V Freq:4 MHz max.                       | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq:4 MHz max.              | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 µA max. at 3V<br>Freq: 4 MHz max.              | VDD: 4.0V to 6.0V<br>IDD: 3.8 mA max. at 5.5V<br>IPD: 21 µA max. at 4V<br>Freq:4 MHz max.              |

| XT  | VDD: 4.0V to 6.0V IDD: 3.8 mA max. at 5.5V IPD: 21 $\mu$ A max. at 4V Freq:4 MHz max.                      | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq:4 MHz max.              | VDD: 4.5V to 5.5V<br>IDD: 2.0 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq:4 MHz max.              | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 4 MHz max.            |                                                                                                        |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq:4 MHz max.              | VDD: $4.5V$ to $5.5V$ IDD: $15$ mA max. at $5.5V$ IPD: $1.5$ $\mu$ A typ. at $4.5V$ Freq: $10$ MHz max. | VDD: $4.5V$ to $5.5V$ IDD: $30$ mA max. at $5.5V$ IPD: $1.5$ $\mu$ A typ. at $4.5V$ Freq: $20$ MHz max. | Not recommended for use in HS mode                                                                        | VDD: 4.5V to 5.5V IDD: 30 mA max. at 5.5V IPD: 1.5 $\mu$ A typ. at 4.5V Freq: 20 MHz max.              |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ.<br>at 32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq:200 kHz max. | Not recommended for use in LP mode                                                                      | Not recommended for use in LP mode                                                                      | VDD: 3.0V to 6.0V<br>IDD: 48 μA max.<br>at 32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq:200 kHz max. | VDD: 3.0V to 6.0V IDD: 48 $\mu$ A max. at 32 kHz, 3.0V IPD:13.5 $\mu$ A max. at 3.0V Freq:200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (Vol x IOL)

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 17.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-------------|-----------|----------------------------------------|

| 2. TppS     | 4 Ts      | (I <sup>2</sup> C specifications only) |

|   |           |   | (i o opcomodiono omy) |

|---|-----------|---|-----------------------|

| Т |           |   |                       |

| F | Frequency | T | Time                  |

Lowercase letters (pp) and their meanings:

| рр |          |     |          |

|----|----------|-----|----------|

| СС | CCP1     | osc | OSC1     |

| ck | CLKOUT   | rd  | RD       |

| cs | CS       | rw  | RD or WR |

| di | SDI      | sc  | SCK      |

| do | SDO      | SS  | SS       |

| dt | Data in  | t0  | T0CKI    |

| io | I/O port | t1  | T1CKI    |

| mc | MCLR     | wr  | WR       |

Uppercase letters and their meanings:

| S                     |                        |      |              |

|-----------------------|------------------------|------|--------------|

| F                     | Fall                   | Р    | Period       |

| Н                     | High                   | R    | Rise         |

| 1                     | Invalid (Hi-impedance) | V    | Valid        |

| L                     | Low                    | Z    | Hi-impedance |

| I <sup>2</sup> C only |                        |      |              |

| AA                    | output access          | High | High         |

| BUF                   | Bus free               | Low  | Low          |

Tcc:st (I<sup>2</sup>C specifications only)

| CC  |                 |     |                |

|-----|-----------------|-----|----------------|

| HD  | Hold            | SU  | Setup          |

| ST  |                 |     |                |

| DAT | DATA input hold | STO | STOP condition |

| STA | START condition |     |                |

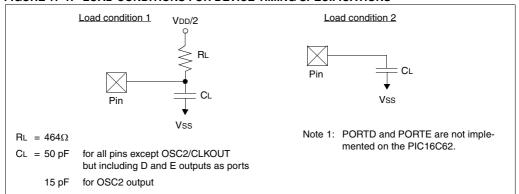

#### FIGURE 17-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

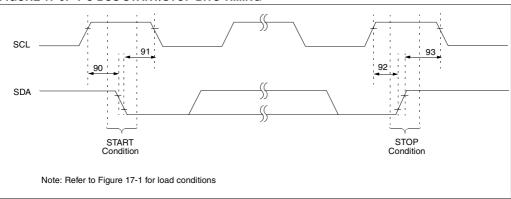

## FIGURE 17-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

## TABLE 17-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|---------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90            | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | _   |       | Only relevant for repeated START  |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   | ns    | condition                         |

| 91            | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   |       | After this period the first clock |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   | ns    | pulse is generated                |

| 92            | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   |       |                                   |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   | ns    |                                   |

| 93            | THD:STO | STOP condition  | 100 kHz mode | 4000 | _   | _   |       |                                   |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   | ns    |                                   |

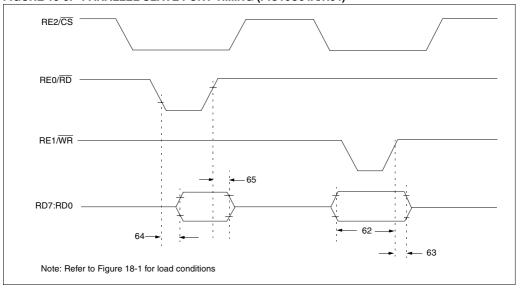

FIGURE 18-8: PARALLEL SLAVE PORT TIMING (PIC16C64A/R64)

TABLE 18-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C64A/R64)

| Parameter No. | Sym      | Characteristic                       |                         | Min | Typ† | Max | Units | Conditions             |

|---------------|----------|--------------------------------------|-------------------------|-----|------|-----|-------|------------------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS↑ (set | up time)                | 20  | _    | _   | ns    |                        |

|               |          |                                      |                         | 25  | _    | _   | ns    | Extended<br>Range Only |

| 63*           | TwrH2dtl | WR↑ or CS↑ to data–in invalid (hold  | PIC16 <b>C</b> 64A/R64  | 20  | _    | _   | ns    |                        |

|               |          | time)                                | PIC16 <b>LC</b> 64A.R64 | 35  | _    | _   | ns    |                        |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid        |                         | _   | _    | 80  | ns    |                        |

|               |          |                                      |                         | _   | _    | 90  | ns    | Extended<br>Range Only |

| 65*           | TrdH2dtl | RD↑ or CS↑ to data-out invalid       |                         | 10  | _    | 30  | ns    |                        |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

NOTES:

# Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

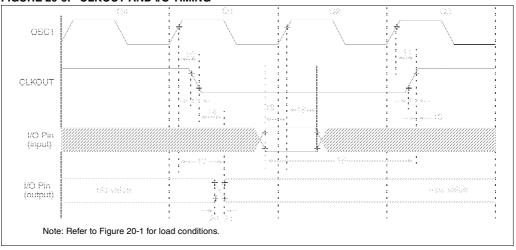

#### FIGURE 20-3: CLKOUT AND I/O TIMING

#### TABLE 20-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter No. | Sym      | Characteristic                    |                        | Min        | Тур† | Max         | Units | Conditions |

|---------------|----------|-----------------------------------|------------------------|------------|------|-------------|-------|------------|

| 10*           | TosH2ckL | OSC1↑ to CLKOUT↓                  |                        | _          | 75   | 200         | ns    | Note 1     |

| 11*           | TosH2ckH | OSC1↑ to CLKOUT↑                  |                        | _          | 75   | 200         | ns    | Note 1     |

| 12*           | TckR     | CLKOUT rise time                  |                        | _          | 35   | 100         | ns    | Note 1     |

| 13*           | TckF     | CLKOUT fall time                  |                        | _          | 35   | 100         | ns    | Note 1     |

| 14*           | TckL2ioV | CLKOUT ↓ to Port out valid        |                        | _          | -    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*           | TioV2ckH | Port in valid before CLKOUT ↑     |                        | Tosc + 200 | _    | _           | ns    | Note 1     |

| 16*           | TckH2iol | Port in hold after CLKOUT ↑       |                        | 0          |      | _           | ns    | Note 1     |

| 17*           | TosH2ioV | OSC1↑ (Q1 cycle) to Port out va   | lid                    | _          | 50   | 150         | ns    |            |

| 18*           | TosH2iol | OSC1↑ (Q2 cycle) to Port input    | PIC16 <b>C</b> 63/65A  | 100        |      | _           | ns    |            |

|               |          | invalid (I/O in hold time)        | PIC16 <b>LC</b> 63/65A | 200        | _    | _           | ns    |            |

| 19*           | TioV2osH | Port input valid to OSC1↑ (I/O in | setup time)            | 0          | _    | _           | ns    |            |

| 20*           | TioR     | Port output rise time             | PIC16 <b>C</b> 63/65A  | _          | 10   | 40          | ns    |            |

|               |          |                                   | PIC16 <b>LC</b> 63/65A | _          | _    | 80          | ns    |            |

| 21*           | TioF     | Port output fall time             | PIC16 <b>C</b> 63/65A  | _          | 10   | 40          | ns    |            |

|               |          |                                   | PIC16 <b>LC</b> 63/65A | _          | _    | 80          | ns    |            |

| 22††*         | Tinp     | INT pin high or low time          |                        | Tcy        | _    | _           | ns    |            |

| 23††*         | Trbp     | RB7:RB4 change INT high or lov    | v time                 | Tcy        | _    | _           | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

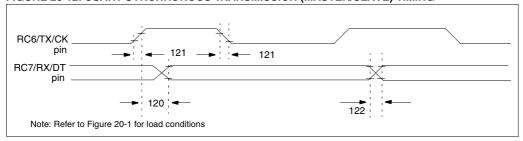

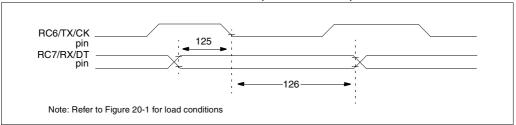

### FIGURE 20-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 20-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter No. | Sym                                          | Characteristic                   | racteristic            |   | Typ† | Max | Units | Conditions |

|---------------|----------------------------------------------|----------------------------------|------------------------|---|------|-----|-------|------------|

| 120*          | TckH2dtV                                     | SYNC XMIT (MASTER & SLAVE)       | PIC16 <b>C</b> 63/65A  |   | _    | 80  | ns    |            |

|               |                                              | Clock high to data out valid     | PIC16 <b>LC</b> 63/65A | _ | _    | 100 | ns    |            |

| 121*          | 121* Tckrf Clock out rise time and fall time | PIC16 <b>C</b> 63/65A            |                        | _ | 45   | ns  |       |            |

|               |                                              | (Master Mode)                    | PIC16 <b>LC</b> 63/65A | _ | _    | 50  | ns    |            |

| 122*          | Tdtrf                                        | Data out rise time and fall time | PIC16 <b>C</b> 63/65A  |   | _    | 45  | ns    |            |

|               |                                              |                                  | PIC16 <b>LC</b> 63/65A | _ | _    | 50  | ns    |            |

These parameters are characterized but not tested.

#### FIGURE 20-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 20-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Typ† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data setup before CK ↓ (DT setup time) | 15  | _    | _   | ns    |            |

| 126*             | TckL2dtl | Data hold after CK ↓ (DT hold time)                              | 15  | _    | _   | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

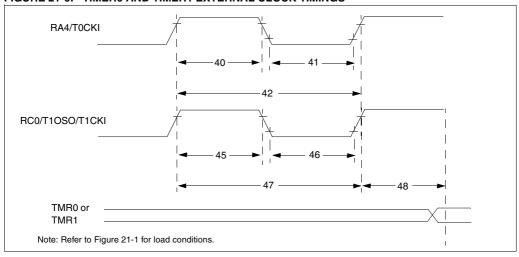

FIGURE 21-6: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 21-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                          |                   |                    | Min                                       | Typ†  | Max | Units | Conditions                         |

|--------------|----------|-----------------------------------------|-------------------|--------------------|-------------------------------------------|-------|-----|-------|------------------------------------|

| 40*          | Tt0H     | T0CKI High Pulse Width                  |                   | No Prescaler       | 0.5Tcy + 20                               | _     | _   | ns    | Must also meet                     |

|              |          |                                         |                   | With Prescaler     | 10                                        | _     | _   | ns    | parameter 42                       |

| 41*          | TtOL     | T0CKI Low Pulse W                       | /idth             | No Prescaler       | 0.5Tcy + 20                               | _     | _   | ns    | Must also meet                     |

|              |          |                                         |                   | With Prescaler     | 10                                        | _     | _   | ns    | parameter 42                       |

| 42*          | Tt0P     | T0CKI Period                            |                   | No Prescaler       | Tcy + 40                                  | _     | _   | ns    |                                    |

|              |          |                                         |                   | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _     | _   | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H     | T1CKI High Time                         | Synchronous, F    | rescaler = 1       | 0.5Tcy + 20                               | _     | _   | ns    | Must also meet                     |

|              |          |                                         | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _     | _   | ns    | parameter 47                       |

|              |          |                                         | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _     | _   | ns    |                                    |

|              |          |                                         | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _     | _   | ns    |                                    |

|              |          |                                         |                   | PIC16 <b>LC</b> 6X | 50                                        | _     | _   | ns    |                                    |

| 46*          | Tt1L     | T1CKI Low Time                          | Synchronous, F    |                    | 0.5Tcy + 20                               | _     | _   | ns    | Must also meet                     |

|              |          |                                         | Synchronous,      | PIC16 <b>C</b> 6X  | 15                                        | _     | _   | ns    | parameter 47                       |

|              |          |                                         | Prescaler = 2,4,8 | PIC16 <b>LC</b> 6X | 25                                        | _     | _   | ns    |                                    |

|              |          |                                         | Asynchronous      | PIC16 <b>C</b> 6X  | 30                                        | _     | _   | ns    |                                    |

|              |          |                                         |                   | PIC16 <b>LC</b> 6X | 50                                        | _     | _   | ns    |                                    |

| 47*          | Tt1P     | T1CKI input period                      | Synchronous       | PIC16 <b>C</b> 6X  | Greater of:<br>30 OR TCY + 40<br>N        | _     | _   | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                         |                   | PIC16 <b>LC</b> 6X | Greater of:<br>50 OR TCY + 40<br>N        |       |     |       | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                         | Asynchronous      | PIC16 <b>C</b> 6X  | 60                                        | _     | _   | ns    |                                    |

|              |          |                                         |                   | PIC16 <b>LC</b> 6X | 100                                       | _     | _   | ns    |                                    |

|              | Ft1      | Timer1 oscillator input frequency range |                   |                    | DC                                        | _     | 200 | kHz   |                                    |

|              |          | (oscillator enabled b                   | , ,               | ,                  |                                           |       |     |       |                                    |

| 48           | TCKEZtmr | 1 Delay from external                   | clock edge to tir | 2Tosc              | <u> </u>                                  | 7Tosc | _   |       |                                    |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### F.7 PIC16C7XX Family of Devces

|             |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|-------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|             | EPROM Program Memory (x14 words)                | 512                                 | 1K                  | 1K                                  | 2K                                  | 2K                         | _                          |

| Memory      | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2K                         |

|             | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|             | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _                                   | _                   | _                                   | _                                   | 1                          | 1                          |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|             | Parallel Slave Port                             | _                                   | _                   | _                                   | _                                   | _                          | _                          |

|             | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |