Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c63-20-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data may be fetched from the same memory using the same bus. Separating program and data busses further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C61 addresses 1K x 14 of program memory. The PIC16C62/62A/R62/64/64A/R64 address 2K x 14 of program memory, and the PIC16C63/R63/65/65A/R65 devices address 4K x 14 of program memory. The PIC16C66/67 address 8K x 14 program memory. All program memory is internal.

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of "special optimal situations" makes programming with the PIC16CXX simple yet efficient, thus significantly reducing the learning curve. The PIC16CXX device contains an 8-bit ALU and working register (W). The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register), the other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending upon the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. Bits C and DC operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## 4.0 MEMORY ORGANIZATION

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 4.1 Program Memory Organization

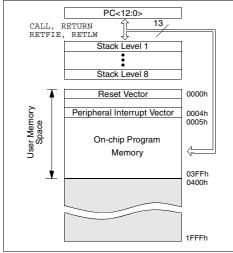

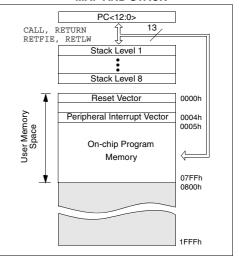

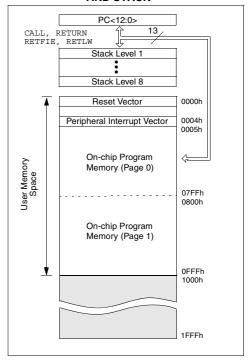

The PIC16C6X family has a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C61  | 1K x 14           | 0000h-03FFh   |

| PIC16C62  | 2K x 14           | 0000h-07FFh   |

| PIC16C62A | 2K x 14           | 0000h-07FFh   |

| PIC16CR62 | 2K x 14           | 0000h-07FFh   |

| PIC16C63  | 4K x 14           | 0000h-0FFFh   |

| PIC16CR63 | 4K x 14           | 0000h-0FFFh   |

| PIC16C64  | 2K x 14           | 0000h-07FFh   |

| PIC16C64A | 2K x 14           | 0000h-07FFh   |

| PIC16CR64 | 2K x 14           | 0000h-07FFh   |

| PIC16C65  | 4K x 14           | 0000h-0FFFh   |

| PIC16C65A | 4K x 14           | 0000h-0FFFh   |

| PIC16CR65 | 4K x 14           | 0000h-0FFFh   |

| PIC16C66  | 8K x 14           | 0000h-1FFFh   |

| PIC16C67  | 8K x 14           | 0000h-1FFFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 4-1: PIC16C61 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-2: PIC16C62/62A/R62/64/64A/ R64 PROGRAM MEMORY MAP AND STACK

#### FIGURE 4-3: PIC16C63/R63/65/65A/R65 PROGRAM MEMORY MAP AND STACK

## FIGURE 4-6: PIC16C62/62A/R62/64/64A/ R64 REGISTER FILE MAP

| 1          |                      |                                 |              |

|------------|----------------------|---------------------------------|--------------|

| File Addre |                      |                                 | File Address |

| 00h        | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup>             | 80h          |

| 01h        | TMR0                 | OPTION                          | 81h          |

| 02h        | PCL                  | PCL                             | 82h          |

| 03h        | STATUS               | STATUS                          | 83h          |

| 04h        | FSR                  | FSR                             | 84h          |

| 05h        | PORTA                | TRISA                           | 85h          |

| 06h        | PORTB                | TRISB                           | 86h          |

| 07h        | PORTC                | TRISC                           | 87h          |

| 08h        | PORTD <sup>(2)</sup> | TRISD <sup>(2)</sup>            | 88h          |

| 09h        | PORTE <sup>(2)</sup> | TRISE <sup>(2)</sup>            | 89h          |

| 0Ah        | PCLATH               | PCLATH                          | 8Ah          |

| 0Bh        | INTCON               | INTCON                          | 8Bh          |

| 0Ch        | PIR1                 | PIE1                            | 8Ch          |

| 0Dh        |                      |                                 | 8Dh          |

| 0Eh        | TMR1L                | PCON                            | 8Eh          |

| 0Fh        | TMR1H                |                                 | 8Fh          |

| 10h        | T1CON                |                                 | 90h          |

| 11h        | TMR2                 |                                 | 91h          |

| 12h        | T2CON                | PR2                             | 92h          |

| 13h        | SSPBUF               | SSPADD                          | 93h          |

| 14h        | SSPCON               | SSPSTAT                         | 94h          |

| 15h        | CCPR1L               |                                 | 95h          |

| 16h        | CCPR1H               |                                 | 96h          |

| 17h        | CCP1CON              |                                 | 97h          |

| 18h        |                      |                                 | 98h          |

|            |                      |                                 |              |

|            |                      |                                 |              |

|            |                      |                                 |              |

|            |                      |                                 | 0.51         |

| 1Fh        |                      |                                 | 9Fh          |

| 20h        |                      | General                         | A0h          |

|            |                      | Purpose                         |              |

|            | General              | Register                        | BFh          |

|            | Purpose<br>Register  |                                 | C0h          |

|            | -                    |                                 |              |

| 7Fh        |                      |                                 | FFh          |

|            | Bank 0               | Bank 1                          | =            |

|            | nplemented data me   |                                 | ead as '0'.  |

| Note       |                      | il register.<br>PORTE are not a | vailable on  |

|            | the PIC16C62         | 2/62A/R62.                      |              |

### FIGURE 4-7: PIC16C63/R63/65/65A/R65 REGISTER FILE MAP

|            | REGIST                                       | TER FILE MA                                  | AP           |

|------------|----------------------------------------------|----------------------------------------------|--------------|

| File Addre | ess                                          |                                              | File Address |

| 00h        | INDF <sup>(1)</sup>                          | INDF <sup>(1)</sup>                          | 80h          |

| 01h        | TMR0                                         | OPTION                                       | 81h          |

| 02h        | PCL                                          | PCL                                          | 82h          |

| 03h        | STATUS                                       | STATUS                                       | 83h          |

| 04h        | FSR                                          | FSR                                          | 84h          |

| 05h        | PORTA                                        | TRISA                                        | 85h          |

| 06h        | PORTB                                        | TRISB                                        | 86h          |

| 07h        | PORTC                                        | TRISC                                        | 87h          |

| 08h        | PORTD <sup>(2)</sup><br>PORTE <sup>(2)</sup> | TRISD <sup>(2)</sup><br>TRISE <sup>(2)</sup> | 88h          |

| 09h        | PCLATH                                       | PCLATH                                       | 89h<br>8Ah   |

| 0Ah        | INTCON                                       | INTCON                                       | 8Bh          |

| 0Bh<br>0Ch | PIR1                                         | PIE1                                         | 8Ch          |

|            | PIR2                                         | PIE2                                         | 8Dh          |

| 0Dh        |                                              |                                              |              |

| 0Eh        | TMR1L                                        | PCON                                         | 8Eh          |

| 0Fh        | TMR1H                                        |                                              | 8Fh          |

| 10h        | T1CON                                        |                                              | 90h          |

| 11h        | TMR2                                         |                                              | 91h          |

| 12h        | T2CON                                        | PR2                                          | 92h          |

| 13h        | SSPBUF                                       | SSPADD                                       | 93h          |

| 14h        | SSPCON                                       | SSPSTAT                                      | 94h          |

| 15h        | CCPR1L                                       |                                              | 95h          |

| 16h        | CCPR1H                                       |                                              | 96h          |

| 17h        | CCP1CON                                      |                                              | 97h          |

| 18h        | RCSTA                                        | TXSTA                                        | 98h          |

| 19h        | TXREG                                        | SPBRG                                        | 99h          |

| 1Ah        | RCREG                                        |                                              | 9Ah          |

| 1Bh        | CCPR2L                                       |                                              | 9Bh          |

| 1Ch        | CCPR2H                                       |                                              | 9Ch          |

| 1Dh        | CCP2CON                                      |                                              | 9Dh          |

| 1Eh        |                                              |                                              | 9Eh          |

| 1Fh        |                                              |                                              | 9Fh          |

| 20h        | General                                      | General                                      | A0h          |

| 7Fh        | Purpose<br>Register                          | Purpose<br>Register                          | FFh          |

|            | Bank 0                                       | Bank 1                                       | 1            |

| Unin Note  |                                              | I register<br>PORTE are not a                |              |

| L          |                                              |                                              |              |

| Address              | Name    | Bit 7              | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|--------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                    |                    |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod         | lule's registe     | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup> | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad        | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   |                    | _                  | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat          | ta Latch whe       | n written: PC | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat          | ta Latch whe       | n written: PC | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat          | ta Latch whe       | n written: PC | ORTD pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                    | _                  | _             | _              | _             | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                  | —                  | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF              | (6)                | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                    | _                  | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L    | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg        | ister for the M    | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                    | _                  | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod         | lule's registe     | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                  | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou         | is Serial Port     | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | 1 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 17h                  | CCP1CON | -                  | —                  | CCP1X         | CCP1Y          | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                                        |

| 18h                  | RCSTA   | SPEN               | RX9                | SREN          | CREN           | —             | FERR            | OERR          | RX9D      | 0000 -00x                | 0000 -00x                                      |

| 19h                  | TXREG   | USART Trai         | nsmit Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Ah                  | RCREG   | USART Red          | ceive Data R       | egister       |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 1Bh                  | CCPR2L  | Capture/Co         | mpare/PWM          | 2 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Ch                  | CCPR2H  | Capture/Co         | mpare/PWM          | 2 (MSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 1Dh                  | CCP2CON | —                  | —                  | CCP2X         | CCP2Y          | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0    | 00 0000                  | 00 0000                                        |

| 1Eh-1Fh              | _       | Unimpleme          | nted               |               |                |               |                 |               |           | —                        | _                                              |

#### TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented location read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

Г

## FIGURE 4-17: PIR1 REGISTER FOR PIC16C63/R63/66 (ADDRESS 0Ch)

| _        | _                                                | RCIF                                                                                  | TXIF                                   | SSPIF         | CCP1IF                               | TMB2IF        | TMR1IF  | B = Beadable                                                | hit                      |

|----------|--------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|---------------|--------------------------------------|---------------|---------|-------------------------------------------------------------|--------------------------|

| bit7     |                                                  | 1101                                                                                  |                                        |               |                                      |               | bit0    | W = Writable<br>U = Unimpler<br>read as '<br>- n = Value at | bit<br>nented bit,<br>0' |

| bit 7-6: | Reserved:                                        | Always ma                                                                             | intain thes                            | e bits clear. |                                      |               |         |                                                             |                          |

| bit 5:   | <b>RCIF:</b> USA<br>1 = The US<br>0 = The US     | ART receiv                                                                            | e buffer is                            | full (cleared | l by reading                         | RCREG)        |         |                                                             |                          |

| bit 4:   | <b>TXIF:</b> USA<br>1 = The US<br>0 = The US     | ART transr                                                                            | nit buffer is                          | empty (cle    | ared by writi                        | ng to TXRE    | G)      |                                                             |                          |

| bit 3:   | <b>SSPIF</b> : Syr<br>1 = The tra<br>0 = Waiting | nsmission/ı                                                                           | eception is                            |               | ag bit<br>must be clea               | ared in softw | vare)   |                                                             |                          |

| bit 2:   | 0 = No TMI<br>Compare M                          | ode<br>1 register c<br>R1 register<br><u>Mode</u><br>1 register c<br>R1 register<br>2 | apture occi<br>capture oc<br>ompare ma | curred        | be cleared i<br>ed (must be c<br>red | ,             | ftware) |                                                             |                          |

| bit 1:   | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TM     | o PR2 mat                                                                             | ch occurred                            | d (must be o  | bit<br>cleared in so                 | ftware)       |         |                                                             |                          |

| bit 0:   | <b>TMR1IF</b> : T<br>1 = TMR1 1<br>0 = No TMI    | register ove                                                                          | rflow occur                            | red (must b   | e cleared in                         | software)     |         |                                                             |                          |

| globa    | 0 = No TMI                                       | R1 register                                                                           | overflow or                            | curred        | n occurs rega                        | ardless of th |         | corresponding e<br>rupt flag bits are                       |                          |

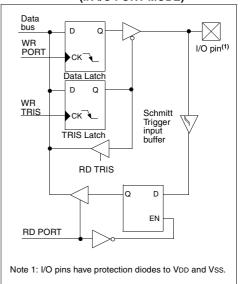

### 5.4 PORTD and TRISD Register

## Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

## TABLE 5-9: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input Note 1: Buffer is a Schmitt Trigger when in I/O mode, and a TTL buffer when in Parallel Slave Port mode.

## TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7   | Bit 6      | Bit 5      | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|------------|------------|---------|-------|----------|--------------|--------|--------------------------|---------------------------|

| 08h     | PORTD | RD7     | RD6        | RD5        | RD4     | RD3   | RD2      | RD1          | RD0    | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORTD I | Data Direc | tion Regis | ter     |       |          |              |        | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF     | OBF        | IBOV       | PSPMODE | _     | PORTE Da | ata Directio | n Bits | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

### 7.2 Using Timer0 with External Clock

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

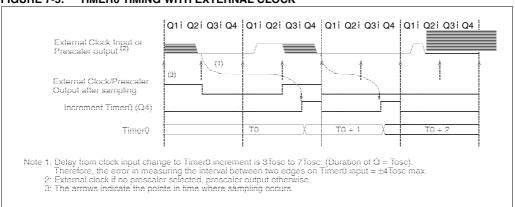

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF   | CCP1CON     | ; | Turn CCP module off   |

|--------|-------------|---|-----------------------|

| MOVLW  | NEW_CAPT_PS | ; | Load the W reg with   |

|        |             | ; | the new prescaler     |

|        |             | ; | mode value and CCP ON |

| MOVWF  | CCP1CON     | ; | Load CCP1CON with     |

| ; this | value       |   |                       |

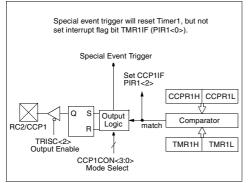

## 10.2 Compare Mode

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time interrupt flag bit CCP1IF is set.

### FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 10.2.1 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 10.2.2 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 10.2.3 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 and CCP2 resets the TMR1 register pair. This allows the CCPR1H:CCPR1L and CCPR2H:CCPR2L registers to effectively be 16-bit programmable period register(s) for Timer1.

For compatibility issues, the special event trigger output of CCP1 (<u>PIC16C72</u>) and CCP2 (all other <u>PIC16C7X</u> devices) also starts an A/D conversion.

Note: The "special event trigger" from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>). Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7                | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|-----------|-------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)       | RCIF        | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9       | SREN        | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 1Ah     | RCREG | USART Re             | eceive Re | egister     |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)       | RCIE        | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN        | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera    | tor Registe | ər    |       |        |        |        | 0000 0000               | 0000 0000                       |

## TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: PSPIE and PSPIF are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

| BCF               | Bit Clear                                                          | f                       |                        |                       |

|-------------------|--------------------------------------------------------------------|-------------------------|------------------------|-----------------------|

| Syntax:           | [ <i>label</i> ] BC                                                | CF f,b                  |                        |                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 7                       |                        |                       |

| Operation:        | $0 \rightarrow (f < b;$                                            | >)                      |                        |                       |

| Status Affected:  | None                                                               |                         |                        |                       |

| Encoding:         | 01                                                                 | 00bb                    | bfff                   | ffff                  |

| Description:      | Bit 'b' in re                                                      | gister 'f' is           | s cleared.             |                       |

| Words:            | 1                                                                  |                         |                        |                       |

| Cycles:           | 1                                                                  |                         |                        |                       |

| Q Cycle Activity: | Q1                                                                 | Q2                      | Q3                     | Q4                    |

|                   | Decode                                                             | Read<br>register<br>'f' | Process<br>data        | Write<br>register 'f' |

| Example           | BCF                                                                | FLAG_                   | REG, 7                 |                       |

|                   | After Inst                                                         | FLAG_RE                 | EG = 0xC7<br>EG = 0x47 |                       |

| BTFSC             | Bit Test,                                                                                                                                                                                                                          | Skip if Cl                                                          | ear              |                  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|------------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] B1                                                                                                                                                                                                                | FSC f,b                                                             |                  |                  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                 | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                  |                  |  |  |  |  |  |

| Operation:        | skip if (f <b>) = 0</b>                                                                                                                                                                                                            |                                                                     |                  |                  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                               | None                                                                |                  |                  |  |  |  |  |  |

| Encoding:         | 01 10bb bfff ffff                                                                                                                                                                                                                  |                                                                     |                  |                  |  |  |  |  |  |

| Description:      | If bit 'b' in register 'f' is '1' then the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2Tcy<br>instruction. |                                                                     |                  |                  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                  |                                                                     |                  |                  |  |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                                                                                                               |                                                                     |                  |                  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                 | Q2                                                                  | Q3               | Q4               |  |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                             | Read<br>register 'f'                                                | Process<br>data  | No-<br>Operation |  |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                                                                                                           | le)                                                                 |                  |                  |  |  |  |  |  |

|                   | Q1                                                                                                                                                                                                                                 | Q2                                                                  | Q3               | Q4               |  |  |  |  |  |

|                   | No-<br>Operation                                                                                                                                                                                                                   | No-<br>Operation                                                    | No-<br>Operation | No-<br>Operation |  |  |  |  |  |

| Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                        |                                                                     |                  |                  |  |  |  |  |  |

|                   | After Inst                                                                                                                                                                                                                         | PC = a                                                              |                  | ERE              |  |  |  |  |  |

| BSF               | Bit Set f                                                           |                         |                 |                       |  |  |  |  |

|-------------------|---------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                 | SF f,b                  |                 |                       |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                         |                 |                       |  |  |  |  |

| Operation:        | $1 \rightarrow (f < b >)$                                           |                         |                 |                       |  |  |  |  |

| Status Affected:  | None                                                                |                         |                 |                       |  |  |  |  |

| Encoding:         | 01                                                                  | 01bb                    | bfff            | ffff                  |  |  |  |  |

| Description:      | Bit 'b' in re                                                       | gister 'f' is           | s set.          |                       |  |  |  |  |

| Words:            | 1                                                                   |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                                                                   |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                                                  | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode                                                              | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | BSF                                                                 | FLAG_F                  | REG, 7          |                       |  |  |  |  |

|                   | Before Instruction<br>FLAG REG = 0x0A                               |                         |                 |                       |  |  |  |  |

|                   | After Inst                                                          | ruction                 |                 |                       |  |  |  |  |

|                   |                                                                     | FLAG_RE                 | EG = 0x8A       | 4                     |  |  |  |  |

PC = address TRUE if FLAG<1>=1, PC = address FALSE

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

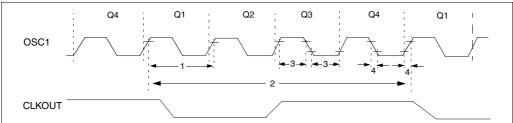

## 15.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 15-2: EXTERNAL CLOCK TIMING

## TABLE 15-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units       | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz         | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz         | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 20     | MHz         | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz         | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz         | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz         | XT osc mode        |

|                  |       |                                  | 1   | _    | 4      | MHz         | HS osc mode (-04)  |

|                  |       |                                  | 1   | _    | 20     | MHz         | HS osc mode (-20)  |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | _      | ns          | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | _    | _      | ns          | HS osc mode (-04)  |

|                  |       |                                  | 50  | _    | _      | ns          | HS osc mode (-20)  |

|                  |       | 5                                | _   | —    | μs     | LP osc mode |                    |

|                  |       | Oscillator Period                | 250 | _    | _      | ns          | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns          | XT osc mode        |

|                  |       |                                  | 250 | _    | 1,000  | ns          | HS osc mode (-04)  |

|                  |       |                                  | 50  | _    | 1,000  | ns          | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | —      | μs          | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 1.0 | Тсү  | DC     | μs          | TCY = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or | 50  | _    | _      | ns          | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | —      | μs          | LP oscillator      |

|                  |       |                                  |     | _    | —      | ns          | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | 25  | _    | _      | ns          | XT oscillator      |

|                  | TosF  | Fall Time                        | 50  | _    | —      | ns          | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns          | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

|  | Applicable Devices | 61 | 62 | 62A | <b>B62</b> | 63 | B63 | 64 | 64A | <b>R64</b> | 65 | 65A | <b>B65</b> | 66 | 67 |

|--|--------------------|----|----|-----|------------|----|-----|----|-----|------------|----|-----|------------|----|----|

|--|--------------------|----|----|-----|------------|----|-----|----|-----|------------|----|-----|------------|----|----|

|       |                                    | Standa                                                | rd Operat | ina ( | Conditior | ns (unle | ess otherwise stated)                                                   |  |  |  |

|-------|------------------------------------|-------------------------------------------------------|-----------|-------|-----------|----------|-------------------------------------------------------------------------|--|--|--|

|       |                                    |                                                       | ng temper | •     |           | •        | TA $\leq$ +125°C for extended,                                          |  |  |  |

|       | ARACTERISTICS                      |                                                       |           |       | -40°      | C ≤      | TA $\leq$ +85°C for industrial and                                      |  |  |  |

|       | ANACIENISTICS                      | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |           |       |           |          |                                                                         |  |  |  |

|       |                                    |                                                       |           | VDD   | range as  | descri   | bed in DC spec Section 18.1 and                                         |  |  |  |

|       |                                    | Section                                               | 18.2      |       |           |          |                                                                         |  |  |  |

| Param | Characteristic                     | Sym                                                   | Min       | Тур   | Max       | Units    | Conditions                                                              |  |  |  |

| No.   |                                    |                                                       |           | †     |           |          |                                                                         |  |  |  |

|       | Output High Voltage                |                                                       |           |       |           |          |                                                                         |  |  |  |

| D090  | I/O ports (Note 3)                 | Vон                                                   | VDD-0.7   | -     | -         | V        | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |  |  |

| D090A |                                    |                                                       | VDD-0.7   | -     | -         | V        | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)        |                                                       | VDD-0.7   | -     | -         | V        | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D092A |                                    |                                                       | VDD-0.7   | -     | -         | V        | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |

| D150* | Open-Drain High Voltage            | Vod                                                   | -         | -     | 14        | V        | RA4 pin                                                                 |  |  |  |

|       | Capacitive Loading Specs on Out-   |                                                       |           |       |           |          |                                                                         |  |  |  |

|       | put Pins                           |                                                       |           |       |           |          |                                                                         |  |  |  |

| D100  | OSC2 pin                           | Cosc2                                                 | -         | -     | 15        | pF       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101  | All I/O pins and OSC2 (in RC mode) | Cio                                                   | -         | -     | 50        | pF       |                                                                         |  |  |  |

| D102  | SCL, SDA in I <sup>2</sup> C mode  | Cb                                                    | -         | -     | 400       | pF       |                                                                         |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

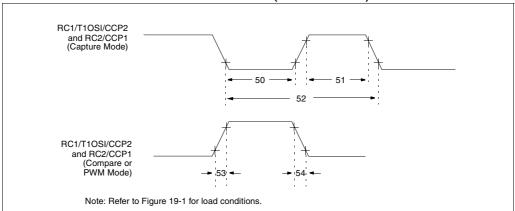

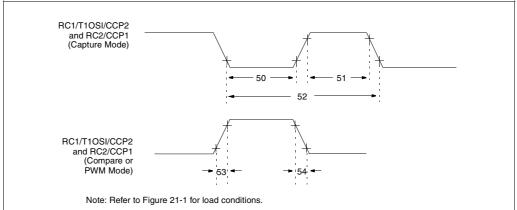

## FIGURE 19-6: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 19-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym  | Characteristic                |                            |                    | Min         | Тур† | Max | Units | Conditions                         |

|------------------|------|-------------------------------|----------------------------|--------------------|-------------|------|-----|-------|------------------------------------|

| 50*              | TccL | CCP1 and CCP2                 |                            |                    | 0.5TCY + 20 | —    | _   | ns    |                                    |

|                  |      | input low time                |                            |                    | 10          | _    |     | ns    |                                    |

|                  |      |                               |                            | PIC16 <b>LC</b> 65 | 20          | —    | -   | ns    |                                    |

| 51*              | TccH | CH CCP1 and CCP2 No Prescaler |                            |                    | 0.5Tcy + 20 | _    |     | ns    |                                    |

|                  |      | input high time               | With Prescaler             | PIC16 <b>C</b> 65  | 10          | _    |     | ns    |                                    |

|                  |      |                               |                            | PIC16 <b>LC</b> 65 | 20          | —    |     | ns    |                                    |

| 52*              | TccP | CCP1 and CCP2 in              | CCP1 and CCP2 input period |                    |             | _    | I   | ns    | N = prescale value<br>(1,4, or 16) |

| 53               | TccR | CCP1 and CCP2 c               | utput rise time            | PIC16 <b>C</b> 65  | _           | 10   | 25  | ns    |                                    |

|                  |      |                               |                            | PIC16 <b>LC</b> 65 | —           | 25   | 45  | ns    |                                    |

| 54               | TccF | CCP1 and CCP2 c               | utput fall time            | PIC16 <b>C</b> 65  | —           | 10   | 25  | ns    |                                    |

|                  |      |                               |                            |                    | —           | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

## FIGURE 21-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

## TABLE 21-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym                    | Characteristic   |                            |                        | Min         | Тур† | Max | Units | Conditions                         |

|--------------|------------------------|------------------|----------------------------|------------------------|-------------|------|-----|-------|------------------------------------|

| 50*          | TccL                   | CCP1 and CCP2    | No Prescaler               |                        | 0.5TCY + 20 | —    | _   | ns    |                                    |

|              |                        | input low time   | With Prescaler             | PIC16CR63/R65          | 10          | —    | —   | ns    |                                    |

|              |                        |                  |                            | PIC16LCR63/R65         | 20          | -    | _   | ns    |                                    |

| 51*          | 51* TccH CCP1 and CCP2 |                  | No Prescaler               |                        | 0.5TCY + 20 | —    | —   | ns    |                                    |

|              |                        | input high time  | With Prescaler             | PIC16CR63/R65          | 10          | _    | _   | ns    |                                    |

|              |                        |                  |                            | PIC16LCR63/R65         | 20          | -    | _   | ns    |                                    |

| 52*          | TccP                   | CCP1 and CCP2 ir | CCP1 and CCP2 input period |                        |             | -    | —   | ns    | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR                   | CCP1 and CCP2 o  | utput rise time            | PIC16CR63/R65          | —           | 10   | 25  | ns    |                                    |

|              |                        |                  |                            | PIC16LCR63/R65         | _           | 25   | 45  | ns    |                                    |

| 54*          | TccF                   | CCP1 and CCP2 o  | utput fall time            | PIC16 <b>CR</b> 63/R65 | —           | 10   | 25  | ns    |                                    |

|              |                        |                  | PIC16LCR63/R65             | —                      | 25          | 45   | ns  |       |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

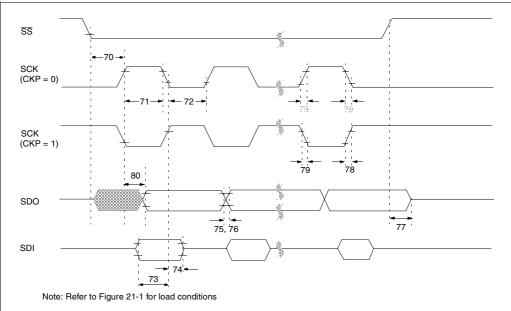

## TABLE 21-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Тур† | Мах | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70*              | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input  | Тсү      | —    | —   | ns    |            |

| 71*              | TscH                  | SCK input high time (slave mode)         | Tcy + 20 | _    | _   | ns    |            |

| 72*              | TscL                  | SCK input low time (slave mode)          | TCY + 20 | _    | —   | ns    |            |

| 73*              | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | —    | —   | ns    |            |

| 74*              | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | —    | —   | ns    |            |

| 75*              | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76*              | TdoF                  | SDO data output fall time                |          | 10   | 25  | ns    |            |

| 77*              | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78*              | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79*              | TscF                  | SCK output fall time (master mode)       | _        | 10   | 25  | ns    |            |

| 80*              | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

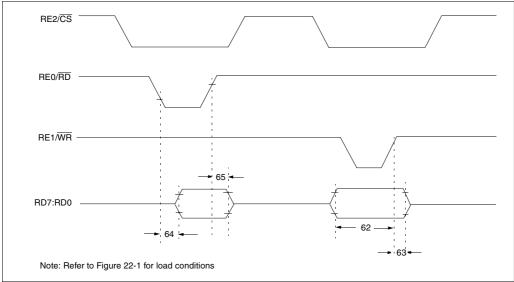

## FIGURE 22-8: PARALLEL SLAVE PORT TIMING (PIC16C67)

## TABLE 22-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C67)

| Parameter<br>No. | Sym      | Characteristic                                                                             |                                                                           | Min | Тур† | Max | Units | Conditions             |

|------------------|----------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|------|-----|-------|------------------------|

| 62*              | TdtV2wrH | Data in valid before $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ (setup time) |                                                                           | 20  | _    | _   | ns    |                        |

|                  |          |                                                                                            |                                                                           | 25  | —    | —   | ns    | Extended<br>Range Only |

| 63*              | TwrH2dtl | $\overline{WR}$ or $\overline{CS}$ to data–in invalid (hold                                | PIC16 <b>C</b> 67                                                         | 20  | _    | —   | ns    |                        |

|                  |          | time)                                                                                      | PIC16 <b>LC</b> 67                                                        | 35  |      | _   | ns    |                        |

| 64               | TrdL2dtV | $\overline{\text{RD}}\downarrow$ and $\overline{\text{CS}}\downarrow$ to data–out valid    | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid |     |      | 80  | ns    |                        |

|                  |          |                                                                                            |                                                                           |     | —    | 90  | ns    | Extended<br>Range Only |

| 65*              | TrdH2dtl | $\overline{\text{RD}}$ for $\overline{\text{CS}}$ to data-out invalid                      |                                                                           |     | -    | 30  | ns    |                        |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

NOTES:

| Figure 11-2:                                                                                                                                                                                                      | SSPCON: Sync Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                   | Control Register (Address 14h) 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 11-3:                                                                                                                                                                                                      | SSP Block Diagram (SPI Mode) 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 11-4:                                                                                                                                                                                                      | SPI Master/Slave Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 11-5:                                                                                                                                                                                                      | SPI Mode Timing, Master Mode or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |