Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c63-20i-sp |

#### Pin Diagrams PDIP, SOIC, Windowed CERDIP SDIP, SOIC, SSOP, Windowed CERDIP (300 mil) 18 → RA1 MCI R/Vpp RA3 ← 2 RA4/T0CKI ← 3 RA0 ← □ 2 27 ☐ → RB6 26 ☐ → RB5 17 → RA0 RA1 **←** ► □ 3 16 → OSC1/CLKIN 25 □ → RB4 MCLR/VPP → 4 15 → OSC2/CLKOUT RA3 **→** □ 5 24 ☐ → RB3 Vss --- □ 5 RA4/T0CKI ← □ 6 23 ☐ → RB2 RA5/SS → □ 7 Vss → □ 8 22 ☐ → RB1 21 ☐ → RB0/INT 13 ←→ RB7 RB0/INT ← 6 RB1 **→** 7 12 ←→ RB6 20 - VDD 19 - VSS RB2 → □ 8 11 → RB5 RC0/T1OSI/T1CKI ← ☐ 11 RC1/T1OSO ← ☐ 12 RC2/CCP1 ← ☐ 13 RB3 **→** 9 RB4 16 ☐ ←→ RC5/SDO PIC16C61 RC3/SCK/SCL ← ► □ 14 15 ☐ ←→ RC4/SDI/SDA **PIC16C62** SDIP, SOIC, SSOP, Windowed CERDIP (300 mil) SDIP, SOIC, Windowed CERDIP (300 mil) R/VPP - C RA0 - C RA1 - C RA2 - C MCI B/Vpp -28 ☐ ←→ RB7 MCI B/Vpp -□ ←→ RB6 □ - RB6 RA1 → □ 3 26 ☐ ←→ RB5 26 ☐ ←→ RB5 RA2 <del>▼ ►</del> □ 4 25 ☐ ←→ RB4 4 25 ☐ ←→ RB4 RA3 **→** 5 RA4/T0CKI **→** 6 24 ☐ → RB3 23 ☐ → RB2 24 ☐ → RB3 23 ☐ → RB2 RA5/SS → □ 7 22 ☐ → RB1 Vss — **-** □ 8 21 □ - RB0/INT OSC1/CLKIN → 9 OSC2/CLKOUT ← 10 10 10 19 ☐ **→** Vss RC0/T1OSO/T1CKI - 11 RC1/T1OSI - 12 RC2/CCP1 - 13 RC0/T1OSO/T1CKI ---18 ☐ ← ► RC7/RX/DT 17 ☐ → RC6 12 17 ☐ → RC6/TX/CK RC2/CCP1 → ► 16 → BC5/SDO 13 16 - RC5/SDO RC3/SCK/SCL ← ► RC3/SCK/SCL → □ 14 15 T → RC4/SDI/SDA 15 RC4/SDI/SDA PIC16C62A PIC16C63 PIC16CR62 PIC16CR63 **PIC16C66** PDIP, Windowed CERDIP MCLR/Vpp → □ 1 40 1 → BR7 MCLB/Vpp → 1 40 1 → BB7 39 ☐ <del>< ►</del> RB6 38 ☐ <del>< ►</del> RB5 RA0 <del>▼ ►</del> □ 2 RA1 → □ 3 37 RB4 36 RB3 35 RB2 34 RB1 RA2 <del>▼ ►</del> □ 4 36 ☐ <del>< ►</del> RB3 35 ☐ <del>< ►</del> RB2 BA3 <del>▼ ►</del> □ 5 RA4/T0CKI → □ 6 RA5/SS → □ 7 33 ☐ → ► RB0/INT RE0/RD → □ 8 RE1/WR → □ 9 RE2/CS → □ 10 26 → RC7/RX/DT PIC16C64A PIC16C64 **PIC16C65** PIC16CR64 PIC16C65A

PIC16CR65 PIC16C67

#### 4.2.2.7 PIR2 REGISTER

Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

This register contains the CCP2 interrupt flag bit.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-21: PIR2 REGISTER (ADDRESS 0Dh)

U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 CCP2IF bit7

R = Readable bit W = Writable bit U = Unimplemented bit,

bit 7-1: Unimplemented: Read as '0'

read as '0' n = Value at POR reset

bit 0: CCP2IF: CCP2 Interrupt Flag bit

Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

**PWM Mode**

Unused in this mode

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

Note:

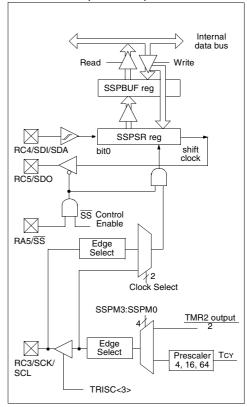

## 11.2.1 OPERATION OF SSP MODULE IN SPI MODE

### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- · Serial Data Out (SDO)

- · Serial Data In (SDI)

- · Serial Clock (SCK)

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>). These control bits allow the following to be specified:

- · Master Mode (SCK is the clock output)

- · Slave Mode (SCK is the clock input)

- Clock Polarity (Output/Input data on the Rising/ Falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full bit, BF (SSPSTAT<0>) and flag bit SSPIF are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>) will be set. User software must clear bit WCOL so that it can be determined if the following write(s) to the SSPBUF completed successfully. When the application software is expecting to receive valid data, the SSPBUF register should be read before the next byte of data to transfer is written to the SSPBUF register. The Buffer Full bit BF (SSPSTAT<0>) indicates when the SSPBUF register has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF register must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-1 shows the loading of the SSPBUF (SSPSR) register for data transmission. The shaded instruction is only required if the received data is meaningful.

## EXAMPLE 11-1: LOADING THE SSPBUF (SSPSR) REGISTER

|    |     | BSF   | STATUS,  | RP0 | ;Specify Bank 1   |

|----|-----|-------|----------|-----|-------------------|

| L( | OOP | BTFSS | SSPSTAT, | BF  | ;Has data been    |

|    |     |       |          |     | ;received         |

|    |     |       |          |     | ;(transmit        |

|    |     |       |          |     | ;complete)?       |

|    |     | GOTO  | LOOP     |     | ; No              |

|    |     | BCF   | STATUS,  | RP0 | ;Specify Bank 0   |

|    |     | MOVF  | SSPBUF,  | W   | ;W reg = contents |

|    |     |       |          |     | ;of SSPBUF        |

|    |     | MOVWF | RXDATA   |     | ;Save in user RAM |

|    |     | MOVF  | TXDATA,  | W   | ;W reg = contents |

|    |     |       |          |     | ; of TXDATA       |

|    |     | MOVWF | SSPBUF   |     | ;New data to xmit |

The block diagram of the SSP module, when in SPI mode (Figure 11-3), shows that the SSPSR register is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

## FIGURE 11-3: SSP BLOCK DIAGRAM (SPI MODE)

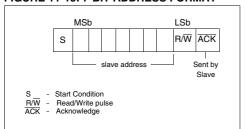

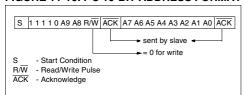

#### 11.4.2 ADDRESSING I2C DEVICES

There are two address formats. The simplest is the 7-bit address format with a  $R\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

#### FIGURE 11-16: I2C 10-BIT ADDRESS FORMAT

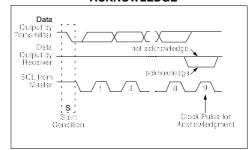

#### 11.4.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

## FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

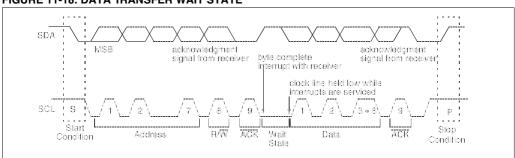

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 11-18: DATA TRANSFER WAIT STATE

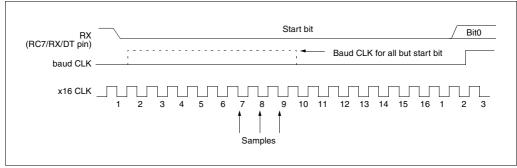

### 12.1 USART Baud Rate Generator (BRG)

| Applicable Devices |    |     |     |    |     |    |     |     |    |     |     |    |    |

|--------------------|----|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| 61                 | 62 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

## EXAMPLE 12-1: CALCULATING BAUD RATE FRROR

Desired Baud rate = Fosc / (64 (X + 1))

9600 = 16000000 / (64 (X + 1)) $X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X+1)) equation can reduce the baud rate error in some cases.

Note: For the PIC16C63/R63/65/65A/R65 the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C66/67.

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address                                | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 98h                                    | TXSTA | CSRC  | TX9   | TXEN  | SYNC  | -     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| 18h                                    | RCSTA | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| 99h SPBRG Baud Rate Generator Register |       |       |       |       |       |       |       |       |       | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

TABLE 13-12: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

| Register |    |    |     |     |    | Appli | cab | le De | vices | \$ |     |     |    |    | Power-on Reset<br>Brown-out<br>Reset | MCLR Reset during:  - normal operation  - SLEEP WDT Reset | Wake-up via<br>interrupt or<br>WDT Wake-up |

|----------|----|----|-----|-----|----|-------|-----|-------|-------|----|-----|-----|----|----|--------------------------------------|-----------------------------------------------------------|--------------------------------------------|

| TRISD    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 1111                            | 1111 1111                                                 | uuuu uuuu                                  |

| TRISE    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 -111                            | 0000 -111                                                 | uuuu -uuu                                  |

| PIE1     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 0000                              | 00 0000                                                   | uu uuuu                                    |

|          | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                 | uuuu uuuu                                  |

| PIE2     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0                                    | 0                                                         | u                                          |

| PCON     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0u                                   | uu                                                        | uu                                         |

| FCON     | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0-                                   | u-                                                        | u-                                         |

| PR2      | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 1111 1111                            | 1111 1111                                                 | 1111 1111                                  |

| SSPADD   | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                 | uuuu uuuu                                  |

| SSPSTAT  | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 00 0000                              | 00 0000                                                   | uu uuuu                                    |

| TXSTA    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 -010                            | 0000 -010                                                 | uuuu -uuu                                  |

| SPBRG    | 61 | 62 | 62A | R62 | 63 | R63   | 64  | 64A   | R64   | 65 | 65A | R65 | 66 | 67 | 0000 0000                            | 0000 0000                                                 | uuuu uuuu                                  |

$<sup>\</sup>label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

<sup>3:</sup> See Table 13-10 and Table 13-11 for reset value for specific conditions.

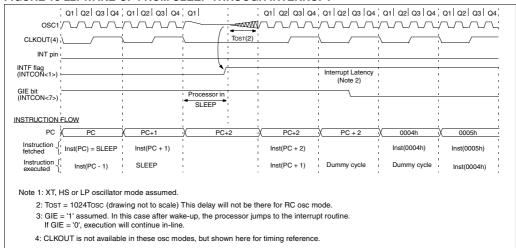

#### FIGURE 13-22: WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### 13.9 Program Verification/Code Protection

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

#### 13.10 ID Locations

## Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

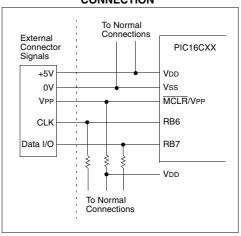

#### 13.11 <u>In-Circuit Serial Programming</u>

| Αp | Applicable Devices |     |     |    |     |    |     |     |    |     |     |    |    |

|----|--------------------|-----|-----|----|-----|----|-----|-----|----|-----|-----|----|----|

| 61 | 62                 | 62A | R62 | 63 | R63 | 64 | 64A | R64 | 65 | 65A | R65 | 66 | 67 |

The PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding pins RB6 and RB7 low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device in program/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

FIGURE 13-23: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic  | ,       | Description                  | Cycles |     | 14-Bit | Opcode | е    | Status   | Notes |

|-----------|---------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands  |         |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE | ENTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF     | f, d    | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d    | AND W with f                 | 1      | 0.0 | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF      | f       | Clear f                      | 1      | 0.0 | 0001   | lfff   | ffff | Z        | 2     |

| CLRW      | -       | Clear W                      | 1      | 0.0 | 0001   | 0xxx   | xxxx | Z        |       |

| COMF      | f, d    | Complement f                 | 1      | 0.0 | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF      | f, d    | Decrement f                  | 1      | 0.0 | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ    | f, d    | Decrement f, Skip if 0       | 1(2)   | 0.0 | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF      | f, d    | Increment f                  | 1      | 0.0 | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ    | f, d    | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF     | f, d    | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF      | f, d    | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF     | f       | Move W to f                  | 1      | 0.0 | 0000   | lfff   | ffff |          |       |

| NOP       | -       | No Operation                 | 1      | 0.0 | 0000   | 0xx0   | 0000 |          |       |

| RLF       | f, d    | Rotate Left f through Carry  | 1      | 0.0 | 1101   | dfff   | ffff | С        | 1,2   |

| RRF       | f, d    | Rotate Right f through Carry | 1      | 0.0 | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF     | f, d    | Subtract W from f            | 1      | 0.0 | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d    | Swap nibbles in f            | 1      | 0.0 | 1110   | dfff   | ffff |          | 1,2   |

| XORWF     | f, d    | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIEN | TED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF       | f, b    | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF       | f, b    | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC     | f, b    | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS     | f, b    | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A | ND CO   | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW     | k       | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW     | k       | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL      | k       | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT    | -       | Clear Watchdog Timer         | 1      | 0.0 | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO      | k       | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW     | k       | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW     | k       | Move literal to W            | 1      | 11  | 00x    | kkkk   | kkkk |          |       |

| RETFIE    | -       | Return from interrupt        | 2      | 0.0 | 0000   | 0000   | 1001 |          |       |

| RETLW     | k       | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN    | -       | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP     | -       | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW     | k       | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW     | k       | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

|           |         |                              |        |     |        |        |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOUF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| INCFSZ            | Increme                                                                                                  | nt f, Skip                                                                     | if 0                                                                     |                                                 |

|-------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------|

| Syntax:           | [ label ]                                                                                                | INCFSZ                                                                         | f,d                                                                      |                                                 |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                           | 27                                                                             |                                                                          |                                                 |

| Operation:        | (f) + 1 $\rightarrow$ skip if res                                                                        | •                                                                              | ion),                                                                    |                                                 |

| Status Affected:  | None                                                                                                     |                                                                                |                                                                          |                                                 |

| Encoding:         | 00                                                                                                       | 1111                                                                           | dfff                                                                     | ffff                                            |

| Description:      | The conte<br>mented. If<br>the W regi<br>placed bad<br>If the resu<br>executed.<br>cuted insta-<br>tion. | 'd' is 0 the<br>ister. If 'd' i<br>ck in regist<br>It is 1, the<br>If the resu | e result is p<br>s 1 the res<br>ter 'f'.<br>next instru<br>It is 0, a NO | olaced in<br>sult is<br>oction is<br>OP is exe- |

| Words:            | 1                                                                                                        |                                                                                |                                                                          |                                                 |

| Cycles:           | 1(2)                                                                                                     |                                                                                |                                                                          |                                                 |

| Q Cycle Activity: | Q1                                                                                                       | Q2                                                                             | Q3                                                                       | Q4                                              |

|                   | Decode                                                                                                   | Read<br>register 'f'                                                           | Process<br>data                                                          | Write to destination                            |

| If Skip:          | (2nd Cyc                                                                                                 | le)                                                                            |                                                                          |                                                 |

|                   | Q1                                                                                                       | Q2                                                                             | Q3                                                                       | Q4                                              |

|                   | No-<br>Operation                                                                                         | No-<br>Operation                                                               | No-<br>Operation                                                         | No-<br>Operation                                |

| Example           | HERE                                                                                                     | INCFS<br>GOTO<br>UE •                                                          | Z CI<br>LO                                                               | NT, 1<br>OP                                     |

|                   | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                     | = add<br>ruction<br>= CN7<br>= 0,<br>= add<br>≠ 0,                             | ress HERE  + 1  ress CONT  ress HERE                                     |                                                 |

| IORLW             | Inclusive                                                                                                       | OR Lite             | eral with       | W             |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|-----------------|---------------|--|--|--|

| Syntax:           | [ label ]                                                                                                       | IORLW               | k               |               |  |  |  |

| Operands:         | $0 \le k \le 25$                                                                                                | 55                  |                 |               |  |  |  |

| Operation:        | (W) .OR.                                                                                                        | $k \rightarrow (W)$ | )               |               |  |  |  |

| Status Affected:  | Z                                                                                                               |                     |                 |               |  |  |  |

| Encoding:         | 11                                                                                                              | 1000                | kkkk            | kkkk          |  |  |  |

| Description:      | The contents of the W register is OR'ed with the eight bit literal 'k'. The result is placed in the W register. |                     |                 |               |  |  |  |

| Words:            | 1                                                                                                               |                     |                 |               |  |  |  |

| Cycles:           | 1                                                                                                               |                     |                 |               |  |  |  |

| Q Cycle Activity: | Q1                                                                                                              | Q2                  | Q3              | Q4            |  |  |  |

|                   | Decode                                                                                                          | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |

| Example           | IORLW                                                                                                           | 0x35                |                 |               |  |  |  |

Before Instruction

After Instruction

W = 0x9A

W = 0xBF Z = 1

### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for industrial and DC CHARACTERISTICS 0°C < TA < +70°C for commercial Operating voltage VDD range as described in DC spec Section 17.1 and Section 17.2 Param Characteristic Sym Min Max Units Conditions Typ No. t Capacitive Loading Specs on Output D100 OSC2 pin рF In XT, HS and LP modes Cosc<sub>2</sub> 15 when external clock is used to drive OSC1. Cio рF D101 All I/O pins and OSC2 (in RC mode) 50 D102 Cb 400 pF SCL. SDA in I<sup>2</sup>C mode

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

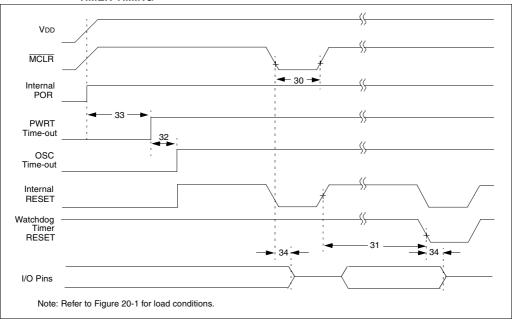

FIGURE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

FIGURE 20-5: BROWN-OUT RESET TIMING

TABLE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                | Min | Тур†      | Max | Units | Conditions                |

|---------------|-------|-----------------------------------------------|-----|-----------|-----|-------|---------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                        | 2   |           |     | μs    | VDD = 5V, -40°C to +125°C |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32            | Tost  | Oscillation Start-up Timer Period             | _   | 1024 Tosc |     | _     | TOSC = OSC1 period        |

| 33*           | Tpwrt | Power-up Timer Period                         | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34            | Tioz  | I/O Hi-impedance from MCLR Low or WDT reset   | _   | _         | 2.1 | μs    |                           |

| 35            | TBOR  | Brown-out Reset Pulse Width                   | 100 | -         | _   | μs    | VDD ≤ BVDD (D005)         |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 21.5 <u>Timing Diagrams and Specifications</u>

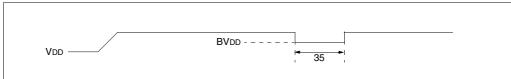

FIGURE 21-2: EXTERNAL CLOCK TIMING

TABLE 21-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                   | Min | Typ† | Max    | Units | Conditions         |

|--------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|              | Fosc  | External CLKIN Frequency         | DC  |      | 4      | MHz   | XT and RC osc mode |

|              |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|              |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|              |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|              |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|              |       | Oscillator Frequency             | DC  |      | 4      | MHz   | RC osc mode        |

|              |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|              |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|              |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1            | Tosc  | External CLKIN Period            | 250 | _    | _      | ns    | XT and RC osc mode |

|              |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

|              |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|              |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|              |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|              |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|              |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|              |       |                                  | 5   | _    | _      | μS    | LP osc mode        |

| 2            | Tcy   | Instruction Cycle Time (Note 1)  | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3*           | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|              | TosH  | Low Time                         | 2.5 | _    | _      | μS    | LP oscillator      |

|              |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4*           | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|              | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|              |       |                                  | _   | _    | 15     | ns    | HS oscillator      |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

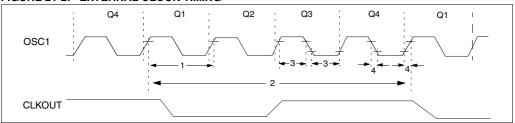

### 24.7 28-Lead Ceramic CERDIP Dual In-line with Window (300 mil)) (JW)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |       |           |       |        |           |

|--------------------------------------------------|-------------|-------|-----------|-------|--------|-----------|

|                                                  | Millimeters |       |           |       | Inches |           |

| Symbol                                           | Min         | Max   | Notes     | Min   | Max    | Notes     |

| α                                                | 0°          | 10°   |           | 0°    | 10°    |           |

| Α                                                | 3.30        | 5.84  |           | .130  | 0.230  |           |

| A1                                               | 0.38        | _     |           | 0.015 | _      |           |

| A2                                               | 2.92        | 4.95  |           | 0.115 | 0.195  |           |

| В                                                | 0.35        | 0.58  |           | 0.014 | 0.023  |           |

| B1                                               | 1.14        | 1.78  | Typical   | 0.045 | 0.070  | Typical   |

| С                                                | 0.20        | 0.38  | Typical   | 0.008 | 0.015  | Typical   |

| D                                                | 34.54       | 37.72 |           | 1.360 | 1.485  |           |

| D2                                               | 32.97       | 33.07 | Reference | 1.298 | 1.302  | Reference |

| Е                                                | 7.62        | 8.25  |           | 0.300 | 0.325  |           |

| E1                                               | 6.10        | 7.87  |           | 0.240 | 0.310  |           |

| е                                                | 2.54        | 2.54  | Typical   | 0.100 | 0.100  | Typical   |

| eA                                               | 7.62        | 7.62  | Reference | 0.300 | 0.300  | Reference |

| eB                                               | _           | 11.43 |           | _     | 0.450  |           |

| L                                                | 2.92        | 5.08  |           | 0.115 | 0.200  |           |

| N                                                | 28          | 28    |           | 28    | 28     |           |

| D1                                               | 0.13        | _     |           | 0.005 | _      |           |

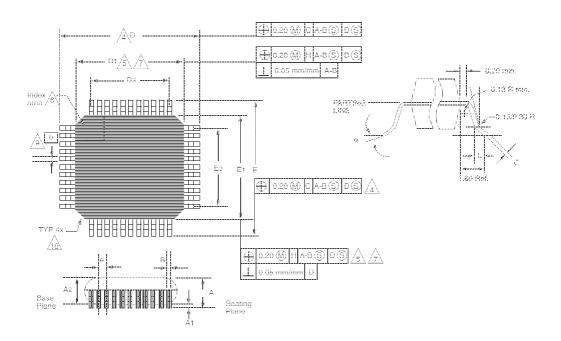

#### 24.12 44-Lead Plastic Surface Mount (MQFP 10x10 mm Body 1.6/0.15 mm Lead Form) (PQ)

Mote: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Plastic MQFP |        |             |           |        |       |           |

|-----------------------------|--------|-------------|-----------|--------|-------|-----------|

|                             |        | Millimeters |           | Inches |       |           |

| Symbol                      | Min    | Max         | Notes     | Min    | Max   | Notes     |

| α                           | 0°     | 7°          |           | 0°     | 7°    |           |

| Α                           | 2.000  | 2.350       |           | 0.078  | 0.093 |           |

| A1                          | 0.050  | 0.250       |           | 0.002  | 0.010 |           |

| A2                          | 1.950  | 2.100       |           | 0.768  | 0.083 |           |

| b                           | 0.300  | 0.450       | Typical   | 0.011  | 0.018 | Typical   |

| С                           | 0.150  | 0.180       |           | 0.006  | 0.007 |           |

| D                           | 12.950 | 13.450      |           | 0.510  | 0.530 |           |

| D1                          | 9.900  | 10.100      |           | 0.390  | 0.398 |           |

| D3                          | 8.000  | 8.000       | Reference | 0.315  | 0.315 | Reference |

| E                           | 12.950 | 13.450      |           | 0.510  | 0.530 |           |

| E1                          | 9.900  | 10.100      |           | 0.390  | 0.398 |           |

| E3                          | 8.000  | 8.000       | Reference | 0.315  | 0.315 | Reference |

| е                           | 0.800  | 0.800       |           | 0.031  | 0.032 |           |

| L                           | 0.730  | 1.030       |           | 0.028  | 0.041 |           |

| N                           | 44     | 44          |           | 44     | 44    |           |

| CP                          | 0.102  | -           |           | 0.004  | _     |           |

| Clearing Interrupts53                                | 44-Lead Plastic Surface Mount (MQFP                           |

|------------------------------------------------------|---------------------------------------------------------------|

| Clock Polarity Select bit, CKP85, 90                 | 10x10 mm Body 1.6/0.15 mm Lead Form) 302, 303                 |

| Clock Polarity, SPI Mode87                           | Device Varieties                                              |

| Clock Source Select bit, CSRC105                     | Digit Carry                                                   |

| Clocking Scheme                                      | Digit Carry bit39                                             |

| Code Examples                                        | Direct Addressing49                                           |

| Changing Between Capture Prescalers79                | F                                                             |

| Ensuring Interrupts are Globally Disabled136         | E                                                             |

| Indirect Addressing49                                | Electrical Characteristics 163, 183, 199, 215, 231, 247, 263  |

| Initializing PORTA51                                 | External Clock Synchronization, TMR0 67                       |

| Initializing PORTB53                                 | F                                                             |

| Initializing PORTC55                                 | г                                                             |

| Loading the SSPBUF Register86                        | Family of Devices                                             |

| Loading the SSPBUF register91                        | PIC12CXXX309                                                  |

| Reading a 16-bit Free-running Timer73                | PIC14C000309                                                  |

| Read-Modify-Write on an I/O Port60                   | PIC16C15X310                                                  |

| Saving Status, W, and PCLATH Registers139            | PIC16C55X31                                                   |

| Subroutine Call, Page0 to Page149                    | PIC16C5X310                                                   |

| Code Protection142                                   | PIC16C62X and PIC16C64X31                                     |

| Compare                                              | PIC16C6X                                                      |

| Block Diagram79                                      | PIC16C7XX                                                     |

| Mode79                                               | PIC16C8X313                                                   |

| Pin Configuration79                                  | PIC16C9XX313                                                  |

| Software Interrupt79                                 | PIC17CXX                                                      |

| Special Event Trigger79                              | FERR100                                                       |

| Computed GOTO48                                      | Framing Error bit, FERR106                                    |

| Configuration Bits123                                | FSR24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34                 |

| Configuration Word, Diagram124                       | Fuzzy Logic Dev. System (fuzzyTECH®-MP) 159, 16 <sup>-1</sup> |

| Connecting Two Microcontrollers87                    | ^                                                             |

| Continuous Receive Enable bit, CREN106               | G                                                             |

| CREN                                                 | General Description                                           |

| CSRC                                                 | General Purpose Registers                                     |

|                                                      | GIE3                                                          |

| D                                                    | Global Interrupt Enable bit, GIE3                             |

| D/A84, 89                                            | Graphs                                                        |

| Data/Address bit, D/A84, 89                          | PIC16C6X28                                                    |

| Data Memory                                          | PIC16C61 173                                                  |

| Organization20                                       | ш                                                             |

| Section                                              | Н                                                             |

| Data Sheet                                           | High Baud Rate Select bit, BRGH105                            |

| Compatibility307                                     | 1                                                             |

| Modifications307                                     | 1                                                             |

| What's New308                                        | I/O Ports, Section5                                           |

| DC35                                                 | I <sup>2</sup> C                                              |

| DC CHARACTERISTICS 164, 184, 200, 216, 232, 248, 264 | Addressing100                                                 |

| Development Support159                               | Addressing I <sup>2</sup> C Devices96                         |

| Development Tools                                    | Arbitration                                                   |

| Device Drawings                                      | Block Diagram99                                               |

| 18-Lead Ceramic CERDIP Dual In-line                  | Clock Synchronization98                                       |

| with Window (300 mil)296                             | Combined Format9                                              |

| 18-Lead Plastic Dual In-line (300 mil)               | I <sup>2</sup> C Operation99                                  |

| 18-Lead Plastic Surface Mount                        | I <sup>2</sup> C Overview99                                   |

| (SOIC - Wide, 300 mil Body)294                       | Initiating and Terminating Data Transfer 95                   |

| 28-Lead Ceramic CERDIP Dual In-line with             | Master Mode103                                                |

| Window (300 mil))297                                 | Master-Receiver Sequence 97                                   |

| 28-Lead Ceramic Side Brazed Dual In-Line             | Master-Transmitter Sequence                                   |

|                                                      | Mode99                                                        |

| with Window (300 mil)                                | Mode Selection99                                              |

| 28-Lead Plastic Dual In-line (300 mil)292            | Multi-master98                                                |

| 28-Lead Plastic Surface Mount                        | Multi-Master Mode                                             |

| (SOIC - Wide, 300 mil Body)                          | Reception                                                     |

| 28-Lead Plastic Surface Mount                        | Reception Timing Diagram10                                    |

| (SSOP - 209 mil Body 5.30 mm)300                     | SCL and SDA pins                                              |

| 40-Lead Ceramic CERDIP Dual In-line                  | Slave Mode                                                    |

| with Window (600 mil)298                             | START 99                                                      |

| 40-Lead Plastic Dual In-line (600 mil)               | STOP                                                          |

| 44-Lead Plastic Leaded Chip Carrier (Square)301      | 0.0.                                                          |

|      | I <sup>2</sup> C Bus Start/Stop Bits244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Oscillator Start-up Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Parallel Slave Port242                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Power-up Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | SPI Mode243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Timer0240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Timer1240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | USART Synchronous Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | (Master/Slave)246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Watchdog Timer239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIC  | 16C66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Brown-out Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Capture/Compare/PWM273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | CLKOUT and I/O270                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | External Clock269                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | I <sup>2</sup> C Bus Data279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | I <sup>2</sup> C Bus Start/Stop Bits278                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Oscillator Start-up Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Power-up Timer271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Reset271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | Timer0272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Timer1272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | USART Synchronous Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | (Master/Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |