Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-04-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.2 OPTION REGISTER

#### Applicable Devices

61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external INT interrupt, TMR0, and the weak pull-ups on PORTB. Note: To achieve a 1:1 prescaler assignment for TMR0 register, assign the prescaler to the Watchdog Timer.

#### R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU INTEDG TOCS T0SE PSA PS2 PS1 PS0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7: RBPU: PORTB Pull-up Enable bit 1 = PORTB pull-ups are disabled 0 = PORTB pull-ups are enabled by individual port latch values INTEDG: Interrupt Edge Select bit bit 6: 1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin bit 5: TOCS: TMR0 Clock Source Select bit 1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) TOSE: TMR0 Source Edge Select bit bit 4. 1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin PSA: Prescaler Assignment bit bit 3: 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0: PS2:PS0: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 000 1:1 1:2 001 1:2 1 · 4 1:4 010 1:8 1:8 011 1:16 100 1:32 1:16 1:32 101 1:64 1:64 110 1:128 1:128 111 1:256

#### FIGURE 4-10: OPTION REGISTER (ADDRESS 81h, 181h)

г

#### FIGURE 4-19: PIR1 REGISTER FOR PIC16C65/65A/R65/67 (ADDRESS 0Ch)

| R/W-0         | R/W-0                                                  | R-0                                                                                          | R-0                                    | R/W-0                                 | R/W-0                                | R/W-0         | R/W-0          |                                                                                                                                                |

|---------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|--------------------------------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PSPIF<br>bit7 | —                                                      | RCIF                                                                                         | TXIF                                   | SSPIF                                 | CCP1IF                               | TMR2IF        | TMR1IF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:        | <b>PSPIF:</b> Part $1 = A \text{ read}$<br>0 = No read | or a write o                                                                                 | peration ha                            | as taken pla                          | ace (must be<br>ce                   | cleared in s  | oftware)       |                                                                                                                                                |

| bit 6:        | Reserved:                                              | Always ma                                                                                    | intain this I                          | bit clear.                            |                                      |               |                |                                                                                                                                                |

| bit 5:        | <b>RCIF:</b> USA<br>1 = The US<br>0 = The US           | SART receiv                                                                                  | /e buffer is                           | full (cleared                         | d by reading                         | RCREG)        |                |                                                                                                                                                |

| bit 4:        | <b>TXIF:</b> USA<br>1 = The US<br>0 = The US           | SART trans                                                                                   | nit buffer is                          | empty (cle                            | eared by writ                        | ing to TXRE   | EG)            |                                                                                                                                                |

| bit 3:        | <b>SSPIF</b> : Syr<br>1 = The tra<br>0 = Waiting       | nsmission/                                                                                   | reception is                           |                                       | ag bit<br>(must be clea              | ared in softw | vare)          |                                                                                                                                                |

| bit 2:        | 0 = No TMI<br>Compare M                                | ode<br>1 register c<br>R1 register<br><u>Aode</u><br>1 register c<br>R1 register<br><u>e</u> | apture occi<br>capture oc<br>ompare ma | urred (must<br>curred<br>atch occurre | be cleared i<br>ed (must be o<br>red | ,             | oftware)       |                                                                                                                                                |

| bit 1:        | <b>TMR2IF</b> : T<br>1 = TMR2 t<br>0 = No TMI          | to PR2 mat                                                                                   | ch occurred                            | d (must be                            | bit<br>cleared in so                 | ftware)       |                |                                                                                                                                                |

| bit 0:        | <b>TMR1IF</b> : T<br>1 = TMR1 1<br>0 = No TMI          | register ove                                                                                 | rflow occur                            | red (must b                           | be cleared in                        | software)     |                |                                                                                                                                                |

| global        |                                                        | GIE (INTC                                                                                    |                                        |                                       |                                      |               |                | corresponding enable bit or the<br>rupt flag bits are clear prior to                                                                           |

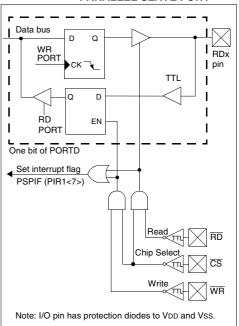

#### 5.7 Parallel Slave Port

#### Applicable Devices

#### 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

PORTD operates as an 8-bit wide parallel slave port (microprocessor port) when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input (RE0/ $\overline{\text{RD}}$ ) and  $\overline{\text{WR}}$  control input pin (RE1/ $\overline{\text{WR}}$ ).

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$  lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-11: PORTD AND PORTE AS A PARALLEL SLAVE PORT

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7                | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|-----------|-------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | (2)       | RCIF        | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9       | SREN        | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 1Ah     | RCREG | USART Re             | eceive Re | egister     |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | (2)       | RCIE        | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN        | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera    | tor Registe | ər    |       |        |        |        | 0000 0000               | 0000 0000                       |

#### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: PSPIE and PSPIF are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIE1<6> and PIR1<6> are reserved, always maintain these bits clear.

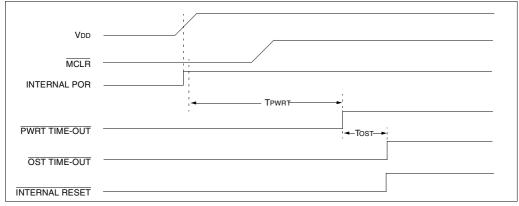

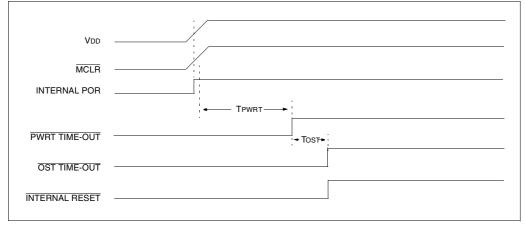

#### FIGURE 13-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

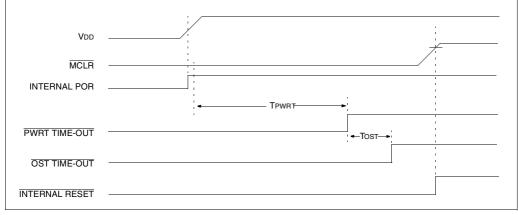

#### FIGURE 13-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### FIGURE 13-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | e    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A  | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

| NOULIN     | ĸ      |                              | · ·    | 11  | TOTO   | ĸĸĸĸ   | кккк | ~        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BCF               | Bit Clear                                                                                        | f                       |                 |                       |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] BC                                                                              | CF f,b                  |                 |                       |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$                               | 7                       |                 |                       |  |  |  |  |  |

| Operation:        | $0 \rightarrow (f < b;$                                                                          | >)                      |                 |                       |  |  |  |  |  |

| Status Affected:  | None                                                                                             |                         |                 |                       |  |  |  |  |  |

| Encoding:         | 01                                                                                               | 00bb                    | bfff            | ffff                  |  |  |  |  |  |

| Description:      | Bit 'b' in re                                                                                    | gister 'f' is           | s cleared.      |                       |  |  |  |  |  |

| Words:            | 1                                                                                                |                         |                 |                       |  |  |  |  |  |

| Cycles:           | 1                                                                                                |                         |                 |                       |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                               | Q2                      | Q3              | Q4                    |  |  |  |  |  |

|                   | Decode                                                                                           | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |

| Example           | BCF                                                                                              | FLAG_                   | REG, 7          |                       |  |  |  |  |  |

|                   | BCF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |                         |                 |                       |  |  |  |  |  |

| BTFSC             | Bit Test,                                                                                                                                      | Skip if Cl                                                                                                                                                                                                                         | ear              |                  |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] B1                                                                                                                            | FSC f,b                                                                                                                                                                                                                            |                  |                  |  |  |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                           |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

| Operation:        | skip if (f<                                                                                                                                    | skip if (f <b>) = 0</b>                                                                                                                                                                                                            |                  |                  |  |  |  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                           | None                                                                                                                                                                                                                               |                  |                  |  |  |  |  |  |  |  |  |

| Encoding:         | 01                                                                                                                                             | 10bb                                                                                                                                                                                                                               | bfff             | ffff             |  |  |  |  |  |  |  |  |

| Description:      | instruction<br>If bit 'b', in<br>instruction<br>executed i                                                                                     | If bit 'b' in register 'f' is '1' then the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0' then the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2Tcy<br>instruction. |                  |                  |  |  |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                              |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

| Cycles:           | 1(2)                                                                                                                                           |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                    |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

|                   | Decode                                                                                                                                         | Read<br>register 'f'                                                                                                                                                                                                               | Process<br>data  | No-<br>Operation |  |  |  |  |  |  |  |  |

| If Skip:          | (2nd Cyc                                                                                                                                       | le)                                                                                                                                                                                                                                |                  |                  |  |  |  |  |  |  |  |  |

|                   | Q1                                                                                                                                             | Q2                                                                                                                                                                                                                                 | Q3               | Q4               |  |  |  |  |  |  |  |  |

|                   | No-<br>Operation                                                                                                                               | No-<br>Operation                                                                                                                                                                                                                   | No-<br>Operation | No-<br>Operation |  |  |  |  |  |  |  |  |

| Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0, |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

|                   |                                                                                                                                                |                                                                                                                                                                                                                                    |                  |                  |  |  |  |  |  |  |  |  |

| BSF               | Bit Set f                                                           |                         |                 |                       |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] BS                                                 | SF f,b                  |                 |                       |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                         |                 |                       |  |  |  |  |  |  |

| Operation:        | $1 \rightarrow (f < b >)$                                           |                         |                 |                       |  |  |  |  |  |  |

| Status Affected:  | None                                                                |                         |                 |                       |  |  |  |  |  |  |

| Encoding:         | 01                                                                  | 01bb                    | bfff            | ffff                  |  |  |  |  |  |  |

| Description:      | Bit 'b' in re                                                       | gister 'f' is           | s set.          |                       |  |  |  |  |  |  |

| Words:            | 1                                                                   |                         |                 |                       |  |  |  |  |  |  |

| Cycles:           | 1                                                                   |                         |                 |                       |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                  | Q2                      | Q3              | Q4                    |  |  |  |  |  |  |

|                   | Decode                                                              | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |  |

| Example           | BSF                                                                 | FLAG_F                  | REG, 7          |                       |  |  |  |  |  |  |

|                   | Before Instruction<br>FLAG REG = 0x0A                               |                         |                 |                       |  |  |  |  |  |  |

|                   | After Inst                                                          | ruction                 |                 |                       |  |  |  |  |  |  |

|                   |                                                                     | FLAG_RE                 | EG = 0x8A       | 4                     |  |  |  |  |  |  |

PC = address TRUE if FLAG<1>=1, PC = address FALSE

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

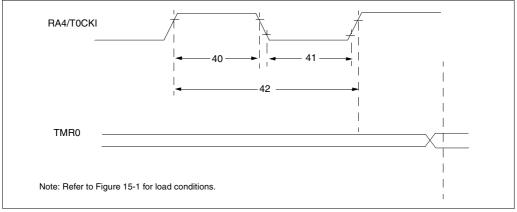

### FIGURE 15-5: TIMER0 EXTERNAL CLOCK TIMINGS

#### TABLE 15-5: TIMER0 EXTERNAL CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                                             | Тур† | Max | Units | Conditions         |

|------------------|------|------------------------|----------------|-------------------------------------------------|------|-----|-------|--------------------|

| 40*              | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5Tcy + 20                                     | _    | _   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | _   | ns    | parameter 42       |

| 41*              | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TCY + 20                                     | —    | —   |       | Must also meet     |

|                  |      |                        | With Prescaler | 10                                              | —    | —   | ns    | parameter 42       |

| 42*              | Tt0P | T0CKI Period           | No Prescaler   | TCY + 40                                        | _    | _   |       | N = prescale value |

|                  |      |                        | With Prescaler | Greater of:<br>20 ns or<br><u>Tcy + 40</u><br>N | _    | _   | ns    | (2, 4,, 256)       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

| DC CHA       | RACTERISTICS                                                            | Operatir<br>Operatir | ng temper | ature    | -40°C<br>0°C | È`≤TA<br>≤TA | so otherwise stated)<br>$\Delta \le +85^{\circ}$ C for industrial and<br>$\Delta \le +70^{\circ}$ C for commercial<br>ed in DC spec Section 17.1 |

|--------------|-------------------------------------------------------------------------|----------------------|-----------|----------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                                          | Sym                  | Min       | Тур<br>† | Max          | Units        | Conditions                                                                                                                                       |

| D100         | Capacitive Loading Specs on Output<br>Pins<br>OSC2 pin                  | Cosc2                | -         | -        | 15           |              | In XT, HS and LP modes<br>when external clock is used to<br>drive OSC1.                                                                          |

| D101<br>D102 | All I/O pins and OSC2 (in RC mode)<br>SCL, SDA in I <sup>2</sup> C mode | Cio<br>Cb            | -         | -        | 50<br>400    | pF<br>pF     |                                                                                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

|  | Applicable Devices | 61 | 62 | 62A | <b>B62</b> | 63 | B63 | 64 | 64A | <b>R64</b> | 65 | 65A | <b>B65</b> | 66 | 67 |

|--|--------------------|----|----|-----|------------|----|-----|----|-----|------------|----|-----|------------|----|----|

|--|--------------------|----|----|-----|------------|----|-----|----|-----|------------|----|-----|------------|----|----|

|       |                                    | Standa  | rd Operat | ina ( | Conditior | ns (unle | ess otherwise stated)                                                   |

|-------|------------------------------------|---------|-----------|-------|-----------|----------|-------------------------------------------------------------------------|

|       |                                    |         | ng temper | •     |           | •        | TA $\leq$ +125°C for extended,                                          |

|       | ARACTERISTICS                      |         |           |       | -40°      | C ≤      | TA $\leq$ +85°C for industrial and                                      |

|       | ANACIENISTICS                      |         |           |       | 0°C       | -        | TA $\leq$ +70°C for commercial                                          |

|       |                                    |         |           | VDD   | range as  | descri   | bed in DC spec Section 18.1 and                                         |

|       |                                    | Section | 18.2      |       |           |          |                                                                         |

| Param | Characteristic                     | Sym     | Min       | Тур   | Max       | Units    | Conditions                                                              |

| No.   |                                    |         |           | †     |           |          |                                                                         |

|       | Output High Voltage                |         |           |       |           |          |                                                                         |

| D090  | I/O ports (Note 3)                 | Vон     | VDD-0.7   | -     | -         | V        | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

| D090A |                                    |         | VDD-0.7   | -     | -         | V        | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092  | OSC2/CLKOUT (RC osc config)        |         | VDD-0.7   | -     | -         | V        | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D092A |                                    |         | VDD-0.7   | -     | -         | V        | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D150* | Open-Drain High Voltage            | Vod     | -         | -     | 14        | V        | RA4 pin                                                                 |

|       | Capacitive Loading Specs on Out-   |         |           |       |           |          |                                                                         |

|       | put Pins                           |         |           |       |           |          |                                                                         |

| D100  | OSC2 pin                           | Cosc2   | -         | -     | 15        | pF       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101  | All I/O pins and OSC2 (in RC mode) | Cio     | -         | -     | 50        | pF       |                                                                         |

| D102  | SCL, SDA in I <sup>2</sup> C mode  | Cb      | -         | -     | 400       | pF       |                                                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C6X be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

#### Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

### 18.5 <u>Timing Diagrams and Specifications</u>

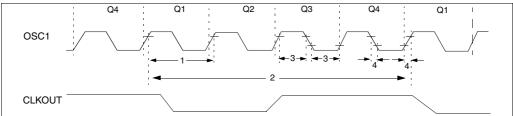

#### FIGURE 18-2: EXTERNAL CLOCK TIMING

#### TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| arameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|-----------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                 | Fosc  | External CLKIN Frequency         |     |      |        |       |                    |

|                 |       | (Note 1)                         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                 |       |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                 |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                 |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                 |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                 |       | Oscillator Frequency             | DC  | -    | 4      | MHz   | RC osc mode        |

|                 |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                 |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                 |       |                                  | 5   | _    | 200    | kHz   | LP osc mode        |

| 1               | Tosc  | External CLKIN Period            | 250 | -    | —      | ns    | XT and RC osc mode |

|                 |       | (Note 1)                         | 250 | _    | —      | ns    | HS osc mode (-04)  |

|                 |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                 |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                 |       |                                  | 5   | _    | —      | μs    | LP osc mode        |

|                 |       | Oscillator Period                | 250 | _    | —      | ns    | RC osc mode        |

|                 |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                 |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                 |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                 |       |                                  | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                 |       |                                  | 5   | _    | —      | μs    | LP osc mode        |

| 2               | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc       |

| 3               | TosL, | External Clock in (OSC1) High or | 100 | —    | —      | ns    | XT oscillator      |

|                 | TosH  | Low Time                         | 2.5 | —    | —      | μs    | LP oscillator      |

|                 |       |                                  | 15  | _    | —      | ns    | HS oscillator      |

| 4               | TosR, | External Clock in (OSC1) Rise or | —   | -    | 25     | ns    | XT oscillator      |

|                 | TosF  | Fall Time                        | —   | —    | 50     | ns    | LP oscillator      |

|                 |       |                                  | —   | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

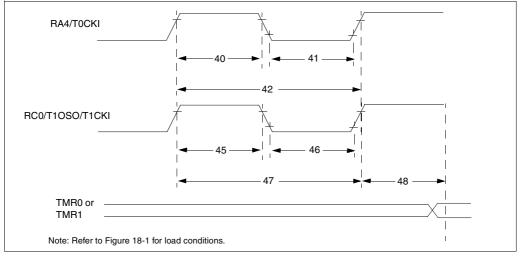

#### FIGURE 18-6: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TABLE 18-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                 |                      |                    | Min                                              | Typ† | Мах   | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|----------------------|--------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H      | H T0CKI High Pulse Width                       |                      | No Prescaler       | 0.5TCY + 20                                      | —    | -     | ns    | Must also meet                     |

|              |           |                                                |                      | With Prescaler     | 10                                               | —    | _     | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth                | No Prescaler       | 0.5TCY + 20                                      | -    | -     | ns    | Must also meet                     |

|              |           |                                                |                      | With Prescaler     | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                      | No Prescaler       | TCY + 40                                         | —    | —     | ns    |                                    |

|              |           |                                                |                      | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | -     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, F       | Prescaler = 1      | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,         | PIC16 <b>C</b> 6X  | 15                                               | _    | —     | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 6X | 25                                               | -    | —     | ns    |                                    |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 30                                               | —    | —     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 50                                               | —    | -     | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, F       | rescaler = 1       | 0.5TCY + 20                                      | _    | —     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,         | PIC16 <b>C</b> 6X  | 15                                               | —    | _     | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 6X | 25                                               | -    | —     | ns    |                                    |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 30                                               | -    | —     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 50                                               | -    | -     | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous          | PIC16 <b>C</b> 6X  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                | Asynchronous         | PIC16 <b>C</b> 6X  | 60                                               | —    | -     | ns    |                                    |

|              |           |                                                |                      | PIC16 <b>LC</b> 6X | 100                                              | -    | —     | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                      |                    | DC                                               | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                            | clock edge to tir    | ner increment      | 2Tosc                                            | _    | 7Tosc | —     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

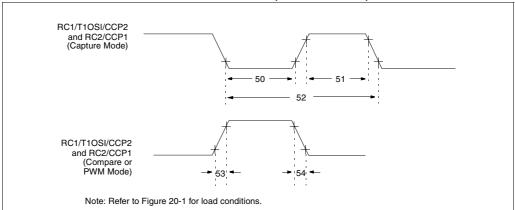

#### FIGURE 20-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

TABLE 20-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym                | Characteristic                   |                        |                        | Min                   | Тур† | Max | Units | Conditions                         |

|------------------|--------------------|----------------------------------|------------------------|------------------------|-----------------------|------|-----|-------|------------------------------------|

| 50*              | TccL               | CCP1 and CCP2                    | No Prescaler           |                        | 0.5Tcy + 20           | _    | _   | ns    |                                    |

|                  |                    | input low time                   | With Prescaler         | PIC16 <b>C</b> 63/65A  | 10                    | —    |     | ns    |                                    |

|                  |                    |                                  |                        | PIC16LC63/65A          | 20                    | —    |     | ns    |                                    |

| 51*              | TccH CCP1 and CCP2 |                                  | No Prescaler           |                        | 0.5TCY + 20           | -    |     | ns    |                                    |

|                  |                    | input high time                  | With Prescaler         | PIC16 <b>C</b> 63/65A  | 10                    | —    |     | ns    |                                    |

|                  |                    |                                  |                        | PIC16 <b>LC</b> 63/65A | 20                    | -    |     | ns    |                                    |

| 52*              | TccP               | CCP1 and CCP2 input period       |                        |                        | <u>3Tcy + 40</u><br>N | -    |     | ns    | N = prescale value<br>(1,4, or 16) |

| 53*              | TccR               | CCP1 and CCP2 o                  | utput rise time        | PIC16 <b>C</b> 63/65A  | _                     | 10   | 25  | ns    |                                    |

|                  |                    | PIC16LC63/65                     | PIC16 <b>LC</b> 63/65A | _                      | 25                    | 45   | ns  |       |                                    |

| 54*              | TccF               | F CCP1 and CCP2 output fall time |                        | PIC16 <b>C</b> 63/65A  | _                     | 10   | 25  | ns    |                                    |

|                  |                    |                                  |                        | PIC16 <b>LC</b> 63/65A | _                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

#### 21.1 DC Characteristics: PIC16CR63/R65-04 (Commercial, Industrial) PIC16CR63/R65-10 (Commercial, Industrial) PIC16CR63/R65-20 (Commercial, Industrial)

| DC CH                 |                                                                  | <b>Standa</b> ı<br>Operatir |            | •                  |                | )°C ≤          | unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------|-----------------------------|------------|--------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym                         | Min        | Тур†               | Max            | Units          | Conditions                                                                                                                                                                                                                                                                                                                      |

| D001<br>D001A         | Supply Voltage                                                   | Vdd                         | 4.0<br>4.5 |                    | 5.5<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                         |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr                         | -          | 1.5                | -              | V              |                                                                                                                                                                                                                                                                                                                                 |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR                        | -          | Vss                | -              | V              | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                       |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD                        | 0.05       | -                  | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                       |

| D005                  | Brown-out Reset Voltage                                          | Bvdd                        | 3.7        | 4.0                | 4.3            | V              | BODEN configuration bit is enabled                                                                                                                                                                                                                                                                                              |

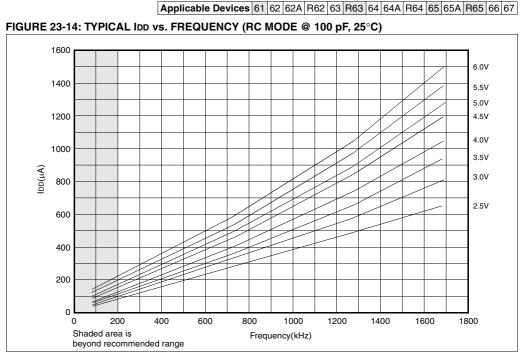

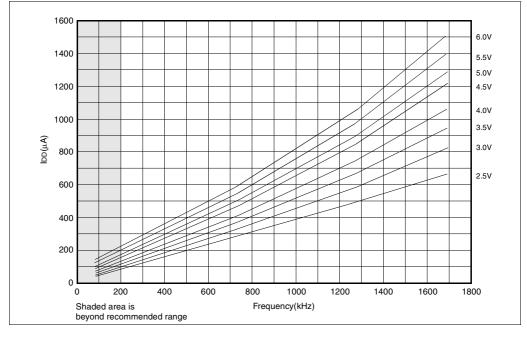

| D010                  | Supply Current (Note 2, 5)                                       | IDD                         | -          | 2.7                | 5              | mA~            | XT, RC, osc config Fosc = 4 MHz,<br>VDD = 5:5V (Note 4)                                                                                                                                                                                                                                                                         |

| D013                  |                                                                  |                             | -          | 10                 | 20             | mA             | HS osc config<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                                                                      |

| D015*                 | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR               | -          | 350                | 425            | μA             | BOR enabled, VDD = 5.0V                                                                                                                                                                                                                                                                                                         |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3, 5)                                |                             | -          | 10.5<br>1.5<br>1.5 | 42<br>16<br>19 | μΑ<br>μΑ<br>μΑ | $\label{eq:VDD} \begin{array}{l} V\text{DD} = 4.0\text{V}, \text{WDT enabled}, -40^{\circ}\text{C to} +85^{\circ}\text{C} \\ \text{VDD} = 4.0\text{V}, \text{WDT disabled}, -0^{\circ}\text{C to} +70^{\circ}\text{C} \\ \text{VDD} = 4.0\text{V}, \text{WDT disabled}, -40^{\circ}\text{C to} +85^{\circ}\text{C} \end{array}$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                              |                             | -          | 350                | 425            | μA             | BOR enabled, VDD = 5.0V                                                                                                                                                                                                                                                                                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 50, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VoD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- $OSC1 \neq external Square wave, from rail to rail; all I/O pins tristated, pulled to VDD, MCLR \neq VDD; WDT enabled/disabled as specified.$

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

Applicable Devices 61 62 62A R62 63 R63 64 64A R64 65 65A R65 66 67

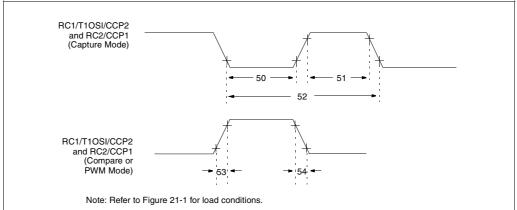

#### FIGURE 21-7: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 21-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym                | Characteristic                 |                 | Min                    | Тур†                  | Max | Units | Conditions |                                    |

|--------------|--------------------|--------------------------------|-----------------|------------------------|-----------------------|-----|-------|------------|------------------------------------|

| 50*          | TccL CCP1 and CCP2 |                                | No Prescaler    |                        | 0.5TCY + 20           | —   | _     | ns         |                                    |

|              |                    | input low time With Presca     |                 | PIC16CR63/R65          | 10                    | —   | —     | ns         |                                    |

|              |                    |                                |                 | PIC16LCR63/R65         | 20                    | -   | _     | ns         |                                    |

| 51*          | TccH CCP1 and CCP2 |                                | No Prescaler    |                        | 0.5TCY + 20           | —   | —     | ns         |                                    |

|              |                    | input high time                | With Prescaler  | PIC16CR63/R65          | 10                    | _   | _     | ns         |                                    |

|              |                    |                                |                 | PIC16LCR63/R65         | 20                    | -   | _     | ns         |                                    |

| 52*          | TccP               | CCP1 and CCP2 ir               | put period      |                        | <u>3Tcy + 40</u><br>N | -   | —     | ns         | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR               | CCP1 and CCP2 o                | utput rise time | PIC16CR63/R65          | _                     | 10  | 25    | ns         |                                    |

|              |                    |                                |                 |                        | _                     | 25  | 45    | ns         |                                    |

| 54*          | TccF               | CCP1 and CCP2 output fall time |                 | PIC16 <b>CR</b> 63/R65 | —                     | 10  | 25    | ns         |                                    |

|              |                    |                                |                 | PIC16LCR63/R65         | —                     | 25  | 45    | ns         |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Data based on matrix samples. See first page of this section for details.

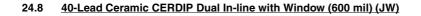

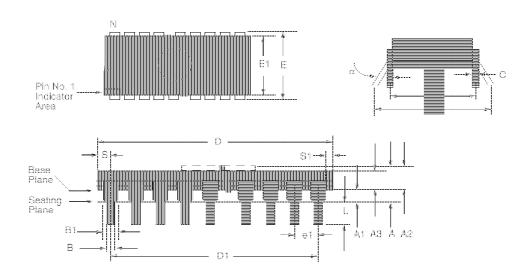

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |        |             |           |        |       |           |  |  |

|--------------------------------------------------|--------|-------------|-----------|--------|-------|-----------|--|--|

|                                                  |        | Millimeters |           | Inches |       |           |  |  |

| Symbol                                           | Min    | Мах         | Notes     | Min    | Мах   | Notes     |  |  |

| α                                                | 0°     | 10°         |           | 0°     | 10°   |           |  |  |

| А                                                | 4.318  | 5.715       |           | 0.170  | 0.225 |           |  |  |

| A1                                               | 0.381  | 1.778       |           | 0.015  | 0.070 |           |  |  |

| A2                                               | 3.810  | 4.699       |           | 0.150  | 0.185 |           |  |  |

| A3                                               | 3.810  | 4.445       |           | 0.150  | 0.175 |           |  |  |

| В                                                | 0.355  | 0.585       |           | 0.014  | 0.023 |           |  |  |

| B1                                               | 1.270  | 1.651       | Typical   | 0.050  | 0.065 | Typical   |  |  |

| С                                                | 0.203  | 0.381       | Typical   | 0.008  | 0.015 | Typical   |  |  |

| D                                                | 51.435 | 52.705      |           | 2.025  | 2.075 |           |  |  |

| D1                                               | 48.260 | 48.260      | Reference | 1.900  | 1.900 | Reference |  |  |

| E                                                | 15.240 | 15.875      |           | 0.600  | 0.625 |           |  |  |

| E1                                               | 12.954 | 15.240      |           | 0.510  | 0.600 |           |  |  |

| e1                                               | 2.540  | 2.540       | Reference | 0.100  | 0.100 | Reference |  |  |

| eA                                               | 14.986 | 16.002      | Typical   | 0.590  | 0.630 | Typical   |  |  |

| eB                                               | 15.240 | 18.034      |           | 0.600  | 0.710 |           |  |  |

| L                                                | 3.175  | 3.810       |           | 0.125  | 0.150 |           |  |  |

| Ν                                                | 40     | 40          |           | 40     | 40    |           |  |  |

| S                                                | 1.016  | 2.286       |           | 0.040  | 0.090 |           |  |  |

| S1                                               | 0.381  | 1.778       |           | 0.015  | 0.070 |           |  |  |

#### 24.13 44-Lead Plastic Surface Mount (TQFP 10x10 mm Body 1.0/0.10 mm Lead Form) (TQ)

|        |       | Packag      | e Group: Plast | ic TQFP |        |       |

|--------|-------|-------------|----------------|---------|--------|-------|

|        |       | Millimeters |                |         | Inches |       |

| Symbol | Min   | Max         | Notes          | Min     | Max    | Notes |

| A      | 1.00  | 1.20        |                | 0.039   | 0.047  |       |

| A1     | 0.05  | 0.15        |                | 0.002   | 0.006  |       |

| A2     | 0.95  | 1.05        |                | 0.037   | 0.041  |       |

| D      | 11.75 | 12.25       |                | 0.463   | 0.482  |       |

| D1     | 9.90  | 10.10       |                | 0.390   | 0.398  |       |

| E      | 11.75 | 12.25       |                | 0.463   | 0.482  |       |

| E1     | 9.90  | 10.10       |                | 0.390   | 0.398  |       |

| L      | 0.45  | 0.75        |                | 0.018   | 0.030  |       |

| е      | 0.80  | BSC         |                | 0.03    | I BSC  |       |

| b      | 0.30  | 0.45        |                | 0.012   | 0.018  |       |

| b1     | 0.30  | 0.40        |                | 0.012   | 0.016  |       |

| С      | 0.09  | 0.20        |                | 0.004   | 0.008  |       |

| c1     | 0.09  | 0.16        |                | 0.004   | 0.006  |       |

| Ν      | 44    | 44          |                | 44      | 44     |       |

| Θ      | 0°    | <b>7</b> °  |                | 0°      | 7°     |       |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

3: This outline conforms to JEDEC MS-026.

### **PIN COMPATIBILITY**

Devices that have the same package type and VDD, VSs and  $\overline{\text{MCLR}}$  pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

| Pin Compatible Devices                                                                                                                                                                                                                                                                                                                                                                      | Package           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PIC12C508, PIC12C509, PIC12C671, PIC12C672                                                                                                                                                                                                                                                                                                                                                  | 8-pin             |

| PIC16C154, PIC16CR154, PIC16C156,<br>PIC16CR156, PIC16C158, PIC16CR158,<br>PIC16C52, PIC16C54, PIC16C54A,<br>PIC16C56,<br>PIC16C58A, PIC16CR58A,<br>PIC16C554, PIC16CR58A,<br>PIC16C554, PIC16C556, PIC16C558<br>PIC16C620, PIC16C621, PIC16C622<br>PIC16C641, PIC16C642, PIC16C661, PIC16C662<br>PIC16C710, PIC16C71, PIC16C711, PIC16C715<br>PIC16F83, PIC16CR83,<br>PIC16F84A, PIC16CR84 | 18-pin,<br>20-pin |

| PIC16C55, PIC16C57, PIC16CR57B                                                                                                                                                                                                                                                                                                                                                              | 28-pin            |

| PIC16CR62, PIC16C62A, PIC16C63, PIC16CR63,<br>PIC16C66, PIC16C72, PIC16C73A, PIC16C76                                                                                                                                                                                                                                                                                                       | 28-pin            |

| PIC16CR64, PIC16C64A, PIC16C65A,<br>PIC16CR65, PIC16C67, PIC16C74A, PIC16C77                                                                                                                                                                                                                                                                                                                | 40-pin            |

| PIC17CR42, PIC17C42A,<br>PIC17C43, PIC17CR43, PIC17C44                                                                                                                                                                                                                                                                                                                                      | 40-pin            |

| PIC16C923, PIC16C924                                                                                                                                                                                                                                                                                                                                                                        | 64/68-pin         |