Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | ·                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-04i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

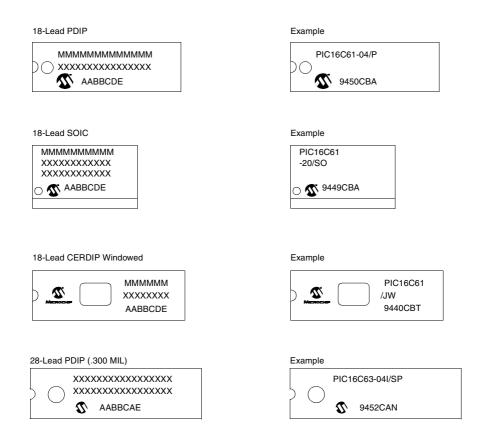

### 2.0 PIC16C6X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C6X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C6X family of devices, there are four device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**64. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC64. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CR**, as in PIC16**CR**64. These devices have ROM program memory and operate over the standard voltage range.

- 4. LCR, as in PIC16LCR64. These devices have ROM program memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C6X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

ROM devices do not allow serialization information in the program memory space. The user may have this information programmed in the data memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

| Address              | Name    | Bit 7              | Bit 6                                                    | Bit 5                     | Bit 4          | Bit 3       | Bit 2       | Bit 1        | Bit 0              | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|--------------------|----------------------------------------------------------|---------------------------|----------------|-------------|-------------|--------------|--------------------|--------------------------|------------------------------------------------|

| Bank 1               |         |                    | •                                                        |                           |                |             |             |              |                    |                          |                                                |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location                                            | uses conte                | nts of FSR to  | address dat | a memory (n | ot a physica | register)          | 0000 0000                | 0000 0000                                      |

| 81h                  | OPTION  | RBPU               | INTEDG                                                   | TOCS                      | T0SE           | PSA         | PS2         | PS1          | PS0                | 1111 1111                | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                                            | Least Sig                 | nificant Byte  |             |             |              |                    | 0000 0000                | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                                       | RP0                       | TO             | PD          | z           | DC           | С                  | 0001 1xxx                | 000q quui                                      |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ac                                              | Idress point              | er             |             |             |              |                    | xxxx xxxx                | սսսս սսսս                                      |

| 85h                  | TRISA   | —                  | —                                                        | PORTA Da                  | ta Direction R | egister     |             |              |                    | 11 1111                  | 11 1111                                        |

| 86h                  | TRISB   | PORTB Dat          | ta Direction F                                           | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 87h                  | TRISC   | PORTC Da           | ta Direction I                                           | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 88h                  | TRISD   | PORTD Da           | ta Direction I                                           | Register                  |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 89h                  | TRISE   | IBF                | OBF                                                      | IBOV                      | PSPMODE        | —           | PORTE Da    | ta Direction | Bits               | 0000 -111                | 0000 -111                                      |

| 8Ah <sup>(1,2)</sup> | PCLATH  | _                  | Write Buffer for the upper 5 bits of the Program Counter |                           |                |             |             |              | ounter             | 0 0000                   | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                                     | TOIE                      | INTE           | RBIE        | TOIF        | INTF         | RBIF               | 0000 000x                | 0000 0001                                      |

| 8Ch                  | PIE1    | PSPIE              | (6)                                                      | RCIE                      | TXIE           | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE             | 0000 0000                | 0000 0000                                      |

| 8Dh                  | PIE2    | _                  | —                                                        | —                         | _              | —           | _           | _            | CCP2IE             | 0                        | (                                              |

| 8Eh                  | PCON    | _                  | —                                                        | —                         | _              | —           | _           | POR          | BOR <sup>(4)</sup> | dd                       | ui                                             |

| 8Fh                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | _                        | —                                              |

| 90h                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | _                        | _                                              |

| 91h                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | _                        | _                                              |

| 92h                  | PR2     | Timer2 Peri        | iod Register                                             |                           |                |             |             |              |                    | 1111 1111                | 1111 1111                                      |

| 93h                  | SSPADD  | Synchronou         | us Serial Por                                            | t (I <sup>2</sup> C mode) | Address Reg    | gister      |             |              |                    | 0000 0000                | 0000 0000                                      |

| 94h                  | SSPSTAT | —                  | _                                                        | D/A                       | Р              | S           | R/W         | UA           | BF                 | 00 0000                  | 00 0000                                        |

| 95h                  | -       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | -                        | —                                              |

| 96h                  | —       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | -                        | —                                              |

| 97h                  | -       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | -                        | —                                              |

| 98h                  | TXSTA   | CSRC               | TX9                                                      | TXEN                      | SYNC           | —           | BRGH        | TRMT         | TX9D               | 0000 -010                | 0000 -010                                      |

| 99h                  | SPBRG   | Baud Rate          | Generator R                                              | egister                   |                |             |             |              |                    | 0000 0000                | 0000 0000                                      |

| 9Ah                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | -                        | —                                              |

| 9Bh                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | _                        | —                                              |

| 9Ch                  | —       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | —                        | —                                              |

| 9Dh                  | —       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | -                        | —                                              |

| 9Eh                  | —       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    | —                        | _                                              |

| 9Fh                  | _       | Unimpleme          | nted                                                     |                           |                |             |             |              |                    |                          |                                                |

TABLE 4-5: SPECIAL FUNCTION REGISTERS FOR THE PIC16C65/65A/R65 (Cont.'d)

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the Program Counter (PC) is not directly accessible. PCLATH is a holding register for the PC whose contents are transferred to the upper byte of the program counter. (PC<12:8>)

3: Other (non power-up) resets include external reset through MCLR and the Watchdog Timer reset.

4: The BOR bit is reserved on the PIC16C65, always maintain this bit set.

5: The IRP and RP1 bits are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

6: PIE1<6> and PIR1<6> are reserved on the PIC16C65/65A/R65, always maintain these bits clear.

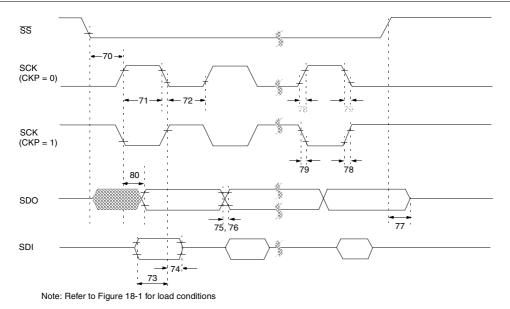

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

- Note: When the SPI is in Slave Mode with SS pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the SS pin is set to VDD.

- Note: If the SPI is used in Slave Mode with CKE = '1', then the SS pin control must be enabled.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

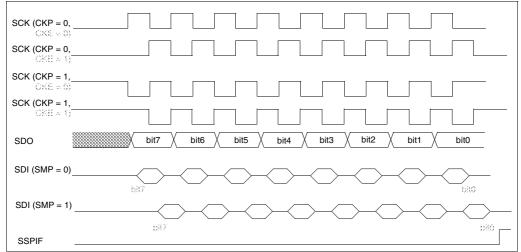

#### FIGURE 11-11: SPI MODE TIMING, MASTER MODE (PIC16C66/67)

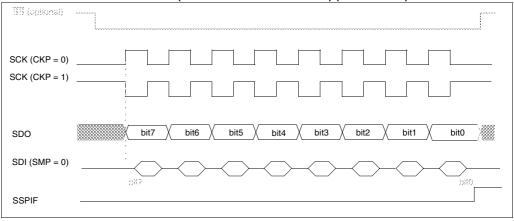

#### FIGURE 11-12: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) (PIC16C66/67)

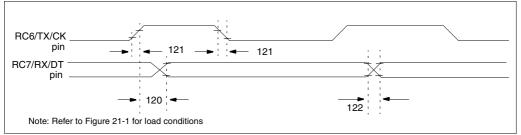

#### 12.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous Mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) bit or enable bit CREN (RCSTA<4>). Data is sampled on the DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until bit CREN is cleared. If both the bits are set then bit CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register, i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit, OERR (RCSTA<1>) is set. The word in the RSR register will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun error bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value. Therefore it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old RX9D bit information.

Steps to follow when setting up Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 5. If 9-bit reception is desired, then set bit RX9.

- If a single reception is required, set enable bit SREN. For continuous reception set enable bit CREN.

- 7. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing enable bit CREN.

|         | 2-J. I                                 |                      |           |         |       |       |        | 1000 100 |        |                         |                                 |

|---------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|----------|--------|-------------------------|---------------------------------|

| Address | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1    | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | (2)       | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF   | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h     | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | —     | FERR   | OERR     | RX9D   | 0000 -00x               | 0000 -00x                       |

| 1Ah     | RCREG                                  | USART Re             | eceive Re | egister |       |       |        |          |        | 0000 0000               | 0000 0000                       |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | (2)       | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE   | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h     | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT     | TX9D   | 0000 -010               | 0000 -010                       |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |          |        | 0000 0000               | 0000 0000                       |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: PSPIF and PSPIE are reserved on the PIC16C63/R63/66, always maintain these bits clear.

2: PIR1<6> and PIE1<6> are reserved, always maintain these bits clear.

#### TABLE 14-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | e    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        | LSb    |      | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A  | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

| NOULIN     | ĸ      |                              | · ·    | 11  | TOTO   | ĸĸĸĸ   | кккк | ~        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRF              | Clear f                                                               |                         |                 |                       |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|

| Syntax:           | [label] C                                                             | LRF f                   |                 |                       |

| Operands:         | $0 \le f \le 12$                                                      | 7                       |                 |                       |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | 1                       |                 |                       |

| Status Affected:  | Z                                                                     |                         |                 |                       |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |

| Description:      | The conter<br>and the Z                                               |                         | ster 'f' are    | cleared               |

| Words:            | 1                                                                     |                         |                 |                       |

| Cycles:           | 1                                                                     |                         |                 |                       |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |

| Example           | CLRF                                                                  | FLAG                    | _REG            |                       |

|                   | Before In                                                             |                         |                 |                       |

|                   | After Inst                                                            | FLAG_RE                 | EG =            | 0x5A                  |

|                   |                                                                       | FLAG RE                 | EG =            | 0x00                  |

|                   |                                                                       | Z                       | =               | 1                     |

| CLRW                                                                | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                                            |                                                              |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|

| Syntax:                                                             | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLRW                                                      |                                                            |                                                              |

| Operands:                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |

| Operation:                                                          | $00h \rightarrow (N 1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V)                                                        |                                                            |                                                              |

| Status Affected:                                                    | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Encoding:                                                           | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0001                                                      | 0xxx                                                       | xxxx                                                         |

| Description:                                                        | W register<br>set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | is cleared                                                | . Zero bit (                                               | (Z) is                                                       |

| Words:                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Cycles:                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |                                                            |                                                              |

| Q Cycle Activity:                                                   | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q2                                                        | Q3                                                         | Q4                                                           |

|                                                                     | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No-<br>Operation                                          | Process<br>data                                            | Write to<br>W                                                |

| Example                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |                                                            |                                                              |

|                                                                     | Before In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | struction                                                 |                                                            |                                                              |

|                                                                     | After Inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 0x5A                                                       |                                                              |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           | 0x00                                                       |                                                              |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z =                                                       | 1                                                          |                                                              |

| CLRWDT                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tobdog -                                                  | Finan                                                      |                                                              |

| Syntax:                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLRWD1                                                    |                                                            |                                                              |