Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

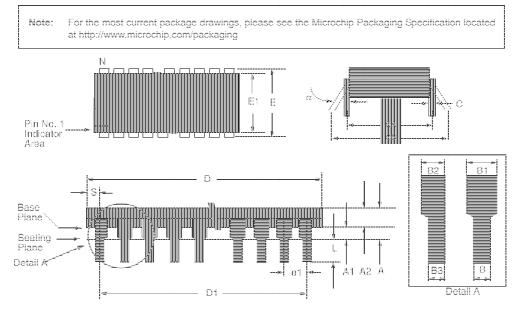

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c64a-04i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| MCLR/VPP     1     I/P     ST     Master clear reset input or programming voltage input<br>an active low reset to the device.       MCLR/VPP     1     I/P     ST     Master clear reset input or programming voltage input<br>an active low reset to the device.       RA0     2     I/O     TTL       RA1     3     I/O     TTL       RA2     4     I/O     TTL       RA3     5     I/O     TTL       RA3     5     I/O     TTL       RA4 can also be the clock input to the Timer0 tir<br>Output is open drain type.     RA4 can also be the clock input to the Timer0 tir<br>Output is open drain type.       RA5/SS     7     I/O     TTL     RA5 can also be the slave select for the synchr<br>port.       RB0/INT     21     I/O     TTL/ST <sup>40</sup> RB0 can also be the external interrupt pin.       RB2     23     I/O     TTL     RB0 can also be the external interrupt pin.       RB4     25     I/O     TTL     Interrupt on change pin.       RB6     27     I/O     TTL     Interrupt on change pin.       RB6     27     I/O     TTL     Interrupt on change pin.       RC1/TLOS( <sup>11</sup> //CCP2 <sup>(2)</sup> )     12     I/O     ST     RC0 can also be the Timer1 oscillator uppuf <sup>1</sup><br>clock input.       RC2/CCP1     13     I/O     ST     RC1 can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin Name                                      | Pin# | Pin Type | Buffer<br>Type         | Description                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

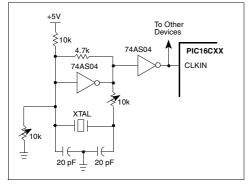

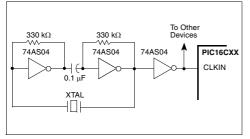

| MCLR/VPP     1     I/P     ST     Master clear reset input or programming voltage input an active low reset to the device.       MCLR/VPP     1     I/P     ST     Master clear reset input or programming voltage input an active low reset to the device.       RA0     2     I/O     TTL       RA1     3     I/O     TTL       RA2     4     I/O     TTL       RA3     5     I/O     TTL       RA3     5     I/O     TTL       RA4     6     I/O     ST       RA4/T0CKI     6     I/O     TTL       RA5/SS     7     I/O     TTL       RA5/SS     7     I/O     TTL       RA5/SS     7     I/O     TTL       RB0/INT     21     I/O     TTL/ST <sup>(4)</sup> RB1     22     I/O     TTL       RB2     23     I/O     TTL       RB4     25     I/O     TTL       RB5     26     I/O     TTL       RB6     27     I/O     TTL       RB6     27     I/O     TTL       RC0/T1OSO <sup>(1)</sup> /T1CKI     11     I/O       RC1/T1OSO <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12     I/O       RC2/CCP1     13     I/O       RC2/CCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OSC1/CLKIN                                    | 9    | I        | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                |

| MCLR/VPP     1     I/P     ST     Master clear reset input or programming voltage input<br>an active low reset to the device.       RA0     2     I/O     TTL       RA1     3     I/O     TTL       RA2     4     I/O     TTL       RA3     5     I/O     TTL       RA4/T0CKI     6     I/O     ST     RA4 can also be the clock input to the Timer0 tin<br>Output is open drain type.       RA5/SS     7     I/O     TTL     RA5 can also be the slave select for the synchr<br>port.       RB0/INT     21     I/O     TTL/ST <sup>40</sup> RB0 can also be the slave select for the synchr<br>port.       RB0/INT     21     I/O     TTL/ST <sup>40</sup> RB0 can also be the external interrupt pin.       RB2     23     I/O     TTL     RB0 can also be the external interrupt pin.       RB3     24     I/O     TTL     Interrupt on change pin.       RB6     27     I/O     TTL     Interrupt on change pin.       RB6     27     I/O     TTL/ST <sup>69</sup> Interrupt on change pin. Serial programming dat       RC0/T1CS0 <sup>(1)</sup> /TCKI     11     I/O     ST     RC2 can also be the Timer1 oscillator uppuf <sup>10</sup><br>clock input.       RC1/TLOS( <sup>11</sup> //CCP2 <sup>(2)</sup> )     12     I/O     ST     RC2 can also be the Serial programming dat       RC2/CCP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OSC2/CLKOUT                                   | 10   | 0        | _                      | Oscillator crystal output. Connects to crystal or resonator in crys                                                                  |

| MICLIVIP       Annow Strugge year         RA0       2       I/O       TTL         RA1       3       I/O       TTL         RA2       4       I/O       TTL         RA3       5       I/O       TTL         RA4/TOCKI       6       I/O       ST       RA4 can also be the clock input to the Timer0 timer 0 t |                                               |      |          |                        | tal oscillator mode. In RC mode, the pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| RA0         2         I/O         TTL           RA1         3         I/O         TTL           RA2         4         I/O         TTL           RA3         5         I/O         TTL           RA3         5         I/O         TTL           RA4/T0CKI         6         I/O         ST         RA4 can also be the clock input to the Timer0 tin<br>Output is open drain type.           RA5/SS         7         I/O         TTL         RA5 can also be the slave select for the synchr<br>output.           RB0/INT         21         I/O         TTL/ST <sup>(4)</sup> RB0 can also be the external interrupt pin.           RB1         22         I/O         TTL         RB0 can also be the external interrupt pin.           RB2         23         I/O         TTL         Interrupt on change pin.           RB4         25         I/O         TTL         Interrupt on change pin.           RB5         26         I/O         TTL         Interrupt on change pin.           RB7         28         I/O         TTL/ST <sup>(9)</sup> Interrupt on change pin. Serial programming dat           RC0/T10S0 <sup>(1)</sup> /T1CKI         11         I/O         ST         RC1 can also be the Timer1 oscillator output <sup>(1)</sup><br>input/Compare2 output/PMZ output <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MCLR/Vpp                                      | 1    | I/P      | ST                     | Master clear reset input or programming voltage input. This pin is<br>an active low reset to the device.                             |

| RA1       3       I/O       TTL         RA2       4       I/O       TTL         RA3       5       I/O       TTL         RA4/T0CKI       6       I/O       ST       RA4 can also be the clock input to the Timer0 time Output is open drain type.         RA5/SS       7       I/O       TTL       RA5 can also be the slave select for the synchropot.         RB0/INT       21       I/O       TTL/ST <sup>(4)</sup> RB0 can also be the external interrupt on all inputs.         RB1       22       I/O       TTL       RA5 can also be the external interrupt on.         RB2       23       I/O       TTL       RB0 can also be the external interrupt on.         RB5       26       I/O       TTL       Interrupt on change pin.         RB6       27       I/O       TTL/ST <sup>(5)</sup> Interrupt on change pin.         RB7       28       I/O       TTL       Interrupt on change pin. Serial programming dat         RC0/T10S0 <sup>(1)</sup> /T1CKI       11       I/O       ST       RC0 can also be the Timer1 oscillator output <sup>(2)</sup> RC2/CCP1       13       I/O       ST       RC1 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.         RC4/SDI/SDA       15       I/O       ST       RC2 can also be the sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |      |          |                        | PORTA is a bi-directional I/O port.                                                                                                  |

| RA24I/OTTLRA35I/OTTLRA4/T0CKI6I/OSTRA4 can also be the clock input to the Timer0 tin<br>Output is open drain type.RA5/SS7I/OTTLRA5 can also be the slave select for the synchr<br>port.RB0/INT21I/OTTL/ST(4)PORTB is a bi-directional I/O port. PORTB can be so<br>grammed for internal weak pull-up on all inputs.RB0/INT21I/OTTL/ST(4)RB0 can also be the external interrupt pin.RB122I/OTTLRB0 can also be the external interrupt pin.RB324I/OTTLInterrupt on change pin.RB425I/OTTLInterrupt on change pin.RB526I/OTTLInterrupt on change pin. Serial programming datRB627I/OTTL/ST(5)Interrupt on change pin. Serial programming datRC0/T1OSO(1)/T1CKI11I/OSTRC0 can also be the Timer1 oscillator output <sup>[1]</sup><br>input/Compare2 output/PWM2 output <sup>[2]</sup> .RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SSCK/SCL14I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC7/RX/DT <sup>(2)</sup> 18I/OSTRC6 can also be the USART Asynchronous F<br>Synch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA0                                           | 2    | I/O      | TTL                    |                                                                                                                                      |

| RA3       5       I/O       TTL       RA4/T0CKI       6       I/O       ST       RA4 can also be the clock input to the Timer0 tin Output is open drain type.         RA5/SS       7       I/O       TTL       RA5 can also be the slave select for the synchra port.         RB0/INT       21       I/O       TTL/ST(4)       RB0 can also be the slave select for the synchra port.         RB0/INT       21       I/O       TTL/ST(4)       RB0 can also be the external interrupt pin.         RB1       22       I/O       TTL       RB0 can also be the external interrupt pin.         RB2       23       I/O       TTL       Interrupt on change pin.         RB4       25       I/O       TTL       Interrupt on change pin.         RB5       26       I/O       TTL/ST(5)       Interrupt on change pin. Serial programming dot         RC0/T10S0 <sup>(1)</sup> /T1CKI       11       I/O       ST       RC0 can also be the Timer1 oscillator output <sup>(1)</sup> clock input.         RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12       I/O       ST       RC1 can also be the Capture1 input/Com put/PM1 output.         RC3/SCK/SCL       14       I/O       ST       RC2 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).         RC4/SDI/SDA       15       I/O       ST       RC4 can also be the SPI D                                                                                                                                                                                                                                                                                                                                                                                                                                         | RA1                                           | 3    | I/O      | TTL                    |                                                                                                                                      |

| RA4/T0CKI6I/OSTRA4 can also be the clock input to the Timer0 tin<br>Output is open drain type.RA5/SS7I/OTTLRA5 can also be the slave select for the synchr<br>port.RB0/INT21I/OTTL/ST <sup>(4)</sup> PORTB is a bi-directional I/O port. PORTB can be so<br>grammed for internal weak pull-up on all inputs.RB0/INT21I/OTTL/ST <sup>(4)</sup> RB0 can also be the external interrupt pin.RB122I/OTTLRB0 can also be the external interrupt pin.RB324I/OTTLInterrupt on change pin.RB425I/OTTLInterrupt on change pin.RB627I/OTTL/ST <sup>(5)</sup> Interrupt on change pin.RB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTRC0 can also be the Timer1 oscillator output <sup>(1)</sup><br>input/Compare2 output/PWM2 output <sup>(2)</sup> .RC2/CCP113I/OSTRC2 can also be the Synchronous serial clock<br>for both SPI and I <sup>2</sup> C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC7/RX/DT <sup>(2)</sup> 18I/OSTRC6 can also be the USART Asynchronous Ta<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC6 can also be the USART Asynchronous Ta<br>Synchronous Clock <sup>(2)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA2                                           | 4    | I/O      | TTL                    |                                                                                                                                      |

| RA5/SS7I/OTTLOutput is open drain type.RA5/SS7I/OTTLRA5 can also be the slave select for the synchr<br>port.RB0/INT21I/OTTL/ST(4)PORTB is a bi-directional I/O port. PORTB can be so<br>grammed for internal weak pull-up on all inputs.RB122I/OTTLRB223I/OTTLRB425I/OTTLRB425I/OTTLRB627I/OTTL/ST(5)Interrupt on change pin.Interrupt on change pin.RB627I/OTTL/ST(5)RC0/T1OSO(1)/T1CKI11I/OSTRC0/T1OSO(1)/T1CKI11I/OSTRC1/T1OSI(1)/CCP2(2)12I/OSTRC2/SCK/SCL14I/OSTRC3/SDDA15I/OSTRC4/SDI/SDA15I/OSTRC5/SDO16I/OSTRC6/TX/CK(2)17I/OSTRC6/TX/CK(2)18I/OSTRC6/SDD16I/OSTRC6/SDD16I/OSTRC6/CAU(2)18I/ORC7/RX/DT(2)18I/OStRC6 can also be the SPI Data In (SPI mode).RC7/RX/DT(2)18I/OStRC6 can also be the USART Asynchronous F<br>Synchronous Clock <sup>2</sup> .RC7/RX/DT(2)18I/OStRC6 can also be the USART Asynchronous F<br>Synchronous Data <sup>2</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RA3                                           | 5    | I/O      | TTL                    |                                                                                                                                      |

| RA5/SS7I/OTTLRA5 can also be the slave select for the synchroport.<br>port.RB0/INT21I/OTTL/ST <sup>(4)</sup> PORTB is a bidirectional I/O port. PORTB can be so<br>grammed for internal weak pull-up on all inputs.RB122I/OTTLRB0 can also be the external interrupt pin.RB223I/OTTLRB0 can also be the external interrupt pin.RB324I/OTTLInterrupt on change pin.RB425I/OTTLInterrupt on change pin.RB526I/OTTLInterrupt on change pin. Serial programming cloRB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTRC1 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Capture1 input/Com<br>put/PWM1 output <sup>(2)</sup> .RC3/SCK/SCL14I/OSTRC2 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC7/RX/DT <sup>(2)</sup> 18I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC7/RX/DT <sup>(2)</sup> 18I/OSTRC6 can also be the SPI Data Out (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the USA                                                                                                                                                                                                                                                                                                                                                                                                                     | RA4/T0CKI                                     | 6    | I/O      | ST                     | RA4 can also be the clock input to the Timer0 timer/counte<br>Output is open drain type.                                             |

| RB0/INT21I/OTTL/ST(4)grammed for internal weak pull-up on all inputs.RB122I/OTTLRB0 can also be the external interrupt pin.RB223I/OTTLRB0 can also be the external interrupt pin.RB324I/OTTLInterrupt on change pin.RB526I/OTTLInterrupt on change pin.RB627I/OTTL/ST(5)Interrupt on change pin. Serial programming cloRB728I/OTTL/ST(5)Interrupt on change pin. Serial programming datRC0/T1OSO(1)/T1CKI11I/OSTRC0 can also be the Timer1 oscillator output(1)<br>clock input.RC1/T1OSI(1)/CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator input(1)<br>input/Compare2 output/PWM2 output(2).RC2/CCP113I/OSTRC2 can also be the SPI Data In (SPI mode) or<br>data I/O (1² c mode).RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA5/SS                                        | 7    | I/O      | TTL                    | RA5 can also be the slave select for the synchronous seria port.                                                                     |

| RB0/INT21I/OTTL/ST <sup>(4)</sup> RB0 can also be the external interrupt pin.RB122I/OTTLRB223I/OTTLRB324I/OTTLRB425I/OTTLInterrupt on change pin.RB526I/OTTLRB627I/ORB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming cloRC0/T10S0 <sup>(1)</sup> /T1CKI11I/OSTRC0 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator input <sup>(2)</sup> .RC3/SCK/SCL14I/OSTRC2 can also be the capture1 input/Com<br>put/PWM1 output.RC5/SDO16I/ORC5/SDO16I/ORC6/TX/CK <sup>(2)</sup> 17INOSTRC5 can also be the SPI Data In (SPI mode).RC6/TX/CK <sup>(2)</sup> 18I/OSTRC5 can also be the USART Asynchronous Ta<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .VSS8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |      |          |                        | PORTB is a bi-directional I/O port. PORTB can be software pro-                                                                       |

| RB122I/OTTLRB223I/OTTLRB324I/OTTLRB425I/OTTLInterrupt on change pin.RB526I/OTTLRB627I/OTTL/ST <sup>(5)</sup> RB728I/OTTL/ST <sup>(5)</sup> RC0/T10S0 <sup>(1)</sup> /T1CKI11I/OSTRC1/T10S1 <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC2/CCP113I/OSTRC3/SCK/SCL14I/OSTRC4/SDI/SDA15I/OSTRC5/SDO16I/OSTRC6/TX/CK <sup>(2)</sup> 17I/OSTRC6/TX/CK <sup>(2)</sup> 18I/OSTRC7/RX/DT <sup>(2)</sup> 18I/OSTRC7/RX/DT <sup>(2)</sup> 18I/OSTRC7/RX/DT <sup>(2)</sup> 18I/OSTRC7/RX/DT <sup>(2)</sup> 18I/OSTRC7can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .RC38,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BB0/INT                                       | 21   | 1/0      | TTI /ST(4)             | · · · ·                                                                                                                              |

| RB223I/OTTLRB324I/OTTLRB425I/OTTLInterrupt on change pin.RB526I/OTTLRB627I/OTTL/ST <sup>(5)</sup> RB728I/OTTL/ST <sup>(5)</sup> RC0/T1OSO <sup>(1)</sup> /T1CKI11I/ORC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC2/CCP113RC3/SCK/SCL14I/ORC4/SDI/SDA15I/OSTRC4 can also be the SPI Data Out (SPI mode).RC5/SDO16I/ORC5/SDO16I/ORC6/TX/CK <sup>(2)</sup> 17INI/OSTRC6 can also be the SPI Data Out (SPI mode).RC5/SDO16I/ORC7/RX/DT <sup>(2)</sup> 18INOSTRC7/RX/DT <sup>(2)</sup> 18INOSTRC7/RX/DT <sup>(2)</sup> 18INOSTRC7/RX/DT <sup>(2)</sup> 18INOSTRC7/RX/DT <sup>(2)</sup> 19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |      |          |                        |                                                                                                                                      |

| RB324I/OTTLRB425I/OTTLInterrupt on change pin.RB526I/OTTLInterrupt on change pin.RB627I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming cloRB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTRC0 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator input <sup>(1)</sup><br>input/Compare2 output/PWM2 output <sup>(2)</sup> .RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode).RC6/TX/CK <sup>(2)</sup> 17I/OSTRC6 can also be the USART Asynchronous Tr<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous Tr<br>Synchronous Data <sup>(2)</sup> .VSS8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |      |          |                        |                                                                                                                                      |

| RB425I/OTTLInterrupt on change pin.RB526I/OTTLInterrupt on change pin.RB627I/OTTL/ST <sup>(5)</sup> Interrupt on change pin.RB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTPORTC is a bi-directional I/O port.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator output <sup>(2)</sup> .RC2/CCP113I/OSTRC2 can also be the Capture1 input/Compare2 output/PWM2 output <sup>(2)</sup> .RC3/SCK/SCL14I/OSTRC3 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode).RC6/TX/CK <sup>(2)</sup> 17I/OSTRC6 can also be the USART Asynchronous Tr<br>Synchronous Data <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               | -    |          |                        |                                                                                                                                      |

| RB526I/OTTLInterrupt on change pin.RB627I/OTTL/ST <sup>(5)</sup> Interrupt on change pin.RB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin.RC0/T10S0 <sup>(1)</sup> /T1CKI11I/OSTPORTC is a bi-directional I/O port.RC0/T10S0 <sup>(1)</sup> /T1CKI11I/OSTRC0 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC1/T10SI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator input <sup>(1)</sup><br>input/Compare2 output/PWM2 output <sup>(2)</sup> .RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the SPI Data In (SPI mode) or<br>data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC5 can also be the SPI Data Out (SPI mode).RC6/TX/CK <sup>(2)</sup> 17I/OSTRC6 can also be the USART Asynchronous T<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |      |          |                        | latere et en aleman ain                                                                                                              |

| RB627I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming cloRB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTPORTC is a bi-directional I/O port.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the synchronous serial clock<br>for both SPI and I²C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I²C mode).RC5/SDO16I/OSTRC5 can also be the USART Asynchronous Tr<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .Vss8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               | -    |          |                        |                                                                                                                                      |

| RB728I/OTTL/ST <sup>(5)</sup> Interrupt on change pin. Serial programming datRC0/T1OSO <sup>(1)</sup> /T1CKI11I/OSTPORTC is a bi-directional I/O port.RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> 12I/OSTRC1 can also be the Timer1 oscillator output <sup>(1)</sup><br>clock input.RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the SPI bata In (SPI mode).RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode).RC5/SDO16I/OSTRC6 can also be the USART Asynchronous Tr<br>Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .VSS8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |      |          |                        |                                                                                                                                      |

| RC0/T1OSO(1)/T1CKI11I/OSTPORTC is a bi-directional I/O port.RC0/T1OSO(1)/T1CKI11I/OSTRC0 can also be the Timer1 oscillator output(1)<br>clock input.RC1/T1OSI(1)/CCP2(2)12I/OSTRC1 can also be the Timer1 oscillator input(1)<br>input/Compare2 output/PWM2 output(2).RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the synchronous serial clock<br>for both SPI and I2C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I2C mode).RC5/SDO16I/OSTRC6 can also be the SPI Data Out (SPI mode).RC6/TX/CK(2)17I/OSTRC6 can also be the USART Asynchronous TI<br>Synchronous Clock(2).RC7/RX/DT(2)18I/OSTRC7 can also be the USART Asynchronous TI<br>Synchronous Data(2).Vss8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |      |          |                        |                                                                                                                                      |

| RC0/T1OSO(1)/T1CKI11I/OSTRC0 can also be the Timer1 oscillator output<br>clock input.RC1/T1OSI(1)/CCP2(2)12I/OSTRC1 can also be the Timer1 oscillator input(1)<br>input/Compare2 output/PWM2 output(2).RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the synchronous serial clock<br>for both SPI and I2C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I2C mode).RC5/SDO16I/OSTRC6 can also be the USART Asynchronous Tr<br>Synchronous Clock(2).RC7/RX/DT(2)18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data(2).VSS8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RB7                                           | 28   | I/O      | TTL/ST(3)              |                                                                                                                                      |

| RC1/T1OSI(1)/CCP2(2)12I/OSTclock input.RC1/T1OSI(1)/CCP2(2)12I/OSTRC1 can also be the Timer1 oscillator input(1)<br>input/Compare2 output/PWM2 output(2).RC2/CCP113I/OSTRC2 can also be the Capture1 input/Com<br>put/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the synchronous serial clock<br>for both SPI and I2C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or<br>data I/O (I2C mode).RC5/SDO16I/OSTRC5 can also be the SPI Data Out (SPI mode).RC6/TX/CK(2)17I/OSTRC6 can also be the USART Asynchronous Tr<br>Synchronous Clock(2).RC7/RX/DT(2)18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data(2).Vss8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |      |          |                        | •                                                                                                                                    |

| Individualinput/Compare2 output/PWM2 output(2).RC2/CCP113I/OSTRC2 can also be the Capture1 input/Comput/PWM1 output.RC3/SCK/SCL14I/OSTRC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.RC4/SDI/SDA15I/OSTRC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).RC5/SDO16I/OSTRC5 can also be the SPI Data Out (SPI mode).RC6/TX/CK <sup>(2)</sup> 17I/OSTRC5 can also be the USART Asynchronous Tr Synchronous Clock <sup>(2)</sup> .RC7/RX/DT <sup>(2)</sup> 18I/OSTRC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .Vss8,19P—Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RC0/T1OSO <sup>(1)</sup> /T1CKI               | 11   | I/O      | ST                     | clock input.                                                                                                                         |

| RC3/SCK/SCL     14     I/O     ST     Put/PWM1 output.       RC4/SDI/SDA     15     I/O     ST     RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.       RC4/SDI/SDA     15     I/O     ST     RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       RC5/SDO     16     I/O     ST     RC5 can also be the SPI Data Out (SPI mode).       RC6/TX/CK <sup>(2)</sup> 17     I/O     ST     RC6 can also be the USART Asynchronous To Synchronous Clock <sup>(2)</sup> .       RC7/RX/DT <sup>(2)</sup> 18     I/O     ST     RC7 can also be the USART Asynchronous For Synchronous Data <sup>(2)</sup> .       Vss     8,19     P     —     Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RC1/T1OSI <sup>(1)</sup> /CCP2 <sup>(2)</sup> | 12   | I/O      | ST                     | RC1 can also be the Timer1 oscillator input <sup>(1)</sup> or Capture input/Compare2 output/PWM2 output <sup>(2)</sup> .             |

| RC4/SDI/SDA     15     I/O     ST     RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).       RC5/SDO     16     I/O     ST     RC5 can also be the SPI Data Out (SPI mode).       RC6/TX/CK <sup>(2)</sup> 17     I/O     ST     RC6 can also be the USART Asynchronous The Synchronous Clock <sup>(2)</sup> .       RC7/RX/DT <sup>(2)</sup> 18     I/O     ST     RC7 can also be the USART Asynchronous Festive Synchronous Data <sup>(2)</sup> .       Vss     8,19     P     —     Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RC2/CCP1                                      | 13   | I/O      | ST                     | RC2 can also be the Capture1 input/Compare1 out<br>put/PWM1 output.                                                                  |

| RC4/SDI/SDA       15       I/O       ST       RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).         RC5/SDO       16       I/O       ST       RC5 can also be the SPI Data Out (SPI mode).         RC6/TX/CK <sup>(2)</sup> 17       I/O       ST       RC6 can also be the USART Asynchronous The Synchronous Clock <sup>(2)</sup> .         RC7/RX/DT <sup>(2)</sup> 18       I/O       ST       RC7 can also be the USART Asynchronous Ferror Synchronous Data <sup>(2)</sup> .         Vss       8,19       P       —       Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RC3/SCK/SCL                                   | 14   | I/O      | ST                     | RC3 can also be the synchronous serial clock input/output                                                                            |

| RC5/SDO       16       I/O       ST       RC5 can also be the SPI Data Out (SPI mode).         RC6/TX/CK <sup>(2)</sup> 17       I/O       ST       RC6 can also be the USART Asynchronous To Synchronous Clock <sup>(2)</sup> .         RC7/RX/DT <sup>(2)</sup> 18       I/O       ST       RC7 can also be the USART Asynchronous For Synchronous Data <sup>(2)</sup> .         Vss       8,19       P       —       Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RC4/SDI/SDA                                   | 15   | I/O      | ST                     | RC4 can also be the SPI Data In (SPI mode) or                                                                                        |

| RC6/TX/CK <sup>(2)</sup> 17       I/O       ST       RC6 can also be the USART Asynchronous Tr<br>Synchronous Clock <sup>(2)</sup> .         RC7/RX/DT <sup>(2)</sup> 18       I/O       ST       RC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .         Vss       8,19       P       —       Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BC5/SDO                                       | 16   | 1/0      | ST                     |                                                                                                                                      |

| RC7/RX/DT <sup>(2)</sup> 18     I/O     ST     Synchronous Clock <sup>(2)</sup> .       RC7 can also be the USART Asynchronous F<br>Synchronous Data <sup>(2)</sup> .       Vss     8,19     P     —       Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               | -    |          |                        |                                                                                                                                      |

| Vss         8,19         P         —         Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |      |          |                        | Synchronous Clock <sup>(2)</sup> .                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |      |          | ST                     | Synchronous Data <sup>(2)</sup> .                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               | ,    |          | _                      | ° 1                                                                                                                                  |

| VDD         20         P         —         Positive supply for logic and I/O pins.           Legend:         I = input         O = output         I/O = input/output         P = power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               | 20   | Р        |                        |                                                                                                                                      |

#### TABLE 3-2: PIC16C62/62A/R62/63/R63/66 PINOUT DESCRIPTION

Note 1: Pin functions T1OSO and T1OSI are reversed on the PIC16C62.

2: The USART and CCP2 are not available on the PIC16C62/62A/R62.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: This buffer is a Schmitt Trigger input when configured as the external interrupt.

5: This buffer is a Schmitt Trigger input when used in serial programming mode.

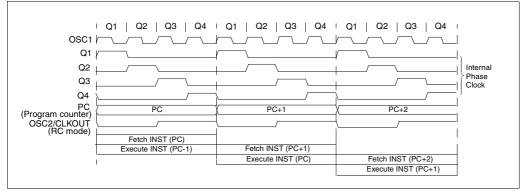

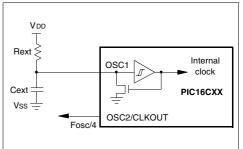

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clock and instruction execution flow is shown in Figure 3-5.

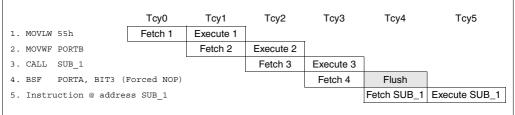

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-5: CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

| Address              | Name    | Bit 7                        | Bit 6                               | Bit 5         | Bit 4          | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets <sup>(3)</sup> |

|----------------------|---------|------------------------------|-------------------------------------|---------------|----------------|---------------|-----------------|---------------|-----------|--------------------------|------------------------------------------------|

| Bank 0               |         |                              |                                     |               |                |               |                 |               |           |                          | <u> </u>                                       |

| 00h <sup>(1)</sup>   | INDF    | Addressing                   | this location                       | uses conten   | ts of FSR to   | address data  | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                                      |

| 01h                  | TMR0    | Timer0 mod                   | lule's registe                      | r             |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL     | Program Co                   | ounter's (PC)                       | Least Signif  | ficant Byte    |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(5)</sup>           | RP1 <sup>(5)</sup>                  | RP0           | TO             | PD            | z               | DC            | С         | 0001 1xxx                | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR     | Indirect data                | a memory ad                         | Idress pointe | ər             |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 05h                  | PORTA   |                              | _                                   | PORTA Dat     | a Latch wher   | n written: PO | RTA pins wh     | en read       |           | xx xxxx                  | uu uuuu                                        |

| 06h                  | PORTB   | PORTB Dat                    | ta Latch whe                        | n written: PC | ORTB pins wi   | nen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 07h                  | PORTC   | PORTC Dat                    | ta Latch whe                        | n written: PC | ORTC pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 08h                  | PORTD   | PORTD Dat                    | ta Latch whe                        | n written: PC | ORTD pins w    | hen read      |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 09h                  | PORTE   |                              | _                                   | _             | _              | _             | RE2             | RE1           | RE0       | xxx                      | uuu                                            |

| 0Ah <sup>(1,2)</sup> | PCLATH  | -                            | —                                   | _             | Write Buffer   | for the uppe  | r 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                          | PEIE                                | TOIE          | INTE           | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                                      |

| 0Ch                  | PIR1    | PSPIF                        | (6)                                 | RCIF          | TXIF           | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF    | 0000 0000                | 0000 0000                                      |

| 0Dh                  | PIR2    |                              | _                                   | _             |                | _             | _               | _             | CCP2IF    | 0                        | 0                                              |

| 0Eh                  | TMR1L   | Holding reg                  | ister for the L                     | east Signific | cant Byte of t | he 16-bit TM  | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 0Fh                  | TMR1H   | Holding reg                  | ister for the M                     | Aost Signific | ant Byte of th | ne 16-bit TMF | R1 register     |               |           | xxxx xxxx                | uuuu uuuu                                      |

| 10h                  | T1CON   |                              | _                                   | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                                        |

| 11h                  | TMR2    | Timer2 mod                   | lule's registe                      | r             |                |               |                 |               |           | 0000 0000                | 0000 0000                                      |

| 12h                  | T2CON   | -                            | TOUTPS3                             | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                                      |

| 13h                  | SSPBUF  | Synchronou                   | is Serial Port                      | Receive Bu    | ffer/Transmit  | Register      |                 | •             |           | xxxx xxxx                | uuuu uuuu                                      |

| 14h                  | SSPCON  | WCOL                         | SSPOV                               | SSPEN         | CKP            | SSPM3         | SSPM2           | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                                      |

| 15h                  | CCPR1L  | Capture/Co                   | mpare/PWM                           | 1 (LSB)       |                |               |                 |               |           | xxxx xxxx                | uuuu uuuu                                      |